ANALOG DEVICES AD9255 Service Manual

14-Bit, 125 MSPS/105 MSPS/80 MSPS,

A

FEATURES

SNR = 78.3 dBFS @ 70 MHz and 125 MSPS

SFDR = 93 dBc @ 70 MHz and 125 MSPS

Low power: 371 mW @ 125 MSPS

1.8 V analog supply operation

1.8 V CMOS or LVDS output supply

Integer 1-to-8 input clock divider

IF sampling frequencies to 300 MHz

−153.4 dBm/Hz small signal input noise with 200 Ω input

impedance @ 70 MHz and 125 MSPS

Optional on-chip dither

Programmable internal ADC voltage reference

Integrated ADC sample-and-hold inputs

Flexible analog input range: 1 V p-p to 2 V p-p

Differential analog inputs with 650 MHz bandwidth

ADC clock duty cycle stabilizer

Serial port control

User-configurable, built-in self-test (BIST) capability

Energy-saving power-down modes

1.8 V Analog-to-Digital Converter

AD9255

APPLICATIONS

Communications

Multimode digital receivers (3G)

GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, and

TD-SCDMA

Smart antenna systems

General-purpose software radios

Broadband data applications

Ultrasound equipment

PRODUCT HIGHLIGHTS

1. On-chip dither option for improved SFDR performance

with low power analog input.

2. Proprietary differential input that maintains excellent SNR

performance for input frequencies up to 300 MHz.

3. Operation from a single 1.8 V supply and a separate digital

output driver supply accommodating 1.8 V CMOS or

LVDS outputs .

4. Standard serial port interface (SPI) that supports various

product features and functions, such as data formatting

(offset binary, twos complement, or gray coding), enabling

the clock DCS, power-down, test modes, and voltage

reference mode.

5. Pin compatibility with the AD9265, allowing a simple

migration up to 16 bits.

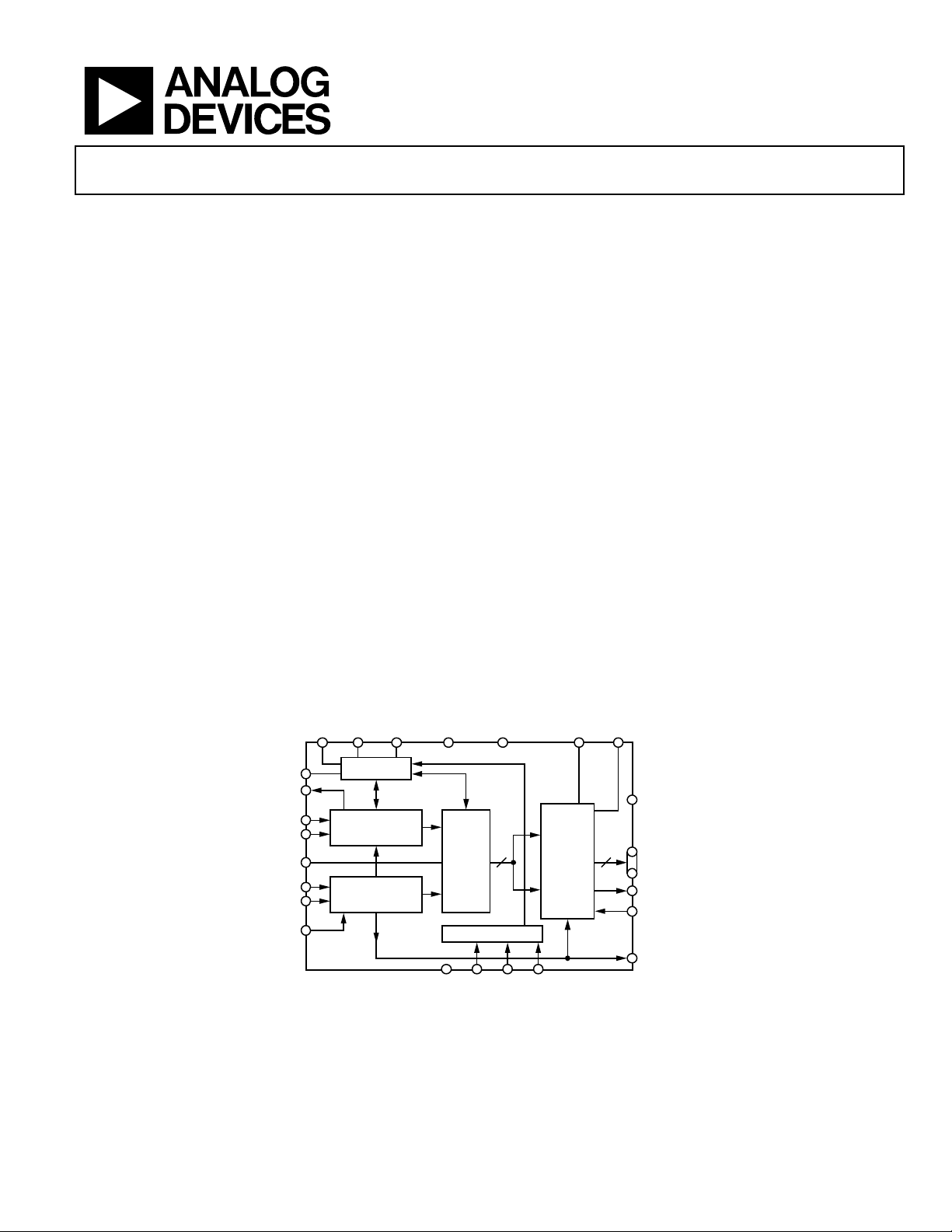

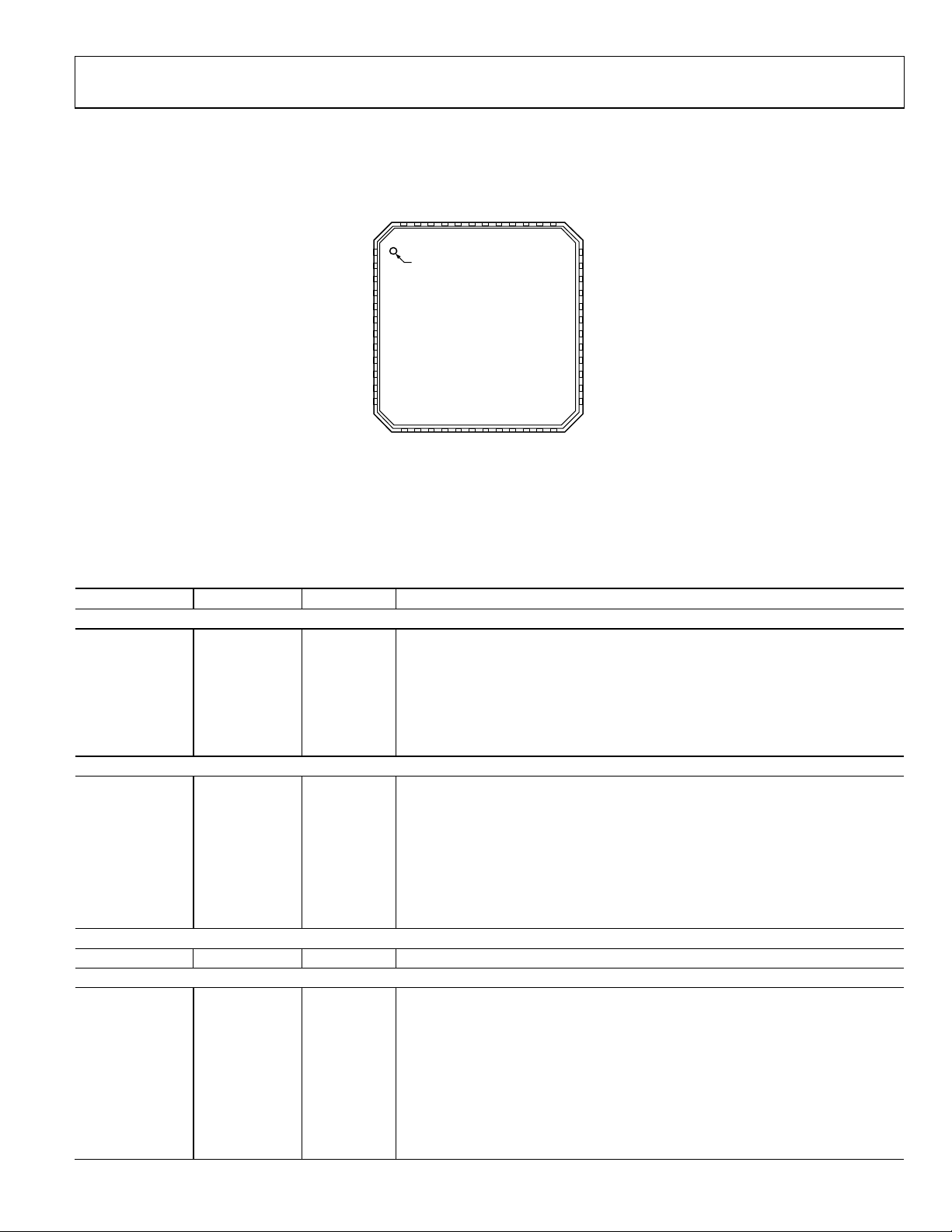

FUNCTIONAL BLOCK DIAGRAM

RBIASSENSE PDWN

VREF

VCM

VIN+

VIN–

DITHER

CLK+

CLK–

SYNC

REFERENCE

TRACK-AND-HOLD

CLOCK

MANAGEMENT

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

GNDAVDD (1.8V) LVDS LVDS_RS

ADC

14-BIT

CORE

SVDD

AD9255

14 14

SERIAL PORT

SCLK/

SDIO/

DFS

Figure 1.

CSB

DCS

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009–2010 Analog Devices, Inc. All rights reserved.

OUTPUT

STAGING

CMOS OR

LVDS

(DDR)

DRVDD (1.8V)

D13 TO D0

OR

OEB

DCO

08505-001

AD9255

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Product Highlights ........................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

General Description ......................................................................... 3

Specifications ..................................................................................... 4

ADC DC Specifications ................................................................. 4

ADC AC Specifications ................................................................. 5

Digital Specifications ................................................................... 6

Switching Specifications ................................................................ 8

Timing Specifications .................................................................. 9

Absolute Maximum Ratings .......................................................... 10

Thermal Characteristics ............................................................ 10

ESD Caution ................................................................................ 10

Pin Configurations and Function Descriptions ......................... 11

Typical Performance Characteristics ........................................... 15

Equivalent Circuits ......................................................................... 23

Theory of Operation ...................................................................... 25

ADC Architecture ...................................................................... 25

Analog Input Considerations .................................................... 25

Voltage Reference ....................................................................... 28

Clock Input Considerations ...................................................... 29

Power Dissipation and Standby Mode .................................... 31

Digital Outputs ........................................................................... 32

Timing ......................................................................................... 32

Built-In Self-Test (BIST) and Output Test .................................. 33

Built-In Self-Test (BIST) ............................................................ 33

Output Test Modes ..................................................................... 33

Serial Port Interface (SPI) .............................................................. 34

Configuration Using the SPI ..................................................... 34

Hardware Interface ..................................................................... 34

Configuration Without the SPI ................................................ 35

SPI Accessible Features .............................................................. 35

Memory Map .................................................................................. 36

Reading the Memory Map Register Table ............................... 36

Memory Map Register Table ..................................................... 37

Memory Map Register Descriptions ........................................ 39

Applications Information .............................................................. 40

Design Guidelines ...................................................................... 40

Outline Dimensions ....................................................................... 41

Ordering Guide .......................................................................... 41

REVISION HISTORY

1/10—Rev. 0 to Rev. A

Changes to Worst Other (Harmonic or Spur) Parameter,

Table 2 ................................................................................................ 6

Changes to Figure 77 ...................................................................... 29

Changes to Input Clock Divider Section ..................................... 30

Changes to Table 17 ........................................................................ 37

Updated Outline Dimensions ....................................................... 41

10/09—Revision 0: Initial Version

Rev. A | Page 2 of 44

AD9255

GENERAL DESCRIPTION

The AD9255 is a 14-bit, 125 MSPS analog-to-digital converter

(ADC). The AD9255 is designed to support communications

applications where high performance combined with low cost,

small size, and versatility is desired.

The ADC core features a multistage, differential pipelined

architecture with integrated output error correction logic to

provide 14-bit accuracy at 125 MSPS data rates and guarantees

no missing codes over the full operating temperature range.

The ADC features a wide bandwidth differential sample-andhold analog input amplifier supporting a variety of user-selectable

input ranges. It is suitable for multiplexed systems that switch

full-scale voltage levels in successive channels and for sampling

single-channel inputs at frequencies well beyond the Nyquist rate.

Combined with power and cost savings over previously available

ADCs, the AD9255 is suitable for applications in communications,

instrumentation, and medical imaging.

A differential clock input controls all internal conversion cycles. A

duty cycle stabilizer provides the means to compensate for variations in the ADC clock duty cycle, allowing the converters to

maintain excellent performance over a wide range of input

clock duty cycles. An integrated voltage reference eases design

considerations.

The ADC output data format is either parallel 1.8 V CMOS or

LVDS (DDR). A data output clock is provided to ensure proper

latch timing with receiving logic.

Programming for setup and control is accomplished using a 3-wire

SPI-compatible serial interface. Flexible power-down options

allow significant power savings, when desired. An optional onchip dither function is available to improve SFDR performance

with low power analog input signals.

The AD9255 is available in a Pb-free, 48-lead LFCSP and is

specified over the industrial temperature range of −40°C to +85°C.

Rev. A | Page 3 of 44

AD9255

SPECIFICATIONS

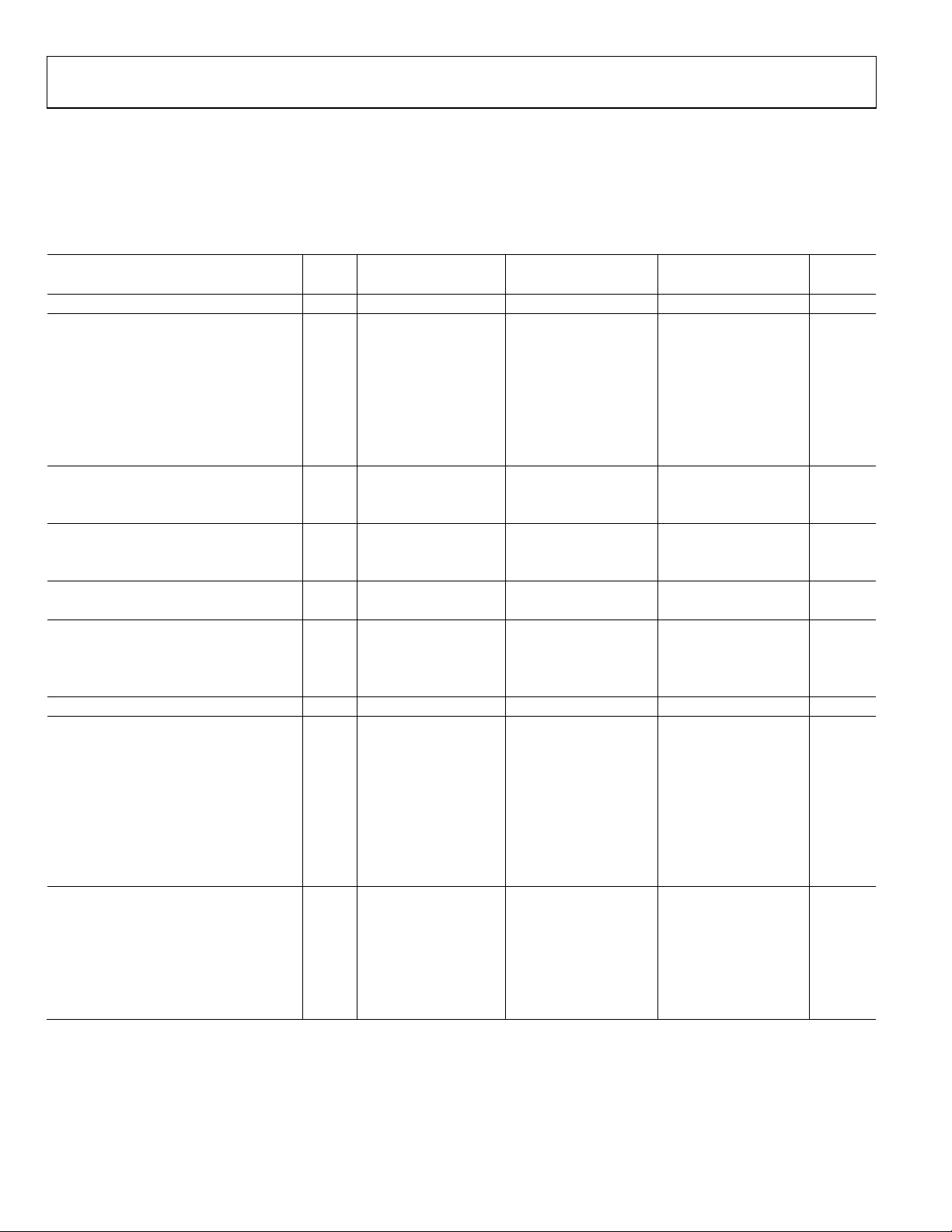

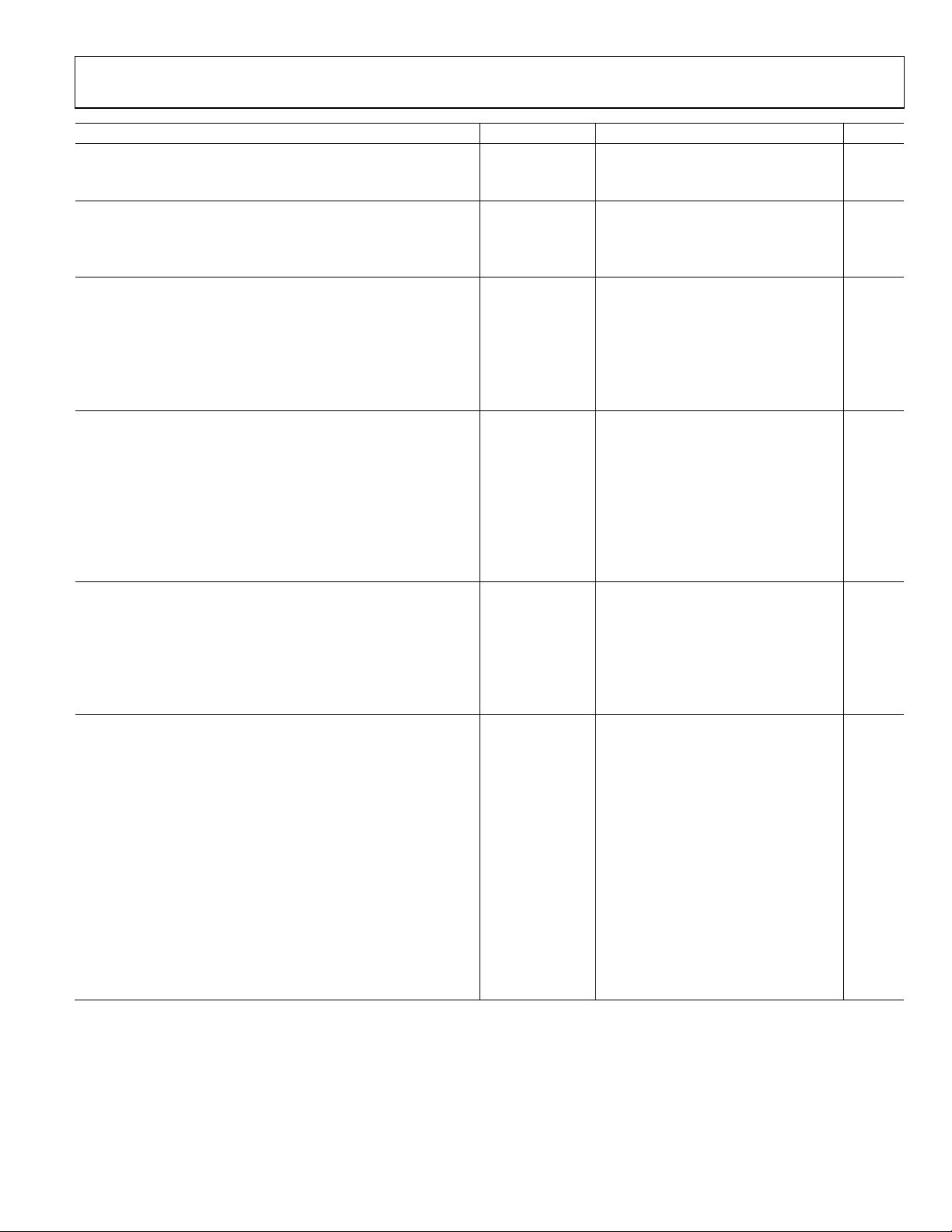

ADC DC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, SVDD = 1.8 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, DCS

enabled, unless otherwise noted.

Table 1.

AD9255BCPZ-80

Parameter Temp

Min Typ Max Min Typ Max Min Typ Max

1

AD9255BCPZ-1051 AD9255BCPZ-1251

Unit

RESOLUTION Full 14 14 14 Bits

ACCURACY

No Missing Codes Full Guaranteed Guaranteed Guaranteed

Offset Error Full ±0.05 ±0.25 ±0.05 ±0.25 ±0.05 ±0.25 % FSR

Gain Error Full ±0.2 ±2.5 ±0.2 ±2.5 ±0.4 ±2.5 % FSR

Differential Nonlinearity (DNL)2 Full ±0.4 ±0.4 ±0.45 LSB

25°C ±0.2 ±0.2 ±0.25 LSB

Integral Nonlinearity (INL)2 Full ±0.9 ±0.9 ±1.2 LSB

25°C ±0.35 ±0.45 ±0.7 LSB

TEMPERATURE DRIFT

Offset Error Full ±2 ±2 ±2 ppm/°C

Gain Error Full ±15 ±15 ±15 ppm/°C

INTERNAL VOLTAGE REFERENCE

Output Voltage Error (1 V Mode) Full +8 ±12 +8 ±12 +8 ±12 mV

Load Regulation @ 1.0 mA Full 3 3 3 mV

INPUT REFERRED NOISE

VREF = 1.0 V 25°C 0.62 0.63 0.61 LSB rms

ANALOG INPUT

Input Span, VREF = 1.0 V Full

Input Capacitance3 Full

Input Common-Mode Voltage Full

REFERENCE INPUT RESISTANCE Full

POWER SUPPLIES

Supply Voltage

AVDD Full

DRVDD Full

SVDD Full

Supply Current

IAVDD2 Full

IDRVDD2 (1.8 V CMOS) Full

IDRVDD2 (1.8 V LVDS) Full

POWER CONSUMPTION

DC Input Full

Sine Wave Input2

CMOS Output Mode Full

LVDS Output Mode Full

Standby Power4 Full

Power-Down Power Full

1

The suffix following the part number refers to the model found in the Ordering Guide section.

2

Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit.

3

Input capacitance refers to the effective capacitance between one differential input pin and AGND.

4

Standby power is measured with a dc input, the CLK pins (CLK+, CLK−) inactive (set to AVDD or AGND).

22

88

0.9 0.9

66

1.7 1.8 1.9 1.7 1.8 1.9

1.7 1.8 1.9 1.7 1.8 1.9

1.7 3.5 1.7 3.5 1.7 3.5

126 131 169 176

13 19

39 42

239 248 321 332

252 338

306 384

54 54

0.05 0.15 0.05 0.15

2 V p-p

8 pF

0.9 V

6 kΩ

1.7 1.8 1.9 V

1.7 1.8 1.9 V

194 202 mA

23 mA

44 mA

371 382 mW

391 mW

437 mW

54 mW

0.05 0.15 mW

V

Rev. A | Page 4 of 44

AD9255

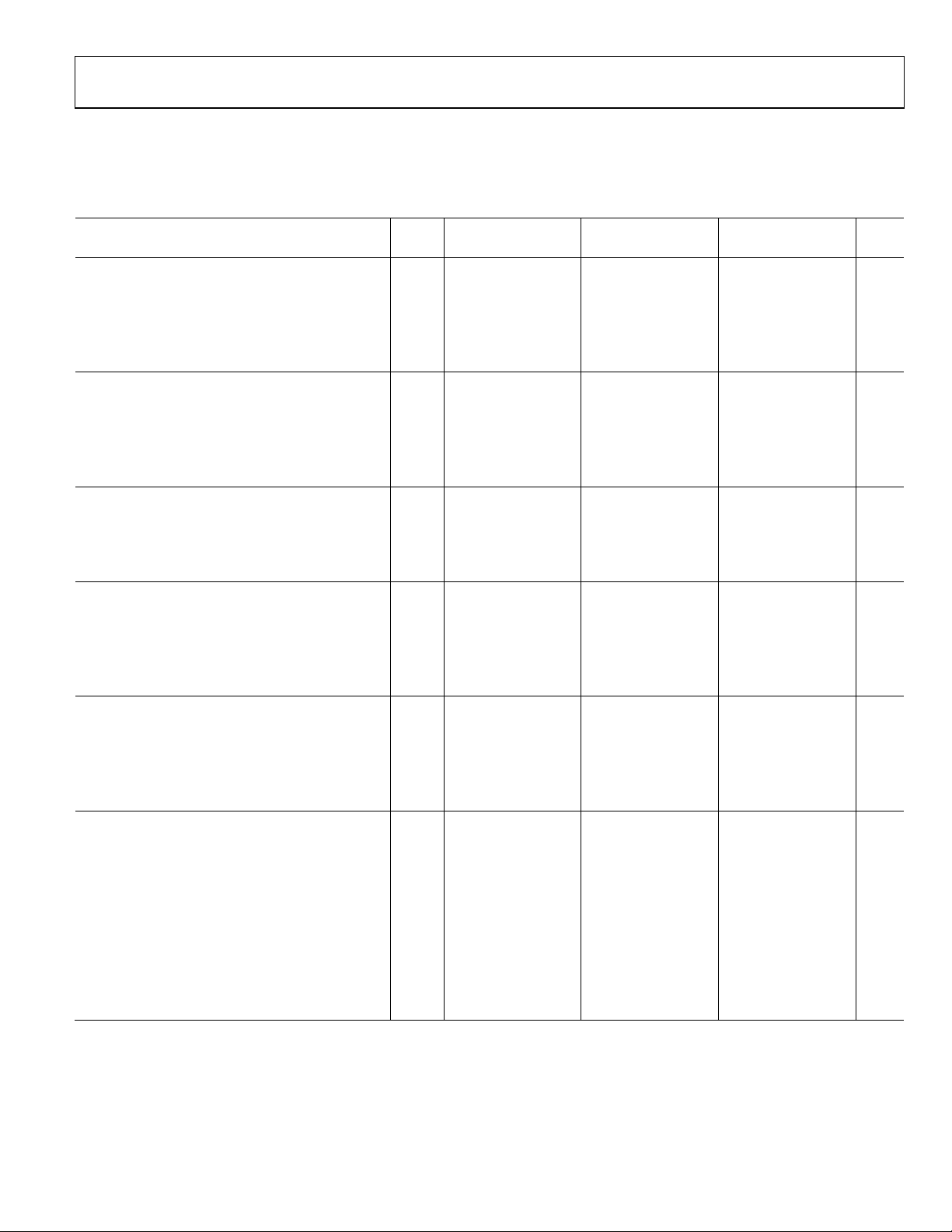

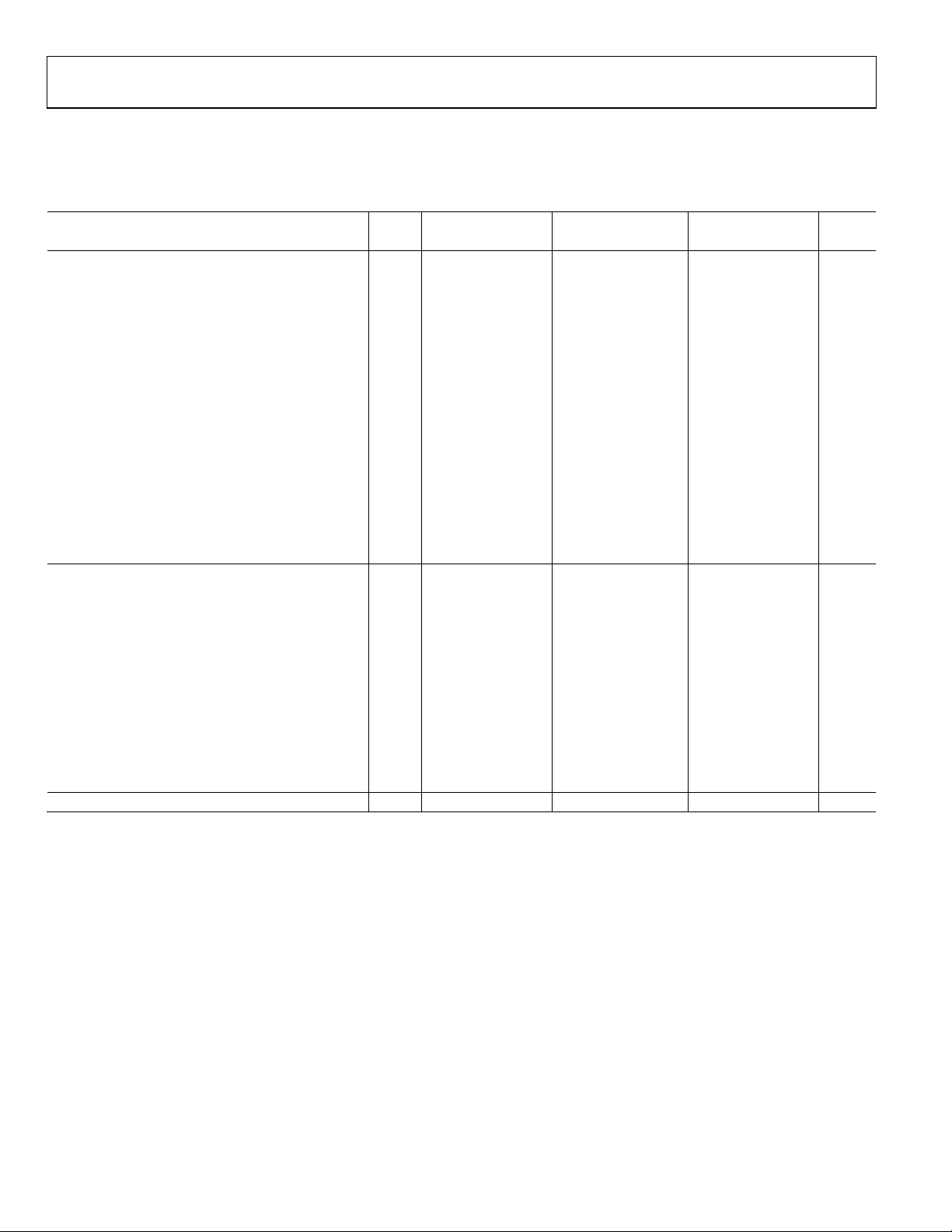

ADC AC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, SVDD = 1.8 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, DCS

enabled, unless otherwise noted.

Table 2.

AD9255BCPZ-80

Parameter1 Temp

SIGNAL-TO-NOISE-RATIO (SNR)

fIN = 2.4 MHz 25°C 79.2 78.9 78.3 dBFS

fIN = 70 MHz 25°C 78.9 78.5 78.3 dBFS

Full 78.1 77.6 76.9 dBFS

fIN = 140 MHz 25°C 78.0 77.7 77.1 dBFS

fIN = 200 MHz 25°C 76.9 76.4 75.5 dBFS

SIGNAL-TO-NOISE-AND DISTORTION (SINAD)

fIN = 2.4 MHz 25°C 78.7 78.6 78.0 dBFS

fIN = 70 MHz 25°C 78.7 78.0 78.0 dBFS

Full 77.9 77.3 76.7 dBFS

fIN = 140 MHz 25°C 76.8 77.0 76.7 dBFS

fIN = 200 MHz 25°C

EFFECTIVE NUMBER OF BITS (ENOB)

fIN = 2.4 MHz 25°C

fIN = 70 MHz 25°C

fIN = 140 MHz 25°C

fIN = 200 MHz 25°C

WORST SECOND OR THIRD HARMONIC

fIN = 2.4 MHz 25°C −88 −90

fIN = 70 MHz 25°C −94 −89

Full

fIN = 140 MHz 25°C −82 −86

fIN = 200 MHz 25°C −81 −81

SPURIOUS-FREE DYNAMIC RANGE (SFDR)

fIN = 2.4 MHz 25°C 88 90

fIN = 70 MHz 25°C 94 89

Full

fIN = 140 MHz 25°C 82 86

fIN = 200 MHz 25°C 81 81

SPURIOUS-FREE DYNAMIC RANGE (SFDR)

Without Dither (AIN @ −23 dBFS)

fIN = 2.4 MHz 25°C 102 99

fIN = 70 MHz 25°C 103 97

fIN = 140 MHz 25°C 104 97

fIN = 200 MHz 25°C 102 101

With On-Chip Dither (AIN @ −23 dBFS)

fIN = 2.4 MHz 25°C 110 109

fIN = 70 MHz 25°C 110 108

fIN = 140 MHz 25°C 110 108

fIN = 200 MHz 25°C 110 109

Min Typ Max Min Typ Max Min Typ Max

75.8

12.8 12.8

12.8 12.7

12.5 12.5

12.3 12.2

91

88 85

2

AD9255BCPZ-1052 AD9255BCPZ-1252

−91

75.3

−88

74.3

12.7

12.7

12.4

12.0

−88

−93

−85

−89

−80

88

93

89

80

96

99

98

97

108

109

109

109

Unit

dBFS

Bits

Bits

Bits

Bits

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

dBFS

Rev. A | Page 5 of 44

AD9255

AD9255BCPZ-80

Parameter1 Temp

Min Typ Max Min Typ Max Min Typ Max

2

AD9255BCPZ-1052 AD9255BCPZ-1252

WORST OTHER (HARMONIC OR SPUR)

Without Dither

fIN = 2.4 MHz 25°C −106 −105 −101

fIN = 70 MHz 25°C −106 −104 −104

Full

−94

−95

−91

fIN = 140 MHz 25°C −104 −104 −103

fIN = 200 MHz 25°C −102 −103 −100

With On-Chip Dither

fIN = 2.4 MHz 25°C −105 −106 −101

fIN = 70 MHz 25°C −106 −105 −104

Full

−97

−99

−98

fIN = 140 MHz 25°C −103 −103 −103

fIN = 200 MHz 25°C −100 −101 −100

TWO-TONE SFDR

Without Dither

fIN = 29 MHz (−7 dBFS ), 32 MHz (−7 dBFS ) 25°C

fIN = 169 MHz (−7 dBFS ), 172 MHz (−7 dBFS ) 25°C

ANALOG INPUT BANDWIDTH 25°C

1

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions.

2

The suffix following the part number refers to the model found in the section. Ordering Guide

93 90

80 78

650

650

95

79

650

Unit

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

MHz

DIGITAL SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, SVDD = 1.8 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, and DCS

enabled, unless otherwise noted.

Table 3.

Parameter Temperature Min Typ Max Unit

DIFFERENTIAL CLOCK INPUTS (CLK+, CLK−)

Logic Compliance CMOS/LVDS/LVPECL

Internal Common-Mode Bias Full 0.9 V

Differential Input Voltage Full 0.3 3.6 V p-p

Input Voltage Range Full AGND AVDD V

Input Common-Mode Range Full 0.9 1.4 V

High Level Input Current Full −100 +100 μA

Low Level Input Current Full −100 +100 μA

Input Capacitance Full 4 pF

Input Resistance Full 8 10 12 kΩ

SYNC INPUT

Logic Compliance CMOS

Internal Bias Full 0.9 V

Input Voltage Range Full AGND AVDD V

High Level Input Voltage Full 1.2 AVDD V

Low Level Input Voltage Full AGND 0.6 V

High Level Input Current Full −100 +100 μA

Low Level Input Current Full −100 +100 μA

Input Capacitance Full 1 pF

Input Resistance Full 12 16 20 kΩ

Rev. A | Page 6 of 44

AD9255

Parameter Temperature Min Typ Max Unit

LOGIC INPUT (CSB)1

High Level Input Voltage Full 1.22 SVDD V

Low Level Input Voltage Full 0 0.6 V

High Level Input Current Full −10 +10 μA

Low Level Input Current Full 40 132 μA

Input Resistance Full 26 kΩ

Input Capacitance Full 2 pF

LOGIC INPUT (SCLK/DFS)2

High Level Input Voltage Full 1.22 SVDD V

Low Level Input Voltage Full 0 0.6 V

High Level Input Current (VIN = 1.8 V) Full −92 −135 μA

Low Level Input Current Full −10 +10 μA

Input Resistance Full 26 kΩ

Input Capacitance Full 2 pF

LOGIC INPUT/OUTPUT (SDIO/DCS)1

High Level Input Voltage Full 1.22 SVDD V

Low Level Input Voltage Full 0 0.6 V

High Level Input Current Full −10 +10 μA

Low Level Input Current Full 38 128 μA

Input Resistance Full 26 kΩ

Input Capacitance Full 5 pF

High Level Output Voltage Full 1.70 V

Low Level Output Voltage Full 0.2 V

LOGIC INPUTS (OEB, PDWN, DITHER, LVDS, LVDS_RS)2

High Level Input Voltage Full 1.22 2.1 V

Low Level Input Voltage Full 0 0.6 V

High Level Input Current (VIN = 1.8 V) Full −90 −134 μA

Low Level Input Current Full −10 +10 μA

Input Resistance Full 26 kΩ

Input Capacitance Full 5 pF

DIGITAL OUTPUTS (DRVDD = 1.8 V)

CMOS Mode

High Level Output Voltage

IOH = 50 μA Full 1.79 V

IOH = 0.5 mA Full 1.75 V

Low Level Output Voltage

IOL = 1.6 mA Full 0.2 V

IOL = 50 μA Full 0.05 V

LVDS Mode

ANSI Mode

Differential Output Voltage (VOD) Full 290 345 400 mV

Output Offset Voltage (VOS) Full 1.15 1.25 1.35 V

Reduced Swing Mode

Differential Output Voltage (VOD) Full 160 200 230 mV

Output Offset Voltage (VOS) Full 1.15 1.25 1.35 V

1

Pull-up.

2

Pull-down.

Rev. A | Page 7 of 44

AD9255

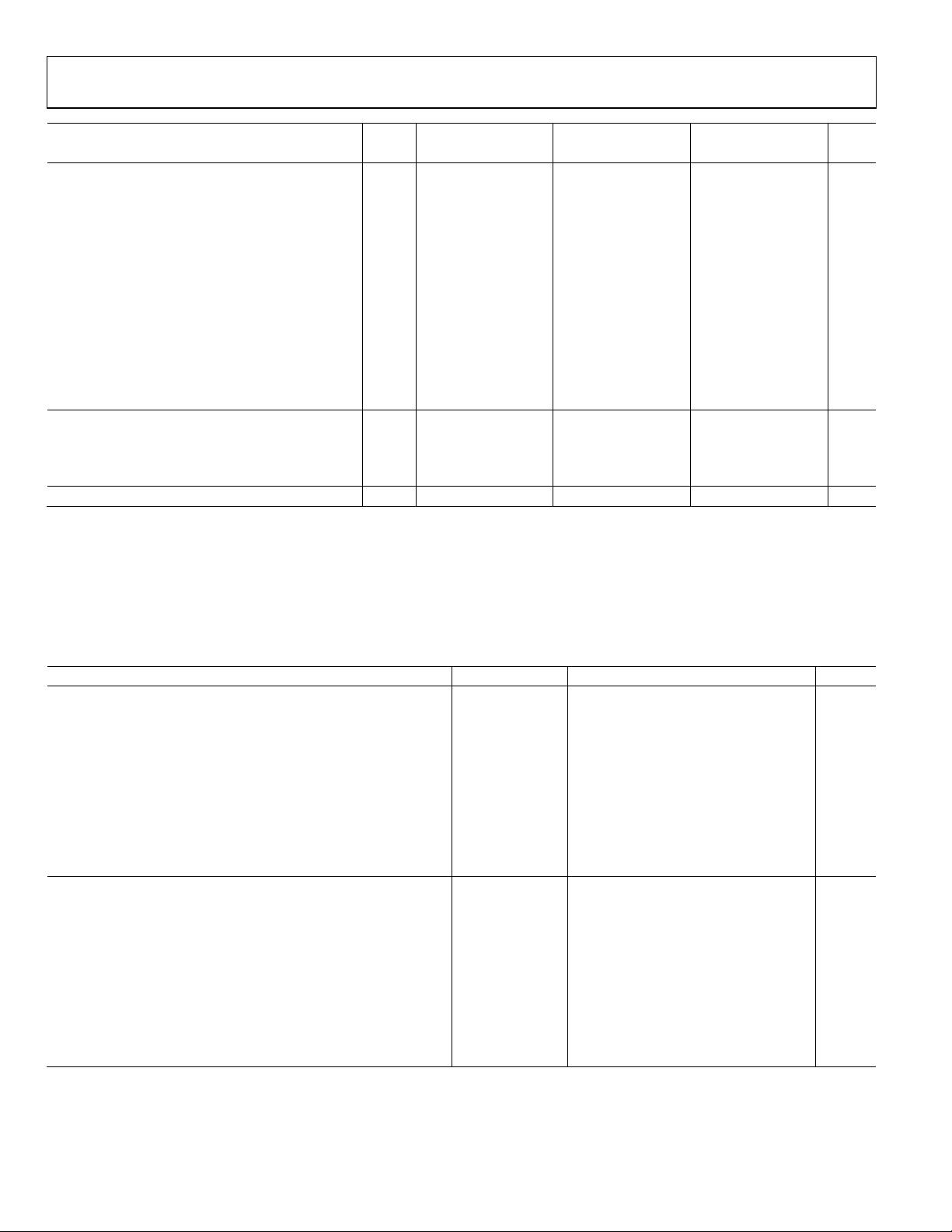

SWITCHING SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, SVDD = 1.8 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, and

DCS enabled, unless otherwise noted.

Table 4.

AD9255BCPZ-801 AD9255BCPZ-1051 AD9255BCPZ-1251

Parameter Temp Min Typ Max Min Typ Max Min Typ Max Unit

CLOCK INPUT PARAMETERS

Input Clock Rate Full 625 625 625 MHz

Conversion Rate2

DCS Enabled Full 20 80 20 105 20 125 MSPS

DCS Disabled Full 10 80 10 105 10 125 MSPS

CLK Period—Divide-by-1 Mode (t

CLK Pulse Width High (tCH)

Divide-by-1 Mode

DCS Enabled Full 3.75 6.25 8.75 2.85 4.75 6.65 2.4 4 5.6 ns

DCS Disabled 5.9 6.25 6.6 4.5 4.75 5.0 3.8 4 4.2 ns

Divide-by-3 Mode, Divide-by-5 Mode, and

Divide-by-7 Mode, DCS Enabled

Divide-by-2 Mode, Divide-by-4 Mode, Divide-

by-6 Mode, and Divide-by-8 Mode, DCS

Enabled or DCS Disabled3

Aperture Delay (tA) Full 1.0 1.0 1.0 ns

Aperture Uncertainty (Jitter, tJ) Full 0.07 0.07 0.07 ps rms

DATA OUTPUT PARAMETERS

CMOS Mode

Data Propagation Delay (tPD) Full 2.4 2.8 3.4 2.4 2.8 3.4 2.4 2.8 3.4 ns

DCO Propagation Delay (t

DCO to Data Skew (t

SKEW

Pipeline Delay (Latency) Full 12 12 12 Cycles

LVDS Mod e

Data Propagation Delay (tPD) Full 2.6 3.4 4.2 2.6 3.4 4.2 2.6 3.4 4.2 ns

DCO Propagation Delay (t

DCO to Data Skew (t

SKEW

Pipeline Delay (Latency) Full 12.5 12.5 12.5 Cycles

Wake-Up Time5 Full 500 500 500 μs

OUT-OF-RANGE RECOVERY TIME Full 2 2 2 Cycles

1

The suffix following the part number refers to the model found in the section. Ordering Guide

2

Conversion rate is the clock rate after the divider.

3

See the section for additional information on using the DCS with the input clock divider. Input Clock Divider

4

Additional DCO delay can be added by writing to Bit 0 through Bit 4 in SPI Register 0x17 (see ). Table 17

5

Wake-up time is defined as the time required to return to normal operation from power-down mode.

) Full 12.5 9.5 8 ns

CLK

3

Full 0.8 0.8 0.8 ns

Full 0.8 0.8 0.8 ns

)4 Full 2.7 3.4 4.2 2.7 3.4 4.2 2.7 3.4 4.2 ns

DCO

) Full 0.3 0.6 0.9 0.3 0.6 0.9 0.3 0.6 0.9 ns

)4 Full 3.3 3.8 4.3 3.3 3.8 4.3 3.3 3.8 4.3 ns

DCO

) −0.3 +0.4 +1.2 −0.3 +0.4 +1.2 −0.3 +0.4 +1.2

Rev. A | Page 8 of 44

AD9255

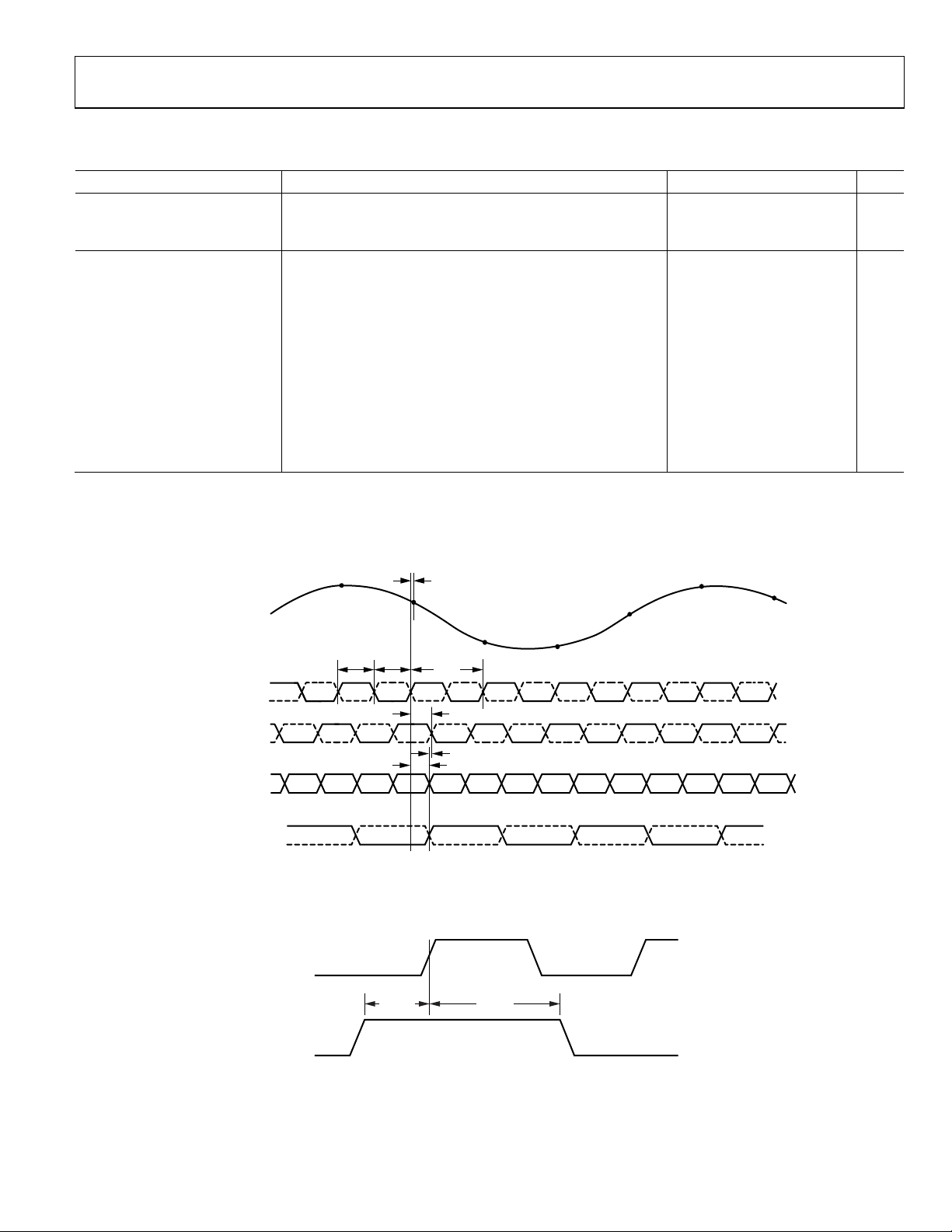

TIMING SPECIFICATIONS

Table 5.

Parameter Conditions Min Typ Max Unit

SYNC TIMING REQUIREMENTS

t

SYNC to rising edge of CLK setup time 0.30 ns

SSYNC

t

SYNC to rising edge of CLK hold time 0.40 ns

HSYNC

SPI TIMING REQUIREMENTS1

tDS Setup time between the data and the rising edge of SCLK 2 ns

tDH Hold time between the data and the rising edge of SCLK 2 ns

t

Period of the SCLK 40 ns

CLK

tS Setup time between CSB and SCLK 2 ns

tH Hold time between CSB and SCLK 2 ns

t

SCLK pulse width high 10 ns

HIGH

t

SCLK pulse width low 10 ns

LOW

t

EN_SDIO

t

DIS_SDIO

1

Refer to for a detailed timing diagram. Figure 84

Timing Diagrams

D0/1+ TO D12/D13+

D0/1– TO D12/D13–

Time required for the SDIO pin to switch from an input to an

output relative to the SCLK falling edge

Time required for the SDIO pin to switch from an output to an

input relative to the SCLK rising edge

VIN

CLK+

CLK–

DCO/DCO+

DCO–

LVDS (DDR) MODE

CMOS MODE

D0 TO D13

NOTES

1. DEx DENOTES EVEN BIT.

2. DOx DENOTES ODD BIT .

N – 1

t

CHtCL

t

DCO

t

A

N

N + 1

t

CLK

t

SKEW

t

PD

DEx

DOx

– 12

– 12

Dx – 12 Dx – 11 Dx – 10 Dx – 9 Dx – 8

DEx

– 11

N + 2

DOx

– 11

DEx

– 10

N + 3

DOx

– 10

Figure 2. LVDS (DDR) and CMOS Output Mode Data Output Timing

10 ns

10 ns

DEx

N + 4

DOx

– 9

– 9

DEx

N + 5

DOx

– 8

– 8

08505-002

CLK+

t

HSYNC

08505-104

SYNC

t

SSYNC

Figure 3. SYNC Input Timing Requirements

Rev. A | Page 9 of 44

AD9255

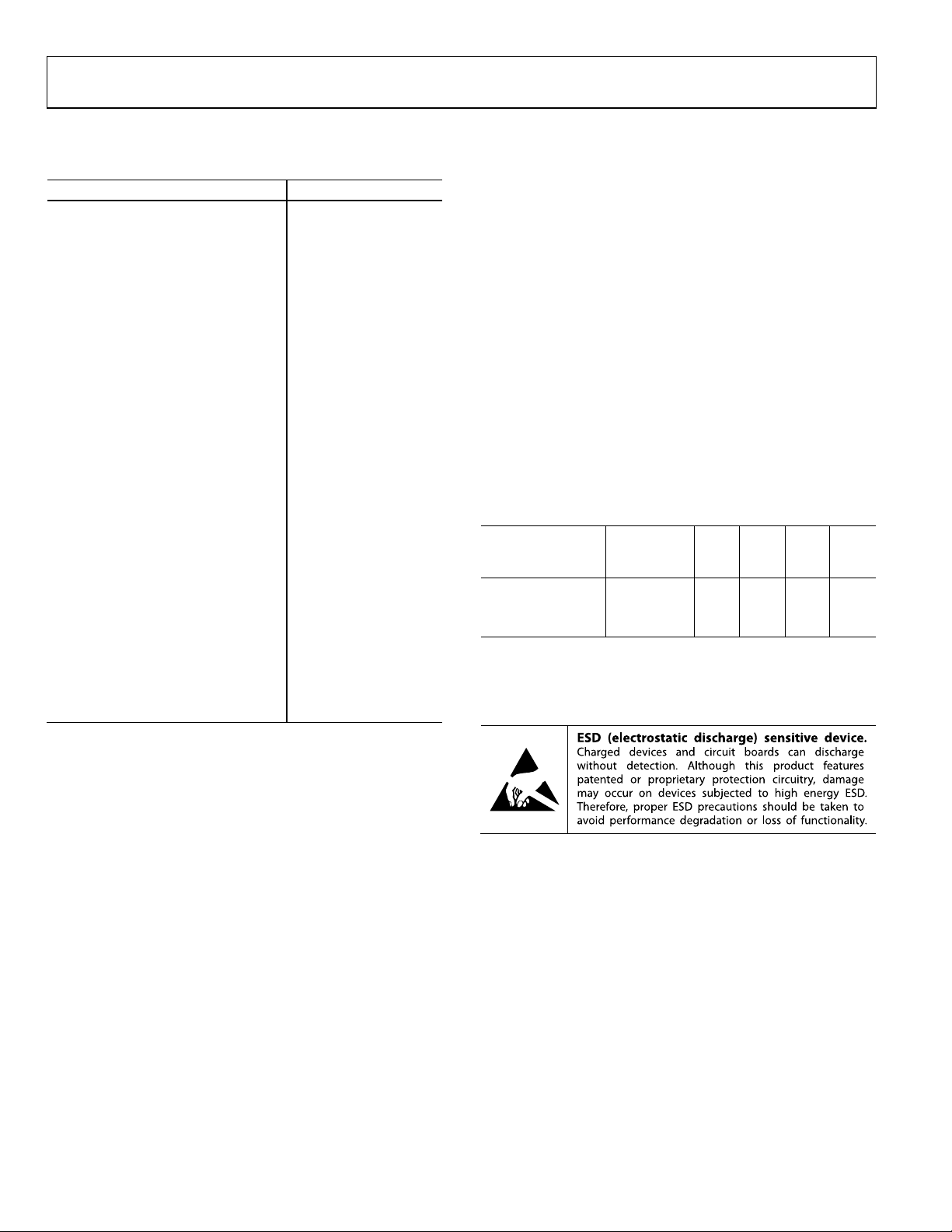

ABSOLUTE MAXIMUM RATINGS

Table 6.

Parameter Rating

Electrical

AVDD to AGND −0.3 V to +2.0 V

DRVDD to AGND −0.3 V to +2.0V

SVDD to AGND −0.3 V to +3.6 V

VIN+, VIN− to AGND −0.3 V to AVDD + 0.2 V

CLK+, CLK− to AGND −0.3 V to AVDD + 0.2 V

SYNC to AGND −0.3 V to AVDD + 0.2 V

VREF to AGND −0.3 V to AVDD + 0.2 V

SENSE to AGND −0.3 V to AVDD + 0.2 V

VCM to AGND −0.3 V to AVDD + 0.2 V

RBIAS to AGND −0.3 V to AVDD + 0.2 V

CSB to AGND −0.3 V to SVDD +0.3 V

SCLK/DFS to AGND −0.3 V to SVDD +0.3 V

SDIO/DCS to AGND −0.3V to SVDD + 0.3 V

OEB to AGND −0.3 V to DRVDD + 0.2 V

PDWN to AGND −0.3 V to DRVDD + 0.2 V

LVDS to AGND −0.3 V to AVDD + 0.2 V

LVD S_RS to AG ND −0.3 V to AVDD + 0.2 V

DITHER to AGND −0.3 V to AVDD + 0.2 V

D0 through D13 to AGND

DCO to AGND

−0.3 V to DRVDD + 0.2 V

−0.3 V to DRVDD + 0.2 V

Environmental

Operating Temperature Range

−40°C to +85°C

(Ambient)

Maximum Junction Temperature

150°C

Under Bias

Storage Temperature Range

−65°C to +150°C

(Ambient)

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

The exposed paddle must be soldered to the ground plane for

the LFCSP package. Soldering the exposed paddle to the customer

board increases the reliability of the solder joints and maximizes

the thermal capability of the package.

Typical θ

plane. As shown, airflow improves heat dissipation, which

reduces θ

leads from metal traces, through holes, ground, and power

planes, reduces the θ

Table 7. Thermal Resistance

Packa ge Type

48-Lead LFCSP

(CP-48-8)

1

Per JEDEC 51-7, plus JEDEC 25-5 2S2P test board.

2

Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

3

Per MIL-Std 883, Method 1012.1.

4

Per JEDEC JESD51-8 (still air).

ESD CAUTION

is specified for a 4-layer PCB with a solid ground

JA

. In addition, metal in direct contact with the package

JA

.

JA

Airflow

Veloc ity

(m/s) θ

1, 2

1, 3

θ

JA

JC

1, 4

θ

JB

0 24.5 1.3 12.7 °C/W

1.0 21.4 °C/W

2.5 19.2 °C/W

Unit

Rev. A | Page 10 of 44

AD9255

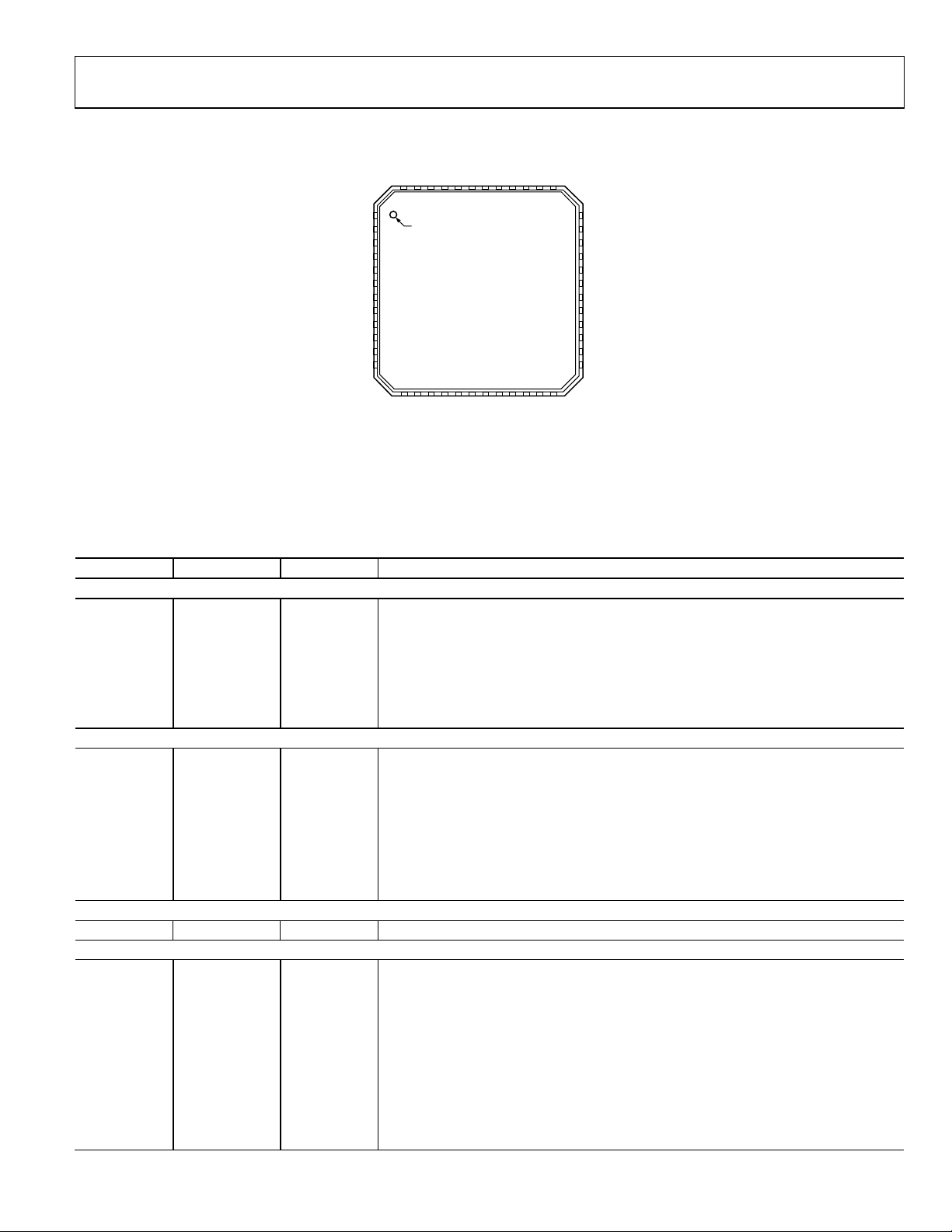

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

PDWN

RBIAS

VCM

AVDD

LVDS

VIN–

VIN+

LVDS_RS

DNC

DNC

VREF

4847464544434241403938

SENSE

37

D11

AVDD36

35

DITHER

34

AVDD

33

SVDD

32

CSB

31

SCLK/DFS

30

SDIO/DCS

29

DRVDD

28

DNC

27

OR

26

D13 (MSB)

25

D12

08505-003

SYNC

1

CLK+

2

CLK–

3

AVDD

4

AVDD

5

OEB

6

DNC

7

DCO

8

DNC

9

DNC

10

D0 (LSB)

11

D1

12

NOTES

1. DNC = DO NOT CONNECT.

2. THE EXPOSED THERM AL P AD ON THE BOTTOM OF THE PACKAGE

PROVIDES T HE ANALOG GRO UND F OR THE INPUT. THIS EXPOSED

PAD MUST BE CONNECTED TO GROUND FOR PROPE R OPERATIO N.

PIN 1

INDICATOR

AD9255

PARALLEL

CMOS

TOP VIEW

(Not to S cale)

13141516171819

D2D3D4D5D6

DRVDD

2021222324

D7

D8

DRVDD

D9

D10

Figure 4. LFCSP Parallel CMOS Pin Configuration (Top View)

Table 8. Pin Function Descriptions (Parallel CMOS Mode)

Pin No. Mnemonic Type Description

ADC Power Supplies

13, 20, 29 DRVDD Supply Digital Output Driver Supply (1.8 V Nominal).

4, 5, 34, 36, 45 AVDD Supply Analog Power Supply (1.8 V Nominal).

33 SVDD Supply SPI Input/Output Voltage

7, 9, 10, 28, 39, 40 DNC Do Not Connect.

0 AGND Ground

Analog Ground. The exposed thermal pad on the bottom of the package provides

the analog ground for the input. This exposed pad must be connected to ground for

proper operation.

ADC Analog

42 VIN+ Input Differential Analog Input Pin (+).

43 VIN− Input Differential Analog Input Pin (−).

38 VREF Input/output Voltage Reference Input/Output.

37 SENSE Input Voltage Reference Mode Select. See Ta ble 11 for details.

47 RBIAS Input/output External Reference Bias Resistor.

46 VCM Output Common-Mode Level Bias Output for Analog Inputs.

2 CLK+ Input ADC Clock Input—True.

3 CLK− Input ADC Clock Input—Complement.

Digital Input

1 SYNC Input Digital Synchronization Pin. Slave mode only.

Digital Outputs

11 D0 (LSB) Output CMOS Output Data.

12 D1 Output CMOS Output Data.

14 D2 Output CMOS Output Data.

15 D3 Output CMOS Output Data.

16 D4 Output CMOS Output Data.

17 D5 Output CMOS Output Data.

18 D6 Output CMOS Output Data.

19 D7 Output CMOS Output Data.

21 D8 Output CMOS Output Data.

Rev. A | Page 11 of 44

AD9255

Pin No. Mnemonic Type Description

22 D9 Output CMOS Output Data.

23 D10 Output CMOS Output Data.

24 D11 Output CMOS Output Data.

25 D12 Output CMOS Output Data.

26 D13 (MSB) Output CMOS Output Data.

27 OR Output Overrange Output.

8 DCO Output Data Clock Output.

SPI Control

31 SCLK/DFS Input SPI Serial Clock/Data Format Select Pin in External Pin Mode.

30 SDIO/DCS Input/output SPI Serial Data I/O/Duty Cycle Stabilizer Pin in External Pin Mode.

32 CSB Input SPI Chip Select (Active Low).

ADC Configuration

6 OEB Input Output Enable Input (Active Low).

35 DITHER Input

41 LVDS_RS Input

44 LVDS Input

48 PDWN Input

In external pin mode, this pin sets dither to on (active high). Pull low for control via

SPI in SPI mode.

In external pin mode, this pin sets LVDS reduced swing output mode (active high).

Pull low for control via SPI in SPI mode.

In external pin mode, this pin sets LVDS output mode (active high). Pull low for

control via SPI in SPI mode.

Power-down input in external pin mode. In SPI mode, this input can be configured

as power-down or standby.

Rev. A | Page 12 of 44

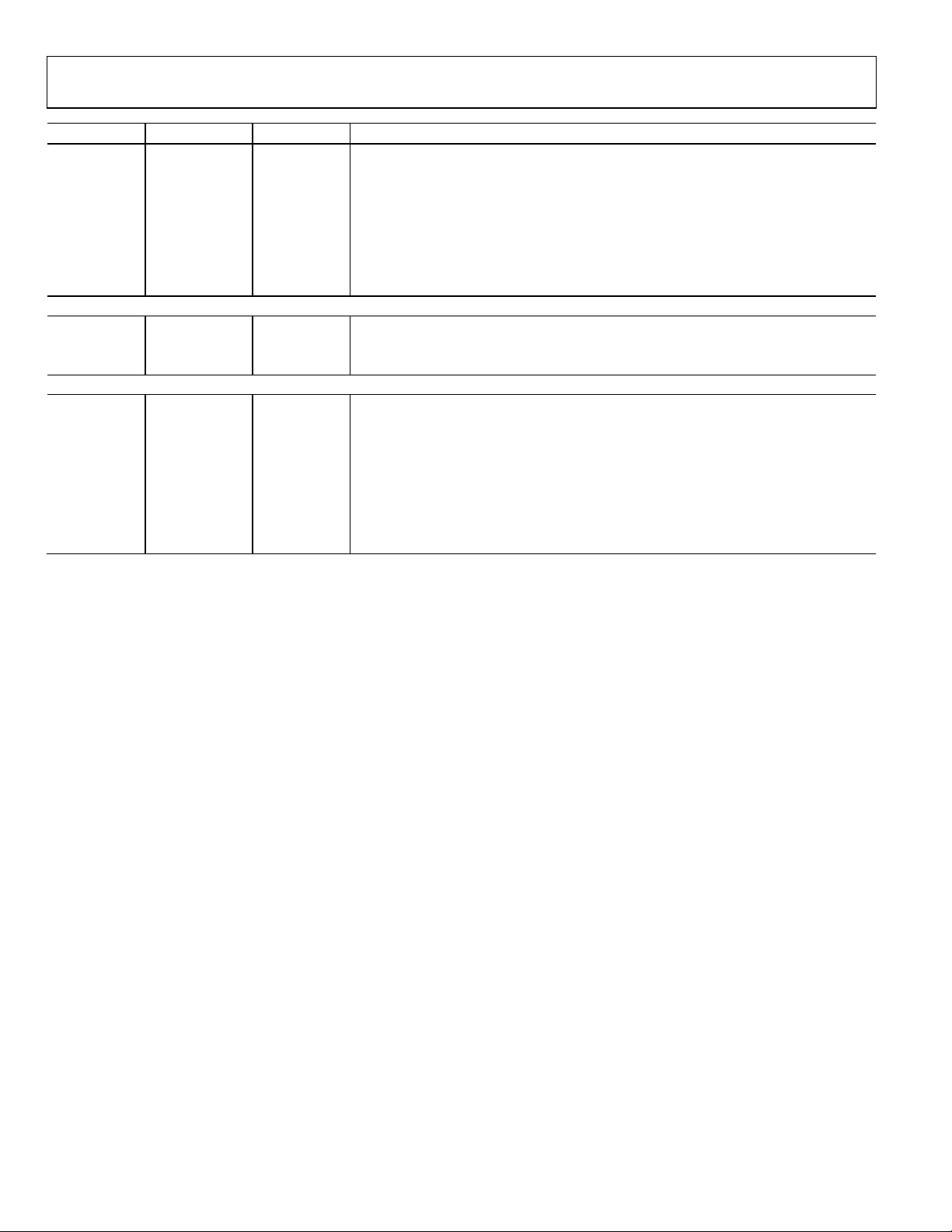

AD9255

PDWN

RBIAS

VCM

AVDD

LVDS

VIN–

VIN+

LVDS_RS

DNC

DNC

VREF

4847464544434241403938

SENSE

37

D10/11+

AVDD36

35

DITHER

34

AVDD

33

SVDD

32

CSB

31

SCLK/DFS

30

SDIO/DCS

29

DRVDD

28

OR+

27

OR–

26

D12/13+

25

D12/13–

08505-004

SYNC

1

CLK+

2

CLK–

3

AVDD

4

AVDD

5

OEB

6

DCO–

7

DCO+

8

DNC

9

DNC

10

D0/1–

11

D0/1+

12

NOTES

1. DNC = DO NOT CONNECT.

2. THE EXPOSED THE RM AL PAD ON THE BOTTOM O F THE PACKAGE

PROVIDES T HE ANALOG GRO UND F OR THE PART. THIS EXPOSED PAD

MUST BE CONNECT E D TO GROUND FOR PROPER O PE RATION.

PIN 1

INDICATOR

AD9255

INTERLEAVED

LVDS

TOP VIEW

(Not to S cale)

13141516171819

D2/3–

D4/5–

D6/7–

D2/3+

DRVDD

D4/5+

2021222324

D8/9–

D6/7+

DRVDD

D8/9+

D10/11–

Figure 5. LFCSP Interleaved Parallel LVDS Pin Configuration (Top View)

Table 9. Pin Function Descriptions (Interleaved Parallel LVDS Mode)

Pin No. Mnemonic Type Description

ADC Power Supplies

13, 20, 29 DRVDD Supply Digital Output Driver Supply (1.8 V Nominal).

4, 5, 34, 36, 45 AVDD Supply Analog Power Supply (1.8 V Nominal).

33 SVDD Supply SPI Input/Output Voltage.

9, 10, 39, 40 DNC Do Not Connect.

0 AGND Ground

Analog Ground. The exposed thermal pad on the bottom of the package provides the

analog ground for the input. This exposed pad must be connected to ground for proper

operation.

ADC Analog

42 VIN+ Input Differential Analog Input Pin (+).

43 VIN− Input Differential Analog Input Pin (−).

38 VREF Input/output Voltage Reference Input/Output.

37 SENSE Input Voltage Reference Mode Select. See Table 11 for details.

47 RBIAS Input/output External Reference Bias Resistor.

46 VCM Output Common-Mode Level Bias Output for Analog Inputs.

2 CLK+ Input ADC Clock Input—True.

3 CLK− Input ADC Clock Input—Complement.

Digital Input

1 SYNC Input Digital Synchronization Pin. Slave mode only.

Digital Outputs

12 D0/1+ Output LVDS Output Data Bit 0/Bit 1 (LSB)—True.

11 D0/1− Output LVDS Output Data Bit 0/Bit 1 (LSB)—Complement.

15 D2/3+ Output LVDS Output Data Bit 2/Bit 3—True.

14 D2/3− Output LVDS Output Data Bit 2/Bit 3—Complement.

17 D4/5+ Output LVDS Output Data Bit 4/Bit 5—True.

16 D4/5− Output LVDS Output Data Bit 4/Bit 5—Complement.

19 D6/7+ Output LVDS Output Data Bit 6/Bit 7—True.

18 D6/7− Output LVDS Output Data Bit 6/Bit 7—Complement.

22 D8/9+ Output LVDS Output Data Bit 8/Bit 9 —True.

21 D8/9− Output LVDS Output Data Bit 8/Bit 9—Complement.

Rev. A | Page 13 of 44

AD9255

Pin No. Mnemonic Type Description

24 D10/11+ Output LVDS Output Data Bit 10/Bit 11—True.

23 D10/11− Output LVDS Output Data Bit 10/Bit 11—Complement.

26 D12/13+ (MSB) Output LVDS Output Data Bit 12/Bit 13—True.

25 D12/13− (MSB) Output LVDS Output Data Bit 12/Bit 13—Complement.

28 OR+ Output LVDS Overrange Output—True.

27 OR− Output LVDS Overrange Output—Complement.

8 DCO+ Output LVDS Data Clock Output—True.

7 DCO− Output LVDS Data Clock Output—Complement.

SPI Control

31 SCLK/DFS Input SPI Serial Clock/Data Format Select Pin in External Pin Mode.

30 SDIO/DCS Input/output SPI Serial Data I/O/Duty Cycle Stabilizer Pin in External Pin Mode.

32 CSB Input SPI Chip Select (Active Low).

ADC Configuration

6 OEB Input Output Enable Input (Active Low).

35 DITHER Input

41 LVDS_RS Input

44 LVDS Input

48 PDWN Input

In external pin mode, this pin sets dither to on (active high). Pull low for control via SPI

in the SPI mode.

In external pin mode, this pin sets LVDS reduced swing output mode (active high). Pull

low for control via SPI in the SPI mode.

In external pin mode, this pin sets LVDS output mode (active high). Pull low for control

via SPI in the SPI mode.

Power-Down Input in External Pin Mode. In SPI mode, this input can be configured as

power-down or standby.

Rev. A | Page 14 of 44

Loading...

Loading...