10-Bit, 40 MSPS, 3 V, 74 mW

Automotive Product

FEATURES

CMOS 10-bit, 40 MSPS sampling analog-to-digital converter

Power dissipation: 74 mW (3 V supply, 40 MSPS)

17 mW (3 V supply, 5 MSPS)

Operation between 2.7 V and 3.6 V supply

Differential nonlinearity: −0.25 LSB

Power-down (standby) mode: 0.65 mW

ENOB: 9.55 at f

Out-of-range indicator

Adjustable on-chip voltage reference

IF undersampling up to f

Input range: 1 V to 2 V p-p differential or single-ended

Adjustable power consumption

Internal clamp circuit

Qualified for automotive applications

APPLICATIONS

Automotive

GENERAL DESCRIPTION

The AD9203W is a monolithic low power, single supply, 10-bit,

40 MSPS analog-to-digital converter, with an on-chip voltage

reference. The AD9203W uses a multistage differential pipeline

architecture and guarantees no missing codes over the full

operating temperature range. Its input range may be adjusted

between 1 V and 2 V p-p.

The AD9203W has an onboard programmable reference. An

external reference can also be chosen to suit the dc accuracy

and temperature drift requirements of an application.

An external resistor can be used to reduce power consumption

when operating at lower sampling rates. This yields power

savings for users who do not require the maximum sample

rate. This feature is especially useful at sample rates far below

40 MSPS. Excellent performance is still achieved at reduced

power. For example, 9.7 ENOB performance may be realized

with only 17 mW of power, using a 5 MHz clock.

A single clock input is used to control all internal conversion

cycles. The digital output data is presented in straight binary or

twos complementary output format by using the DFS pin. An

out-of-range signal (OTR) indicates an overflow condition that

= 20 MHz

IN

= 130 MHz

IN

Analog-to-Digital Converter

AD9203W

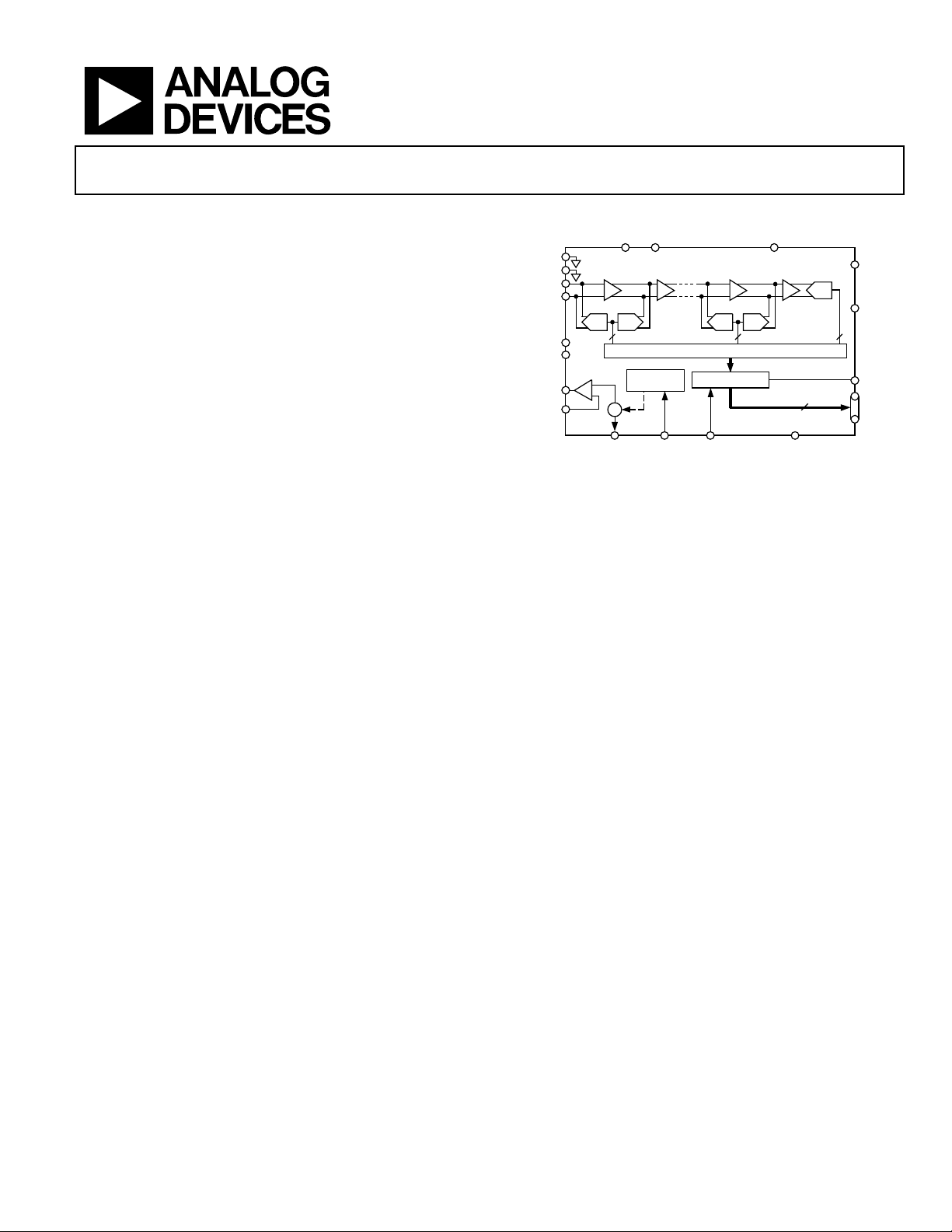

FUNCTIONAL BLOCK DIAGRAM

CLKAVDD DRVDD

CLAMP

CLAMPIN

AINP

AINN

REFTF

REFBF

VREF

REFSENSE

SHA GAIN

A/D D/A

REFERENCE

+

–

0.5V

BANDGAP

SHA GAIN

A/D D/A

CORRECTION LOG IC

OUTPUT BUFFERS

Figure 1.

can be used with the most significant bit to determine over- or

underrange.

The AD9203W can operate with a supply range from 2.7 V to

3.6 V, an attractive option for low power operation in high

speed portable applications.

The AD9203W is specified over industrial (−40°C to +85°C)

temperature ranges and is available in a 28-lead TSSOP package.

PRODUCT HIGHLIGHTS

1. Low Power. The AD9203W consumes 74 mW on a 3 V

supply operating at 40 MSPS. In standby mode, power is

reduced to 0.65 mW.

2. High Performance. Maintains better than 9.55 ENOB at

40 MSPS input signal from dc to Nyquist.

3. Ver y Sm a ll P a cka g e . T h e AD9203W is available in a

28-lead TSSOP.

4. Programmable Power. The AD9203W power can be

further reduced by using an external resistor at lower

sample rates.

5. Built-In Clamp Function. Allows dc restoration of video

signals.

AD9203W

10

DRVSSDFSPWRCONAVSS

STBY

A/D

3-STATE

OTR

D9 (MSB)

D0 (LSB)

10258-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

AD9203W Automotive Product

TABLE OF CONTENTS

Features .............................................................................................. 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 5

REVISION HISTORY

10/11—Revision 0: Initial Version

Thermal Characteristics ...............................................................5

ESD Caution...................................................................................5

Pin Configuration and Function Descriptions ..............................6

Outline Dimensions ..........................................................................7

Ordering Guide .............................................................................7

Rev. 0 | Page 2 of 8

Automotive Product AD9203W

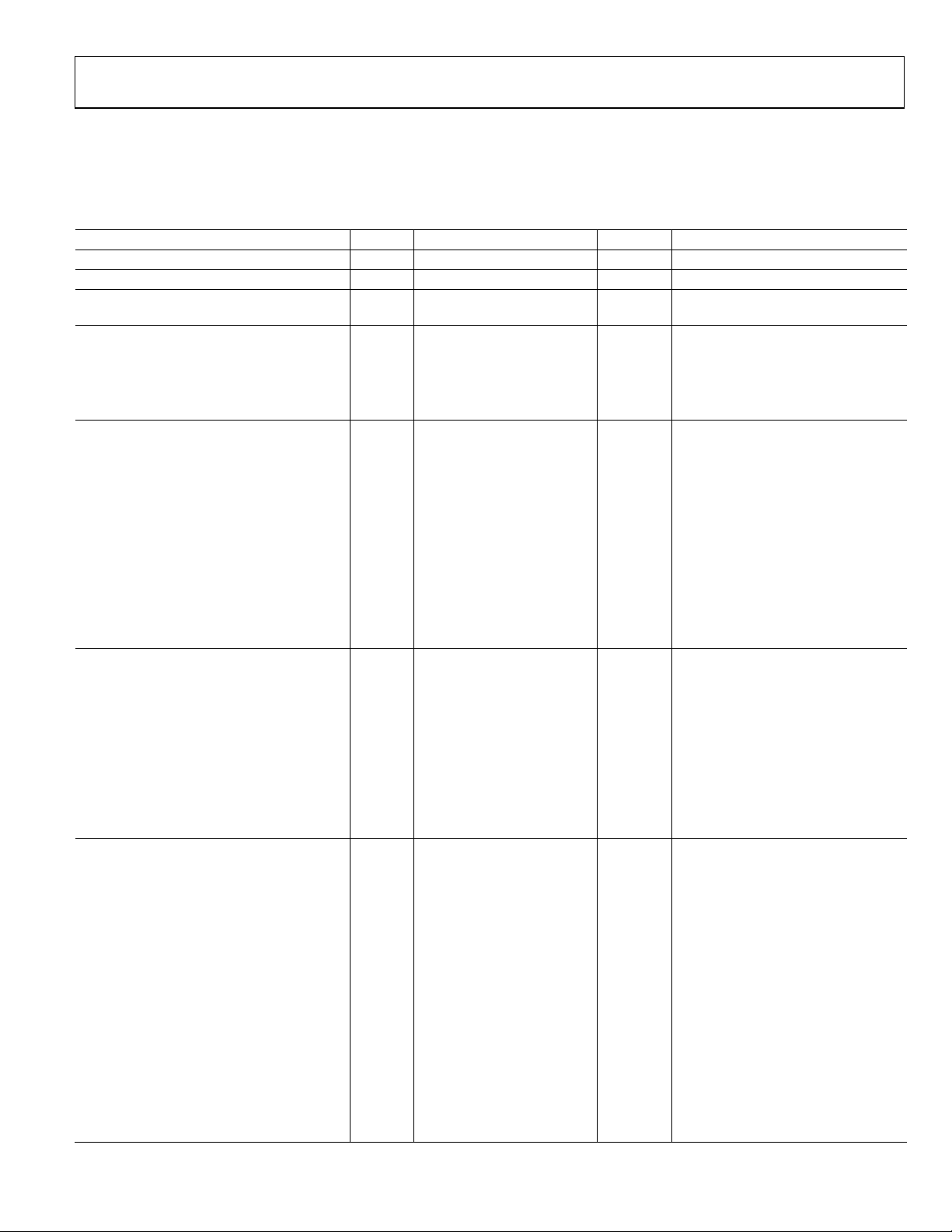

SPECIFICATIONS

AVDD = 3 V, DRVDD = 3 V, FS = 40 MSPS, input span from 0.5 V to 2.5 V, internal 1 V reference, PWRCON = AVDD, 50% clock duty

MIN

to T

cycle, T

Table 1.

Parameter Symbol Min Typ Max Unit Conditions

RESOLUTION 10 Bits

MAX CONVERSION RATE FS 40 MSPS

PIPELINE DELAY 5.5

DC ACCURACY

Differential Nonlinearity DNL ±0.25 ±0.7 LSB

Integral Nonlinearity INL ±0.65 ±1.4 LSB

Offset Error EZS ±0.6 ±2.8 % FSR

Gain Error EFS ±0.7 ±4.0 % FSR

ANALOG INPUT

Input Voltage Range AIN 1 2 V p-p

Input Capacitance CIN 1.4 pF

Aperture Delay TAP 2.0 ns

Aperture Uncertainty (Jitter) TAJ 1.2 ps rms

Input Bandwidth (–3 dB) BW 390 MHz

Input Referred Noise 0.3 mV Switched, single-ended

INTERNAL REFERENCE

Output Voltage (0.5 V Mode) VREF 0.5 V REFSENSE = VREF

Output Voltage (1 V Mode) VREF 1 V REFSENSE = GND

Output Voltage Tolerance (1 V Mode) ± 5 ± 30 mV

Load Regulation 0.65 1.2 mV 1.0 mA load

POWER SUPPLY

Operating Voltage AVDD 2.7 3.0 3.6 V

DRVDD 2.7 3.0 3.6 V

Analog Supply Current IAVDD 20.1 22.0 mA

Digital Supply Current IDRVDD 4.4 6.0 mA f

9.5 14.0 mA f

Power Consumption 74 84.0 mW f

88.8 108.0 mW f

Power-Down PD 0.65 1.2 mW

Power Supply Rejection Ratio PSRR 0.04 ± 0.25 % FSR

DYNAMIC PERFORMANCE (AIN = 0.5 dBFS)

Signal-to-Noise and Distortion1 SINAD

f = 4.8 MHz 59.7 dB

f = 20 MHz 57.2 59.3 dB

Effective Bits ENOB

f = 4.8 MHz1 9.6 Bits

f = 20 MHz 9.2 9.55 Bits

Signal-to-Noise Ratio SNR

f = 4.8 MHz1 60.0 dB

f = 20 MHz 57.5 59.5 dB

Total Harmonic Distortion THD

f = 4.8MHz −76.0 dB

f = 20 MHz −74.0 −65.0 dB

Spurious-Free Dynamic Range SFDR

f = 4.8 MHz1 80 dB

f = 20 MHz 67.8 78 dB

unless otherwise noted.

MAX

Clock

Cycles

= 4.8 MHz, output bus load = 10 pF

IN

= 20 MHz, output bus load = 20 pF

IN

= 4.8 MHz, output bus load = 10pF

IN

= 20 MHz, output bus load = 20 pF

IN

Rev. 0 | Page 3 of 8

AD9203W Automotive Product

Parameter Symbol Min Typ Max Unit Conditions

Two-Tone Intermodulation Distortion IMD 68 dB f = 44.49 MHz and 45.52 MHz

Differential Phase DP 0.2 Degree NTSC 40 IRE ramp

Differential Gain DG 0.3 %

DIGITAL INPUTS

High Input Voltage VIH 2.0 V

Low Input Voltage V

Clock Pulse Width High 11.25 ns

Clock Pulse Width Low 11.25 ns

Clock Period2 25 ns

DIGITAL OUTPUTS

High-Z Leakage I

Data Valid Delay t

Data Enable Delay t

Data High-Z Delay t

LOGIC OUTPUT (with DRVDD = 3 V)

High Level Output Voltage (IOH = 50 μA) V

High Level Output Voltage (IOH = 0.5 mA) VOH 2.80 V

Low Level Output Voltage (IOL= 1.6 mA) VOL 0.3 V

Low Level Output Voltage (IOL= 50 μA) V

1

Differential Input (2 V p-p).

2

The AD9203W converts at clock rates as low as 20 kHz.

ANALOG

INPUT

0.4 V

IL

± 5.0 μA Output = 0 to DRVDD

OZ

5 ns CL = 20 pF

OD

6 ns CL = 20 pF

DEN

6 ns CL = 20 pF

DHZ

2.95 V

OH

0.05 V

OL

N+1

N

N–1

N+2

N+3

N+4

N+5

N+6

CLOCK

DATA

OUT

N–7N–6N–5N–4

=3ns MIN

T

OD

Figure 2. Timing Diagram

N–3 N–2 N–1 N N+1

7ns MAX

(C

= 20pF)

LOAD

10258-002

Rev. 0 | Page 4 of 8

Automotive Product AD9203W

ABSOLUTE MAXIMUM RATINGS

Table 2.

With

Parameter

AVDD AVSS –0.3 to +3.9 V

DRVDD DRVSS –0.3 to +3.9 V

AVSS DRVSS –0.3 to +0.3 V

AVDD DRVDD –3.9 to +3.9 V

REFCOM AVSS –0.3 to +0.3 V

CLK AVSS –0.3 to AVDD + 0.3 V

Digital Outputs DRVSS –0.3 to DRVDD + 0.3 V

AINP AINN AVSS – 0.3 to AVDD + 0.3 V

VREF AVSS –0.3 to AVDD + 0.3 V

REFSENSE AVSS –0.3 to AVDD + 0.3 V

REFTF, REFBF AVSS –0.3 to AVDD + 0.3 V

STBY AVSS –0.3 to AVDD + 0.3 V

CLAMP AVSS –0.3 to AVDD + 0.3 V

CLAMPIN AVSS –0.3 to AVDD + 0.3 V

PWRCON AVSS –0.3 to AVDD + 0.3 V

DFS AVSS –0.3 to AVDD + 0.3 V

3-STATE AVSS –0.3 to AVDD + 0.3 V

Junction

Temperature

Storage

Temperature

Lead

Temperature

(10 s)

Respect to

150 °C

+150 °C

300 °C

Rating Unit

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL CHARACTERISTICS

28-Lead TSSOP

J

= 97.9°C/W

A

= 14.0°C/W

J

C

ESD CAUTION

Rev. 0 | Page 5 of 8

AD9203W Automotive Product

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

DRVSS

2

DRVDD

OTR

DFS

D1

D2

D3

D4

D5

D6

D7

D8

3

4

5

6

AD9203W

7

TOP VIEW

8

(Not to Scale)

9

10

11

12

13

14

(LSB) D0

(MSB) D9

Figure 3. Pin Configuration

Table 3. Pin Function Descriptions

Pin Name Description

1 DRVSS Digital Ground.

2 DRVDD Digital Supply.

3 D0 Bit 0, Least Significant Bit.

4 D1 Bit 1.

5 D2 Bit 2.

6 D3 Bit 3.

7 D4 Bit 4.

8 D5 Bit 5.

9 D6 Bit 6.

10 D7 Bit 7.

11 D8 Bit 8.

12 D9 Bit 9, Most Significant Bit.

13 OTR Out-of-Range Indicator.

14 DFS Data Format Select HI: Twos Complement; LO: Straight Binary.

15 CLK Clock Input.

16 3-STATE HI: High Impedance State Output; LO: Active Digital Output Drives.

17 STBY HI: Power-Down Mode; LO: Normal Operation.

18 REFSENSE Reference Select.

19 CLAMP HI: Enable Clamp; LO: Open Clamp.

20 CLAMPIN Clamp Signal Input.

21 PWRCON Power Control Input.

22 REFTF Top Reference Decoupling.

23 VREF Reference In/Out.

24 REFBF Bottom Reference Decoupling.

25 AINP Noninverting Analog Input.

26 AINN Inverting Analog Input.

27 AVSS Analog Ground.

28 AVDD Analog Supply.

AVDD

28

AVSS

27

AINN

26

AINP

25

REFBF

24

VREF

23

REFTF

22

PWRCON

21

CLAMPIN

20

CLAMP

19

REFSENSE

18

STBY

17

3-STATE

16

CLK

15

10258-003

Rev. 0 | Page 6 of 8

Automotive Product AD9203W

C

Y

OUTLINE DIMENSIONS

9.80

9.70

9.60

28

PIN 1

0.65

0.15

0.05

OPLANARIT

0.10

BSC

0.30

0.19

COMPLIANT TO JEDEC STANDARDS MO-153-AE

Figure 4. 28-Lead Thin Shrink Small Outline Package [TSSOP]

1.20 MAX

SEATING

PLANE

15

4.50

4.40

4.30

0.20

0.09

6.40 BSC

8°

0°

0.75

0.60

0.45

141

(RU-28)

Dimensions shown in millimeters

ORDERING GUIDE

1, 2

Model

AD9203WARUZ

AD9203WARUZRL7

1

Z = RoHS Compliant Part.

2

W = Qualified for Automotive Applications.

Temperature Range Package Description Package Option

−40°C to +85°C 28-Lead Thin Shrink Small Outline [TSSOP] RU-28

−40°C to +85°C 28-Lead Thin Shrink Small Outline [TSSOP] RU-28

AUTOMOTIVE PRODUCTS

The AD9203W models are available with controlled manufacturing to support the quality and reliability requirements of automotive

applications. Note that these automotive models may have specifications that differ from the commercial models; therefore, designers

should review the Specifications section of this data sheet carefully. Only the automotive grade products shown are available for use in

automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to

obtain the specific Automotive Reliability reports for these models.

Rev. 0 | Page 7 of 8

AD9203W Automotive Product

NOTES

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D10258-0-10/11(0)

Rev. 0 | Page 8 of 8

Loading...

Loading...