Complete 12-Bit 10 MSPS

a

SMD/883B

Scope

This specification covers the detail requirements for a complete monolithic 12-bit, 10 MSPS A/D converter with an on-chip, high performance track-and-hold amplifier (THA) and voltage reference. The

electrical specifications match the Standard Microcircuit Drawing (SMD) 5962-93060 in effect at the

release of this data sheet. For a copy of the latest official SMD, contact DESC-ELDS.

Part Number/Case Outline

For case outline dimensions, see Package Information Appendix of General Specification ADI-M-1000.

The complete part numbers of these SMD and 883 devices are as follows:

Device SMD ADI 883B Package Package Designation

Type Part Number Part Number Description ADI MIL-STD-1835

01 5962-9306001MXA AD872ASD/883B 28-Pin Side Brazed DIP D-28 CDIP2-T28

02 5962-9306002MYA AD872ASE/883B 44-Terminal LCC E-44A CQCCI-N44

Absolute Maximum Ratings

AV

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to +6.5 V

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −6.5 V to +0.5 V

AV

SS

DRV

DV

DD,

DRV

DD to DVDD

DRGND to DGND

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −1 V to +1 V

to DVDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −6.5 V to +6.5 V

AV

DD

Clock Input, OEN

Digital Outputs to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to DV

REF IN to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .AV

V

, to V

INA

Storage Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −65°C to +150°C

Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +300°C

2

to DGND, DRGND2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to +6.5 V

DD

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −6.5 V to +6.5 V

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.3 V to +0.3 V

2

to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to DVDD + 0.5 V

, REF IN to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −6.5 V to +6.5 V

INB

(TA = +25°C unless otherwise noted)

Monolithic A/D Converter

AD872A

1

+ 0.3 V

DD

to AV

SS

DD

Recommended Operating Conditions

2

Operating Ambient Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

Thermal Characteristics

Thermal Resistance, Junction-to-Case (θJC) for D-28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28°C/W

Thermal Resistance, Junction-to-Ambient (θ

Thermal Resistance, Junction-to-Case (θ

Thermal Resistance, Junction-to-Ambient (θ

NOTES

1

Permanent damage may occur if any absolute maximum rating is exceeded. Functional operation is not implied and device

reliability may be impaired by exposure to higher-than-recommended voltages for extended periods of time.

2

Device Type 02 only.

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for

its use, nor for any infringements of patents or other rights of third

parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

) for D-28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60°C/W

JA

) for E-44A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20°C/W

JC

) for E-44A . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70°C/W

JA

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1997

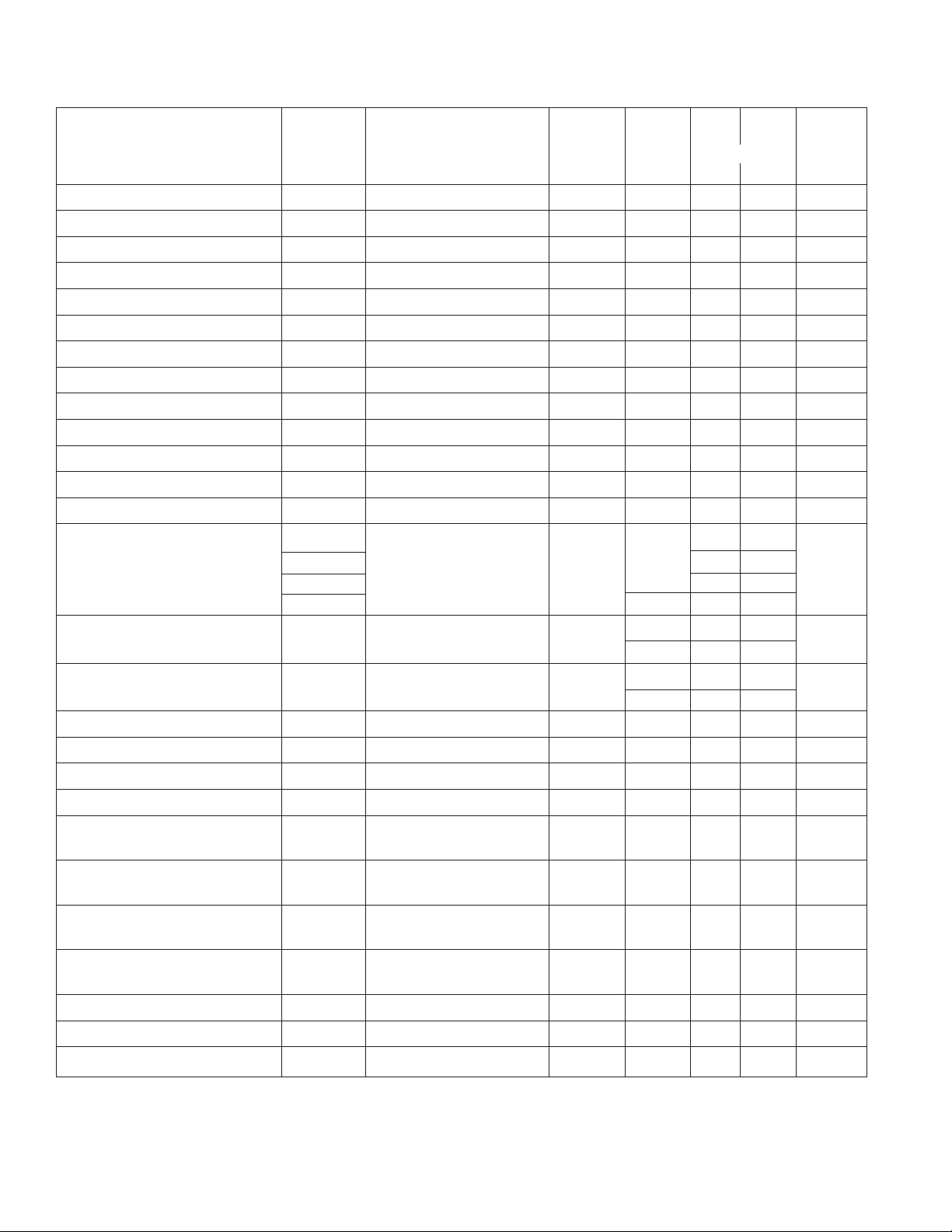

AD872A–SPECIFICA TIONS

Table 1. Electrical Performance Characteristics

Conditions

= +5 V, AVSS = –5 V,

AV

DD

= +5 V, DRVDD = +5 V Group A Device Limits

DV

DD

Test Symbol unless otherwise specified Subgroups Type Min Max Units

Resolution RES 1, 2, 3 01, 02 12 Bits

Differential Nonlinearity

Zero Error B

Gain Error A

Zero Error Drift TCB

Gain Error Drift TCA

Gain Error Drift TCA

Power Supply Rejection PSR See Note 2 1, 2, 3 01, 02 0.125 ±% FSR

Analog Input Range V

Input Resistance R

Input Capacitance C

Internal Reference Output Voltage V

Power Dissipation PD 1, 2, 3 01, 02 1.3 W

1

DNL All Codes Histogram 1, 2, 3 01, 02 12 Bits

POE

E

IN

IN

IN

REF

POE

INT

EXT

External 2.5 V Reference 2, 3 01, 02 0.30 ±% FSR

Internal 2.5 V Reference 2, 3 01, 02 1.75 ± % FSR

External 2.5 V Reference 2, 3 01, 02 0.5 ±% FSR

TA = +25°C 01, 02 50 typ kΩ

TA = +25°C 01, 02 10 typ pF

1 01, 02 0.75 ±% FSR

1 01, 02 1.25 ±% FSR

1, 2, 3 01, 02 1 ±V

1, 2, 3 01, 02 2.46 2.54 V

Power Supply Current IAV

DD

IAV

SS

IDV

IDRV

DD

DD

Signal-to-Noise and Distortion Ratio S/(N + D) f

Total Harmonic Distortion THD f

Logic Input High Voltage V

Logic Input Low Voltage V

Logic Input High Current (CLK) I

Logic Input Low Current (CLK) I

IH

IL

IH

IL

Logic Input High Current

(OEN, CLK) I

IH

Logic Input Low Current

(OEN, CLK) I

IL

Logic Output High Voltage

(MSB—Bit 12, OTR) V

OH

Logic Output Low Voltage

(MSB—Bit 12, OTR) V

Leakage I

Clock Period t

Output Delay t

OL

Z

C

OD

1, 2, 3 01, 02 92 mA

150

21

02 2

= 1 MHz; fS = 10 MHz 1, 2, 3 01 61 dB

IN

02 60

= 1 MHz; fS = 10 MHz 1, 2, 3 01 –62 dB

IN

02 –60

1, 2, 3 01, 02 2.0 V

1, 2, 3 01, 02 0.8 V

1, 2, 3 01 115 ±µA

1, 2, 3 01 115 ±µA

1, 2, 3 02 115 ±µA

1, 2, 3 02 115 ±µA

I

= 500 µA 1, 2, 3 01, 02 2.4 V

SOURCE

I

= 1.6 mA 1, 2, 3 01, 02 0.4 V

SINK

Three State 1, 2, 3 02 10 ±µA

See Figure 1. 9, 10, 11 01, 02 100 ns

See Figure 1. 9, 10, 11 01, 02 10 ns

NOTES

1

Minimum resolution for which “No Missing Codes” is guaranteed.

2

Test conditions for PSR: 4.75 V ≤ AVDD ≤ 5.25 V, –5.25 V ≤ AVSS ≤ –4.75 V, 4.75 V ≤ DVDD ≤ 5.25 V.

–2–

REV. B

SMD/883B

Functional Block Diagram and Terminal Assignment

AD872A

V

INA

V

INB

AV

AV

AGND

DGND

DV

(LSB) BIT 12

BIT 11

BIT 10

BIT 9

BIT 8

BIT 7

BIT 6

DV

SS

DACA/D

CORRECTION LOGIC

DGNDAV

DD

T/H A/D

OUTPUT BUFFERS

*MSBOTR

*DRV

AD872A

A/D

DAC

MSB-BIT 12 (LSB)

DD

*DRGND

12

V

INA

V

INB

CLOCK

REF IN

REF OUT

AV

AGND

DD

T/HT/H

A/D

DAC

4434

+2.5V

REFERENCE

REF GND

*ONLY AVAILABLE ON 44-PIN SURFACE MOUNT PACKAGE

*OUTPUT

ENABLE

D-28 Package E-44A Package

1

2

3

SS

4

DD

5

6

AD872A

7

TOP VIEW

DD

(Not to Scale)

8

9

10

11

12

13

14

NC = NO CONNECT

28

REF IN

27

REF GND

26

REF OUT

25

AV

24

AGND

23

DGND

22

DV

21

CLK

20

OTR

19

BIT 1 (MSB)

18

BIT 2

17

BIT 3

16

BIT 4

15

BIT 5

INA

(Not to Scale)

BIT 9

BIT 8

INB

V

AD872A

TOP VIEW

BIT 7

BIT 5

BIT 6

AVDDAVSSNCNCV

6 5 4 3 2 1 44 43 42 41 40

7

NC

8

SS

DD

NC

AGND

DGND

DRGND

DRV

DD

OEN

NC

NC

(MSB) BIT 12

BIT 11

NC = NO CONNECT

9

10

11

12

13

14

15

16

17

18 19 20 21 22 23 24 25 26 27 28

BIT 10

NC

REF IN

REF GND

PIN 1

IDENTIFIER

BIT 4

BIT 3

BIT 2

SS

REF OUT

AV

39

NC

38

AV

37

NC

36

AGND

35

NC

34

DRGND

33

DV

DRV

32

31

CLK

QTR

30

29

MSB

NC

( MSB) BIT 1

DD

DD

DD

CLOCK

BIT 2–12

MSB, OTR

REV. B

N

V

IN

N+1

t

C

t

CL

t

CH

DATA

IN

DATA

N+1

t

OD

Figure 1. Timing Diagram

SWITCHING SPECIFICATIONS

(

T

to T

MIN

with AVDD = +5 V, DVDD = +5 V, DRVDD =

MAX

+5 V, AVSS = –5 V; VIL = 0.8 V, VIH = 2.0 V. These characteristics

are included for design guidance only and are not tested or guaranteed.)

Parameter Symbol Limits Units

CLOCK Pulse Width High t

CLOCK Pulse Width Low t

CH

CL

45 ns min

45 ns min

Clock Duty Cycle 40 % min (50% typ)

60 % max

Pipeline Delay (Latency) 3 Clock Cycles

–3–

AD872A

Microcircuit Technology Group

This microcircuit is covered by technology group (93).

Life Test /Burn-In Circuit

Steady state life test is per MIL-STD-883 Method 1005. Burn-in is per MIL-STD-883 Method 1015 test

condition (B).

7V rms

–5V

60Hz

7V rms

60Hz

–5V

9kV

47mF 0.1mF

47mF

9kV

1kV

MR-280

0.1mF

1kV

NC

NC

NC

NC

NC

NC

NC

1

V

INA

2

V

INB

3

AV

SS

4

AV

DD

5

AGND

6

DGND

7

DV

DD

8

NC

MR-280

7

8

9

10

11

12

13

14

15

16

17

NC

NC

AGND

DGND

DRGND

DRV

OEN

NC

NC

BIT 12 (MSB)

BIT 11

BIT 12 (LSB)

9

NC

BIT 11

10

NC

BIT 10

11

BIT 9

NC

12

BIT 8

NC

13

NC

BIT 7

14

BIT 6

NC

NC NC

6 5 4 3 2 1 44 43 42 41 40

SS

NC

AVDDAV

DD

NC

AD872A

REF GND

REF OUT

(MSB) BIT 1

NC

INB

INA

V

V

AD872A

REF IN

AV

AGND

DGND

DV

CLK

OTR

BIT 2

BIT 3

BIT 4

BIT 5

NC

SS

DD

REF IN

REF GND

28

27

26

25

24

23

22

21

20

NC

19

NC

18

NC

17

NC

NC

16

NC

15

10mF

REF OUT

SS

AV

NC

AV

NC

AGND

NC

DRGND

DV

DRV

CLK

QTR

MSB

0.1mF

+5V

MR-280

47mF

10mF

C1945a–0–11/97

0-5V

1kHz

+5V

47mF

0.1mF

MR-280

NC

39

38

DD

NC

37

36

35

NC

34

33

DD

32

DD

31

30

NC

29

NC

0-5V

1kHz

0.225 (5.72)

MAX

0.200 (5.08)

0.125 (3.18)

BIT 10

18 19 20 21 22 23 24 25 26 27 28

NC NC NC NC NC NC NC NC NCNC NC

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

D-28

28-Lead Side Brazed DIP

0.100 (2.54) MAX0.005 (0.13) MIN

28

114

PIN 1

1.490 (37.85) MAX

0.026 (0.66)

0.014 (0.36)

0.110 (2.79)

0.090 (2.29)

15

0.070 (1.78)

0.030 (0.76)

0.610 (15.49)

0.500 (12.70)

0.060 (1.52)

0.015 (0.38)

0.150

(3.81)

MIN

SEATING

PLANE

0.620 (15.75)

0.590 (14.99)

0.018 (0.46)

0.008 (0.20)

BIT 9

BIT 8

BIT 7

BIT 6

BIT 5

BIT 2

BIT 1 ( MSB)

NC

BIT 4

BIT 3

NC = NO CONNECT

E-44A

44-Terminal Ceramic Leadless Chip Carrier

0.100 (2.54)

0.064 (1.63)

0.055 (1.40)

0.045 (1.14)

0.050

(1.27)

BSC

40

39

43

44

1

BOTTOM

VIEW

0.662 (16.82)

0.640 (16.27)

0.075 (1.91) REF

SQ

7

27

6

26

0.020 (0.51)

REF x 45°

0.028 (0.71)

0.022 (0.56)

0.040 (1.02)

REF x 45°

3 PLACES

PRINTED IN U.S.A.

REV. B–4–

Loading...

Loading...