Precision, Low Noise, CMOS, Rail-to-Rail,

O

O

O

www.BDTIC.com/ADI

Input/Output Operational Amplifiers

FEATURES

Low offset voltage: 65 μV maximum

Low input bias currents: 1 pA maximum

Low noise: 8 nV/√Hz

Wide bandwidth: 10 MH

High open-loop gain: 1000 V/mV

Unity gain stable

Single-supply operation: 2.7 V to 5.5 V

5-ball WLCSP for single (AD8605) and 8-ball WLCSP for

dual (AD8606)

APPLICATIONS

Photodiode amplification

Battery-powered instrumentation

Multipole filters

Sensors

Barcode scanners

Audio

GENERAL DESCRIPTION

The AD8605, AD8606, and AD86081 are single, dual, and quad

rail-to-rail input and output, single-supply amplifiers. They

feature very low offset voltage, low input voltage and current

noise, and wide signal bandwidth. They use the Analog Devices,

Inc. patented DigiTrim® trimming technique, which achieves

superior precision without laser trimming.

The combination of low offsets, low noise, very low input bias

currents, and high speed makes these amplifiers useful in a

wide variety of applications. Filters, integrators, photodiode

amplifiers, and high impedance sensors all benefit from the

combination of performance features. Audio and other ac

applications benefit from the wide bandwidth and low

distortion. Applications for these amplifiers include optical

control loops, portable and loop-powered instrumentation,

and audio amplification for portable devices.

The AD8605, AD8606, and AD8608 are specified over the

extended industrial temperature range (−40°C to +125°C). The

AD8605 single is available in 5-lead SOT-23 and 5-ball WLCSP

packages. The AD8606 dual is available in an 8-lead MSOP, an

8-ball WLSCP, and a narrow SOIC surface-mounted package.

The AD8608 quad is available in a 14-lead TSSOP package and

a narrow 14-lead SOIC package. The 5-ball and 8-ball WLCSP

offer the smallest available footprint for any surface-mounted

operational amplifier. The WLCSP, SOT-23, MSOP, and TSSOP

versions are available in tape-and-reel only.

1

Protected by U.S. Patent No. 5,969,657; other patents pending.

Rev. I

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

Z

AD8605/AD8606/AD8608

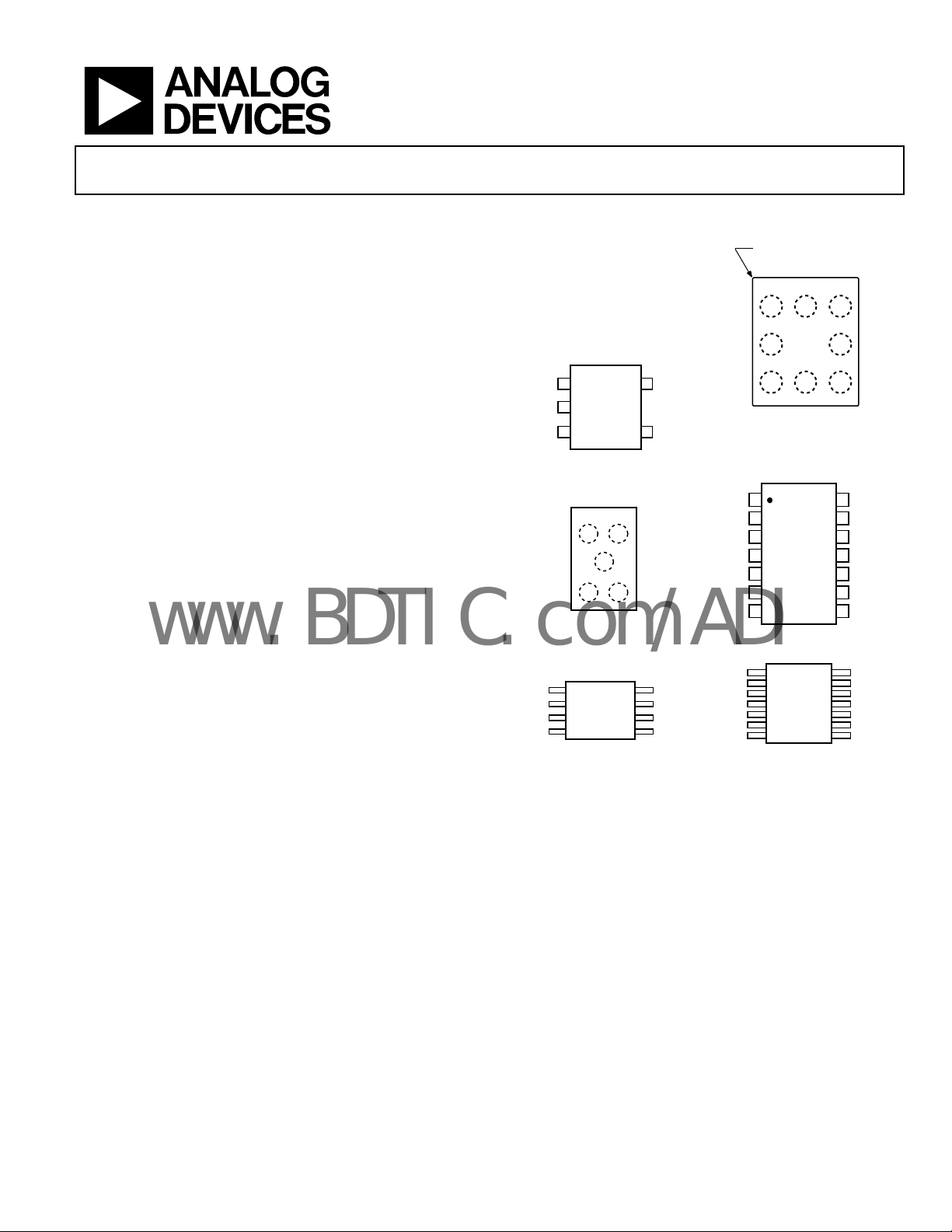

FUNCTIONAL BLOCK DIAGRAMS

BALLA1

CORNER

OUTA V+ OUTB

A1 A2 A3

–INA –INB

B1 B3

+INA V– +INB

–IN A

+IN A

+IN B

–IN B

UT B

–IN A

+IN A

V+

+IN B

–IN B

UT B

V+

C1 C2 C3

AD8606

TOP VIEW

(BALL SIDE DO WN)

1

2

3

AD8608

TOP VIEW

4

(Not to Scal e)

5

6

7

1

(Not to Scale)

7

AD8608

TOP VIEW

14

OUT

+IN

V–

1

AD8605

TOP VIEW

2

(Not to Scale)

3

V+

5

–IN

4

2731-001

Figure 1. 5-Lead SOT-23 (RJ Suffix) Figure 2. 8-Ball WLCSP (CB Suffix)

TOP VIE W

(BUMP SIDE DO WN)

OUT V+

135

V–

2

+IN –IN

4

AD8605 ONLY

02731-006

OUT A

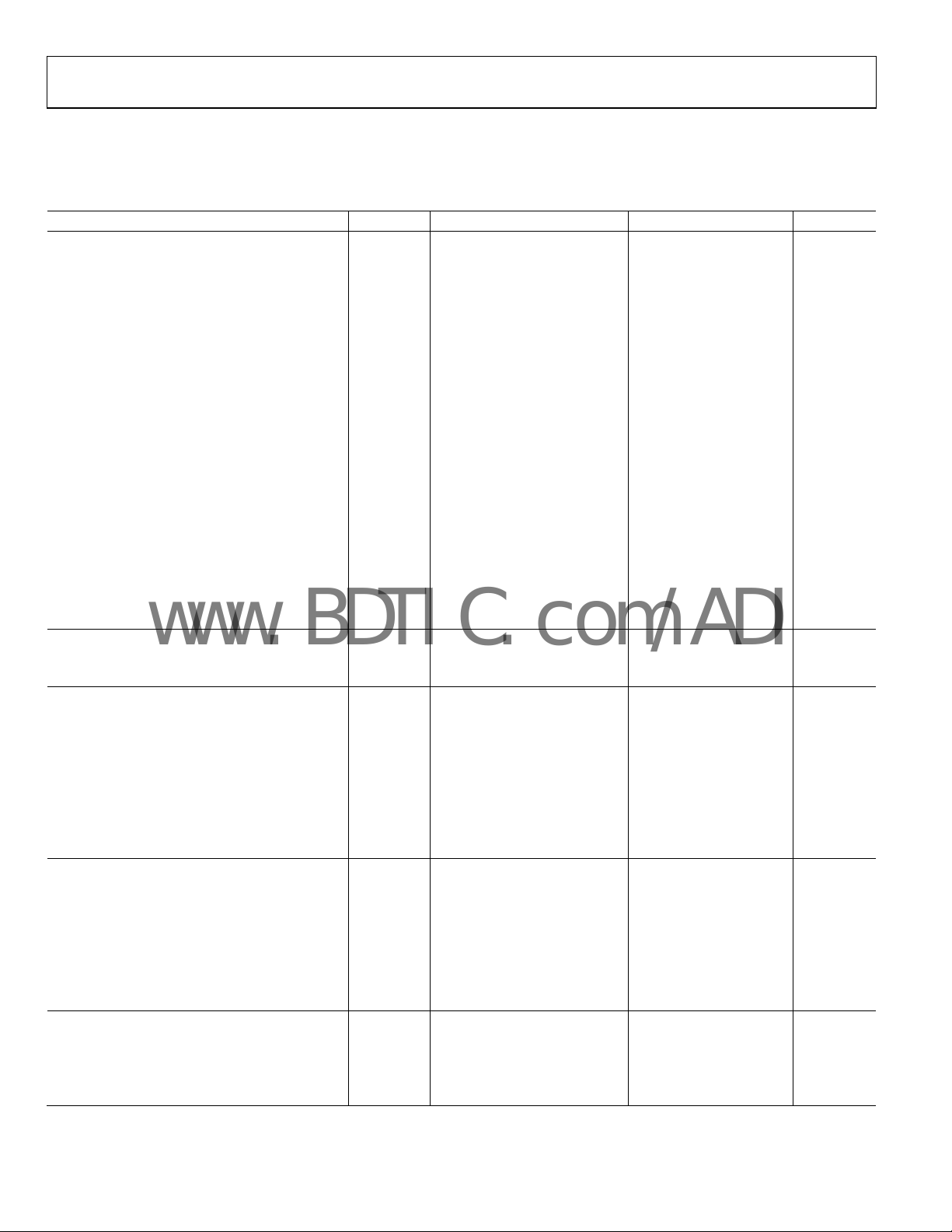

Figure 3. 5-Ball WLCSP (CB Suffix) Figure 4. 14-Lead SOIC_N (R Suffix)

18

UT A

–IN A

+IN A

AD8606

TOP VIEW

(Not to Scale)

45

V–

V+

OUT B

–IN B

+IN B

Figure 5. 8-Lead MSOP (RM Suffix),

OUT A

02731-003

Figure 6. 14-Lead TSSOP (RU Suffix)

8-Lead SOIC_N (R Suffix)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2002–2008 Analog Devices, Inc. All rights reserved.

02731-057

14

OUT D

13

–IN D

12

+IN D

11

V–

10

+IN C

9

–IN C

8

OUT C

02731-004

OUT D

–IN D

+IN D

V–

+IN C

–IN C

8

OUT C

02731-002

AD8605/AD8606/AD8608

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagrams ............................................................. 1

Revision History ............................................................................... 3

5 V Electrical Specifications ............................................................ 4

2.7 V Electrical Specifications ......................................................... 6

Absolute Maximum Ratings ............................................................ 8

ESD Caution .................................................................................. 8

Typical Performance Characteristics ............................................. 9

Applications Information .............................................................. 15

Output Phase Reversal ............................................................... 15

Maximum Power Dissipation ................................................... 15

Input Overvoltage Protection ................................................... 15

THD + Noise ............................................................................... 15

Total Noise Including Source Resistors ................................... 16

Channel Separation .................................................................... 16

Capacitive Load Drive ............................................................... 16

Light Sensitivity .......................................................................... 17

WLCSP Assembly Considerations ........................................... 17

I-V Conversion Applications ........................................................ 18

Photodiode Preamplifier Applications .................................... 18

Audio and PDA Applications ................................................... 18

Instrumentation Amplifiers ...................................................... 19

DAC Conversion ........................................................................ 19

Outline Dimensions ....................................................................... 20

Ordering Guide .......................................................................... 22

Rev. I | Page 2 of 24

AD8605/AD8606/AD8608

www.BDTIC.com/ADI

REVISION HISTORY

9/08—Rev. H to Rev. I

Changes to Input Overvoltage Protection Section ................ 15

Changes to Ordering Guide ...................................................... 22

2/08—Rev. G to Rev. H

Changes to Features ..................................................................... 1

Changes to Table 1 ....................................................................... 4

Changes to Table 2 ....................................................................... 6

Changes to Figure 11 ................................................................... 9

Changes to Figure 13, Figure 14, and Figure 16 Captions .... 10

Changes to Figure 15, Figure 17, and Figure 18 ..................... 10

Changes to Figure 34 and Figure 35 Captions ........................ 13

Changes to Figure 36 ................................................................. 13

Changes to Figure 37 Caption .................................................. 14

Changes to Figure 38 and Figure 41 ........................................ 14

Changes to Figure 45 ................................................................. 15

Changes to Audio and PDA Applications Section ................. 18

Changes to Figure 52 ................................................................. 18

Changes to Ordering Guide ...................................................... 22

10/07—Rev. F to Rev. G

Changes to Figure 2 ...................................................................... 1

Updated Outline Dimensions ................................................... 20

8/07—Rev. E to Rev. F

Added 8-Ball WLCSP Package ..................................... Universal

Changes to Features ..................................................................... 1

Changes to Table 1 ....................................................................... 3

Changes to Table 2 ....................................................................... 5

Changes to Table 4 ....................................................................... 7

Updated Outline Dimensions ................................................... 19

Changes to Ordering Guide ...................................................... 21

1/06—Rev. D to Rev. E

Changes to Table 1 ....................................................................... 3

Changes to Table 2 ....................................................................... 5

Changes to Table 4 ....................................................................... 6

Changes to Figure 12 Caption .................................................... 8

Changes to Figure 26 and Figure 27 Captions ........................ 11

Changes to Figure 33 Caption .................................................. 12

Changes to Figure 44 ................................................................. 14

Updated Outline Dimensions ................................................... 19

Changes to Ordering Guide ...................................................... 20

5/04—Rev. C to Rev. D

Updated Format ............................................................. Universal

Edit to Light Sensitivity Section ............................................... 16

Updated Outline Dimensions ................................................... 19

Changes to Ordering Guide ...................................................... 20

7/03—Rev. B to Rev. C

Changes to Features ....................................................................... 1

Change to General Description .................................................... 1

Addition to Functional Block Diagrams ..................................... 1

Addition to Absolute Maximum Ratings .................................... 4

Addition to Ordering Guide ......................................................... 4

Change to Equation in Maximum Power Dissipation

Section .......................................................................................... 11

Added Light Sensitivity Section ................................................ 12

Added New Figure 8; Renumbered Subsequently .................. 13

Added New MicroCSP Assembly Considerations Section .... 13

Changes to Figure 9 .................................................................... 13

Change to Equation in Photodiode Preamplifier

Applications Section .................................................................. 13

Changes to Figure 12 .................................................................. 14

Change to Equation in D/A Conversion Section .................... 14

Updated Outline Dimensions ................................................... 15

3/03—Rev. A to Rev. B

Changes to Functional Block Diagram ....................................... 1

Changes to Absolute Maximum Ratings..................................... 4

Changes to Ordering Guide ........................................................ 4

Changes to Figure 9 ................................................................... 13

Updated Outline Dimensions .................................................... 15

11/02—Rev. 0 to Rev. A

Change to Electrical Characteristics ............................................ 2

Changes to Absolute Maximum Ratings..................................... 4

Changes to Ordering Guide ......................................................... 4

Change to TPC 6 ........................................................................... 5

Updated Outline Dimensions .................................................... 15

5/02—Revision 0: Initial Version

Rev. I | Page 3 of 24

AD8605/AD8606/AD8608

www.BDTIC.com/ADI

5 V ELECTRICAL SPECIFICATIONS

VS = 5 V, VCM = VS/2, TA = 25°C, unless otherwise noted.

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS

AD8605/AD8606 (Except WLCSP) VS = 3.5 V, VCM = 3 V 20 65 μV

AD8608 VS = 3.5 V, VCM = 2.7 V 20 75 μV

AD8605/AD8606/AD8608 VS = 5 V, VCM = 0 V to 5 V 80 300 μV

−40°C < TA < +125°C 750 μV

Input Bias Current IB 0.2 1 pA

AD8605/AD8606 −40°C < TA < +85°C 50 pA

AD8605/AD8606 −40°C < TA < +125°C 250 pA

AD8608 −40°C < TA < +85°C 100 pA

AD8608 −40°C < TA < +125°C 300 pA

Input Offset Current IOS 0.1 0.5 pA

−40°C < TA < +85°C 20 pA

−40°C < TA < +125°C 75 pA

Input Voltage Range 0 5 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 5 V 85 100 dB

−40°C < TA < +125°C 75 90 dB

Large Signal Voltage Gain AVO RL = 2 kΩ, VO = 0.5 V to 4.5 V 300 1000 V/mV

Offset Voltage Drift

AD8605/AD8606 ΔVOS/ΔT −40°C < TA < +125°C 1 4.5 μV/°C

AD8608 ΔVOS/ΔT −40°C < TA < +125°C 1.5 6.0 μV/°C

INPUT CAPACITANCE

Common-Mode Input Capacitance C

Differential Input Capacitance C

OUTPUT CHARACTERISTICS

Output Voltage High VOH IL = 1 mA 4.96 4.98 V

I

−40°C < TA < +125°C 4.6 V

Output Voltage Low VOL IL = 1 mA 20 40 mV

I

−40°C < TA < +125°C 290 mV

Output Current I

Closed-Loop Output Impedance Z

POWER SUPPLY

Power Supply Rejection Ratio PSRR

AD8605/AD8606 VS = 2.7 V to 5.5 V 80 95 dB

AD8605/AD8606 WLCSP VS = 2.7 V to 5.5 V 75 92 dB

AD8608 VS = 2.7 V to 5.5 V 77 92 dB

−40°C < TA < +125°C 70 90 dB

Supply Current/Amplifier ISY I

−40°C < TA < +125°C 1.4 mA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 2 kΩ, CL = 16 pF 5 V/μs

Settling Time tS To 0.01%, 0 V to 2 V step, AV = 1 <1 μs

Unity Gain Bandwidth Product GBP 10 MHz

Phase Margin Φ

8.8 pF

COM

2.6 pF

DIFF

= 10 mA 4.7 4.79 V

L

= 10 mA 170 210 mV

L

±80 mA

OUT

f = 1 MHz, AV = 1 1 Ω

OUT

= 0 mA 1 1.2 mA

OUT

M

65 Degrees

Rev. I | Page 4 of 24

AD8605/AD8606/AD8608

www.BDTIC.com/ADI

Parameter Symbol Conditions Min Typ Max Unit

NOISE PERFORMANCE

Peak-to-Peak Noise en p-p f = 0.1 Hz to 10 Hz 2.3 3.5 μV p-p

Voltage Noise Density en f = 1 kHz 8 12 nV/√Hz

e

Current Noise Density in f = 1 kHz 0.01 pA/√Hz

f = 10 kHz 6.5 nV/√Hz

n

Rev. I | Page 5 of 24

AD8605/AD8606/AD8608

www.BDTIC.com/ADI

2.7 V ELECTRICAL SPECIFICATIONS

VS = 2.7 V, VCM = VS/2, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS

AD8605/AD8606 (Except WLCSP) VS = 3.5 V, VCM = 3 V 20 65 μV

AD8608 VS = 3.5 V, VCM = 2.7 V 20 75 μV

AD8605/AD8606/AD8608 VS = 2.7 V, VCM = 0 V to 2.7 V 80 300 μV

−40°C < TA < +125°C 750 μV

Input Bias Current IB 0.2 1 pA

AD8605/AD8606 −40°C < TA < +85°C 50 pA

AD8605/AD8606 −40°C < TA < +125°C 250 pA

AD8608 −40°C < TA < +85°C 100 pA

AD8608 −40°C < TA < +125°C 300 pA

Input Offset Current IOS 0.1 0.5 pA

−40°C < TA < +85°C 20 pA

−40°C < TA < +125°C 75 pA

Input Voltage Range 0 2.7 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 2.7 V 80 95 dB

−40°C < TA < +125°C 70 85 dB

Large Signal Voltage Gain AVO RL = 2 kΩ, VO = 0.5 V to 2.2 V 110 350 V/mV

Offset Voltage Drift

AD8605/AD8606 ΔVOS/ΔT −40°C < TA < +125°C 1 4.5 μV/°C

AD8608 ΔVOS/ΔT −40°C < TA < +125°C 1.5 6.0 μV/°C

INPUT CAPACITANCE

Common-Mode Input Capacitance C

Differential Input Capacitance C

OUTPUT CHARACTERISTICS

Output Voltage High VOH IL = 1 mA 2.6 2.66 V

−40°C < TA < +125°C 2.6 V

Output Voltage Low VOL IL = 1 mA 25 40 mV

−40°C < TA < +125°C 50 mV

Output Current I

Closed-Loop Output Impedance Z

POWER SUPPLY

Power Supply Rejection Ratio PSRR

AD8605/AD8606 VS = 2.7 V to 5.5 V 80 95 dB

AD8605/AD8606 WLCSP VS = 2.7 V to 5.5 V 75 92 dB

AD8608 VS = 2.7 V to 5.5 V 77 92 dB

−40°C < TA < +125°C 70 90 dB

Supply Current/Amplifier I

−40°C < TA < +125°C 1.5 mA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 2 kΩ, CL = 16 pF 5 V/μs

Settling Time tS To 0.01%, 0 V to 1 V step, AV = 1 <0.5 μs

Unity Gain Bandwidth Product GBP 9 MHz

Phase Margin Φ

8.8 pF

COM

2.6 pF

DIFF

±30 mA

OUT

f = 1 MHz, AV = 1 1.2 Ω

OUT

I

SY

M

= 0 mA 1.15 1.4 mA

OUT

50 Degrees

Rev. I | Page 6 of 24

AD8605/AD8606/AD8608

www.BDTIC.com/ADI

Parameter Symbol Conditions Min Typ Max Unit

NOISE PERFORMANCE

Peak-to-Peak Noise en p-p f = 0.1 Hz to 10 Hz 2.3 3.5 μV p-p

Voltage Noise Density en f = 1 kHz 8 12 nV/√Hz

e

Current Noise Density in f = 1 kHz 0.01 pA/√Hz

f = 10 kHz 6.5 nV/√Hz

n

Rev. I | Page 7 of 24

AD8605/AD8606/AD8608

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage 6 V

Input Voltage GND to V

Differential Input Voltage 6 V

Output Short-Circuit Duration to GND Observe Derating Curves

Storage Temperature Range

All Packages −65°C to +150°C

Operating Temperature Range

All Packages −40°C to +125°C

Junction Temperature Range

All Packages −65°C to +150°C

Lead Temperature (Soldering, 60 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

S

Table 4.

Package Type θ

5-Ball WLCSP (CB) 170 °C/W

5-Lead SOT-23 (RJ) 240 92 °C/W

8-Ball WLCSP (CB) 115 °C/W

8-Lead MSOP (RM) 206 44 °C/W

8-Lead SOIC_N (R) 157 56 °C/W

14-Lead SOIC_N (R) 105 36 °C/W

14-Lead TSSOP (RU) 148 23 °C/W

1

θJA is specified for the worst-case conditions, that is, a device soldered in a

circuit board for surface-mount packages.

1

θJC Unit

JA

ESD CAUTION

Rev. I | Page 8 of 24

Loading...

Loading...