Page 1

General-Purpose CMOS

FEATURES

Single-supply operation: 2.7 V to 5.5 V

Low supply current: 45 μA/amplifier

Wide bandwidth: 1 MHz

No phase reversal

Low input currents: 4 pA

Unity gain stable

Rail-to-rail input and output

APPLICATIONS

ASIC input or output amplifiers

Sensor interfaces

Piezoelectric transducer amplifiers

Medical instrumentations

Mobile communications

Audio outputs

Portable systems

GENERAL DESCRIPTION

The AD8541/AD8542/AD8544 are single, dual, and quad railto-rail input and output single-supply amplifiers featuring very

low supply current and 1 MHz bandwidth. All are guaranteed to

operate from a 2.7 V single supply as well as a 5 V supply. These

parts provide 1 MHz bandwidth at a low current consumption

of 45 A per amplifier.

Very low input bias currents enable the AD8541/AD8542/AD8544

to be used for integrators, photodiode amplifiers, piezoelectric

sensors, and other applications with high source impedance.

The supply current is only 45 A per amplifier, ideal for battery

operation.

Rail-to-rail inputs and outputs are useful to designers buffering

ASICs in single-supply systems. The AD8541/AD8542/AD8544

are optimized to maintain high gains at lower supply voltages,

making them useful for active filters and gain stages.

The AD8541/AD8542/AD8544 are specified over the extended

industrial temperature range (–40°C to +125°C). The AD8541

is available in 8-lead SOIC, 5-lead SC70, and 5-lead SOT-23

packages. The AD8542 is available in 8-lead SOIC, 8-lead

MSOP, and 8-lead TSSOP surface-mount packages. The

AD8544 is available in 14-lead narrow SOIC and 14-lead

TSSOP surface-mount packages. All MSOP, SC70, and SOT

versions are available in tape and reel only.

Rail-to-Rail Amplifiers

AD8541/AD8542/AD8544

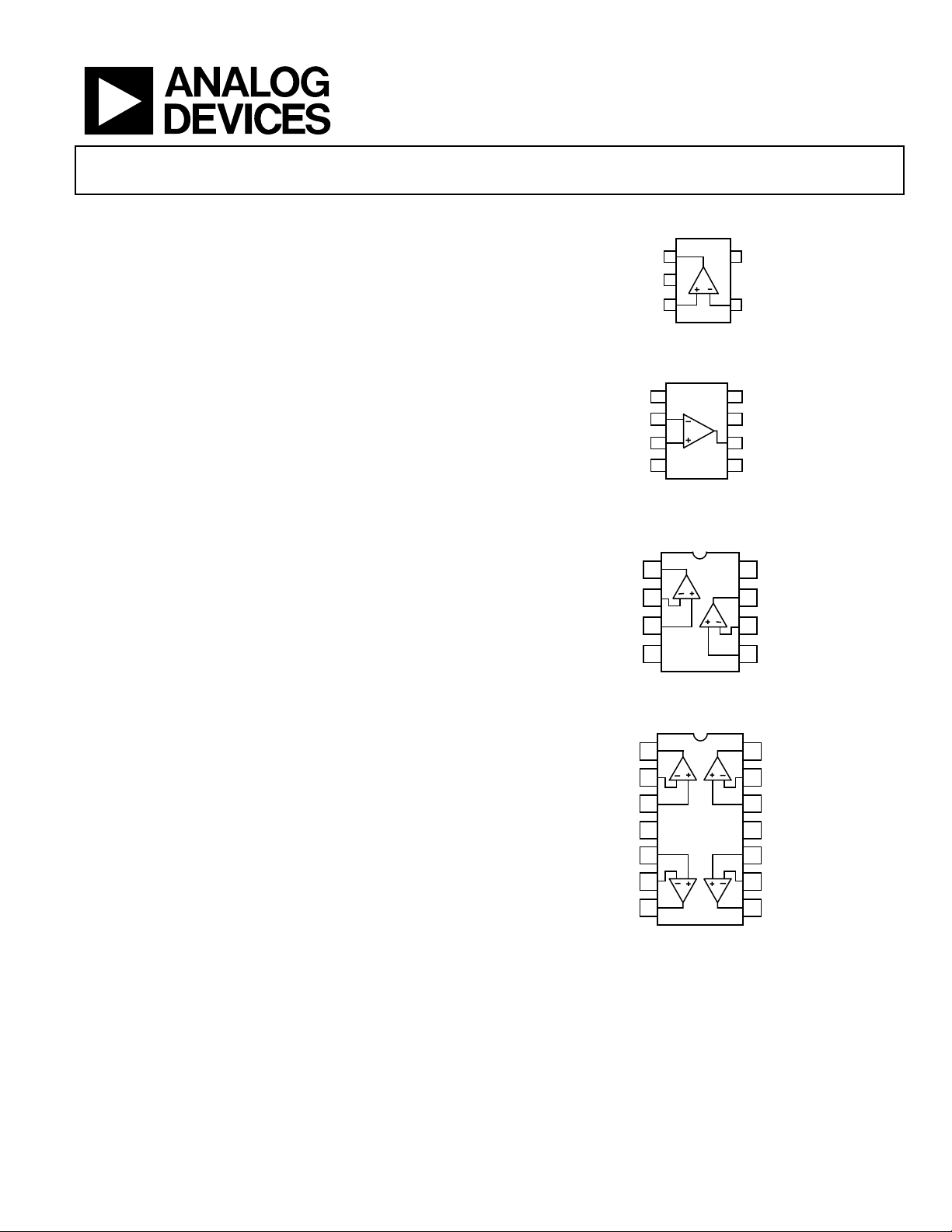

PIN CONFIGURATIONS

+IN A

V–

AD8541

1

2

3

OUT A

Figure 1. 5-Lead SC70 and 5-Lead SOT-23

(KS and R

1

NC

AD8541

2

–IN A

3

+IN A

4

V–

NC = NO CONNECT

Figure 2. 8-Lead SOIC

(R Suffix)

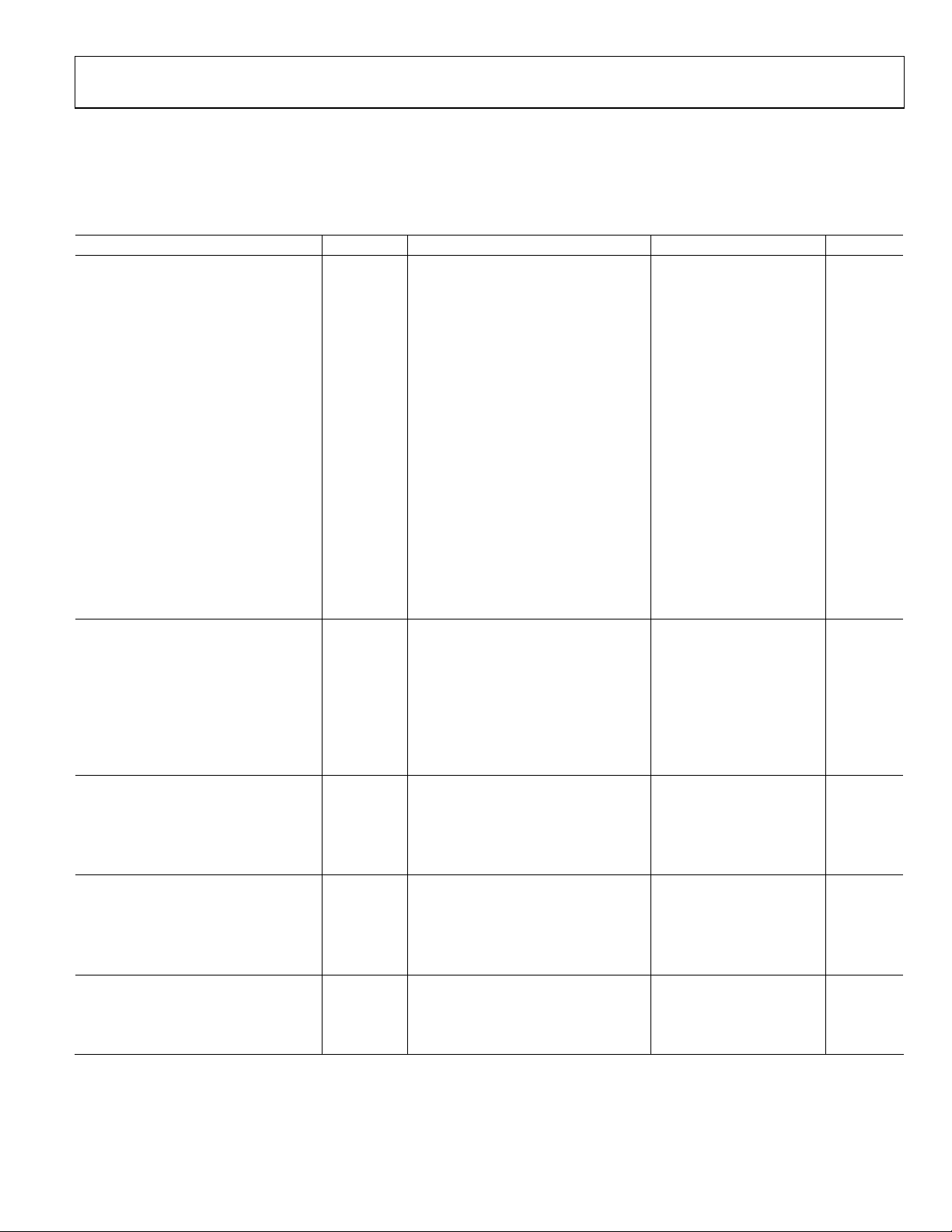

OUT A

–IN A

+IN A

V–

AD8542

1

2

3

4

Figure 3. 8-Lead SOIC, 8-Lead MSOP, and 8-Lead TSSOP

(R, RM, and RU Suffixes)

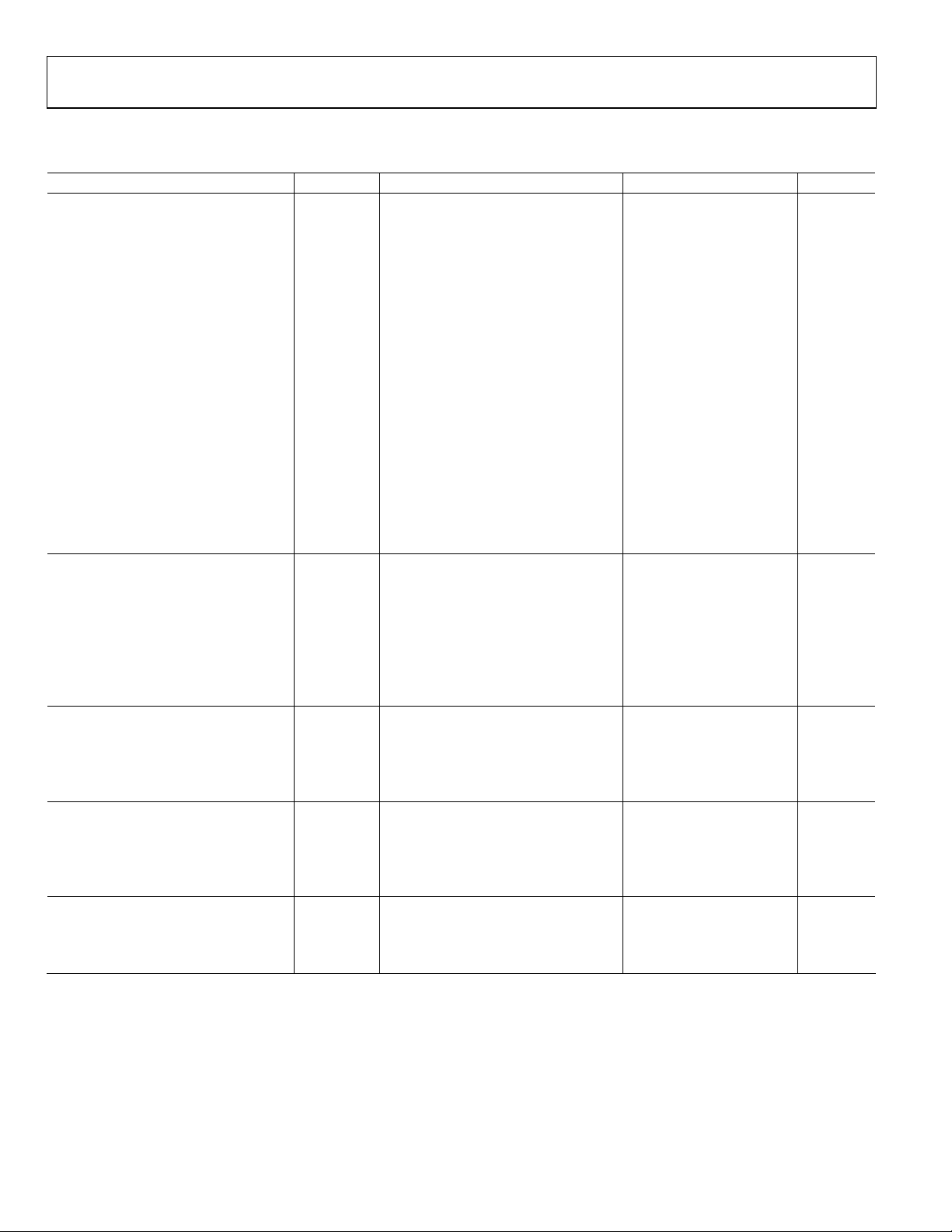

1

OUT A

2

–IN A

3

+IN A

AD8544

4

V+

5

+IN B

6

–IN B

7

OUT B

Figure 4. 14-Lead SOIC and 14-Lead TSSOP

(R and RU Suffixes)

5

4

J Suffixes)

8

7

6

5

V+

–IN A

NC

V+

OUT A

NC

8

7

6

5

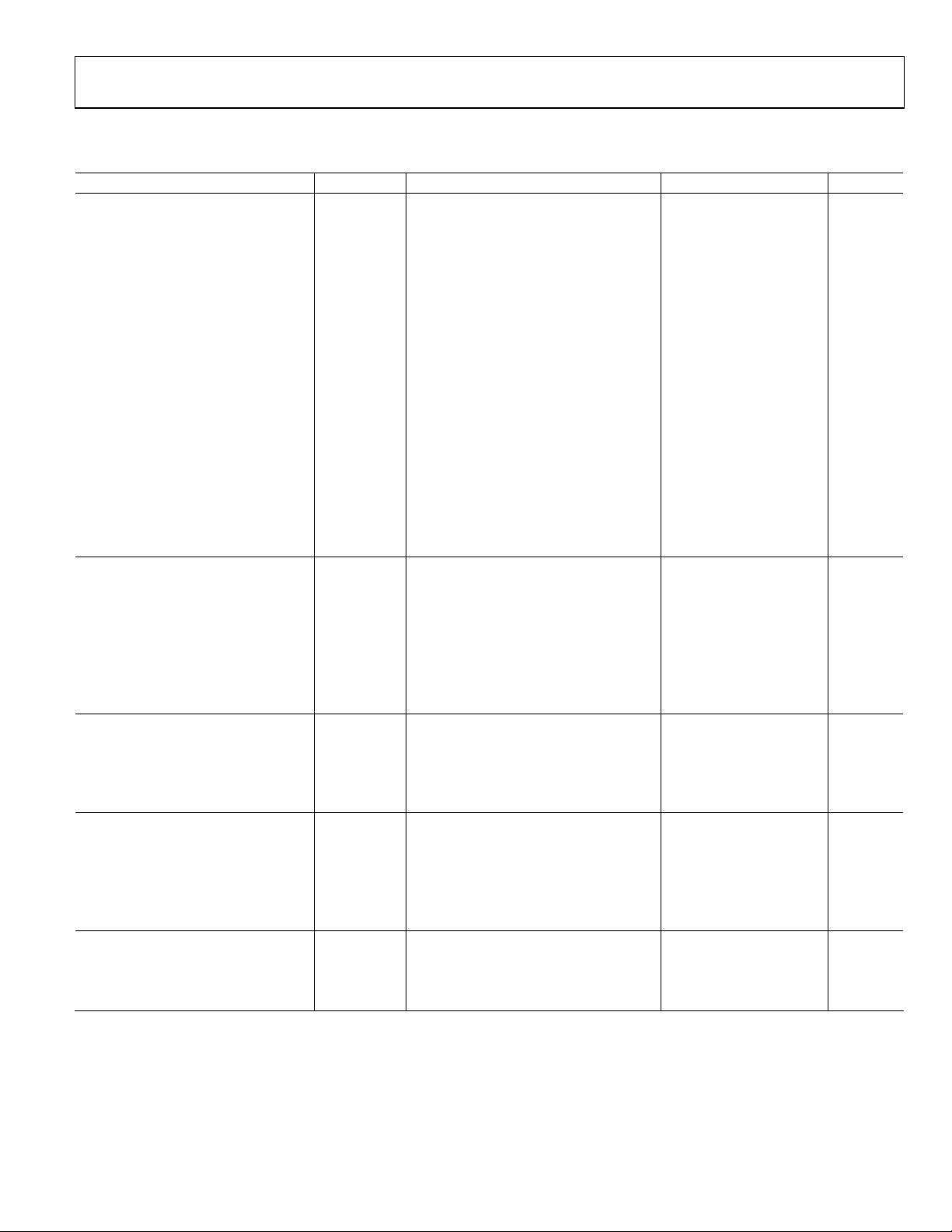

14

13

12

11

10

9

8

V+

OUT B

–IN B

+IN B

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

00935-001

00935-002

00935-003

00935-004

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

Page 2

AD8541/AD8542/AD8544

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Pin Configurations ........................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Electrical Characteristics ............................................................. 3

Absolute Maximum Ratings............................................................ 6

Thermal Resistance ...................................................................... 6

ESD Caution.................................................................................. 6

REVISION HISTORY

1/07—Rev. D to Rev. E

Updated Format ..................................................................Universal

Changes to Photodiode Application Section ..............................14

Changes to Ordering Guide.......................................................... 17

8/04—Rev. C to Rev. D

Changes to Ordering Guide............................................................ 5

Changes to Figure 3........................................................................ 10

Updated Outline Dimensions....................................................... 12

1/03—Rev. B to Rev. C

Updated Format ..................................................................Universal

Changes to General Description .................................................... 1

Changes to Ordering Guide............................................................ 5

Changes to Outline Dimensions................................................... 12

Typical Performance Characteristics ..............................................7

Theory of Operation ...................................................................... 12

Notes on the AD854x Amplifiers............................................. 12

Applications..................................................................................... 13

Notch Filter ................................................................................. 13

Comparator Function................................................................ 13

Photodiode Application ............................................................ 14

Outline Dimensions....................................................................... 15

Ordering Guide .......................................................................... 17

Rev. E | Page 2 of 20

Page 3

AD8541/AD8542/AD8544

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VS = 2.7 V, VCM = 1.35 V, TA = 25°C, unless otherwise noted.

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS 1 6 mV

–40°C ≤ TA ≤ +125°C 7 mV

Input Bias Current IB 4 60 pA

–40°C ≤ TA ≤ +85°C 100 pA

–40°C ≤ TA ≤ +125°C 1000 pA

Input Offset Current IOS 0.1 30 pA

–40°C ≤ TA ≤ +85°C 50 pA

–40°C ≤ TA ≤ +125°C 500 pA

Input Voltage Range 0 2.7 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 2.7 V 40 45 dB

–40°C ≤ TA ≤ +125°C 38 dB

Large Signal Voltage Gain AVO RL = 100 kΩ , VO = 0.5 V to 2.2 V 100 500 V/mV

–40°C ≤ TA ≤ +85°C 50 V/mV

–40°C ≤ TA ≤ +125°C 2 V/mV

Offset Voltage Drift ΔVOS/ΔT –40°C ≤ TA ≤ +125°C 4 μV/°C

Bias Current Drift ΔIB/ΔT –40°C ≤ TA ≤ +85°C 100 fA/°C

–40°C ≤ TA ≤ +125°C 2000 fA/°C

Offset Current Drift ΔIOS/ΔT –40°C ≤ TA ≤ +125°C 25 fA/°C

OUTPUT CHARACTERISTICS

Output Voltage High VOH IL = 1 mA 2.575 2.65 V

–40°C ≤ TA ≤ +125°C 2.550 V

Output Voltage Low VOL IL = 1 mA 35 100 mV

–40°C ≤ TA ≤ +125°C 125 mV

Output Current I

±ISC ±20 mA

Closed-Loop Output Impedance Z

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = 2.5 V to 6 V 65 76 dB

–40°C ≤ TA ≤ +125°C 60 dB

Supply Current/Amplifier ISY VO = 0 V 38 55 μA

–40°C ≤ TA ≤ +125°C 75 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ 0.4 0.75 V/μs

Settling Time tS To 0.1% (1 V step) 5 μs

Gain Bandwidth Product GBP 980 kHz

Phase Margin Φo 63 Degrees

NOISE PERFORMANCE

Voltage Noise Density en f = 1 kHz 40 nV/√Hz

e

Current Noise Density in <0.1 pA/√Hz

V

OUT

f = 200 kHz, AV = 1 50 Ω

OUT

f = 10 kHz 38 nV/√Hz

n

= VS – 1 V 15 mA

OUT

Rev. E | Page 3 of 20

Page 4

AD8541/AD8542/AD8544

VS = 3.0 V, VCM = 1.5 V, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS 1 6 mV

–40°C ≤ TA ≤ +125°C 7 mV

Input Bias Current IB 4 60 pA

–40°C ≤ TA ≤ +85°C 100 pA

–40°C ≤ TA ≤ +125°C 1000 pA

Input Offset Current IOS 0.1 30 pA

–40°C ≤ TA ≤ +85°C 50 pA

–40°C ≤ TA ≤ +125°C 500 pA

Input Voltage Range 0 3 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 3 V 40 45 dB

–40°C ≤ TA ≤ +125°C 38 dB

Large Signal Voltage Gain AVO RL = 100 kΩ , VO = 0.5 V to 2.2 V 100 500 V/mV

–40°C ≤ TA ≤ +85°C 50 V/mV

–40°C ≤ TA ≤ +125°C 2 V/mV

Offset Voltage Drift ΔVOS/ΔT –40°C ≤ TA ≤ +125°C 4 μV/°C

Bias Current Drift ΔIB/ΔT –40°C ≤ TA ≤ +85°C 100 fA/°C

–40°C ≤ TA ≤ +125°C 2000 fA/°C

Offset Current Drift ΔIOS/ΔT –40°C ≤ TA ≤ +125°C 25 fA/°C

OUTPUT CHARACTERISTICS

Output Voltage High VOH IL = 1 mA 2.875 2.955 V

–40°C ≤ TA ≤ +125°C 2.850 V

Output Voltage Low VOL IL = 1 mA 32 100 mV

–40°C ≤ TA ≤ +125°C 125 mV

Output Current I

±ISC ±25 mA

Closed-Loop Output Impedance Z

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = 2.5 V to 6 V 65 76 dB

–40°C ≤ TA ≤ +125°C 60 dB

Supply Current/Amplifier ISY VO = 0 V 40 60 μA

–40°C ≤ TA ≤ +125°C 75 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ 0.4 0.8 V/μs

Settling Time tS To 0.01% (1 V step) 5 μs

Gain Bandwidth Product GBP 980 kHz

Phase Margin Φo 64 Degrees

NOISE PERFORMANCE

Voltage Noise Density en f = 1 kHz 42 nV/√Hz

e

Current Noise Density in <0.1 pA/√Hz

V

OUT

f = 200 kHz, AV = 1 50 Ω

OUT

f = 10 kHz 38 nV/√Hz

n

= VS – 1 V 18 mA

OUT

Rev. E | Page 4 of 20

Page 5

AD8541/AD8542/AD8544

VS = 5.0 V, VCM = 2.5 V, TA = 25°C, unless otherwise noted.

Table 3.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS 1 6 mV

–40°C ≤ TA ≤ +125°C 7 mV

Input Bias Current IB 4 60 pA

–40°C ≤ TA ≤ +85°C 100 pA

–40°C ≤ TA ≤ +125°C 1000 pA

Input Offset Current IOS 0.1 30 pA

–40°C ≤ TA ≤ +85°C 50 pA

–40°C ≤ TA ≤ +125°C 500 pA

Input Voltage Range 0 5 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 5 V 40 48 dB

–40°C ≤ TA ≤ +125°C 38 dB

Large Signal Voltage Gain AVO RL = 100 kΩ , VO = 0.5 V to 2.2 V 20 40 V/mV

–40°C ≤ TA ≤ +85°C 10 V/mV

–40°C ≤ TA ≤ +125°C 2 V/mV

Offset Voltage Drift ΔVOS/ΔT –40°C ≤ TA ≤ +125°C 4 μV/°C

Bias Current Drift ΔIB/ΔT –40°C ≤ TA ≤ +85°C 100 fA/°C

–40°C ≤ TA ≤ +125°C 2000 fA/°C

Offset Current Drift ΔIOS/ΔT –40°C ≤ TA ≤ +125°C 25 fA/°C

OUTPUT CHARACTERISTICS

Output Voltage High VOH IL = 1 mA 4.9 4.965 V

–40°C ≤ TA ≤ +125°C 4.875 V

Output Voltage Low VOL IL = 1 mA 25 100 mV

–40°C ≤ TA ≤ +125°C 125 mV

Output Current I

±ISC ±60 mA

Closed-Loop Output Impedance Z

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = 2.5 V to 6 V 65 76 dB

–40°C ≤ TA ≤ +125°C 60 dB

Supply Current/Amplifier ISY VO = 0 V 45 65 μA

–40°C ≤ TA ≤ +125°C 85 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ, CL = 200 pF 0.45 0.92 V/μs

Full-Power Bandwidth BWP 1% distortion 70 kHz

Settling Time tS To 0.1% (1 V step) 6 μs

Gain Bandwidth Product GBP 1000 kHz

Phase Margin Φo 67 Degrees

NOISE PERFORMANCE

Voltage Noise Density en f = 1 kHz 42 nV/√Hz

e

Current Noise Density in <0.1 pA/√Hz

V

OUT

f = 200 kHz, AV = 1 45 Ω

OUT

f = 10 kHz 38 nV/√Hz

n

= VS – 1 V 30 mA

OUT

Rev. E | Page 5 of 20

Page 6

AD8541/AD8542/AD8544

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage (VS) 6 V

Input Voltage GND to VS

Differential Input Voltage1 ±6 V

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +125°C

Junction Temperature Range −65°C to +150°C

Lead Temperature (Soldering, 60 sec) 300°C

1

For supplies less than 6 V, the differential input voltage is equal to ±VS.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 5.

Package Type θJA θ

5-Lead SC70 (KS) 376 126 °C/W

5-Lead SOT-23 (RJ) 230 146 °C/W

8-Lead SOIC (R) 158 43 °C/W

8-Lead MSOP (RM) 210 45 °C/W

8-Lead TSSOP (RU) 240 43 °C/W

14-Lead SOIC (R) 120 36 °C/W

14-Lead TSSOP (RU) 240 43 °C/W

Unit

JC

ESD CAUTION

Rev. E | Page 6 of 20

Page 7

AD8541/AD8542/AD8544

TYPICAL PERFORMANCE CHARACTERISTICS

180

160

140

120

100

80

60

NUMBER OF AMPLIFIERS

40

20

0

–4.5 –3.5 4. 5–2.5 –1.5 –0.5 0.5

INPUT OFFSET VOLTAGE (mV)

Figure 5. Input Offset Voltage Distribution

VS=5V

V

CM

T

= 25°C

A

1.5 2.5 3.5

=2.5V

00935-005

400

VS = 2.7V AND 5V

V

= VS/2

CM

350

300

250

200

150

100

INPUT BIAS CURRENT (pA)

50

0

–40 –20 0 20 40 60 80 100 120 140

TEMPERATURE ( °C)

Figure 8. Input Bias Current vs. Temperature

00935-008

1.0

VS = 2.7V AND 5V

0.5

V

= VS/2

CM

0

–0.5

–1.0

–1.5

–2.0

–2.5

INPUT OFFSET VOLTAGE (mV)

–3.0

–3.5

–4.0

–55 –35 –15

5 25 45 65 85 105 125

TEMPERATURE (° C)

Figure 6. Input Offset Voltage vs. Temperature

9

VS = 2.7V AND 5V

8

V

= VS/2

CM

7

6

5

4

3

INPUT BIAS CURRENT (pA)

2

1

0

–0.5 0.5 1.5 2.5 3.5 4.5 5.5

COMMON-MODE VOLTAGE (V)

Figure 7. Input Bias Current vs. Common-Mode Voltage

145

7

VS = 2.7V AND 5V

= VS/2

V

6

CM

5

4

3

2

1

INPUT OFF SET CURRENT (p A)

0

–1

00935-006

–55 – 35 –15 5 25 45 65 85 105 125 145

TEMPERATURE ( °C)

00935-009

Figure 9. Input Offset Current vs. Temperature

160

VS = 2.7V

140

= 25°C

T

A

120

100

80

60

40

20

0

POWER SUPPLY REJECTIO N (dB)

–20

–40

00935-007

100 1k 10k 100k 1M 10M

+PSRR

–PSRR

FREQUENCY (Hz)

00935-010

Figure 10. Power Supply Rejection Ratio vs. Frequency

Rev. E | Page 7 of 20

Page 8

AD8541/AD8542/AD8544

V

10k

1k

VS = 2.7V

T

= 25°C

A

60

50

VS = 2.7V

R

= 10kΩ

L

T

= 25°C

A

100

10

1

Δ OUTPUT VOLTAGE (mV)

0.1

0.01

0.001 0.01 0.1 1 10 100

SOURCE

SINK

LOAD CURRENT (mA)

Figure 11. Output Voltage to Supply Rail vs. Load Current

3.0

2.5

2.0

1.5

1.0

OUTPUT SWING (V p-p)

0.5

VS = 2.7V

V

= 2.5V p-p

IN

R

= 2kΩ

L

T

= 25°C

A

40

30

20

SMALL SIGNAL OVERSHOOT (%)

10

0

00935-011

10 100 1k 10k

CAPACITANCE (pF )

+OS

–OS

00935-014

Figure 14. Small Signal Overshoot vs. Load Capacitance

60

VS = 2.7V

R

= 2kΩ

L

50

T

= 25°C

A

40

30

20

SMALL SIGNAL OVERSHOOT (%)

10

+OS

–OS

0

1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 12. Closed-Loop Output Voltage Swing vs. Frequency

60

VS = 2.7V

R

=

L

∞

TA = 25°C

50

40

30

20

SMALL SIGNAL OVERSHOOT (%)

10

0

10 100 1k 10k

CAPACITANCE (pF )

+OS

–OS

Figure 13. Small Signal Overshoot vs. Load Capacitance

0

00935-012

10 100 1k 10k

CAPACITANCE (pF )

00935-015

Figure 15. Small Signal Overshoot vs. Load Capacitance

VS = 2.7V

= 100kΩ

R

L

= 300pF

C

L

= 1

A

V

= 25°C

T

A

1.35

50mV 10µs

00935-013

0935-016

Figure 16. Small Signal Transient Response

Rev. E | Page 8 of 20

Page 9

AD8541/AD8542/AD8544

90

VS = 5V

T

= 25°C

80

A

70

60

50

40

30

20

10

COMMON-MO DE REJECTIO N (dB)

0

–10

1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 20. Common-Mode Rejection Ratio vs. Frequency

00935-020

1.35V

VS = 2.7V

R

= 2kΩ

L

A

= 1

V

T

= 25°C

A

500mV 10µs

Figure 17. Large Signal Transient Response

00935-017

VS = 2.7V

R

= NO LOAD

L

T

= 25°C

A

80

60

40

GAIN (dB)

20

0

1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 18. Open-Loop Gain and Phase vs. Frequency

160

VS = 5V

140

T

= 25°C

A

120

100

80

60

40

20

0

POWER SUPPLY REJECTI ON RATIO ( dB)

–20

–40

100 1k 10k 100k 1M 10M

–PSRR

+PSRR

FREQUENCY (Hz)

Figure 19. Power Supply Rejection Ratio vs. Frequency

45

90

135

180

PHASE SHIF T (Degrees)

00935-019

10k

VS = 5V

= 25°C

T

A

1k

100

10

1

Δ OUTPUT VOLTAGE (mV)

0.1

0.01

00935-018

0.001 0.01 0.1 1 10 100

SOURCE

SINK

LOAD CURRENT (mA)

00935-021

Figure 21. Output Voltage to Supply Rail vs. Frequency

5.0

4.5

4.0

3.5

3.0

2.5

2.0

1.5

OUTPUT SWING (V p-p)

1.0

0.5

0

1k 10k 100k 1M 10M

FREQUENCY (Hz)

VS = 5V

= 4.9V p-p

V

IN

= NO LOAD

R

L

= 25°C

T

A

00935-022

Figure 22. Closed-Loop Output Voltage Swing vs. Frequency

Rev. E | Page 9 of 20

Page 10

AD8541/AD8542/AD8544

5.0

4.5

4.0

3.5

3.0

2.5

2.0

1.5

OUTPUT SWING (V p-p)

1.0

0.5

0

1k 10k 100k 1M 10M

FREQUENCY (Hz)

VS = 5V

= 4.9V p-p

V

IN

= 2kΩ

R

L

= 25°C

T

A

Figure 23. Closed-Loop Output Voltage Swing vs. Frequency

00935-023

60

VS = 5V

R

=

L

50

40

30

20

SMALL SIGNAL OVERSHOOT (%)

10

∞

TA = 25°C

+OS

–OS

0

10 100 1k 10k

CAPACITANCE (pF )

Figure 26. Small Signal Overshoot vs. Load Capacitance

00935-026

60

VS = 5V

= 10kΩ

R

L

= 25°C

T

50

A

40

+OS

30

20

SMALL SIGNAL OVERSHO OT (%)

10

0

10 100 1k 10k

CAPACITANCE (pF )

–OS

Figure 24. Small Signal Overshoot vs. Load Capacitance

60

VS = 5V

R

= 2kΩ

L

T

= 25°C

50

A

40

30

20

+OS

–OS

VS = 5V

= 100kΩ

R

L

= 300pF

C

L

= 1

A

V

= 25°C

T

A

2.5V

50mV 10µs

00935-024

00935-027

Figure 27. Small Signal Transient Response

VS = 5V

= 2kΩ

R

L

= 1

A

V

= 25°C

T

A

2.5V

SMALL SIGNAL OVERSHO OT (%)

10

0

10 100 1k 10k

CAPACITANCE (pF )

Figure 25. Small Signal Overshoot vs. Load Capacitance

00935-025

Rev. E | Page 10 of 20

1V 10µs

Figure 28. Large Signal Transient Response

00935-028

Page 11

AD8541/AD8542/AD8544

V

55

50

45

40

35

30

SUPPLY CURRENT/ AMPLIF IER (µA)

25

VS = 5V

VS = 2.7V

GAIN (dB)

80

60

40

20

0

VS = 5V

R

= NO LOAD

L

T

= 25°C

A

45

90

135

180

PHASE SHIF T (Degrees)

1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 29. Open-Loop Gain and Phase vs. Frequency

VS = 5V

= 10kΩ

R

L

A

V

T

A

= 1

= 25°C

2.5V

V

IN

V

OUT

1V 20µs

Figure 30. No Phase Reversal

60

TA = 25°C

50

40

20

00935-029

–55 –35 –15 5 25 45 65 85 105 125 145

TEMPERATURE (° C)

00935-032

Figure 32. Supply Current per Amplifier vs. Temperature

1000

VS= 2.7V AND 5V

900

=1

A

V

=25°C

T

A

800

700

600

500

400

IMPEDANCE (Ω)

300

200

00935-030

100

0

1k 10k 100k 1M 10M 100M

FREQUENCY (Hz)

00935-033

Figure 33. Closed-Loop Output Impedance vs. Frequency

VS=5V

MARKER SET @ 10kHz

MARKER READING: 37.6nV/ Hz

T

=25°C

A

30

20

10

SUPPLY CURRENT/ AMPLIF IER (µA)

0

0123456

SUPPLY VOLTAGE (V)

Figure 31. Supply Current per Amplifier vs. Supply Voltage

00935-031

15nV/DI

0 5 10 15 20 25

FREQUENCY (kHz)

Figure 34. Voltage Noise

00935-034

Rev. E | Page 11 of 20

Page 12

AD8541/AD8542/AD8544

THEORY OF OPERATION

NOTES ON THE AD854x AMPLIFIERS

The AD8541/AD8542/AD8544 amplifiers are improved

performance, general-purpose operational amplifiers.

Performance has been improved over previous amplifiers in

several ways.

Lower Supply Current for 1 MHz Gain Bandwidth

The AD854x series typically uses 45 A of current per amplifier.

This is much less than the 200 A to 700 A used in earlier

generation parts with similar performance. This makes the

AD854x series a good choice for upgrading portable designs for

longer battery life. Alternatively, additional functions and

performance can be added at the same current drain.

Higher Output Current

At 5 V single supply, the short-circuit current is typically 60 A.

Even 1 V from the supply rail, the AD854x amplifiers can

provide a 30 mA output current, sourcing or sinking.

Sourcing and sinking are strong at lower voltages, with 15 mA

available at 2.7 V and 18 mA at 3.0 V. For even higher output

currents, see the Analog Devices, Inc.

parts, with output currents to 250 mA. Information on these

parts is available from your Analog Devices representative, and

data sheets are available at

www.analog.com.

AD8531/AD8532/AD8534

Better Performance at Lower Voltages

The AD854x family of parts was designed to provide better ac

performance at 3.0 V and 2.7 V than previously available parts.

Typical gain-bandwidth product is close to 1 MHz at 2.7 V.

Voltage gain at 2.7 V and 3.0 V is typically 500,000. Phase

margin is typically over 60°C, making the part easy to use.

Rev. E | Page 12 of 20

Page 13

AD8541/AD8542/AD8544

V

2.5V

f

f

V

2.5V

V

APPLICATIONS

NOTCH FILTER

The AD854x have very high open-loop gain (especially with a

supply voltage below 4 V), which makes it useful for active

filters of all types. For example,

in the classic twin-T notch filter design. The twin-T notch is

desired for simplicity, low output impedance, and minimal use

of op amps. In fact, this notch filter can be designed with only

one op amp if Q adjustment is not required. Simply remove U2

as illustrated in

Figure 36. However, a major drawback to this

circuit topology is ensuring that all the Rs and Cs closely match.

The components must closely match or notch frequency offset

and drift causes the circuit to no longer attenuate at the ideal

notch frequency. To achieve desired performance, 1% or better

component tolerances or special component screens are usually

required. One method to desensitize the circuit-to-component

mismatch is to increase R2 with respect to R1, which lowers Q.

A lower Q increases attenuation over a wider frequency range

but reduces attenuation at the peak notch frequency.

R

100kΩR100kΩ

C2

53.6µF

REF

26.7nF

1

=

0

2πRC

1

=

0

V

IN

2.5V

4 1 –

REF

R1

R1 + R2

Figure 36. 60 Hz Twin-T Notch Filter, Q = ∞ (Ideal)

R/2

50kΩ

C

26.7nF

Figure 35. 60 Hz Twin-T Notch Filter, Q = 10

RR

2C

R/2

C

Figure 35 illustrates the AD8542

5.0

8

3

1/2 AD8542

U1

2

1

4

C

1/2 AD8542

C

5

7

U2

6

2.5V

5.0

7

3

AD8541

2

6

4

R2

2.5kΩ

R1

97.5kΩ

REF

V

OUT

00935-035

V

OUT

00935-036

Figure 37 is an example of the AD8544 in a notch filter circuit.

The frequency dependent negative resistance (FNDR) notch

filter has fewer critical matching requirements than the twin-T

notch and for the FNDR Q is directly proportional to a single

resistor R1. While matching component values is still

important, it is also much easier and/or less expensive to

accomplish in the FNDR circuit. For example, the twin-T notch

uses three capacitors with two unique values, whereas the

FNDR circuit uses only two capacitors, which may be of the

same value. U3 is simply a buffer that is added to lower the

output impedance of the circuit.

R

2.61kΩ

R

2.61kΩ

R

2.61kΩ

R

2.61kΩ

REF

1/4 AD8544

9

U3

10

3

2

2.5V

13

12

REF

8

4

U1

U4

1/4 AD8544

1

11

1/4 AD8544

14

V

OUT

NC

00935-037

R1

Q ADJUST

200Ω

C1

1µF

REF

1/4 AD8544

7

U2

1

f =

2π LC1

L = R2C2

C2

1µF

6

5

2.5V

Figure 37. FNDR 60 Hz Notch Filter with Output Buffer

COMPARATOR FUNCTION

A comparator function is a common application for a spare op

amp in a quad package.

a comparator in a standard overload detection application.

Unlike many op amps, the AD854x family can double as

comparators because this op amp family has a rail-to-rail

differential input range, rail-to-rail output, and a great speed

vs. power ratio. R2 is used to introduce hysteresis. The AD854x,

when used as comparators, have 5 µs propagation delay at 5 V

and 5 µs overload recovery time.

IN

2.5V

REF

Figure 38. AD854x Comparator Application—Overload Detector

Figure 38 illustrates ¼ of the AD8544 as

R2

1MΩ

R1

1kΩ

V

OUT

DC

1/4 AD8541

2.5V

00935-038

Rev. E | Page 13 of 20

Page 14

AD8541/AD8542/AD8544

PHOTODIODE APPLICATION

The AD854x family has very high impedance with an input bias

current typically around 4 pA. This characteristic allows the

AD854x op amps to be used in photodiode applications and

other applications that require high input impedance. Note that

the AD854x has significant voltage offset that can be removed

by capacitive coupling or software calibration.

Figure 39 illustrates a photodiode or current measurement

application. The feedback resistor is limited to 10 M to avoid

excessive output offset. Also, note that a resistor is not needed

on the noninverting input to cancel bias current offset because

the bias current-related output offset is not significant when

compared to the voltage offset contribution. For best

performance, follow the standard high impedance layout

techniques, which include:

• Shielding the circuit.

• Cleaning the circuit board.

• Putting a trace connected to the noninverting input around

the inverting input.

• Using separate analog and digital power supplies.

C

100pF

R

10MΩ

OR

D

2.5V

Figure 39. High Input Impedance Application—Photodiode Amplifier

REF

2.5V

REF

V+

7

2

3

6

AD8541

4

V

OUT

00935-039

Rev. E | Page 14 of 20

Page 15

AD8541/AD8542/AD8544

OUTLINE DIMENSIONS

2.90 BSC

1.60 BSC

1.30

1.15

0.90

0.15 MAX

5

123

PIN 1

COMPLIANT TO JEDEC STANDARDS MO-178-AA

1.90

BSC

0.50

0.30

4

2.80 BSC

0.95 BSC

1.45 MAX

SEATING

PLANE

0.22

0.08

10°

5°

0°

Figure 40. 5-Lead Small Outline Transistor Package [SOT-23]

(RJ-5)

Dimensions shown in millimeters

2.20

2.00

1.80

1.35

1.25

1.15

PIN 1

1.00

0.90

0.70

0

.

1

0

M

X

A

0.10 COPLANARITY

123

0.30

0.15

COMPLIANT TO JEDEC STANDARDS MO-203-AA

45

0.65 BSC

2.40

2.10

1.80

1.10

0.80

SEATING

PLANE

0.40

0.10

0.22

0.08

Figure 42. 5-Lead Thin Shrink Small Outline Transistor Package [SC70]

(KS-5)

Dimensions shown in millimeters

0.60

0.45

0.30

0.46

0.36

0.26

COPLANARIT Y

4.50

4.40

4.30

PIN 1

1.05

1.00

0.80

Figure 41. 14-Lead Thin Shrink Small Outline Package [TSSOP]

4.00 (0.1575)

3.80 (0.1496)

0.25 (0.0098)

0.10 (0.0039)

0.10

CONTROLL ING DIMENSIONS ARE IN MILLI METERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-O FF MIL LIMETE R EQUIVALENTS FOR

REFERENCE ON LY AND ARE NOT APPROPRI ATE FOR USE IN DESIGN.

Figure 43. 14-Lead Standard Small Outline Package [SOIC_N]

5.10

5.00

4.90

14

0.65

BSC

0.15

0.05

COMPLIANT TO JEDEC STANDARDS MO-153-AB-1

0.30

0.19

8

6.40

BSC

71

1.20

MAX

SEATING

PLANE

0.20

0.09

COPLANARITY

0.10

(RU-14)

Dimensions shown in millimeters

8.75 (0.3445)

8.55 (0.3366)

BSC

8

7

6.20 (0.2441)

5.80 (0.2283)

1.75 (0.0689)

1.35 (0.0531)

SEATING

PLANE

0.25 (0.0098)

0.17 (0.0067)

14

1

1.27 (0.0500)

0.51 (0.0201)

0.31 (0.0122)

COMPLIANT TO JEDEC STANDARDS MS-012-AB

Narrow Body

(R-14)

Dimensions shown in millimeters and (inches)

8°

0°

0.75

0.60

0.45

0.50 (0.0197)

0.25 (0.0098)

8°

0°

1.27 (0.0500)

0.40 (0.0157)

45°

060606-A

Rev. E | Page 15 of 20

Page 16

AD8541/AD8542/AD8544

Y

3.20

3.00

2.80

8

5

4

SEATING

PLANE

5.15

4.90

4.65

1.10 MAX

0.23

0.08

8°

0°

3.20

3.00

1

2.80

PIN 1

0.65 BSC

0.95

0.85

0.75

0.15

0.38

0.00

0.22

COPLANARITY

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-AA

Figure 44. 8-Lead Mini Small Outline Package [MSOP]

(RM-8)

Dimensions shown in millimeters

0.80

0.60

0.40

5.00 (0.1968)

4.80 (0.1890)

0.15

0.05

COPLANARIT

0.10

Figure 45. 8-Lead Thin Shrink Small Outline Package [TSSOP]

3.10

3.00

2.90

8

5

4.50

6.40 BSC

4.40

4.30

41

PIN 1

0.65 BSC

1.20

MAX

0.30

SEATING

0.19

PLANE

COMPLIANT TO JEDEC STANDARDS MO-153-AA

0.20

0.09

8°

0°

(RU-8)

Dimensions shown in millimeters

0.75

0.60

0.45

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLL ING DIMENSI ONS ARE IN MILLIMETERS; INCH DI MENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRI ATE FOR USE IN DES IGN.

85

1

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-A A

BSC

6.20 (0.2440)

5.80 (0.2284)

4

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

8°

0°

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

1.27 (0.0500)

0.40 (0.0157)

45°

060506-A

Figure 46. 8-Lead Standard Small Outline Package [SOIC_N]

Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

Rev. E | Page 16 of 20

Page 17

AD8541/AD8542/AD8544

ORDERING GUIDE

Package

Model Temperature Range Package Description

AD8541AKS-R2 –40°C to +125°C 5-Lead SC70 KS-5 A4B

AD8541AKS-REEL7 –40°C to +125°C 5-Lead SC70 KS-5 A4B

AD8541AKSZ-R21 –40°C to +125°C 5-Lead SC70 KS-5 A12

AD8541AKSZ-REEL71 –40°C to +125°C 5-Lead SC70 KS-5 A12

AD8541AR –40°C to +125°C 8-Lead SOIC_N R-8

AD8541AR-REEL –40°C to +125°C 8-Lead SOIC_N R-8

AD8541AR-REEL7 –40°C to +125°C 8-Lead SOIC_N R-8

AD8541ARZ1 –40°C to +125°C 8-Lead SOIC_N R-8

AD8541ARZ-REEL1 –40°C to +125°C 8-Lead SOIC_N R-8

AD8541ARZ-REEL71 –40°C to +125°C 8-Lead SOIC_N R-8

AD8541ART-R2 –40°C to +125°C 5-Lead SOT-23 RJ-5 A4A

AD8541ART-REEL –40°C to +125°C 5-Lead SOT-23 RJ-5 A4A

AD8541ART-REEL7 –40°C to +125°C 5-Lead SOT-23 RJ-5 A4A

AD8541ARTZ-R21 –40°C to +125°C 5-Lead SOT-23 RJ-5 A4A#

AD8541ARTZ-REEL1 –40°C to +125°C 5-Lead SOT-23 RJ-5 A4A#

AD8541ARTZ-REEL71 –40°C to +125°C 5-Lead SOT-23 RJ-5 A4A#

AD8542AR –40°C to +125°C 8-Lead SOIC_N R-8

AD8542AR-REEL –40°C to +125°C 8-Lead SOIC_N R-8

AD8542AR-REEL7 –40°C to +125°C 8-Lead SOIC_N R-8

AD8542ARZ1 –40°C to +125°C 8-Lead SOIC_N R-8

AD8542ARZ-REEL1 –40°C to +125°C 8-Lead SOIC_N R-8

AD8542ARZ-REEL71 –40°C to +125°C 8-Lead SOIC_N R-8

AD8542ARM-R2 –40°C to +125°C 8-Lead MSOP RM-8 AVA

AD8542ARM-REEL –40°C to +125°C 8-Lead MSOP RM-8 AVA

AD8542ARMZ-R21 –40°C to +125°C 8-Lead MSOP RM-8 AVA#

AD8542ARMZ-REEL1 –40°C to +125°C 8-Lead MSOP RM-8 AVA#

AD8542ARU –40°C to +125°C 8-Lead TSSOP RU-8

AD8542ARU-REEL –40°C to +125°C 8-Lead TSSOP RU-8

AD8542ARUZ1 –40°C to +125°C 8-Lead TSSOP RU-8

AD8542ARUZ-REEL1 –40°C to +125°C 8-Lead TSSOP RU-8

AD8544AR –40°C to +125°C 14-Lead SOIC_N R-14

AD8544AR-REEL –40°C to +125°C 14-Lead SOIC_N R-14

AD8544AR-REEL7 –40°C to +125°C 14-Lead SOIC_N R-14

AD8544ARZ1 –40°C to +125°C 14-Lead SOIC_N R-14

AD8544ARZ-REEL1 –40°C to +125°C 14-Lead SOIC_N R-14

AD8544ARZ-REEL71 –40°C to +125°C 14-Lead SOIC_N R-14

AD8544ARU –40°C to +125°C 14-Lead TSSOP RU-14

AD8544ARU-REEL –40°C to +125°C 14-Lead TSSOP RU-14

AD8544ARUZ1 –40°C to +125°C 14-Lead TSSOP RU-14

AD8544ARUZ-REEL1 –40°C to +125°C 14-Lead TSSOP RU-14

1

Z = Pb-free part; # denotes lead-free product, may be top or bottom marked.

Option Branding

Rev. E | Page 17 of 20

Page 18

AD8541/AD8542/AD8544

NOTES

Rev. E | Page 18 of 20

Page 19

AD8541/AD8542/AD8544

NOTES

Rev. E | Page 19 of 20

Page 20

AD8541/AD8542/AD8544

NOTES

©2007 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

C00935-0-1/07(E)

Rev. E | Page 20 of 20

Loading...

Loading...