Page 1

Rail-to-Rail, High Output Current Amplifier

FEATURES

Dual operational amplifier

Voltage feedback

Wide supply range: from 3 V to 24 V

Rail-to-rail output

Output swing to within 0.5 V of supply rails

High linear output current

310 mA peak into 32 Ω on ±12 V supplies while maintaining

−80 dBc SFDR

Low noise

4.5 nV/√Hz voltage noise density @ 100 kHz

1.5 pA/√Hz current noise density @ 100 kHz

High speed

69 MHz bandwidth (G = 1, −3 dB)

53 V/µs slew rate (R

APPLICATIONS

Twisted-pair line drivers

Audio applications

General-purpose high current amplifiers

GENERAL DESCRIPTION

The AD8397 has two voltage feedback operational amplifiers

capable of driving heavy loads with excellent linearity. The

common-emitter, rail-to-rail output stage surpasses the output

voltage capability of typical emitter-follower output stages and

can swing to within 0.5 V of either rail while driving a 25 Ω

load. The low distortion, high output current, and wide output

dynamic range make the AD8397 ideal for applications that

require a large signal swing into a heavy load.

Fabricated with ADI’s high speed eXtra Fast Complementary

Bipolar High Voltage (XFCB-HV) process, the high bandwidth

and fast slew rate of the AD8397 keep distortion to a minimum

while also dissipating minimum power. The AD8397 is available

in a standard 8-lead SOIC package and, for higher power applications, a thermally enhanced 8-lead SOIC EPAD package. Both

packages can operate from −40°C to +85°C.

LOAD

= 25 Ω)

PIN CONFIGURATION

1

OUT1

2

–IN1

+IN1

3

–V

4

S

Figure 1. 8-Lead SOIC

1.50

1.25

1.00

0.75

0.50

0.25

(V)

0

OUT

–0.25

V

–0.50

–0.75

–1.00

–1.25

–1.50

0 2 4 6 8 10 12 14 16 18 20

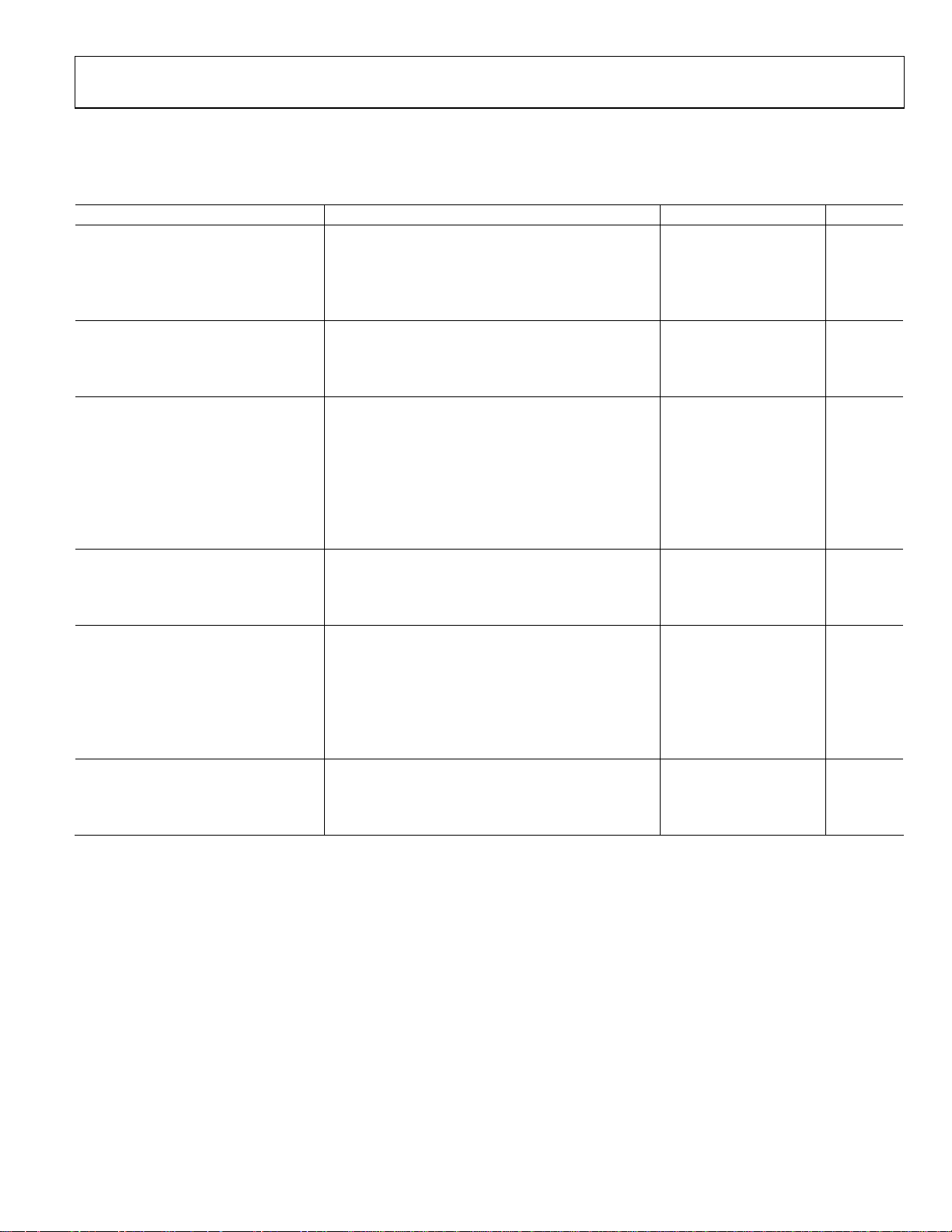

Figure 2. Output Swing, V

12

9

6

3

(V)

0

OUT

V

–3

–6

–9

–12

0 2 4 6 8 10 12 14 16 18 20

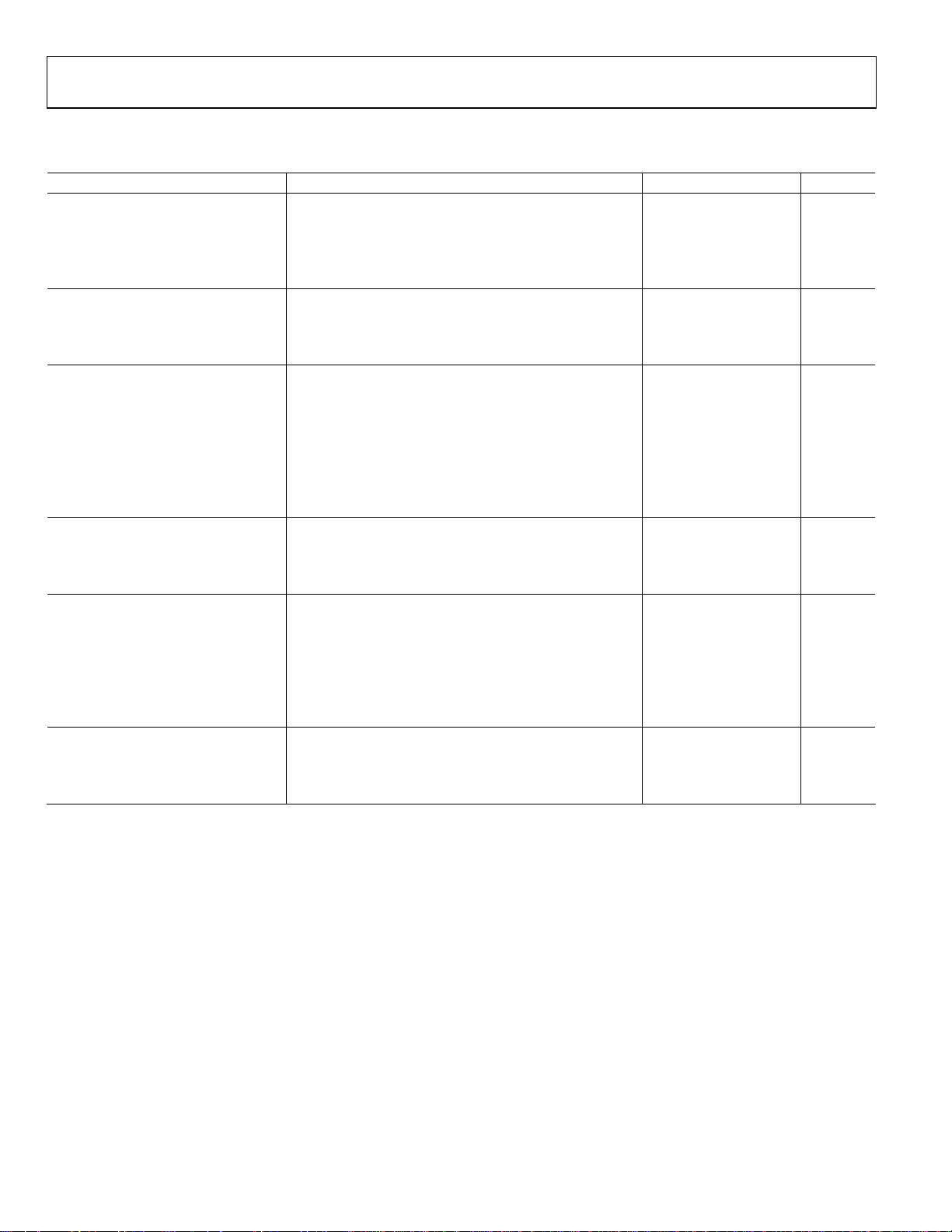

Figure 3. Output Swing, V

8

+V

7

OUT2

–IN2

6

+IN2

5

TIME (µs)

= ±1.5 V, RL = 25 Ω

S

TIME (µs)

= ±12 V, RL = 100 Ω

S

S

05069-001

AD8397

05069-031

05069-032

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

www.analog.com

Page 2

AD8397

TABLE OF CONTENTS

Specifications..................................................................................... 3

Power Supply and Decoupling ................................................. 11

Absolute Maximum Ratings............................................................ 7

Maximum Power Dissipation ..................................................... 7

ESD Caution.................................................................................. 7

Typical Performance Characteristics............................................. 8

General Description....................................................................... 11

REVISION HISTORY

1/05—Revision 0: Initial Version

Layout Considerations............................................................... 11

Unity-Gain Output Swing ......................................................... 11

Capacitive Load Drive ............................................................... 12

Outline Dimensions....................................................................... 13

Ordering Guide .......................................................................... 13

Rev. 0 | Page 2 of 16

Page 3

AD8397

SPECIFICATIONS

VS = ±1.5 V or +3 V (@ TA = 25°C, G = +1, RL = 25 Ω, unless otherwise noted).

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Bandwidth V

0.1 dB Flatness V

Large Signal Bandwidth V

Slew Rate V

NOISE/DISTORTION PERFORMANCE

Distortion (Worst Harmonic) fC = 100 kHz, V

Input Voltage Noise f = 100 kHz 4.5 nV/√Hz

Input Current Noise f = 100 kHz 1.5 pA/√Hz

DC PERFORMANCE

Input Offset Voltage 1.0 2.5 mV

T

Input Offset Voltage Match 1.0 2.0 mV

Input Bias Current 200 900 nA

T

Input Offset Current 50 300 nA

Open-Loop Gain V

INPUT CHARACTERISTICS

Input Resistance f = 100 kHz 87 kΩ

Input Capacitance 1.4 pF

Common-Mode Rejection ∆VCM = ±1 V −71 −80 dB

OUTPUT CHARACTERISTICS

Output Resistance 0.2 Ω

+Swing R

−Swing R

+Swing R

−Swing R

Maximum Output Current SFDR ≤ −70 dBc, f = 100 kHz, V

POWER SUPPLY

Operating Range (Dual Supply) ±1.5 ±12.0 V

Supply Current 6 7 8.5 mA/Amp

Power Supply Rejection ∆VS = ±0.5 V −70 −82 dB

= 0.1 V p-p 50 MHz

OUT

= 0.1 V p-p 3.6 MHz

OUT

= 2.0 V p-p 9 MHz

OUT

= 0.8 V p-p 32 V/µs

OUT

= 1.4 V p-p, G = +2 −90 dBc

OUT

− T

MIN

MAX

− T

MIN

MAX

= ±0.5 V 81 88 dB

OUT

= 25 Ω +1.39 +1.43 V

LOAD

= 25 Ω −1.4 −1.37 V

LOAD

= 100 Ω +1.45 +1.48 V

LOAD

= 100 Ω −1.47 −1.44 V

LOAD

= 0.7 VP, R

OUT

= 4.1 Ω 170 mA

LOAD

2.5 mV

1.3 µA

P

P

P

P

Rev. 0 | Page 3 of 16

Page 4

AD8397

VS = ±2.5V or +5 V (@ TA = 25°C, G = +1, RL = 25 Ω, unless otherwise noted).

Table 2.

Parameter Test Conditions/Comments Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Bandwidth V

0.1 dB Flatness V

Large Signal Bandwidth V

Slew Rate V

NOISE/DISTORTION PERFORMANCE

Distortion (Worst Harmonic) fC = 100 kHz, V

Input Voltage Noise f = 100 kHz 4.5 nV/√Hz

Input Current Noise f = 100 kHz 1.5 pA/√Hz

DC PERFORMANCE

Input Offset Voltage 1.0 2.4 mV

T

Input Offset Voltage Match 1.0 2.0 mV

Input Bias Current 200 900 nA

T

Input Offset Current 50 300 nA

Open-Loop Gain V

INPUT CHARACTERISTICS

Input Resistance f = 100 kHz 87 kΩ

Input Capacitance 1.4 pF

Common-Mode Rejection ∆VCM = ±1 V −76 −80 dB

OUTPUT CHARACTERISTICS

Output Resistance 0.2 Ω

+Swing R

−Swing R

+Swing R

−Swing R

Maximum Output Current SFDR ≤ −70 dBc, f = 100 kHz, V

POWER SUPPLY

Operating Range (Dual Supply) ±1.5 ±12.6 V

Supply Current 7 9 12 mA/Amp

Power Supply Rejection ∆VS = ±0.5 V −75 −85 dB

= 0.1 V p-p 60 MHz

OUT

= 0.1 V p-p 4.8 MHz

OUT

= 2.0 V p-p 14 MHz

OUT

= 2.0 V p-p 53 V/µs

OUT

= 2 V p-p, G = +2 −98 dBc

OUT

− T

MIN

MAX

− T

MIN

MAX

= ±1.0 V 85 90 dB

OUT

= 25 Ω +2.37 +2.42 V

LOAD

= 25 Ω −2.37 −2.32 V

LOAD

= 100 Ω +2.45 +2.48 V

LOAD

= 100 Ω −2.46 −2.42 V

LOAD

= 1.0 VP, R

OUT

= 4.3 Ω 230 mA

LOAD

2.5 mV

1.3 µA

P

P

P

P

Rev. 0 | Page 4 of 16

Page 5

AD8397

VS = ±5 V or +10 V (@ TA = 25°C, G = +1, RL = 25 Ω, unless otherwise noted).

Table 3.

Parameter Test Conditions/Comments Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Bandwidth V

0.1 dB Flatness V

Large Signal Bandwidth V

Slew Rate V

NOISE/DISTORTION PERFORMANCE

Distortion (Worst Harmonic) fC = 100 kHz, V

Input Voltage Noise f = 100 kHz 4.5 nV/√Hz

Input Current Noise f = 100 kHz 1.5 pA/√Hz

DC PERFORMANCE

Input Offset Voltage 1.0 2.5 mV

T

Input Offset Voltage Match 1.0 2.0 mV

Input Bias Current 200 900 nA

T

Input Offset Current 50 300 nA

Open-Loop Gain V

INPUT CHARACTERISTICS

Input Resistance f = 100 kHz 87 kΩ

Input Capacitance 1.4 pF

Common-Mode Rejection ∆VCM = ±1 V −84 −94 dB

OUTPUT CHARACTERISTICS

Output Resistance 0.2 Ω

+Swing R

−Swing R

+Swing R

−Swing R

Maximum Output Current SFDR ≤ −80 dBc, f = 100 kHz, V

POWER SUPPLY

Operating Range (Dual Supply) ±1.5 ±12.6 V

Supply Current 7 9 12 mA/Amp

Power Supply Rejection ∆VS = ±0.5 V −76 −85 dB

= 0.1 V p-p 66 MHz

OUT

= 0.1 V p-p 6.5 MHz

OUT

= 2.0 V p-p 14 MHz

OUT

= 4.0 V p-p 53 V/µs

OUT

= 6 V p-p, G = +2 −94 dBc

OUT

− T

MIN

MAX

− T

MIN

MAX

= ±2.0 V 85 94 dB

OUT

= 25 Ω +4.7 +4.82 V

LOAD

= 25 Ω −4.74 −4.65 V

LOAD

= 100 Ω +4.92 +4.96 V

LOAD

= 100 Ω −4.92 −4.88 V

LOAD

= 3 VP, R

OUT

= 12 Ω 250 mA

LOAD

2.5 mV

1.3 µA

P

P

P

P

Rev. 0 | Page 5 of 16

Page 6

AD8397

VS = ±12 V or +24 V (@ TA = 25°C, G = +1, RL = 25 Ω, unless otherwise noted).

Table 4.

Parameter Test Conditions/Comments Min Typ Max Unit

DYNAMIC PERFORMANCE

−3 dB Bandwidth V

0.1 dB Flatness V

Large Signal Bandwidth V

Slew Rate V

NOISE/DISTORTION PERFORMANCE

Distortion (Worst Harmonic) fC = 100 kHz, V

Input Voltage Noise f = 100 kHz 4.5 nV/√Hz

Input Current Noise f = 100 kHz 1.5 pA/√Hz

DC PERFORMANCE

Input Offset Voltage 1.0 3.0 mV

T

Input Offset Voltage Match 1.0 2.0 mV

Input Bias Current 200 900 nA

T

Input Offset Current 50 300 nA

Open-Loop Gain

INPUT CHARACTERISTICS

Input Resistance f = 100 kHz 87 kΩ

Input Capacitance 1.4 pF

Common-Mode Rejection VCM = ±1 V −85 −96 dB

OUTPUT CHARACTERISTICS

Output Resistance 0.2 Ω

+Swing R

−Swing R

Maximum Output Current SFDR ≤ −80 dBc, f = 100 kHz, V

POWER SUPPLY

Operating Range (Dual Supply) ±1.5 ±12.6 V

Supply Current 8.5 11 15 mA/Amp

Power Supply Rejection VS = ±0.5 V −76 −86 dB

= 0.1 V p-p 69 MHz

OUT

= 0.1 V p-p 7.6 MHz

OUT

= 2.0 V p-p 14 MHz

OUT

= 4.0 V p-p 53 V/µs

OUT

= 20 V p-p, G = +5 −84 dBc

OUT

− T

MIN

MAX

− T

MIN

MAX

= ±3.0 V

V

OUT

= 100 Ω +11.82 +11.89 V

LOAD

= 100 Ω −11.83 −11.77 V

LOAD

= 10 VP, R

OUT

= 32 Ω 310 mA

LOAD

2.5 mV

1.3 µA

90 96 dB

P

P

Rev. 0 | Page 6 of 16

Page 7

AD8397

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter Rating

Supply Voltage 26.4 V

Power Dissipation

1

See Figure 4

Storage Temperature −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Lead Temperature Range

300°C

(Soldering 10 sec)

Junction Temperature 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

1

Thermal resistance for standard JEDEC 4-layer board:

8-lead SOIC: θ

8-Lead SOIC EPAD: θ

= 157.6°C/W

JA

= 47.2°C/W

JA

MAXIMUM POWER DISSIPATION

The maximum power that can be dissipated safely by

the AD8397 is limited by the associated rise in junction

temperature. The maximum safe junction temperature for

plastic encapsulated devices is determined by the glass

transition temperature of the plastic, approximately 150°C.

Temporarily exceeding this limit may cause a shift in

parametric performance due to a change in the stresses

exerted on the die by the package.

4.5

4.0

3.5

3.0

2.5

2.0

1.5

1.0

MAXIMUM POWER DISSIPATION (W)

0.5

0

–40–30–20–100 102030405060708090

Figure 4. Maximum Power Dissipation vs. Temperature

8-LEAD SOIC EPAD

8-LEAD SOIC

AMBIENT TEMPERATURE (°C)

TJ = 150°C

05069-020

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate

on the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation

or loss of functionality.

Rev. 0 | Page 7 of 16

Page 8

AD8397

TYPICAL PERFORMANCE CHARACTERISTICS

100

80

60

40

20

0

–20

OUTPUT (mV)

–40

–60

–80

–100

0 20 40 60 80 100 120 140 160 180 200

Figure 5. Small Signal Pulse Response (G = +1, V

V

OUT

V

IN

05069-029

TIME (ns)

= ±5 V, RL = 25 Ω)

S

0

–10

–20

–30

–40

–50

CMRR (dB)

–60

–70

–80

–90

0.01 0.1 1 10 100

FREQUENCY (MHz)

OUT 1

OUT 2

Figure 8. Common -Mode Rejection v s. Frequenc y

= ±5 V, RL = 25 Ω)

(V

S

05069-005

5

4

V

IN

3

2

OUTPUT (V)

1

0

–1

0 2.01.81.61.41.21.00.80.60.40.2

Figure 6. Large Signal Pulse Response (0 V to 4 V, V

3.0

2.5

2.0

1.5

1.0

INPUT (V)

0.5

0

–0.5

–1.0

0 40 80 120 160 200 240 280 320 360 400

V

V

OUT

TIME (µs)

= ±5 V, RL = 25 Ω)

S

IN

TIME (ns)

V

OUT

Figure 7. Output Overdrive Recovery

= ±5 V, Gain = +2, RL = 25 Ω)

(V

S

6

5

4

3

2

1

0

–1

–2

05069-022

OUTPUT (V)

05069-004

0

–10

–20

–30

–40

–50

–60

–70

CROSSTALK (dB)

–80

–90

–100

–110

0.01 0.1 1 10 100

OUT 1

OUT 2

FREQUENCY (MHz)

Figure 9. Output-to-Output Crosstalk vs. Frequency

= ±5 V, VO = 1 V p-p, RL = 25 Ω)

(V

S

0.3

0.2

0.1

0

GAIN (dB)

–0.1

–0.2

–0.3

0.1 1 10

FREQUENCY (MHz)

VO = 100mV p-p

Figure 10. 0.1 dB Flatness

= ±5 V, VO = 0.1 V p-p, Gain = +1, RL = 25 Ω)

(V

S

05069-006

05069-007

Rev. 0 | Page 8 of 16

Page 9

AD8397

10

G = +1

10

0

G = +2

–10

–20

NORMALIZED GAIN (dB)

–30

–40

0.01 1001010.1

FREQUENCY (MHz)

G = +10

Figure 11. Small Signal Frequency Response for Various Gains

= ±5 V, VO = 0.1 V p-p, RL = 25 Ω)

(V

S

10

0

–10

GAIN (dB)

–20

–30

–40

0.01 1001010.1

FREQUENCY (MHz)

12V

5V

2.5V

Figure 12. Small Signal Frequency Response for Various Supplies

(Gain = +1, V

= 0.1 V p-p, RL = 25 Ω)

O

05069-008

05069-009

0

–10

–20

NORMALIZED GAIN (dB)

–30

–40

0.01 0.1 1 10 100

FREQUENCY (MHz)

G = +1

G = +2

G = +10

Figure 14. Large Signal Frequency Response for Various Gains

= ±5 V, VO = 2 V p-p, RL = 25 Ω)

(V

S

20

10

0

–10

GAIN (dB)

–20

–30

–40

0.01 0.1 1 10 100

FREQUENCY (MHz)

12V

2.5V

5V

Figure 15. Large Signal Frequency Response for Various Supplies

(Gain = +1, V

= 2 V p-p, RL = 25 Ω)

O

05069-011

05069-012

100

80

60

40

20

0

OPEN-LOOP GAIN (dB)

–20

–40

0.001 0.01 0.1 1 10 100 1000

FREQUENCY (MHz)

GAIN

PHASE

Figure 13. Open Loop Gain and Phase vs. Frequency

= ±5 V, RL = 25 Ω)

(V

S

135

90

45

0

–45

PHASE (Degrees)

–90

–135

05069-010

–180

Rev. 0 | Page 9 of 16

0

–10

–20

–30

–40

PSRR (dB)

–50

–60

–70

–80

0.01 0.1 1

+PSRR

Figure 16. Power Supply Rejection

(V

–PSRR

FREQUENCY (MHz)

= ±5 V, RL = 25 Ω)

S

10 100

05069-013

Page 10

AD8397

0

–10

–20

–30

–40

–50

–60

–70

–80

DISTORTION (dBc)

–90

–100

–110

–120

0.01 1010.1

–40

SECOND

HARMONIC

THIRD

HARMONIC

FREQUENCY (MHz)

Figure 17. Distortion vs. Frequency

= ±5 V, VO = 2 V p-p, G = +2, RL = 25 Ω)

(V

S

05069-023

–40

–50

–60

–70

–80

–90

DISTORTION (dBc)

–100

–110

–120

012345678910

SECOND

HARMONIC

THIRD

HARMONIC

OUTPUT VOLTAGE (V p-p)

Figure 20. Distortion vs. Output Voltage @ 100 kHz,

= ±5 V, G = +2, RL = 25 Ω)

(V

S

–40

05069-026

–50

–60

–70

–80

–90

DISTORTION (dBc)

–100

–110

–120

0 0.25 0.50 0.75 1.00 1.25 1.50 1.75 2.00 2.25 2.50 2.75

SECOND

HARMONIC

THIRD

HARMONIC

OUTPUT VOLTAGE (V p-p)

Figure 18. Distortion vs. Output Voltage @ 100 kHz,

= ±1.5 V, G = +2, RL = 25 Ω)

(V

S

–40

–50

–60

–70

–80

–90

DISTORTION (dBc)

–100

SECOND

HARMONIC

05069-024

–50

–60

–70

–80

–90

DISTORTION (dBc)

–100

–110

–120

SECOND

HARMONIC

THIRD

HARMONIC

0 2 4 6 8 10 12 14 16 18 20 22 24

OUTPUT VOLTAGE (V p-p)

Figure 21. Distortion vs. Output Voltage @ 100 kHz,

= ±12 V, G = +5, RL = 50 Ω)

(V

S

05069-027

–110

–120

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

OUTPUT VOLTAGE (V p-p)

THIRD

HARMONIC

05069-025

Figure 19. Distortion vs. Output Voltage @ 100 kHz,

= ±2.5 V, G = +2, RL = 25 Ω)

(V

S

Rev. 0 | Page 10 of 16

Page 11

AD8397

GENERAL DESCRIPTION

The AD8397 is a voltage feedback operational amplifier which

features an H-bridge input stage and common-emitter, rail-torail output stage. The AD8397 can operate from a wide supply

range, ±1.5 V to ±12 V. When driving light loads, the rail-to-rail

output is capable of swinging to within 0.2 V of either rail. The

output can also deliver high linear output current when driving

heavy loads, up to 310 mA into 32 Ω while maintaining −80 dBc

SFDR. The AD8397 is fabricated on Analog Devices’ proprietary

eXtra Fast Complementary Bipolar High Voltage process

(XFCB-HV).

POWER SUPPLY AND DECOUPLING

The AD8397 can be powered with a good quality, wellregulated, low noise supply from ±1.5 V to ±12 V. Careful

attention should be paid to decoupling the power supply. High

quality capacitors with low equivalent series resistance (ESR),

such as multilayer ceramic capacitors (MLCCs), should be used

to minimize the supply voltage ripple and power dissipation. A

0.1 µF MLCC decoupling capacitor(s) should be located no

more than 1/8 inch away from the power supply pin(s). A large

tantalum 10 µF to 47 µF capacitor is recommended to provide

good decoupling for lower frequency signals and to supply

current for fast, large signal changes at the AD8397 outputs.

LAYOUT CONSIDERATIONS

As with all high speed applications, careful attention should be

paid to printed circuit board (PCB) layout in order to prevent

associated board parasitics from becoming problematic. The

PCB should have a low impedance return path (or ground) to

the supply. Removing the ground plane from all layers in the

immediate area of the amplifier helps to reduce stray capacitances. The signal routing should be short and direct in order to

minimize the parasitic inductance and capacitance associated

with these traces. Termination resistors and loads should be

located as close as possible to their respective inputs and

outputs. Input traces should be kept as far apart as possible

from the output traces to minimize coupling (crosstalk) though

the board.

When the AD8397 is configured as a differential driver, as in

some line driving applications, a symmetrical layout should be

provided to the extent possible in order to maximize balanced

performance. When running differential signals over a long

distance, the traces on the PCB should be close together or

any differential wiring should be twisted together to minimize

the area of the inductive loop that is formed. This reduces the

radiated energy and makes the circuit less susceptible to RF

interference. Adherence to stripline design techniques for

long signal traces (greater than approximately 1 inch) is

recommended.

UNITY-GAIN OUTPUT SWING

When operating the AD8397 in a unity-gain configuration,

the output does not swing to the rails and is constrained by

the H-bridge input. This can be seen by comparing the output

overdrive recovery in Figure 7 and the input overdrive recovery

in Figure 22. To avoid overdriving the input and to realize the

full swing afforded by the rail-to-rail output stage, the amplifier

should be used in a gain of two or greater.

7

6

INPUT

OUTPUT

0 80 160 240 320 400

Figure 22. Unity-Gain Input Overdrive Recovery

480 560 640 720 800

TIME (ns)

05069-028

VOLTS

–1

5

4

3

2

1

0

Rev. 0 | Page 11 of 16

Page 12

AD8397

CAPACITIVE LOAD DRIVE

When driving capacitive loads, many high speed operational

amplifiers exhibit peaking in their frequency response. In a

gain-of-two circuit, Figure 23 shows that the AD8397 can drive

capacitive loads up to 270 pF with only 3 dB of peaking. For

amplifiers with more limited capacitive load drive, a small series

resistor (R

the capacitive load in order to minimize peaking and ensure

device stability. Figure 24 shows that the use of a 2.2 Ω series

resistor can further extend the capacitive load drive of the

AD8397 out to 470 pF, while keeping the frequency response

peaking to within 3 dB.

) is generally used between the amplifier output and

S

5

0

–5

–10

–15

–20

GAIN (dB)

–25

–30

–35

–40

0.01 0.1 1 10 100

FREQUENCY (MHz)

220pF

150pF

100pF

Figure 23. Capacitive Load Peaking Without Series Resistor

270pF

05069-021

5

0

–5

–10

–15

–20

GAIN (dB)

–25

–30

–35

–40

0.01 0.1 1 10 100

FREQUENCY (MHz)

Figure 24. Capacitive Load Peaking with 2.2 Ω Series Resistor

390pF

270pF

470pF

330pF

05069-030

Rev. 0 | Page 12 of 16

Page 13

AD8397

Y

OUTLINE DIMENSIONS

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

85

6.20 (0.2440)

5.80 (0.2284)

41

1.27 (0.0500)

BSC

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012AA

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

8°

1.27 (0.0500)

0°

0.40 (0.0157)

× 45°

Figure 25. 8-Lead Standard Small Outline Package [SOIC]

Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

5.00 (0.197)

4.90 (0.193)

4.00 (0.157)

3.90 (0.154)

3.80 (0.150)

0.25 (0.0098)

0.10 (0.0039)

COPLANARIT

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETER; INCHES DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

4.80 (0.189)

85

TOP VIEW

1.27 (0.05)

BSC

1.75 (0.069)

1.35 (0.053)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-AA

6.20 (0.244)

6.00 (0.236)

41

5.80 (0.228)

0.51 (0.020)

0.31 (0.012)

BOTTOM VIEW

0.25 (0.0098)

0.17 (0.0068)

(PINS UP)

8°

0°

3.098 (0.122)

0.50 (0.020)

0.25 (0.010)

1.27 (0.050)

0.40 (0.016)

2.41 (0.095)

× 45

Figure 26. 8-Lead Standard Small Outline Package with Exposed Pad [SOIC_N_EP]

Narrow Body (RD-8-2)

Dimensions shown in millimeters and (inches)

ORDERING GUIDE

Model Temperature Package Package Description Package Outline

AD8397ARZ

AD8397ARZ-REEL1 −40°C to +85°C 8-Lead SOIC R-8

AD8397ARZ-REEL71 −40°C to +85°C 8-Lead SOIC R-8

AD8397ARDZ1 −40°C to +85°C 8-Lead SOIC-EPAD RD-8-2

AD8397ARDZ-REEL1 −40°C to +85°C 8-Lead SOIC-EPAD RD-8-2

AD8397ARDZ-REEL71 −40°C to +85°C 8-Lead SOIC-EPAD RD-8-2

1

Z = Pb-free part.

1

−40°C to +85°C 8-Lead SOIC R-8

Rev. 0 | Page 13 of 16

Page 14

AD8397

Rev. 0 | Page 14 of 16

Page 15

AD8397

NOTES

Rev. 0 | Page 15 of 16

Page 16

AD8397

NOTES

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05069–0–1/05(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...