Analog Devices AD8381AST-REEL, AD8381AST Datasheet

a

Fast, High Voltage Drive, 6-Channel Output

TM

DecDriver

Decimating LCD Panel Driver

AD8381

FEATURES

High Voltage Drive:

Rated Settling Time to within 1.3 V of Supply Rails

Output Overload Protection

High Update Rates:

Fast, 100 Ms/s 10-Bit Input Word Rate

Low Power Dissipation: 570 mW

Includes STBY Function

Voltage Controlled Video Reference (Brightness) and

Full-Scale (Contrast) Output Levels

3.3 V or 5 V Logic and 9 V–18 V Analog Supplies

High Accuracy:

Laser Trimming Eliminates External Calibration

Flexible Logic:

INV Reverses Polarity of Video Signal

STSQ/XFR for Parallel AD8381 Operation in

12-Channel Systems

Drives Capacitive Loads:

27 ns Settling Time to 1% into 150 pF Load

Slew Rate 265 V/s with 150 pF Load

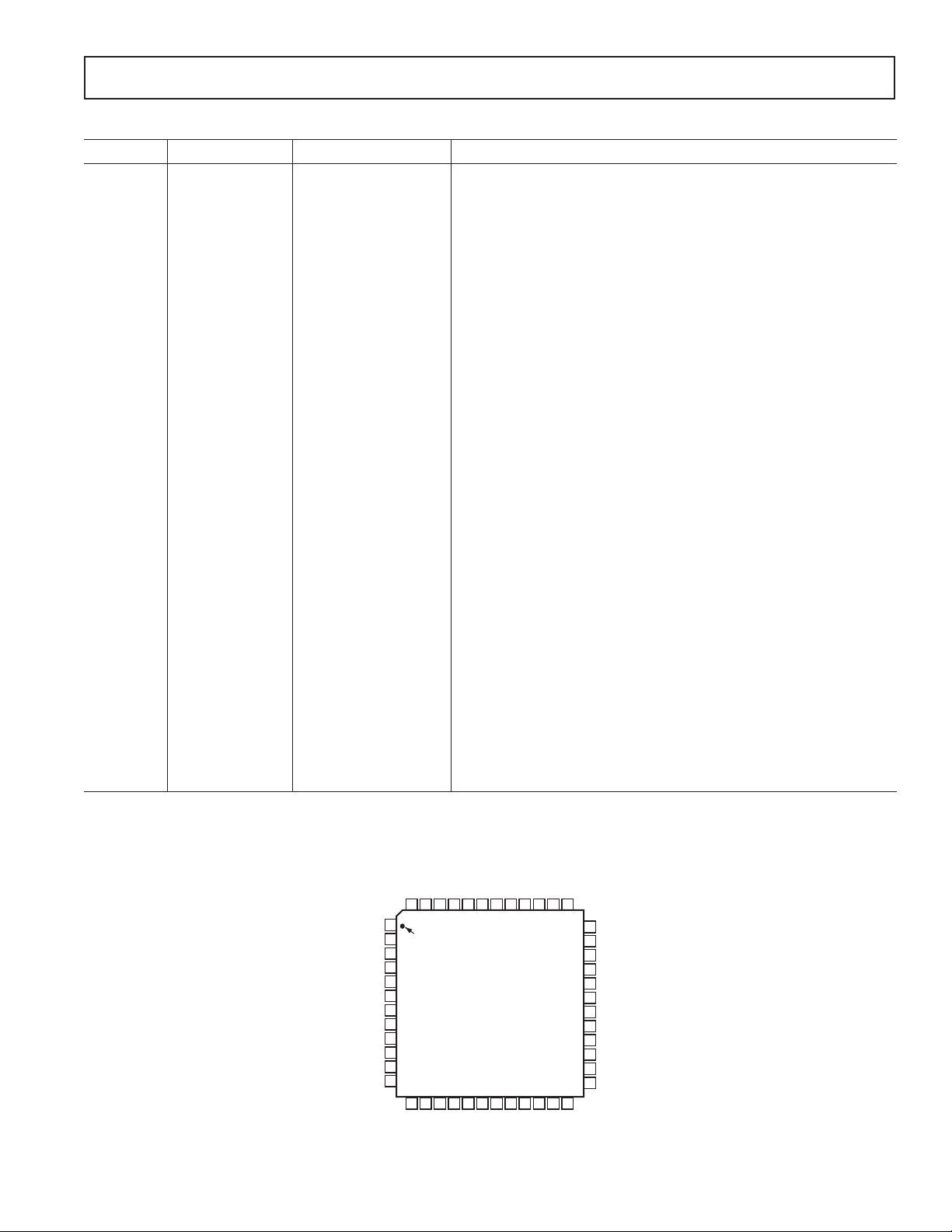

Available in 48-Lead LQFP

APPLICATIONS

LCD Analog Column Driver

PRODUCT DESCRIPTION

The AD8381 provides a fast, 10-bit latched decimating digital

input, which drives six high voltage outputs. Ten-bit input

words are sequentially loaded into six separate high-speed, bipolar

DACs. Flexible digital input format allows several AD8381s to be

used in parallel for higher resolution displays. STSQ synchronizes

sequential input loading, XFR controls synchronous output

updating and R/L controls the direction of loading as either

Left to Right or Right to Left. Six channels of high voltage

output drivers drive to within 1.3 V of the rail in rated settling

time. The output signal can be adjusted for brightness, signal

inversion and contrast for maximum flexibility.

The AD8381 is fabricated on ADI’s proprietary, fast bipolar

24 V process, providing fast input logic, bipolar DACs with

trimmed accuracy and fast settling, high voltage precision drive

amplifiers on the same chip.

The AD8381 dissipates 570 mW nominal static power. STBY

pin reduces power to a minimum, with fast recovery.

The AD8381 is offered in a 48-lead 7 × 7 × 1.4 mm LQFP

package and operates over the commercial temperature range of

0°C to 85°C.

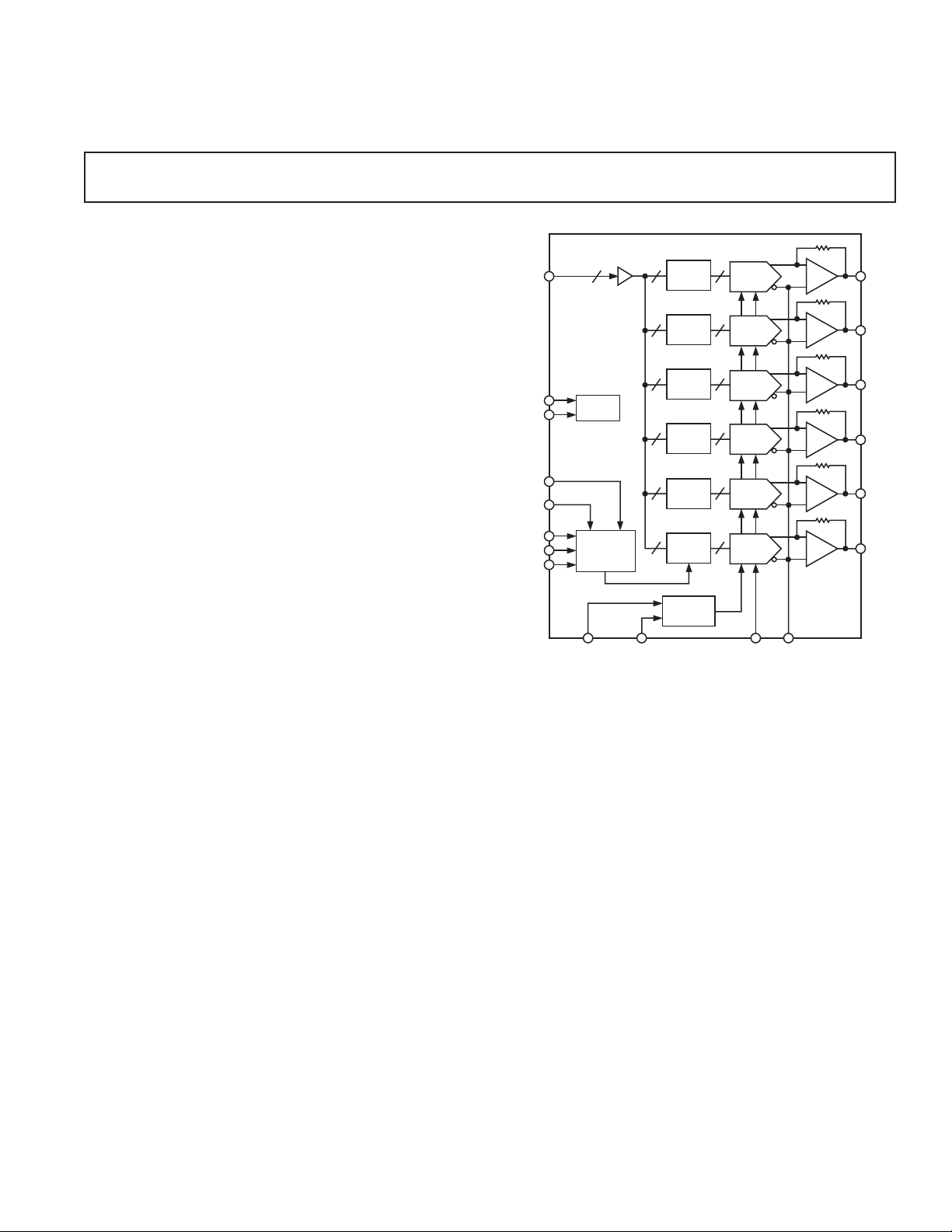

DB (0:9)

STBY

BYP

E/O

L/R

CLK

STSQ

XFR

FUNCTIONAL BLOCK DIAGRAM

10

AD8381

BIAS

SEQUENCE

CONTROL

VREFHI VREFLO INV VMID

10

10

10

10

10

10

CONTROL

2-STAGE

LATCH

2-STAGE

LATCH

2-STAGE

LATCH

2-STAGE

LATCH

2-STAGE

LATCH

2-STAGE

LATCH

SCALING

10

DAC

10

DAC

10

DAC

10

DAC

10

DAC

10

DAC

VID0

VID1

VID2

VID3

VID4

VID5

DecDriver is a trademark of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

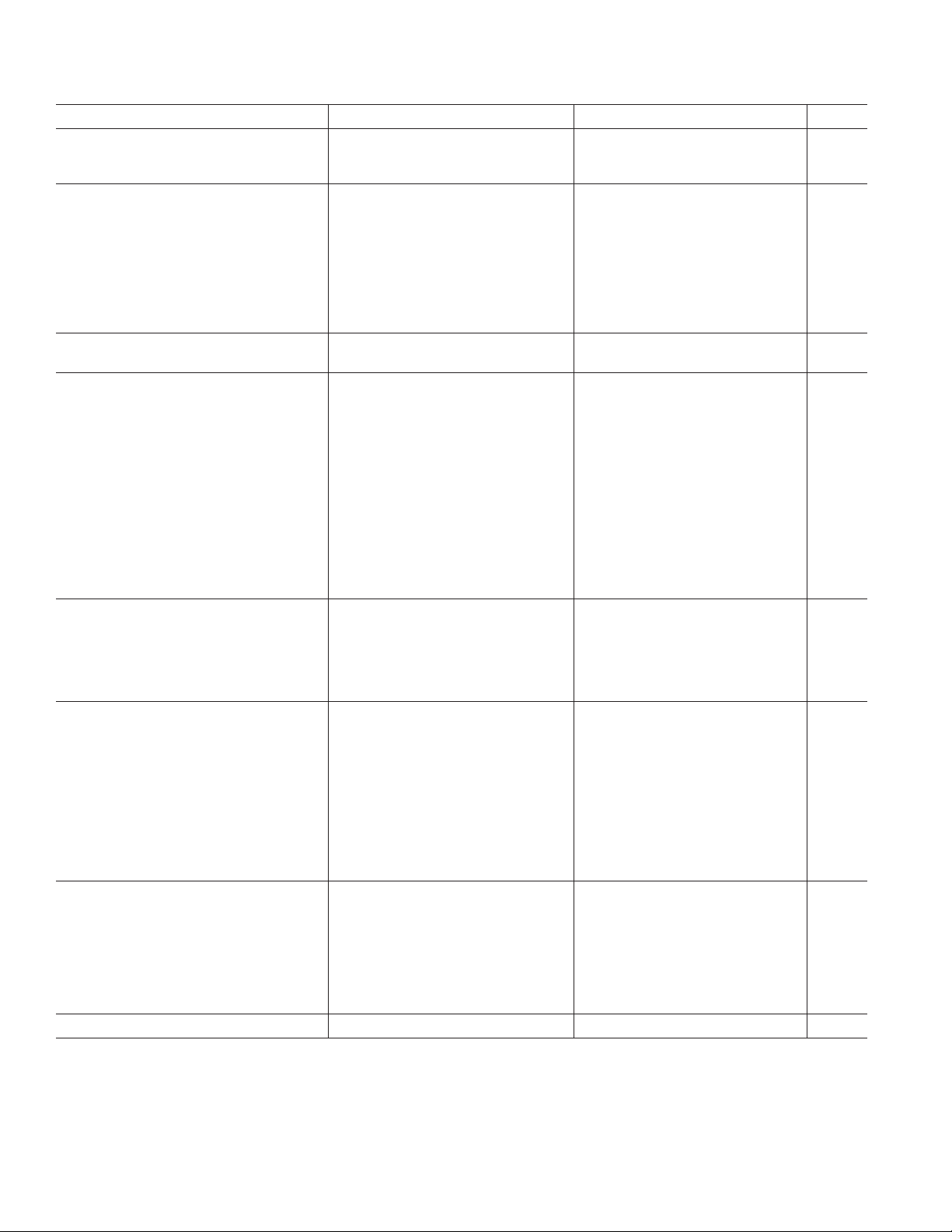

(@ 25ⴗC, AVCC = 15.5 V, DVCC = 3.3 V, VREFLO = VMID = 7 V, VREFHI = 9.5 V,

T

AD8381–SPECIFICATIONS

= 0ⴗC, T

MIN

Model Conditions Min Typ Max Unit

VIDEO DC PERFORMANCE

1

T

to T

MIN

MAX

VDE DAC Code 450 to 800 –7.5 +1.0 +7.5 mV

VCME DAC Code 450 to 800 –3.5 +0.5 +3.5 mV

REFERENCE INPUTS (VREFHI–VREFLO) = 2.5 V

VMID Range

2

VMID Bias Current 35 77 µA

VREFHI VREFLO AVCC V

VREFLO VMID – 0.5 VREFHI V

VREFHI Input Resistance to VREFLO 20 kΩ

VREFLO Bias Current 0.01 0.07 µA

VREFHI Input Current 125 165 µA

VFS Range

3

RESOLUTION

Coding Binary 10 Bits

DIGITAL INPUT CHARACTERISTICS CLK Rise and Fall Time = 5 ns

Input Data Update Rate NRZ 100 Ms/s

CLK to Data Setup Time: t

CLK to STSQ Setup Time: t

CLK to XFR Setup Time: t

CLK to Data Hold Time: t

CLK to STSQ Hold Time: t

CLK to XFR Hold Time: t

C

IN

I

IH

I

IL

V

IH

V

IL

V

TH

1

3

5

2

4

6

Threshold Voltage 1.4 V

VIDEO OUTPUT CHARACTERISTICS

Output Voltage Swing AVCC – VOH, VOL – AGND 1 1.3 V

CLK to VID Delay4: t

7

50% of VIDx 13.5 15.5 17.5 ns

INV to VID Delay 50% of VIDx 12 14 16 ns

Output Current 30 75 mA

Output Resistance 29 Ω

VIDEO OUTPUT DYNAMIC PERFORMANCE T

MIN

to T

, VO = 5 V Step, CL = 150 pF

MAX

Data Switching Slew Rate 265 V/µs

Invert Switching Slew Rate 410 V/µs

Data Switching Settling Time to 1% 27 32 ns

Data Switching Settling Time to 0.25% 50 75 ns

Invert Switching Settling Time to 1% 33 40 ns

Invert Switching Settling Time to 0.25% 55 100 ns

CLK and Data Feedthrough

All-Hostile Crosstalk

5

6

Amplitude 50 mV p-p

Glitch Duration 45 ns

POWER SUPPLY

Supply Rejection (VDE) AVCCx = +15.5 V ± 1 V 0.6 mV/V

DVCC, Operating Range 3 5.5 V

DVCC, Quiescent Current 18 25 mA

AVCC, Operating Range 918V

Total AVCC Quiescent Current 33 40 mA

STBY AVCC Current STBY = H 1.8 3 mA

STBY DVCC Current STBY = H 0.03 0.1 mA

OPERATING TEMPERATURE RANGE 0 85 °C

NOTES

1

VDE = Differential Error Voltage. VCME = Common-Mode Error Voltage. See the Functional Description section.

2

See Figure 6 in the Functional Description section.

3

VFS = 2 × (VREFHI–VREFLO). See Functional Description section.

4

Measured from 50% of falling CLK edge to 50% of output change. Measurement is made for both states of INV.

5

Measured on one output as CLK is driven and STSQ and XFR are held LOW.

6

Measured on one output as the other five are changing from 000

Specifications subject to change without notice.

HEX

to 3FF

= 85ⴗC, unless otherwise noted.)

MAX

for both states of INV.

HEX

6.25 9.25 V

0 5.75 V

0ns

0ns

0ns

5ns

5ns

5ns

3pF

0.6 0.7 µA

0.05 0.16 µA

2.0 V

0.08 V

5 mV p-p

–2–

REV. 0

AD8381

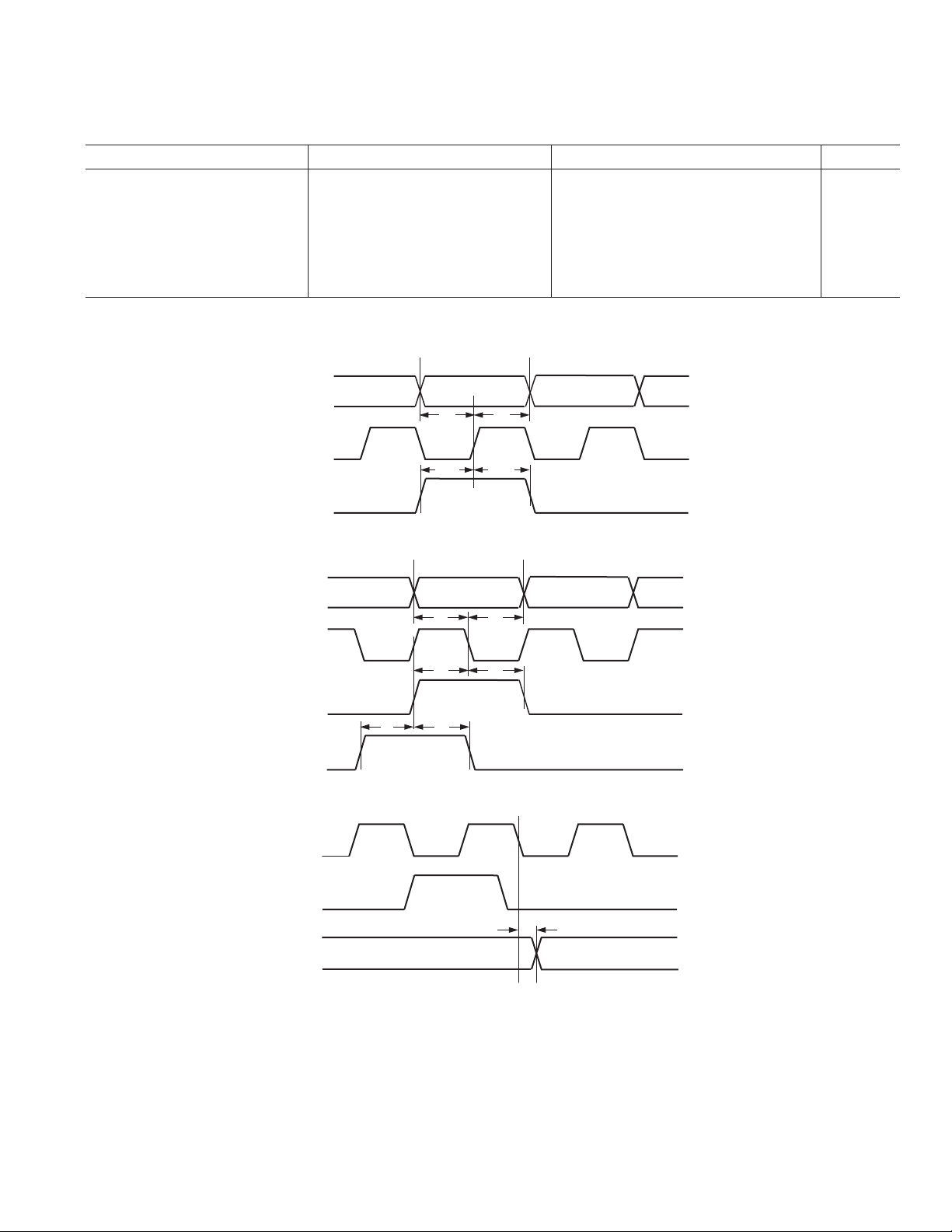

TIMING CHARACTERISTICS

Parameter Conditions Min Typ Max Unit

CLK to Data Setup Time CLK Rise and Fall Time = 5 ns 0 ns

t

1

t2CLK to Data Hold Time CLK Rise and Fall Time = 5 ns 5 ns

CLK to STSQ Setup Time CLK Rise and Fall Time = 5 ns 0 ns

t

3

CLK to STSQ Hold Time CLK Rise and Fall Time = 5 ns 5 ns

t

4

t5CLK to XFR Setup Time CLK Rise and Fall Time = 5 ns 0 ns

CLK to XFR Hold Time CLK Rise and Fall Time = 5 ns 5 ns

t

6

t7CLK to VID Delay 13.5 15.5 17.5 ns

DB (0:9)

CLK

STSQ, XFR

DB (0:9)

CLK

STSQ

XFR

–1 0

t3,t

t

1

t

2

t4,t

5

6

Figure 1. Timing Requirement E/O = HIGH

–1

t

1

t

3

t

5

t

6

t

2

t

4

0

Figure 2. Timing Requirements E/O = LOW

REV. 0

CLK

XFR

VIDx

t

7

Figure 3. Output Timing

–3–

AD8381

ABSOLUTE MAXIMUM RATINGS

1

Supply Voltages

AVCCx – AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 V

DVCC – DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5 V

Input Voltages

Maximum Digital Input Voltages . . . . . . . . DVCC + 0.5 V

Minimum Digital Input Voltages . . . . . . . . DGND – 0.5 V

Maximum Analog Input Voltages . . . . . . . . . AVCC + 0.5 V

Minimum Analog Input Voltages . . . . . . . . AGND – 0.5 V

Internal Power Dissipation

2

LQFP Package @ 25°C Ambient . . . . . . . . . . . . . . . . 2.7 W

Output Short Circuit Duration . . . . . . . . . . . . . . . . . . Infinite

Operating Temperature Range . . . . . . . . . . . . . . 0°C to 85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +125°C

Lead Temperature Range (Soldering 10 sec) . . . . . . . . 300°C

NOTES

1

Stresses above those listed under the Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those indicated in the

operational section of this specification is not implied. Exposure to the absolute

maximum ratings for extended periods may reduce device reliability.

2

48-lead LQFP Package:

θJA = 45°C/W (Still Air, 4-Layer PCB)

θJC = 19°C/W

Overload Protection

The AD8381 employs a two-stage overload protection circuit

that consists of an output current limiter and a thermal shutdown.

The maximum current at any one output of the AD8381 is

internally limited to 100 mA average. In the event of a momentary short-circuit between a video output and a power supply rail

(VCC or AGND), the output current limit is sufficiently low to

provide temporary protection.

The thermal shutdown “debiases” the output amplifier when the

junction temperature reaches the internally set trip point. In the

event of an extended short-circuit between a video output and a

power supply rail, the output amplifier current continues to

switch between 0 mA and 100 mA typ with a period determined by

the thermal time constant and the hysteresis of the thermal trip

point. The thermal shutdown provides long term protection by

limiting the average junction temperature to a safe level.

Recovery from a momentary short-circuit is fast, approximately

100 ns. Recovery from a thermal shutdown is slow and is

dependent on the ambient temperature.

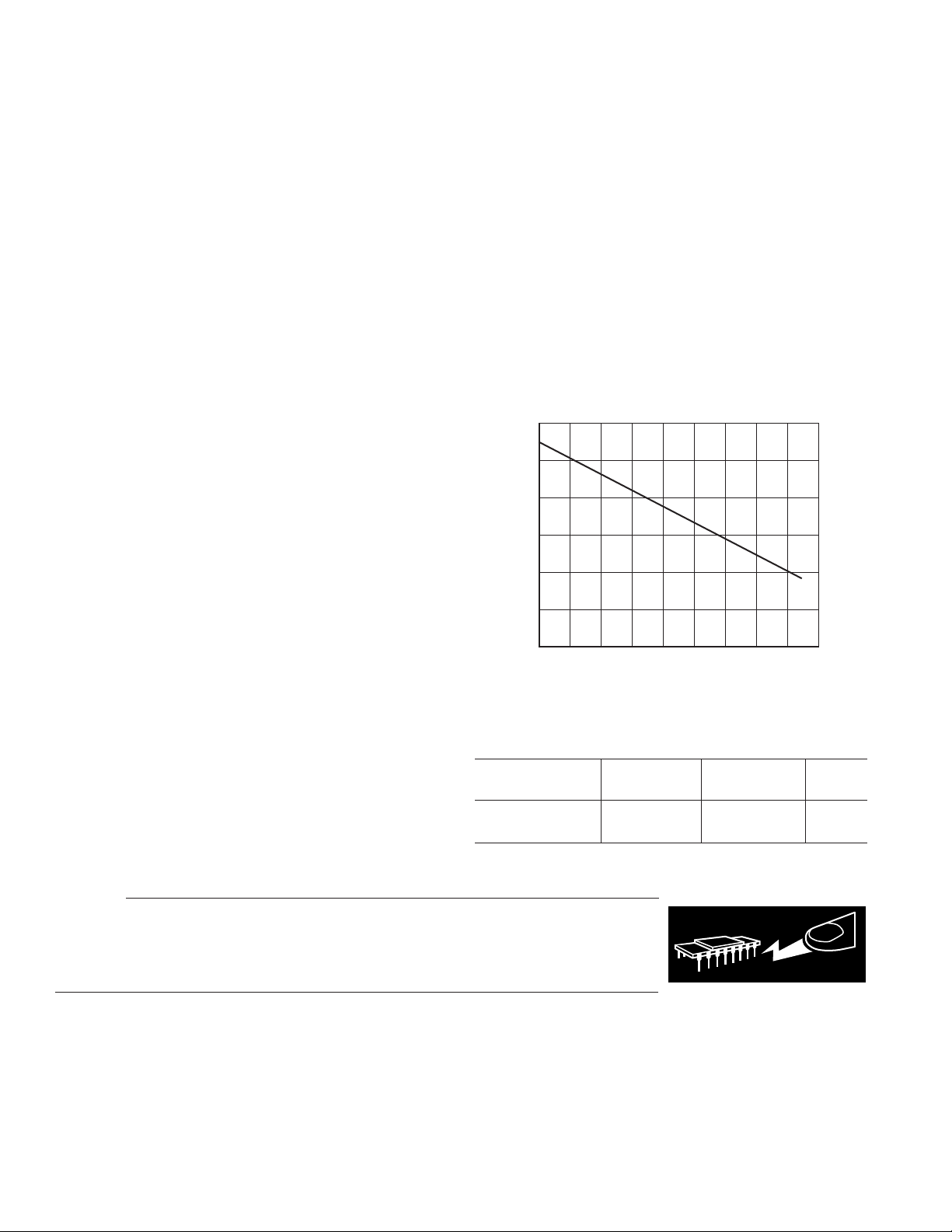

MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD8381

is limited by its junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined

by the glass transition temperature of the plastic, approximately

150°C. Exceeding this limit temporarily may cause a shift in the

parametric performance due to a change in the stresses exerted

on the die by the package. Exceeding a junction temperature of

175°C for an extended period can result in device failure.

To ensure proper operation within the specified operating temperature range, it is necessary to limit the maximum power

dissipation as follows:

P

DMAX

= (T

JMAX

– TA)/θ

JA

where

T

= 150°C.

JMAX

3.5

3.0

2.5

2.0

1.5

1.0

MAXIMUM POWER DISSIPATION – W

0.5

0

10 20 30 40 50 60 70 80 90

AMBIENT TEMPERATURE – ⴗC

Figure 4. Maximum Power Dissipation vs. Temperature

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD8381AST 0°C to 85°C 48-Lead LQFP ST-48

AD8381AST-REEL

Reel

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD8381 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–4–

WARNING!

ESD SENSITIVE DEVICE

REV. 0

AD8381

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function Description

1, 12, 19, 23, NC No Connect

24, 43–45

2–11 DB (0:9) Data Input 10-Bit Data Input MSB = DB (9).

13 E/O Even/Odd Select The active CLK edge is the rising edge when this input is held HIGH

and it is the falling edge when this input is held LOW.

Data is loaded sequentially on the rising edges of CLK when this input

is HIGH and loaded on the falling edges when this input is LOW.

14 R/L Right/Left Select A new data loading sequence begins on the left, with Channel 0, when this

input is LOW, and on the right, with Channel 5 when this input is HIGH.

15 INV Invert When this pin is HIGH, the analog output voltages are above VMID.

When LOW, the analog output voltages are below VMID.

16 DGND Digital Supply Return This pin is normally connected to the analog ground plane.

17 DVCC Digital Power Supply Digital Power Supply.

18, 27, 31, AVCCx Analog Power Supplies Analog Power Supplies.

35, 42

20 STBY Standby When HIGH, the internal circuits are “debiased” and the power

dissipation drops to a minimum.

21 BYP Bypass A 0.1 µF capacitor connected between this pin and AGND ensures

optimum settling time.

22, 25, 29, AGNDx Analog Supply Returns These pins are normally connected to the analog ground plane.

33, 37, 41

26, 28, 30, VID5, VID4, VID3, Analog Outputs These pins are directly connected to the analog inputs of the LCD panel.

32, 34, 36 VID2, VID1, VID0

38 VMID Midpoint Reference The voltage applied between this pin and AGND sets the midpoint

reference of the analog outputs. This pin is normally connected to VCOM.

39 VREFLO Full-Scale Reference The voltage applied between Pins 39 and 40 sets the full-scale output voltage.

40 VREFHI Full-Scale Reference The voltage applied between Pins 39 and 40 sets the full-scale output voltage.

46 STSQ Start Sequence A new data loading sequence begins on the rising edge of CLK when

this input was HIGH on the preceding rising edge of CLK and the E/O

input is held HIGH.

A new data loading sequence begins on the falling edge of CLK when

this input was HIGH on the preceding falling edge of CLK and the E/O

input is held LOW.

47 XFR Data Transfer Data is transferred to the outputs on the immediately following falling

edge of CLK when this input is HIGH on the rising edge of CLK.

48 CLK Clock Clock Input.

REV. 0

48

1

NC

2

DB0

3

DB1

4

DB2

5

DB3

6

DB4

7

DB5

8

DB6

9

DB7

10

DB8

11

DB9

12

NC

13 14

NC = NO CONNECT

PIN CONFIGURATION

VMID

VREFLO

VREFHI

AGNDDAC

AV CC DAC

NC

NC

NC

STSQ

XFR

CLK

47 46

45 44 39 38 3743 42 41 40

PIN 1

IDENTIFIER

AD8381

TOP VIEW

(Not to Scale)

E/O

R/L

15 16 17 18

INV

DVC C

DGND

19 20

NC

AV CCBIAS

21 22

STBY

BYP

AGNDBIAS

23 24

NC

–5–

AGND0

NC

36

VID0

35

AV CC0, 1

34

VID1

33

AGND1, 2

32

VID2

31

AV CC2, 3

30

VID3

29

AGND3, 4

28

VID4

27

AV CC4, 5

26

VID5

25

AGND5

Loading...

Loading...