Low Distortion

1

2

3

4

8

7

6

5

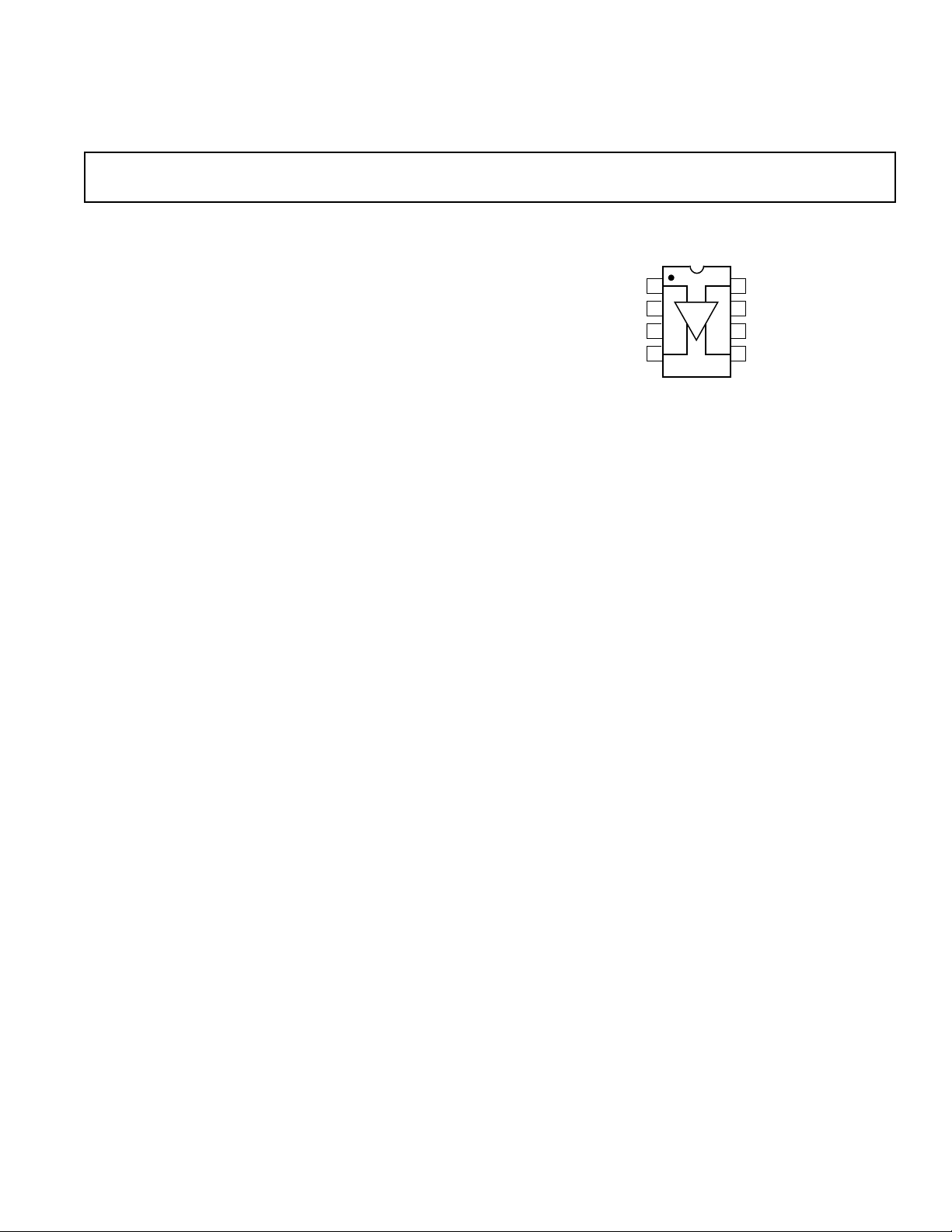

AD8350

IN+ IN–

ENBL

OUT+

OUT–

V

CC

GND

+

–

GND

a

FEATURES

High Dynamic Range

Output IP3: +28 dBm: Re 50 @ 250 MHz

Low Noise Figure: 5.9 dB @ 250 MHz

Two Gain Versions:

AD8350-15: 15 dB

AD8350-20: 20 dB

–3 dB Bandwidth: 1.0 GHz

Single Supply Operation: 5 V to 10 V

Supply Current: 28 mA

Input/Output Impedance: 200

Single-Ended or Differential Input Drive

8-Lead SOIC Package and 8-Lead microSOIC Package

APPLICATIONS

Cellular Base Stations

Communications Receivers

RF/IF Gain Block

Differential A-to-D Driver

SAW Filter Interface

Single-Ended-to-Differential Conversion

High Performance Video

High Speed Data Transmission

1.0 GHz Differential Amplifier

AD8350

FUNCTIONAL BLOCK DIAGRAM

8-Lead SOIC and SOIC Packages (with Enable)

PRODUCT DESCRIPTION

The AD8350 series are high performance fully-differential

amplifiers useful in RF and IF circuits up to 1000 MHz. The

amplifier has excellent noise figure of 5.9 dB at 250 MHz. It

offers a high output third order intercept (OIP3) of +28 dBm

at 250 MHz. Gain versions of 15 dB and 20 dB are offered.

The AD8350 is designed to meet the demanding performance

requirements of communications transceiver applications. It

enables a high dynamic range differential signal chain, with

exceptional linearity and increased common-mode rejection.

The device can be used as a general purpose gain block, an

A-to-D driver, and high speed data interface driver, among

other functions. The AD8350 input can also be used as a singleended-to-differential converter.

The amplifier can be operated down to 5 V with an OIP3 of

+28 dBm at 250 MHz and slightly reduced distortion performance. The wide bandwidth, high dynamic range and temperature

stability make this product ideal for the various RF and IF

frequencies required in cellular, CATV, broadband, instrumentation and other applications.

The AD8350 is offered in an 8-lead single SOIC package and

µSOIC package. It operates from 5 V and 10 V power supplies,

drawing 28 mA typical. The AD8350 offers a power enable function for power-sensitive applications. The AD8350 is fabricated

using Analog Devices’ proprietary high speed complementary

bipolar process. The device is available in the industrial (–40°C to

+85°C) temperature range.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

(@ 25C, VS = 5 V, G = 15 dB, unless otherwise noted. All specifications refer to

AD8350–SPECIFICATIONS

differential inputs and differential outputs unless noted.)

Parameter Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

–3 dB Bandwidth VS = 5 V, V

V

= 10 V, V

S

Bandwidth for 0.1 dB Flatness V

Slew Rate V

Settling Time 0.1%, V

Gain (S21)

1

Gain Supply Sensitivity V

Gain Temperature Sensitivity T

Isolation (S12)

1

= 5 V, V

S

V

= 10 V, V

S

= 1 V p-p 2000 V/µs

OUT

VS = 5 V, f = 50 MHz 14 15 16 dB

= 5 V to 10 V, f = 50 MHz 0.003 dB/V

S

to T

MIN

f = 50 MHz –18 dB

= 1 V p-p 0.9 GHz

OUT

= 1 V p-p 1.1 GHz

OUT

= 1 V p-p 90 MHz

OUT

= 1 V p-p 90 MHz

OUT

= 1 V p-p 10 ns

OUT

MAX

–0.002 dB/°C

NOISE/HARMONIC PERFORMANCE

50 MHz Signal

Second Harmonic V

Third Harmonic V

Output Second Order Intercept

Output Third Order Intercept

2

2

= 5 V, V

S

= 10 V, V

V

S

= 5 V, V

S

V

= 10 V, V

S

= 1 V p-p –66 dBc

OUT

= 1 V p-p –67 dBc

OUT

= 1 V p-p –65 dBc

OUT

= 1 V p-p –70 dBc

OUT

VS = 5 V 58 dBm

V

= 10 V 58 dBm

S

VS = 5 V 28 dBm

= 10 V 29 dBm

V

S

250 MHz Signal

Second Harmonic V

Third Harmonic V

Output Second Order Intercept

Output Third Order Intercept

1 dB Compression Point (RTI)

2

2

2

= 5 V, V

S

= 10 V, V

V

S

= 5 V, V

S

V

= 10 V, V

S

= 1 V p-p –48 dBc

OUT

= 1 V p-p –49 dBc

OUT

= 1 V p-p –52 dBc

OUT

= 1 V p-p –61 dBc

OUT

VS = 5 V 39 dBm

V

= 10 V 40 dBm

S

VS = 5 V 24 dBm

= 10 V 28 dBm

V

S

VS = 5 V 2 dBm

V

= 10 V 5 dBm

S

Voltage Noise (RTI) f = 150 MHz 1.7 nV/√Hz

Noise Figure f = 150 MHz 6.8 dB

INPUT/OUTPUT CHARACTERISTICS

Differential Offset Voltage (RTI) V

Differential Offset Drift T

OUT+

MIN

– V

to T

OUT–

MAX

±1mV

0.02 mV/°C

Input Bias Current 15 µA

Input Resistance Real 200 Ω

CMRR f = 50 MHz –67 dB

Output Resistance Real 200 Ω

POWER SUPPLY

Operating Range 411.0V

Quiescent Current Powered Up, V

Powered Down, V

Powered Up, V

Powered Down, V

= 5 V 25 28 32 mA

S

= 5 V 3 3.8 5.5 mA

S

= 10 V 27 30 34 mA

S

= 10 V 3 4 6.5 mA

S

Power-Up/Down Switching 15 ns

Power Supply Rejection Ratio f = 50 MHz, VS ∆ = 1 V p-p –58 dB

OPERATING TEMPERATURE RANGE –40 +85 °C

NOTES

1

See Tables II–III for complete list of S-Parameters.

2

Re: 50 Ω.

Specifications subject to change without notice.

–2–

REV. A

AD8350

AD8350-20–SPECIFICATIONS

(@ 25C, VS = 5 V, G = 20 dB, unless otherwise noted. All specifications refer to

differential inputs and differential outputs unless noted.)

Parameter Conditions Min Typ Max Unit

DYNAMIC PERFORMANCE

–3 dB Bandwidth V

Bandwidth for 0.1 dB Flatness V

Slew Rate V

Settling Time 0.1%, V

Gain (S21)

1

Gain Supply Sensitivity V

Gain Temperature Sensitivity T

Isolation (S12)

1

= 5 V, V

S

= 10 V, V

V

S

= 5 V, V

S

= 10 V, V

V

S

= 1 V p-p 2000 V/µs

OUT

VS = 5 V, f = 50 MHz 19 20 21 dB

= 5 V to 10 V, f = 50 MHz 0.003 dB/V

S

to T

MIN

f = 50 MHz –22 dB

= 1 V p-p 0.7 GHz

OUT

= 1 V p-p 0.9 GHz

OUT

= 1 V p-p 90 MHz

OUT

= 1 V p-p 90 MHz

OUT

= 1 V p-p 15 ns

OUT

MAX

–0.002 dB/°C

NOISE/HARMONIC PERFORMANCE

50 MHz Signal

Second Harmonic V

Third Harmonic V

Output Second Order Intercept

Output Third Order Intercept

2

2

= 5 V, V

S

V

= 10 V, V

S

= 5 V, V

S

= 10 V, V

V

S

VS = 5 V 56 dBm

V

= 10 V 56 dBm

S

VS = 5 V 28 dBm

V

= 10 V 29 dBm

S

= 1 V p-p –65 dBc

OUT

= 1 V p-p –66 dBc

OUT

= 1 V p-p –66 dBc

OUT

= 1 V p-p –70 dBc

OUT

250 MHz Signal

Second Harmonic V

Third Harmonic V

Output Second Order Intercept

Output Third Order Intercept

1 dB Compression Point (RTI)

2

2

2

= 5 V, V

S

V

= 10 V, V

S

= 5 V, V

S

= 10 V, V

V

S

VS = 5 V 37 dBm

V

= 10 V 38 dBm

S

VS = 5 V 24 dBm

V

= 10 V 28 dBm

S

VS = 5 V –2.6 dBm

= 10 V 1.8 dBm

V

S

= 1 V p-p –45 dBc

OUT

= 1 V p-p –46 dBc

OUT

= 1 V p-p –55 dBc

OUT

= 1 V p-p –60 dBc

OUT

Voltage Noise (RTI) f = 150 MHz 1.7 nV/√Hz

Noise Figure f = 150 MHz 5.6 dB

INPUT/OUTPUT CHARACTERISTICS

Differential Offset Voltage (RTI) V

Differential Offset Drift T

OUT+

MIN

– V

to T

OUT–

MAX

±1mV

0.02 mV/°C

Input Bias Current 15 µA

Input Resistance Real 200 Ω

CMRR f = 50 MHz –52 dB

Output Resistance Real 200 Ω

POWER SUPPLY

Operating Range 411.0V

Quiescent Current Powered Up, V

Powered Down, V

Powered Up, V

Powered Down, V

= 5 V 25 28 32 mA

S

= 5 V 3 3.8 5.5 mA

S

= 10 V 27 30 34 mA

S

= 10 V 3 4 6.5 mA

S

Power-Up/Down Switching 15 ns

Power Supply Rejection Ratio f = 50 MHz, VS ∆ = 1 V p-p –45 dB

OPERATING TEMPERATURE RANGE –40 +85 °C

NOTES

1

See Tables II–III for complete list of S-Parameters.

2

Re: 50 Ω.

REV. A

–3–

AD8350

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage, VS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 V

Input Power Differential . . . . . . . . . . . . . . . . . . . . . . +8 dBm

Internal Power Dissipation . . . . . . . . . . . . . . . . . . . . 400 mW

SOIC (R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100°C/W

θ

JA

θ

µSOIC (RM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133°C/W

JA

Maximum Junction Temperature . . . . . . . . . . . . . . . . . 125°C

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range (Soldering 60 sec) . . . . . . . . . 300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

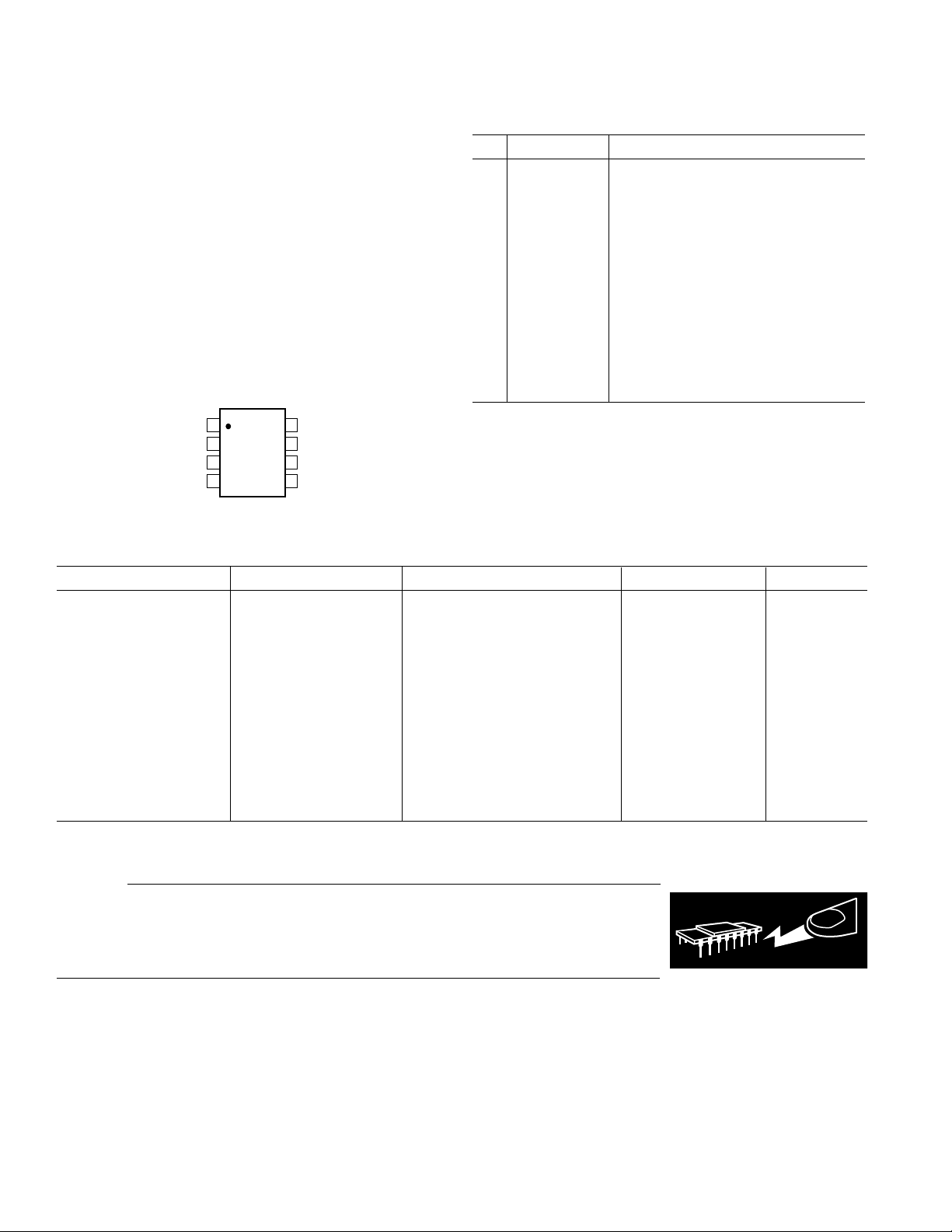

PIN CONFIGURATION

IN+

ENBL

V

OUT+

CC

1

2

AD8350

TOP VIEW

3

(Not to Scale)

4

8

IN–

7

GND

6

GND

5

OUT–

ORDERING GUIDE

PIN FUNCTION DESCRIPTIONS

Pin Function Description

1, 8 IN+, IN– Differential Inputs. IN+ and IN–

should be ac-coupled (pins have a dc

bias of midsupply). Differential input

impedance is 200 Ω.

2 ENBL Power-up Pin. A high level (5 V) enables

the device; a low level (0 V) puts device

in sleep mode.

3V

CC

Positive Supply Voltage. 5 V to 10 V.

4, 5 OUT+, OUT– Differential Outputs. OUT+ and

OUT– should be ac-coupled (pins have

a dc bias of midsupply). Differential

input impedance is 200 Ω.

6, 7 GND Common External Ground Reference.

Model Temperature Range Package Description Package Option Brand Code

AD8350AR15 –40°C to +85°C 8-Lead SOIC SO-8 Standard

AD8350AR15-REEL –40°C to +85°C 8-Lead SOIC 13" Reel SO-8 Standard

AD8350AR15-REEL7 –40°C to +85°C 8-Lead SOIC 7" Reel SO-8 Standard

AD8350ARM15 –40°C to +85°C 8-Lead microSOIC RM-8 J2N

AD8350ARM15-REEL –40°C to +85°C 8-Lead microSOIC 13" Reel RM-8 J2N

AD8350ARM15-REEL7 –40°C to +85°C 8-Lead microSOIC 7" Reel RM-8 J2N

AD8350AR20 –40°C to +85°C 8-Lead SOIC SO-8 Standard

AD8350AR20-REEL –40°C to +85°C 8-Lead SOIC 13" Reel SO-8 Standard

AD8350AR20-REEL7 –40°C to +85°C 8-Lead SOIC 7" Reel SO-8 Standard

AD8350ARM20 –40°C to +85°C 8-Lead microSOIC RM-8 J2P

AD8350ARM20-REEL –40°C to +85°C 8-Lead microSOIC 13" Reel RM-8 J2P

AD8350ARM20-REEL7 –40°C to +85°C 8-Lead microSOIC 7" Reel RM-8 J2P

AD8350-EVAL SOIC Evaluation Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD8350 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–4–

REV. A

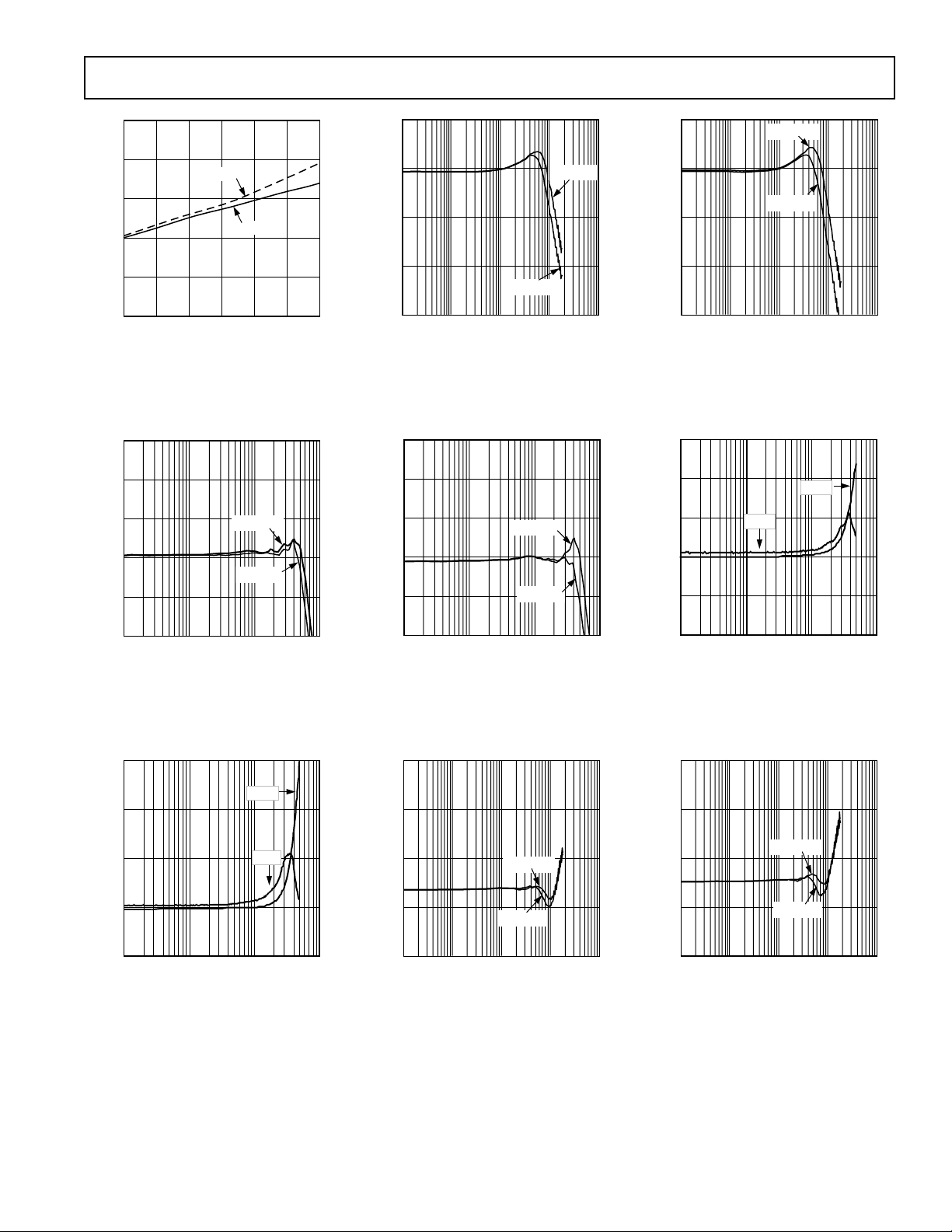

Typical Performance Characteristics–AD8350

FREQUENCY – MHz

ISOLATION – dB

–10

1

–15

–20

–25

–30

10 100 1k 10k

VCC = 10V

VCC = 5V

50

SUPPLY CURRENT – mA

40

30

20

10

0

–20

–40

VCC = 10V

VCC = 5V

0

20 40 60 80

TEMPERATURE – C

TPC 1. Supply Current vs.

Temperature

350

300

250

200

IMPEDANCE –

150

VCC = 10V

VCC = 5V

20

GAIN – dB

15

10

5

0

1

10 100 1k 10k

FREQUENCY – MHz

VCC = 10V

VCC = 5V

TPC 2. AD8350-15 Gain (S21) vs.

Frequency

350

300

250

200

IMPEDANCE –

150

VCC = 10V

VCC = 5V

GAIN – dB

25

20

15

10

5

1

10 100 1k 10k

VCC = 10V

VCC = 5V

FREQUENCY – MHz

TPC 3. AD8350-20 Gain (S21) vs.

Frequency

500

400

300

200

IMPEDANCE –

100

SOIC

SOIC

100

1

10 100 1k

FREQUENCY – MHz

TPC 4. AD8350-15 Input Imped ance vs. Frequency

800

SOIC

600

400

IMPEDANCE –

200

0

0 10 1000

FREQUENCY – MHz

SOIC

100

TPC 7. AD8350-20 Output Impedance vs. Frequency

100

1

10 100 1k

FREQUENCY – MHz

TPC 5. AD8350-20 Input Impedance

vs. Frequency

–5

–10

ISOLATION – dB

–15

–20

–25

10 100 1k 10k

1

FREQUENCY – MHz

VCC = 10V

VCC = 5V

TPC 8. AD8350-15 Isolation (S12)

vs. Frequency

0

0 10 1000

FREQUENCY – MHz

100

TPC 6. AD8350-15 Output Impedance

vs. Frequency

TPC 9. AD8350-20 Isolation (S12)

vs. Frequency

REV. A

–5–

AD8350

p

FREQUENCY – MHz

1dB COMPRESSION – dBm (Re: 50)

0

100 200 300 400 500 600

7.5

5.0

2.5

0

–2.5

–5.0

VCC = 10V

VCC = 5V

INPUT REFERRED

10.0

–40

V

= 1V p-p

OUT

–45

–50

–55

–60

–65

DISTORTION – dBc

–70

–75

–80

0

50 100 150 200 250 300

FUNDAMENTAL FREQUENCY – MHz

HD2 (VCC = 10V)

HD2 (VCC = 5V)

HD3 (VCC = 5V)

HD3 (VCC = 10V)

TPC 10. AD8350-15 Harmonic

Distortion vs. Frequency

–45

–55

–65

DISTORTION – dBc

–75

FO = 50MHz

HD2 (VCC = 5V)

HD3 (VCC = 5V)

HD2 (VCC = 10V)

HD3 (VCC = 10V)

–40

V

= 1V p-p

OUT

–45

–50

–55

–60

–65

DISTORTION – dBc

–70

–75

–80

0

HD2 (VCC = 5V)

HD2 (VCC = 10V)

HD3 (VCC = 5V)

HD3 (VCC = 10V)

50 100 150 200 250 300

FUNDAMENTAL FREQUENCY – MHz

TPC 11. AD8350-20 Harmonic Distortion vs. Frequency

66

61

56

51

46

OIP2 – dBm (Re: 50)

41

VCC = 10V

VCC = 5V

–45

FO = 50MHz

HD3 (VCC = 5V)

HD2 (VCC = 5V)

–55

–65

HD2 (VCC = 10V)

DISTORTION – dBc

–75

–85

0

HD3 (VCC = 10V)

0.5 1 1.5 2 2.5 3 3.5

OUTPUT VOLTAGE – V p-p

TPC 12. AD8350-15 Harmonic Distortion vs. Differential Output Voltage

66

61

56

51

46

OIP2 – dBm (Re: 50)

41

VCC = 10V

VCC = 5V

–85

0

0.5 1 1.5 2 2.5 3 3.5

OUTPUT VOLTAGE – V p-

TPC 13. AD8350-20 Harmonic Distortion vs. Differential Output Voltage

41

36

VCC = 10V

VCC = 5V

FREQUENCY – MHz

31

26

21

OIP3 – dBm (Re: 50)

16

11

0

50 100 150 200 250 300

TPC 16. AD8350-15 Output Referred

IP3 vs. Frequency

36

0

50 100 150 200 250 300

FREQUENCY – MHz

TPC 14. AD8350-15 Output Referred

IP2 vs. Frequency

41

36

31

26

21

OIP3 – dBm (Re: 50)

16

11

0

50 100 150 200 250 300

VCC = 10V

VCC = 5V

FREQUENCY – MHz

TPC 17. AD8350-20 Output Referred

IP3 vs. Frequency

36

0

50 100 150 200 250 300

FREQUENCY – MHz

TPC 15. AD8350-20 Output Referred

IP2 vs. Frequency

TPC 18. AD8350-15 1 dB Compression vs. Frequency

–6–

REV. A

AD8350

–2.5

–5.0

1dB COMPRESSION – dBm (Re: 50)

–7.5

7.5

5.0

2.5

0

VCC = 5V

0

100 200 300 400 500 600

FREQUENCY – MHz

INPUT REFERRED

VCC = 10V

TPC 19. AD8350-20 1 dB Compression vs. Frequency

25

20

15

10

5

0

GAIN – dB

–5

–10

–15

–20

2345678910

1

VCC – Volts

AD8350-20

AD8350-15

TPC 22. AD8350 Gain (S21) vs.

Supply Voltage

10

9

NOISE FIGURE – dB

8

7

6

5

0

VCC = 10V

VCC = 5V

50 100 150 200 250 300 350 400 450 500

FREQUENCY – MHz

TPC 20. AD8350-15 Noise Figure

vs. Frequency

100

OUTPUT OFFSET – mV

–50

–100

–150

–200

–250

50

0

–20

–40

V

+ (VCC = 5V)

OUT

V

– (VCC = 5V)

OUT

V

+ (VCC = 10V)

OUT

V

– (VCC = 10V)

OUT

0

20 40 60 80

TEMPERATURE – C

TPC 23. AD8350 Output Offset Voltage vs. Temperature

10

9

8

7

NOISE FIGURE – dB

6

5

0

50 100 150 200 250 300 350 400 450 500

VCC = 10V

VCC = 5V

FREQUENCY – MHz

TPC 21. AD8350-20 Noise Figure

vs. Frequency

–20

VCC = 5V

–30

–40

PSRR – dB

–50

–60

–70

–80

–90

AD8350-20

AD8350-15

1

10 100 1k

FREQUENCY – MHz

TPC 24. AD8350 PSRR vs. Frequency

–20

VCC = 5V

PSRR – dB

–30

–40

–50

–60

–70

–80

–90

1

AD8350-20

AD8350-15

10 100 1k

FREQUENCY – MHz

TPC 25. AD8350 CMRR vs. Frequency

REV. A

500mV

V

OUT

VCC = 5V

ENBL

5V

30ns

TPC 26. AD8350 Power-Up/Down

Response Time

–7–

AD8350

APPLICATIONS

Using the AD8350

Figure 1 shows the basic connections for operating the AD8350.

A single supply in the range 5 V to 10 V is required. The power

supply pin should be decoupled using a 0.1 µF capacitor. The

ENBL pin is tied to the positive supply or to 5 V (when V

CC

=

10 V) for normal operation and should be pulled to ground to

put the device in sleep mode. Both the inputs and the outputs

have dc bias levels at midsupply and should be ac-coupled.

Also shown in Figure 1 are the impedance balancing requirements,

either resistive or reactive, of the input and output. With an

input and output impedance of 200 Ω, the AD8350 should be

driven by a 200 Ω source and loaded by a 200 Ω impedance. A

reactive match can also be implemented.

5

4

C5

0.1F

C4

0.001F

C3

0.001F

LOAD

Z = 200

SOURCE

Z = 100

Z = 100

C2

0.001F

C1

0.001F

ENBL (5V)

8

6

7

AD8350

–

+

2

1

3

+VS (5V TO 10V)

Figure 1. Basic Connections for Differential Drive

Figure 2 shows how the AD8350 can be driven by a singleended source. The unused input should be ac-coupled to ground.

When driven single-endedly, there will be a slight imbalance in

the differential output voltages. This will cause an increase in

the second order harmonic distortion (at 50 MHz, with V

10 V and V

= 1 V p-p, –59 dBc was measured for the second

OUT

CC

=

harmonic on AD8350-15).

LOAD

C2

0.001F

7

8

6

C4

5

0.001F

AD8350

SOURCE

Z = 200

C1

0.001F

ENBL (5V)

1

+V

–

+

3

2

(5V TO 10V)

S

4

C5

0.1F

C3

0.001F

Z = 200

Figure 2. Basic Connections for Single-Ended Drive

Reactive Matching

In practical applications, the AD8350 will most likely be matched

using reactive matching components as shown in Figure 3.

Matching components can be calculated using a Smith Chart or

by using a resonant approach to determine the matching network

that results in a complex conjugate match. In either situation,

the circuit can be analyzed as a single-ended equivalent circuit

to ease calculations as shown in Figure 4.

–8–

RS/2

V

S

R

S

LS/2

C

AC

876

AD8350

C

P

/2

LS/2

C

AC

ENBL (5V)

–

+

1234

(5V TO 10V)

+V

S

5

0.1F

C

AC

C

AC

LS/2

C

P

LS/2

R

LOAD

Figure 3. Reactively Matching the Input and Output

C

P

C

AC

C

AC

ENBL (5V)

876

AD8350

–

+

1234

+VS (5V TO 10V)

L

S

R

S

V

S

5

0.1F

C

AC

C

AC

L

S

C

P

R

LOAD

Figure 4. Single-Ended Equivalent Circuit

When the source impedance is smaller than the load impedance,

a step-up matching network is required. A typical step-up network

is shown on the input of the AD8350 in Figure 3. For purely

resistive source and load impedances the resonant approach may

be used. The input and output impedance of the AD8350 can be

modeled as a real 200 Ω resistance for operating frequencies less

than 100 MHz. For signal frequencies exceeding 100 MHz, classical Smith Chart matching techniques should be invoked in order

to deal with the complex impedance relationships. Detailed S

parameter data measured differentially in a 200 Ω system can be

found in Tables II and III.

For the input matching network the source resistance is less

than the input resistance of the AD8350. The AD8350 has a

nominal 200 Ω input resistance from Pins 1 to 8. The reactance

of the ac-coupling capacitors, C

, should be negligible if 100 nF

AC

capacitors are used and the lowest signal frequency is greater

than 1 MHz. If the series reactance of the matching network

inductor is defined to be X

of the matching capacitor to be X

RR

×

=

S

S LOAD

X

P

X

= 2 π f LS, and the shunt reactance

S

= (2 π f CP)–1, then:

P

R

XR

=×where

PLOAD

S

RR

–

LOAD S

(1)

For a 70 MHz application with a 50 Ω source resistance, and

assuming the input impedance is 200 Ω, or R

then X

= 115.5 Ω and XS = 86.6 Ω, which results in the follow-

P

= RIN = 200 Ω,

LOAD

ing component values:

CP = (2 π × 70 × 106 × 115.5)–1 = 19.7 pF and

= 86.6 × (2 π × 70 × 106)–1 = 197 nH

L

S

REV. A

AD8350

For the output matching network, if the output source resistance of the AD8350 is greater than the terminating load

resistance, a step-down network should be employed as shown

on the output of Figure 3. For a step-down matching network,

the series and parallel reactances are calculated as:

X

RR

=

S

×

S LOAD

X

P

XR

=×where

PS

R

LOAD

RR

–

S LOAD

(2)

For a 10 MHz application with the 200 Ω output source resistance

of the AD8350, R

50 Ω, then X

= 115.5 Ω and XS = 86.6 Ω, which results in

P

= 200 Ω, and a 50 Ω load termination, R

S

LOAD

=

the following component values:

CP = (2 π × 10 × 106 × 115.5)–1 = 138 pF and

= 86.6 × (2 π × 10 × 106)–1 = 1.38 µH

L

S

The same results can be obtained using the plots in Figure 5

and Figure 6. Figure 5 shows the normalized shunt reactance

versus the normalized source resistance for a step-up matching

network, R

S

< R

can be found for a given value of R

is then calculated using X

. By inspection, the appropriate reactance

LOAD

= RS R

S

S/RLOAD

LOAD/XP.

. The series reactance

The same technique

can be used to design the step-down matching network using

Figure 6.

2

1.8

LOAD

1.6

/R

P

1.4

1.2

0.8

0.6

0.4

NORMALIZED REACTANCE – X

0.2

R

SOURCE

1

0

0.01

0.05

0.09

NORMALIZED SOURCE RESISTANCE – R

0.13

0.17

0.21

X

0.25

S

X

P

0.29

0.33

0.37

R

0.41

LOAD

0.45

0.49

0.53

SOURCE

0.57

0.61

0.65

/R

0.69

LOAD

0.73

0.77

Figure 5. Normalized Step-Up Matching Components

3.2

R

SOURCE

3

LOAD

/R

P

2.8

2.6

2.4

X

S

X

P

R

LOAD

The same results could be found using a Smith Chart as shown

in Figure 7. In this example, a shunt capacitor and a series inductor

are used to match the 200 Ω source to a 50 Ω load. For a frequency of 10 MHz, the same capacitor and inductor values

previously found using the resonant approach will transform the

200 Ω source to match the 50 Ω load. At frequencies exceeding

100 MHz, the S parameters from Tables II and III should be

used to account for the complex impedance relationships.

LOAD

SERIES L

SOURCE

SHUNT C

Figure 7. Smith Chart Representation of Step-Down Network

After determining the matching network for the single-ended

equivalent circuit, the matching elements need to be applied in a

differential manner. The series reactance needs to be split such

that the final network is balanced. In the previous examples, this

simply translates to splitting the series inductor into two equal

halves as shown in Figure 3.

Gain Adjustment

The effective gain of the AD8350 can be reduced using a number of techniques. Obviously a matched attenuator network will

reduce the effective gain, but this requires the addition of a

separate component which can be prohibitive in size and cost.

The attenuator will also increase the effective noise figure resulting

in an SNR degradation. A simple voltage divider can be implemented using the combination of the driving impedance of the

previous stage and a shunt resistor across the inputs of the AD8350

as shown in Figure 8. This provides a compact solution but

suffers from an increased noise spectral density at the input

of the AD8350 due to the thermal noise contribution of the

shunt resistor. The input impedance can be dynamically altered

through the use of feedback resistors as shown in Figure 9. This

will result in a similar attenuation of the input signal by virtue

of the voltage divider established from the driving source impedance and the reduced input impedance of the AD8350. Yet

this technique does not significantly degrade the SNR with

the unnecessary increase in thermal noise that arises from a truly

resistive attenuator network.

2.2

NORMALIZED REACTANCE – X

2

2

2.4

2.8

3.2

NORMALIZED SOURCE RESISTANCE – R

3.644.4

4.8

5.2

5.666.4

6.8

SOURCE

7.2

7.688.4

/R

LOAD

8.8

Figure 6. Normalized Step-Down Matching Components

REV. A

–9–

AD8350

C

AC

C

AC

ENBL (5V)

876

AD8350

–

+

1234

(5V TO 10V)

+V

S

R

S

R

SHUNT

V

S

R

R

S

SHUNT

5

0.1F

C

AC

R

L

R

L

C

AC

Figure 8. Gain Reduction Using Shunt Resistor

R

FEXT

C

AC

R

S

V

S

R

S

C

AC

876

AD8350

–

+

1234

ENBL

(5V)

+V

R

S

FEXT

(5V TO 10V)

0.1F

C

AC

5

R

L

R

L

C

AC

Figure 9. Dynamic Gain Reduction

Figure 8 shows a typical implementation of the shunt divider

concept. The reduced input impedance that results from the

parallel combination of the shunt resistor and the input impedance

of the AD8350 adds attenuation to the input signal effectively

reducing the gain. For frequencies less than 100 MHz, the input

impedance of the AD8350 can be modeled as a real 200 Ω resis-

tance (differential). Assuming the frequency is low enough to

ignore the shunt reactance of the input, and high enough such

that the reactance of moderately sized ac-coupling capacitors

can be considered negligible, the insertion loss, IL, due to the

shunt divider can be expressed as:

The insertion loss and the resultant power gain for multiple

shunt resistor values is summarized in Table I. The source

resistance and input impedance need careful attention when

using Equation 1. The reactance of the input impedance of the

AD8350 and the ac-coupling capacitors need to be considered

before assuming they have negligible contribution. Figure 10

shows the effective power gain for multiple values of R

SHUNT

for

the AD8350-15 and AD8350-20.

Table I. Gain Adjustment Using Shunt Resistor,

= 100 and RIN = 100 Single-Ended

R

S

Power Gain–dB

R

– IL–dB AD8350-15 AD8350-20

SHUNT

50 6.02 8.98 13.98

100 3.52 11.48 16.48

200 1.94 13.06 18.06

300 1.34 13.66 18.66

400 1.02 13.98 18.98

20

18

GAIN – dB

16

14

12

10

8

6

4

2

0

100 200 300 400 500 600 700 800

0

AD8350-20

AD8350-15

R

SHUNT

–

Figure 10. Gain for Multiple Values of Shunt Resistance

for Circuit in Figure 8

The gain can be adjusted dynamically by employing external

feedback resistors as shown in Figure 9. The effective attenuation is a result of the lowered input impedance as with the shunt

resistor method, yet there is no additional noise contribution at

the input of the device. It is necessary to use well-matched resistors

to minimize common-mode offset errors. Quality 1% tolerance

resistors should be used along with a symmetric board layout to

help guarantee balanced performance. The effective gain for multiple values of external feedback resistors is shown in Figure 11.

IL dB Log

()

=×

20

where

RR

IN SHUNT

=

10

()

RR

×

IN SHUNT

RR

+

IN SHUNT

R

IN

RR

()

+

IN S

RR

IN SHUNT

RR R

IN SHUNT S

and Ω sin e e

+

R gl nded

=−

100

IN

(3)

–10–

REV. A

AD8350

20

GAIN – dB

18

16

14

12

10

8

6

4

2

0

0

AD8350-20

AD8350-15

500 1000 1500 2000

R

–

FEXT

Figure 11. Power Gain vs. External Feedback Resistors

for the AD8350-15 and AD8350-20 with R

= 100

R

L

Ω

= 100 Ω and

S

The power gain of any two-port network is dependent on the

source and load impedance. The effective gain will change if the

differential source and load impedance is not 200 Ω. The singleended input and output resistance of the AD8350 can be modeled

using the following equations:

RR

+

R

=

IN

RR

FL

+

FL

R

INT

++ ×1

gR

mL

(4)

and

R

F

R

=

OUT

1

g

+×

m

1

+

11

+

RR

S INT

1

11

+

RR

S INT

≈

+

RR

FS

+×

1

gR

mS

≤

for R k

1 Ω

S

(5)

Driving Lighter Loads

It is not necessary to load the output of the AD8350 with a

200 Ω differential load. Often it is desirable to try to achieve a

complex conjugate match between the source and load in order

to minimize reflections and conserve power. But if the AD8350

is driving a voltage responding device, such as an ADC, it is no

longer necessary to maximize power transfer. The harmonic

distortion performance will actually improve when driving

loads greater than 200 Ω. The lighter load requires less cur-

rent driving capability on the output stages of the AD8350

resulting in improved linearity. Figure 12 shows the improvement in second and third harmonic distortion for increasing

differential load resistance.

–66

–68

–70

–72

–74

–76

DISTORTION – dBc

–78

–80

–82

200

300 400 500 600 700 800 900 1000

R

LOAD

HD3

HD2

–

Figure 12. Second and Third Harmonic Distortion vs.

Differential Load Resistance for the AD8350-15 with

= 5 V, f = 70 MHz, and V

V

S

= 1 V p-p

OUT

where

=R

R

F

R

= R Feedback External

FEXT

R

= 662 Ω for the AD8350-15

FINT

FEXT

//R

FINT

= 1100 Ω for the AD8350-20

= 25000 Ω

R

INT

g

= 0.066 mhos for the AD8350-15

m

= 0.110 mhos for the AD8350-20

= R Source (Single-Ended)

R

S

R

= R Load (Single-Ended)

L

= R Input (Single-Ended)

R

IN

R

= R Output (Single-Ended)

OUT

The resultant single-ended gain can be calculated using the

following equation:

RgR

××−

()

G

=

V

LmF

RRRRRg

+++××

LSF LSm

1

REV. A

(6)

–11–

AD8350

EVALUATION BOARD

Figure 13 shows the schematic of the AD8350 evaluation board,

for SOIC, as it is shipped from the factory. The board is configured to allow easy evaluation using single-ended 50 Ω test

equipment. The input and output transformers have a 4-to-1

impedance ratio and transform the AD8350’s 200 Ω input and

output impedances to 50 Ω. In this mode, 0 Ω resistors (R1 and

R4) are required.

To allow compensation for the insertion loss of the transformers, a calibration path is provided at Test In and Test Out. This

consists of two transformers connected back to back.

C1

0.001F

7

8

IN–

IN+

R1

T1: TC4-1W

0

(MINI CIRCUITS)

61

0

R2

(OPEN)

C2

0.001F

+V

L1

A

3

S

2

B

AD8350

1

SW1

1

6

–

+

3

2

+V

To drive and load the board differentially, transformers T1 and

T2 should be removed and replaced with four 0 Ω resistors

(0805 size); Resistors R1 and R4 (0 Ω) should also be removed.

This yields a circuit with a broadband input and output impedance

of 200 Ω. To match to impedances other than this, matching

components (0805 size) can be placed on pads C1, C2, C3, C4,

L1, and L2.

C3

0.001F

5

T2: TC4-1W

(MINI CIRCUITS)

R3

L2

(OPEN)

4

C4

0.001F

C5

0.1F

S

0

1

6

R4

0

OUT–

OUT+

TEST IN

T3: TC4-1W

(MINI CIRCUITS)

61

T4: TC4-1W

(MINI CIRCUITS)

16

Figure 13. Evaluation Board

TEST OUT

–12–

REV. A

AD8350

Table II. Typical Scattering Parameters for the AD8350-15: VCC = 5 V, Differential Input and Output, Z

(diff) = 200

Z

LOAD

SOURCE

(diff) = 200 ,

Frequency – MHz S11 S12 S21 S22

25 0.015∠–48.8° 0.119∠176.3° 5.60∠–4.3° 0.034∠–4.8°

50 0.028∠–65.7° 0.119∠171.1° 5.61∠–8.9° 0.032∠–14.3°

75 0.043∠–75.3° 0.119∠166.9° 5.61∠–13.5° 0.036∠–30.2°

100 0.057∠–87.5° 0.120∠163.5° 5.61∠–17.9° 0.043∠–39.6°

125 0.073∠–91.8° 0.119∠159.8° 5.65∠–22.6° 0.053∠–40.6°

150 0.080∠–95.6° 0.120∠154.8° 5.68∠–27.0° 0.058∠–37°

175 0.100∠–97.4° 0.117∠151.2° 5.73∠–31.8° 0.072∠–45.1°

200 0.111∠–99.1° 0.121∠147.3° 5.78∠–36.3° 0.077∠–47.7°

225 0.128∠–103.2° 0.120∠143.7° 5.83∠–41.0° 0.091∠–52.5°

250 0.141∠–106.7° 0.120∠140.3° 5.90∠–45.6° 0.104∠–55.1°

275 0.151∠–109.7° 0.120∠136.6° 6.02∠–50.2° 0.108∠–54.2°

300 0.161∠–111.9° 0.123∠132.9° 6.14∠–55.1° 0.122∠–51.5°

325 0.179∠–114.7° 0.121∠130.7° 6.19∠–60.2° 0.135∠–55.6°

350 0.187∠–117.4° 0.122∠126.6° 6.27∠–65.0° 0.150∠–56.9°

375 0.194∠–121° 0.123∠123.6° 6.43∠–70.1° 0.162∠–60.9°

400 0.199∠–121.2° 0.124∠120.1° 6.61∠–75.8° 0.187∠–60.3°

425 0.215∠–122.6° 0.126∠117.2° 6.77∠–81.7° 0.215∠–63.3°

450 0.225∠–127.0° 0.126∠113.9° 6.91∠–87.6° 0.242∠–63.9°

475 0.225∠–127.7° 0.126∠112° 7.06∠–93.8° 0.268∠–65.2°

500 0.244∠–129.9° 0.128∠108.1° 7.27∠–99.8° 0.304∠–68.2°

Table III. Typical Scattering Parameters for the AD8350-20: VCC = 5 V, Differential Input and Output, Z

Z

(diff) = 200

LOAD

SOURCE

(diff) = 200 ,

Frequency – MHz S11 S12 S21 S22

25 0.017∠–142.9° 0.074∠174.9° 9.96∠–4.27° 0.023–16.6°

50 0.033∠–114.9° 0.074∠171.0° 9.98∠–8.9° 0.022∠–2.7°

75 0.055∠–110.6° 0.075∠167.0° 9.98∠–13.3° 0.023∠–23.5°

100 0.073∠–109.4° 0.075∠163.1° 10.00∠–17.7° 0.029∠–22.7°

125 0.089∠–112.1° 0.075∠159.2° 10.12∠–22.1° 0.037∠–18.0°

150 0.098∠–116.5° 0.076∠153.8° 10.20∠–26.4° 0.045∠–3.2°

175 0.124∠–118.1° 0.075∠150.2° 10.34∠–30.9° 0.055∠–15.7°

200 0.141∠–119.4° 0.076∠147.2° 10.50∠–35.6° 0.065∠–15.6°

225 0.159∠–122.6° 0.077∠142.2° 10.65∠–40.1° 0.080∠–17.7°

250 0.170∠–128.5° 0.078∠139.5° 10.80∠–44.7° 0.085∠–22.4°

275 0.186∠–131.6° 0.078∠135.8° 11.14∠–49.3° 0.096∠–23.5°

300 0.203∠–132.9° 0.080∠132.5° 11.45∠–54.7° 0.116∠–25.9°

325 0.215∠–135.0° 0.080∠129.3° 11.70∠–60.3° 0.139∠–29.6°

350 0.222∠–136.9° 0.082∠125.9° 11.93∠–65.0° 0.161∠–32.2°

375 0.242∠–142.4° 0.082∠123.6° 12.39∠–70.3° 0.173∠–38.6°

400 0.240∠–145.2° 0.084∠120.3° 12.99∠–76.8° 0.207∠–37.6°

425 0.267∠–146.7° 0.084∠117.3° 13.34∠–84.0° 0.241∠–48.1°

450 0.266∠–150.7° 0.086∠115.1° 13.76∠–90.1° 0.265∠–49.7°

475 0.267∠–153.7° 0.087∠112.8° 14.34∠–97.5° 0.317∠–53.5°

500 0.285∠–161.1° 0.088∠110.9° 14.89∠–105.0° 0.359∠–59.2°

REV. A

–13–

AD8350

0.1574 (4.00)

0.1497 (3.80)

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

8-Lead Plastic SOIC

(SO-8)

0.1968 (5.00)

0.1890 (4.80)

85

0.2440 (6.20)

0.2284 (5.80)

41

PIN 1

0.0098 (0.25)

0.0040 (0.10)

SEATING

0.122 (3.10)

0.114 (2.90)

0.006 (0.15)

0.002 (0.05)

SEATING

0.0500 (1.27)

PLANE

BSC

0.0192 (0.49)

0.0138 (0.35)

0.0688 (1.75)

0.0532 (1.35)

0.0098 (0.25)

0.0075 (0.19)

8-Lead microSOIC Package

(RM-8)

0.122 (3.10)

0.114 (2.90)

85

PIN 1

0.0256 (0.65) BSC

0.120 (3.05)

0.112 (2.84)

0.018 (0.46)

0.008 (0.20)

PLANE

0.199 (5.05)

0.187 (4.75)

41

0.043 (1.09)

0.037 (0.94)

0.011 (0.28)

0.003 (0.08)

0.0196 (0.50)

0.0099 (0.25)

8

0.0500 (1.27)

0

0.0160 (0.41)

0.120 (3.05)

0.112 (2.84)

33

27

45

0.028 (0.71)

0.016 (0.41)

–14–

REV. A

–15–

C01014–1.5–6/01(A)

–16–

PRINTED IN U.S.A.

Loading...

Loading...