Analog Devices AD8347ARU-REEL7, AD8347ARU-REEL, AD8347ARU, AD8347 Datasheet

0.8 GHz–2.7 GHz

a

Direct Conversion Quadrature Demodulator

FEATURES

Integrated RF and Baseband AGC Amplifiers

Quadrature Phase Accuracy 1ⴗ Typ

I/Q Amplitude Balance 0.3 dB Typ

Third Order Intercept (IIP3) +11.5 dBm @ Min Gain

Noise Figure 11 dB @ Max Gain

AGC Range 69.5 dB

Baseband Level Control Circuit

Low LO Drive –8 dBm

ADC Compatible I/Q Outputs

Single Supply 2.7 V–5.5 V

Power-Down Mode

Package 28-Lead TSSOP

APPLICATIONS

Cellular Basestations

Radio Links

Wireless Local Loop

IF Broadband Demodulator

RF Instrumentation

Satellite Modems

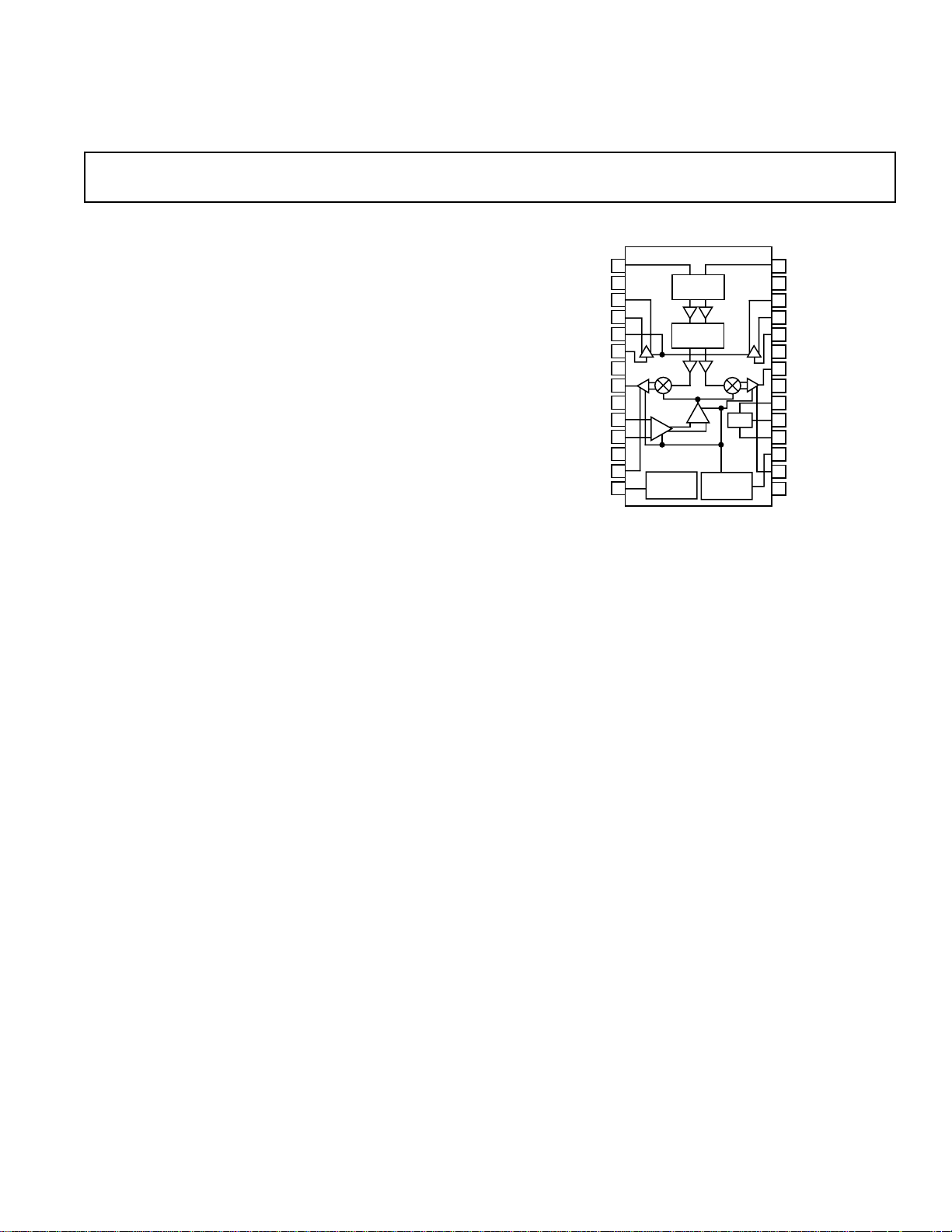

AD8347

FUNCTIONAL BLOCK DIAGRAM

LOIN

VPS1

IOPN

IOPP

VCMO

IAIN

COM3

IMXO

COM2

RFIN

RFIP

VPS2

IOFS

VREF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

AD8347

SPLITTER

SPLITTER

BIAS

PHASE

PHASE

DET

GAIN

CONTROL

LOIP

28

COM1

27

26

QOPN

25

QOPP

24

QAIN

23

COM3

22

QMXO

21

VPS3

20

VDT1

19

VAGC

18

VDT2

17

VGIN

16

QOFS

15

ENBL

*

GENERAL DESCRIPTION

The AD8347 is a broadband Direct Quadrature Demodulator

with RF and baseband Automatic Gain Control (AGC) amplifiers.

It is suitable for use in many communications receivers,

performing Quadrature demodulation directly to baseband

frequencies. The input frequency range is 800 MHz to 2.7 GHz.

The outputs can be connected directly to popular A-to-D converters

such as the AD9201 and AD9283.

The RF input signal goes through two stages of variable gain

amplifiers prior to two Gilbert-cell Mixers. The LO quadrature

phase splitter employs polyphase filters to achieve high quadrature accuracy and amplitude balance over the entire operating

frequency range. Separate I & Q channel variable-gain amplifiers

follow the baseband outputs of the mixers. The RF and baseband

*U.S. Patents Issued and Pending

amplifiers together provide 69.5 dB of gain control. A precision

control circuit sets the Linear-in-dB RF gain response to the gain

control voltage.

Baseband level detectors are included for use in an AGC loop to

maintain the output level. The demodulator dc offsets are

minimized by an internal loop, whose time constant is controlled

by external capacitor values. The offset control can also be

overridden by forcing an external voltage at the offset nulling pins.

The baseband variable gain amplifier outputs are brought off-chip

for filtering before final amplification. By inserting a channel

selection filter before each output amplifier high-level out-ofchannel interferers can be eliminated. Additional internal circuitry

also allows the user to set the dc common-mode level at the

baseband outputs.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

AD8347–SPECIFICATIONS

(VS = 5 V; TA = 25ⴗC; FLO = 1.9 GHz; V

R

= 10 k⍀, dBm with respect to 50 ⍀, unless otherwise noted.)

LOAD

= 1 V; FRF = 1.905 GHz; PLO = –8 dBm,

VCMO

Parameter Conditions Min Typ Max Unit

OPERATING CONDITIONS

LO/RF Frequency Range 0.8 2.7 GHz

LO Input Level –10 0 dBm

VGIN Input Level 0.2 1.2 V

V

SUPPLY (VS

) 2.7 5.5 V

Temperature Range –40 +85 °C

RF AMPLIFIER/DEMODULATOR From RFIP/RFIN to IMXO and QMXO

(IMXO/QMXO Load >1 kΩ)

AGC Gain Range 69.5 dB

Conversion Gain (Max) V

Conversion Gain (Min) V

Gain Linearity V

Gain Flatness F

Input P1 dB V

Third Order Input Intercept (IIP3) F

= 0.2 V (Max Gain) 39.5 dB

VGIN

= 1.2 V (Min Gain) –30 dB

VGIN

= 0.3 V to 1 V ±2dB

VGIN

= 0.8 GHz – 2.7 GHz, F

LO

= 0.2 V –30 dBm

VGIN

V

= 1.2 V –2 dBm

VGIN

= 1.905 GHz, +11.5 dBm

RF1

F

= 1.906 GHz, –10 dBm Each Tone,

RF2

= 1 MHz 0.7 dB p-p

BB

(Min Gain)

Second Order Input Intercept (IIP2) F

= 1.905 GHz, +25.5 dBm

RF1

F

= 1.906 GHz, –10 dBm Each Tone,

RF2

(Min Gain)

LO Leakage (RF) At RFIP –60 dBm

LO Leakage (MXO) At IMXO/QMXO –42 dBm

Demodulation Bandwidth –3 dB 90 MHz

Quadrature Phase Error F

I/Q Amplitude Imbalance F

= 1.9 GHz –3 ±1 +3 Degree

RF

= 1.9 GHz 0.3 dB

RF

Noise Figure Max Gain 11 dB

Mixer AGC Output Level See TPC 30 24 mV p-p

Baseband DC Offset At IMXO/QMXO, Max Gain 2 mV

(Corrected, Ref to VREF)

Mixer Output Swing Level at which IMD3 = 45 dBc

= 200 Ω 65 mV p-p

R

LOAD

R

= 1 kΩ 65 mV p-p

LOAD

Mixer Output Impedance 3 Ω

BASEBAND OUTPUT AMPLIFIER From IAIN to IOPP/IOPN and

QAIN to QOPP/QOPN

R

= 10 kΩ

LOAD

Gain 30 dB

Bandwidth –3 dB (See TPC 18) 65 MHz

– V

Output DC Offset (Differential) (V

Common-Mode Offset (V

IOPP

IOPP

) –200 ±50 +200 mV

IOPN

+ V

IOPN

)/2 – V

VCMO

–40 ±5 +40 mV

Group Delay Flatness 0 MHz–50 MHz 1.8 ns p-p

Second Order Intermod. Distortion F

Third Order Intermod. Distortion F

1 = 5 MHz, FIN2 = 6 MHz, –49 dBc

IN

1 = VIN2 = 8 mV p-p

V

IN

1 = 5 MHz, FIN2 = 6 MHz, –67 dBc

IN

V

1 = VIN2 = 8 mV p-p

IN

Input Bias Current 2 µA

Input Impedance 1储3MΩ储pF

Output Swing Limit (Upper) V

– 1.3 V

S

Output Swing Limit (Lower) 0.4 V

–2–

REV. 0

AD8347

Parameter Conditions Min Typ Max Unit

CONTROL INPUT/OUTPUTS

VCMO Input @ VS = 2.7 V 1 V

= 5 V 0.5 1 2.5 V

@ V

Gain Control Input Bias Current VGIN <1 µA

Offset Input Overriding Current IOFS, QOFS 10 µA

VREF Output R

RESPONSE FROM RF INPUT TO IMXO/QMXO Connected Directly to

FINAL BB AMP IAIN/QAIN Respectively

Gain @ V

Gain @ V

= 0.2 V 65.5 69.5 72.5 dB

VGIN

= 1.2 V –3 +0.5 +4 dB

VGIN

Gain Slope –96.5 –89 –82.5 dB/V

Gain Intercept Linear extrapolation back to 88 94 101 dB

LO/RF INPUT (See TPC 26 Through 29 for More Detail)

LOIP Input Return Loss Measuring LOIP LOIN, ac-coupled to –4 dB

RFIP Input Return Loss RFIP Input Pin –10 dB

ENABLE

Power-Up Control Low = Standby 0 0.5 V

Power-Up Control High = Enabled +V

Power-Up Time Time for Final BB Amps to be Within

Power-Down Time Time for Supply Current to be <4 mA

POWER SUPPLIES V

Voltage 2.7 5.5 V

Current (Enabled) @ 5 V 48 64 80 mA

Current (Standby) @ 5 V 400 µA

Current (Standby) @ 3.3 V 80 µA

Specifications subject to change without notice.

S

= 10 kΩ 0.95 1.00 1.05 V

LOAD

theoretical value at VGIN = 0

Ground with 100 pF.

Measuring Through Evaluation Board

Balun with Termination –9.5 dB

– 1 +V

S

S

V

90% of Final Amplitude

= 5 V 20 µs

@ V

S

= 2.7 V 10 µs

@ V

S

@ V

= 5 V 30 µs

S

@ VS = 2.7 V 1.5 ms

, V

PS2

, V

PS3

PS1

REV. 0

–3–

AD8347

ABSOLUTE MAXIMUM RATINGS

Supply Voltage V

PS1

, V

PS2

, V

PS3

*

. . . . . . . . . . . . . . . . . . . 5.5 V

LO and RF Input Power . . . . . . . . . . . . . . . . . . . . . . 10 dBm

Internal Power Dissipation . . . . . . . . . . . . . . . . . . . . 500 mW

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68°C/W

JA

Maximum Junction Temperature . . . . . . . . . . . . . . . . 150°C

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering 60 sec) . . . . . . . . . . . . . 300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD8347ARU –40°C to +85°C Tube (28-Lead TSSOP) Thin RU-28

AD8347ARU-REEL 13" Tape and Reel

AD8347ARU-REEL7 7" Tape and Reel

AD8347-EVAL Evaluation Board

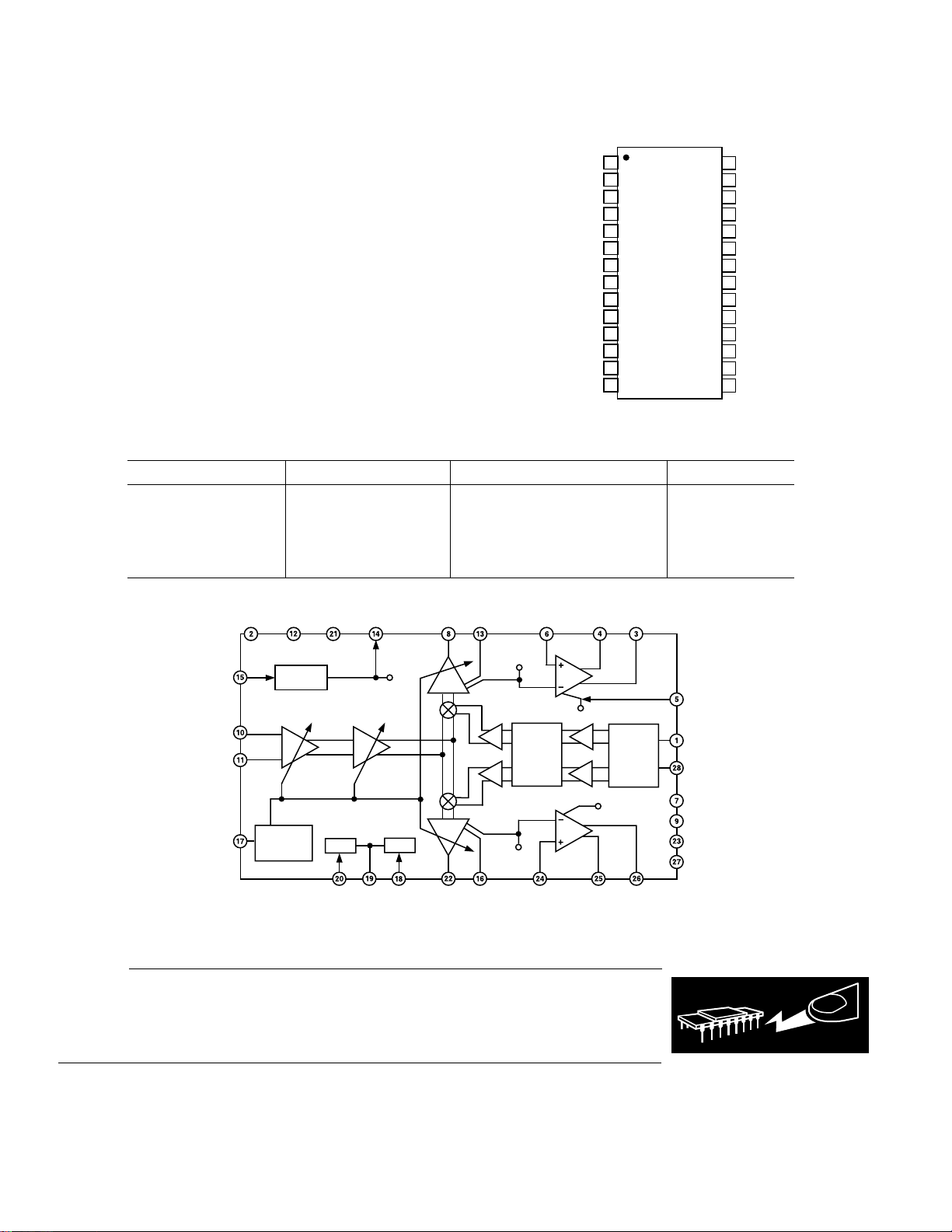

PIN CONFIGURATION

1

LOIN

2

VPS1

3

IOPN

4

IOPP

5

VCMO

6

IAIN

COM3

IMXO

COM2

RFIN

RFIP

VPS2

IOFS

VREF

7

8

9

10

11

12

13

14

AD8347

TOP VIEW

(Not to Scale)

Shrink Small Outline Package

LOIP

28

COM1

27

26

QOPN

25

QOPP

24

QAIN

23

COM3

22

QMXO

21

VPS3

20

VDT1

19

VAGC

18

VDT2

17

VGIN

16

QOFS

15

ENBL

VPS3

DET 1

VREF

VREF

DET 2

VDT2 QMXO QOPPQOFSVAGCVDT1 QAIN

VREF

PHASE

SPLITTER

VREF

IAIN

2

VCMO

IOPPIOFS IOPN

PHASE

SPLITTER

1

VCMO

QOPN

ENBL

RFIN

RFIP

VGIN

VPS2 IMXO

VPS1

AD8347

BIAS

CELL

GAIN

CONTROL

INTERFACE

Figure 1. Block Diagram

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD8347 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

VCMO

LOIN

LOIP

COM3

COM2

COM3

COM1

WARNING!

ESD SENSITIVE DEVICE

–4–

REV. 0

AD8347

PIN FUNCTION DESCRIPTIONS

Pin Equiv.

No. Mnemonic Cir. Description

1, 28 LOIN, LOIP A LO Input. For optimum performance, these inputs should be driven differentially. Typical input

drive level is equal to –8 dBm. To improve the match to a 50 Ω source, connect a 200 Ω shunt

resistor between LOIP and LOIN. A single-ended drive is also possible but this will slightly

increase LO leakage.

2 VPS1 Positive Supply for LO Section. This pin should be decoupled with 0.1 µF and 100 pF capacitors.

3, 4 IOPN, IOPP B

5 VCMO C Baseband Amplifier Common-Mode Voltage. The voltage applied to this pin sets the output

6 IAIN D I Channel Baseband Amplifier Input. This pin, which has a high input impedance, should be

7, 23 COM3 Ground for Biasing and Baseband Sections

8, 22 IMXO, QMXO B I & Q Channel Baseband Mixer/VGA Outputs. These are low impedance outputs whose bias

9 COM2 RF Section Ground

10, 11 RFIN, RFIP E RF Input. RFIN must be ac-coupled to ground. The RF input signal should be ac-coupled into

12 VPS2 Positive Supply for RF Section. This pin should be decoupled with 0.1 µF and 100 pF capacitors.

13, 16 IOFS, QOFS F I Channel and Q Channel Offset Nulling Inputs. To null the dc-offset on the I Channel and

14 VREF G Reference Voltage Output. This output voltage (1 V) is the main bias level for the device and

15 ENBL H Chip Enable Input. Active high.

17 VGIN C Gain Control Input. The voltage on this pin controls the gain on the RF and baseband VGAs.

18, 20 VDT2, VDT1 D Detector Inputs. These pin are the inputs to the on-board detector. VDT2 and VDT1, which

19 VAGC I AGC Output. This pin provides the output voltage from the on-board detector. In AGC mode,

21 VPS3 Positive Supply for Biasing and Baseband Sections. This pin should be decoupled with 0.1 µF

24 QAIN D Q Channel Baseband Amplifier Input. This pin, which has a high input impedance, should be

25, 26 QOPP, QOPN B Q Channel Differential Baseband Output. Typical output swing is equal to 1 V p-p differential.

27 COM1 LO Section Ground

I Channel Differential Baseband Output. Typical output swing is equal to 760 mV p-p differential

in AGC mode

common-mode level of the baseband amplifiers. This pin can either be connected to VREF

(Pin 14) or to a reference voltage from another device (typically an ADC).

biased to VREF (approximately 1 V). If IAIN is connected directly to IMXO, biasing will be

provided by IMXO. If an ac-coupled filter is placed between IMXO and IAIN, this pin can be

biased from VREF through a 1 kΩ resistor. The gain from IAIN to the differential outputs

IOPN/IOPP is 30 dB.

levels are equal to VREF. IMXO and QMXO are typically connected to IAIN and QAIN

respectively, either directly or through filters. These outputs have a maximum current limit of

about 1.5 mA. This allows for a 600 mV p-p swing into a 200 Ω load. This corresponds to an

input level of –40 dBm @ max gain of 39.5 dB. At lower output levels, IMXO and QMXO, can

drive a lower load resistance, subject to the same current limit.

RFIP. For a broadband 50 Ω input impedance, connect a 200 Ω resistor from the signal side of

RFIP’s coupling capacitor to ground. Please note that RFIN and RFIP are not interchangeable

differential inputs. RFIN is the ground reference for the input system.

Q Channel Mixer Outputs (IMXO, QMXO), connect a 0.1 µF capacitor from these pins to

ground. Alternately, a forced voltage of approximately 1 V on these pins will disable the offset

compensation circuit.

can be used to externally bias the inputs and outputs of the baseband amplifiers.

The gain control is applied in parallel to all VGAs. The gain control voltage range is from 0.2 V

to 1.2 V and corresponds to a gain range from +39.5 dB to –30 dB. This is the gain to the output

of the baseband VGAs (i.e., QMXO and IMXO). There is an additional 30 dB of gain in the

baseband amplifiers. Note that the gain control function has a negative sense (i.e., increasing

control voltage decreases gain). In AGC mode, this pin is connected directly to VAGC.

have high input impedances, are normally connected to IMXO and QMXO respectively.

this pin is connected directly to VGIN.

and 100 pF capacitors.

biased to VREF (approximately 1 V). If QAIN is connected directly to QMXO, biasing will be

provided by QMXO. If an ac-coupled filter is placed between QMXO and QAIN, this pin can

be biased from VREF through a 1 kΩ resistor. The gain from QAIN to the differential outputs

QOPN/QOPP is 30 dB.

The common-mode level on these pins is programmed by the voltage on VCMO.

. The common mode level on these pins is programmed by the voltage on VCMO.

REV. 0

–5–

AD8347

VPS3

VAGC

COM3

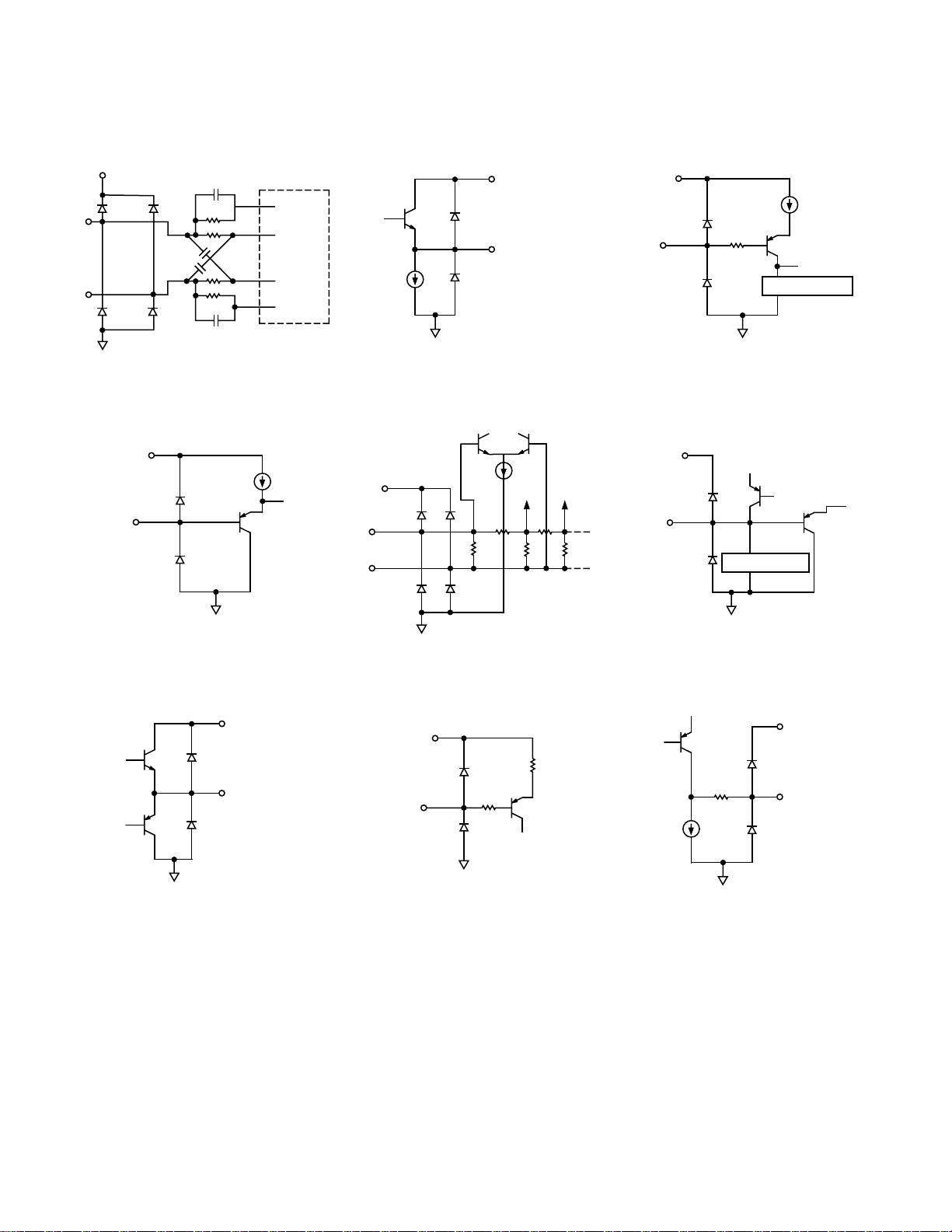

EQUIVALENT CIRCUITS

LOIN

LOIP

VPS1

COM1

IAIN

QAIN

VPS3

Circuit A

PHASE

SPLITTER

CONTINUES

RFIP

RFIN

VPS2

COM3

Circuit B

VPS3

IOPP, IOPN,

QOPP, QOPN,

IMXO, QMXO

VCMO

IOFS

QOFS

VPS3

CURRENT MIRROR

COM3

Circuit C

VPS3

CURRENT MIRROR

Circuit D

COM3

Circuit G

COM3

VPS3

VREF

COM2

Circuit E

VPS3

ENBL

COM3

Circuit H

Figure 2. Equivalent Circuits

COM3

Circuit F

Circuit I

–6–

REV. 0

Loading...

Loading...