Page 1

0.8 GHz to 2.5 GHz

FEATURES

High accuracy

1 degree rms quadrature error @ 1.9 GHz

0.2 dB I/Q amplitude balance @ 1.9 GHz

Broad frequency range: 0.8 GHz to 2.5 GHz

Sideband suppression: −46 dBc @ 0.8 GHz

Sideband suppression: −36 dBc @ 1.9 GHz

Modulation bandwidth: dc to 70 MHz

0 dBm output compression level @ 0.8 GHz

Noise floor: −147 dBm/Hz

Single 2.7 V to 5.5 V supply

Quiescent operating current: 45 mA

Standby current: 1 μA

16-lead TSSOP

APPLICATIONS

Digital and spread spectrum communication systems

Cellular/PCS/ISM transceivers

Wireless LAN/wireless local loop

QPSK/GMSK/QAM modulators

Single-sideband (SSB) modulators

Frequency synthesizers

Image reject mixer

GENERAL DESCRIPTION

The AD8346 is a silicon RFIC I/Q modulator for use from

0.8 GHz to 2.5 GHz. Its excellent phase accuracy and amplitude

balance allow high performance direct modulation to RF.

The differential LO input is applied to a polyphase network

phase splitter that provides accurate phase quadrature from

0.8 GHz to 2.5 GHz. Buffer amplifiers are inserted between

two sections of the phase splitter to improve the signal-tonoise ratio. The I and Q outputs of the phase splitter drive the

LO inputs of two Gilbert-cell mixers. Two differential V-to-I

converters connected to the baseband inputs provide the

baseband modulation signals for the mixers. The outputs of

the two mixers are summed together at an amplifier which is

designed to drive a 50 Ω load.

Quadrature Modulator

AD8346

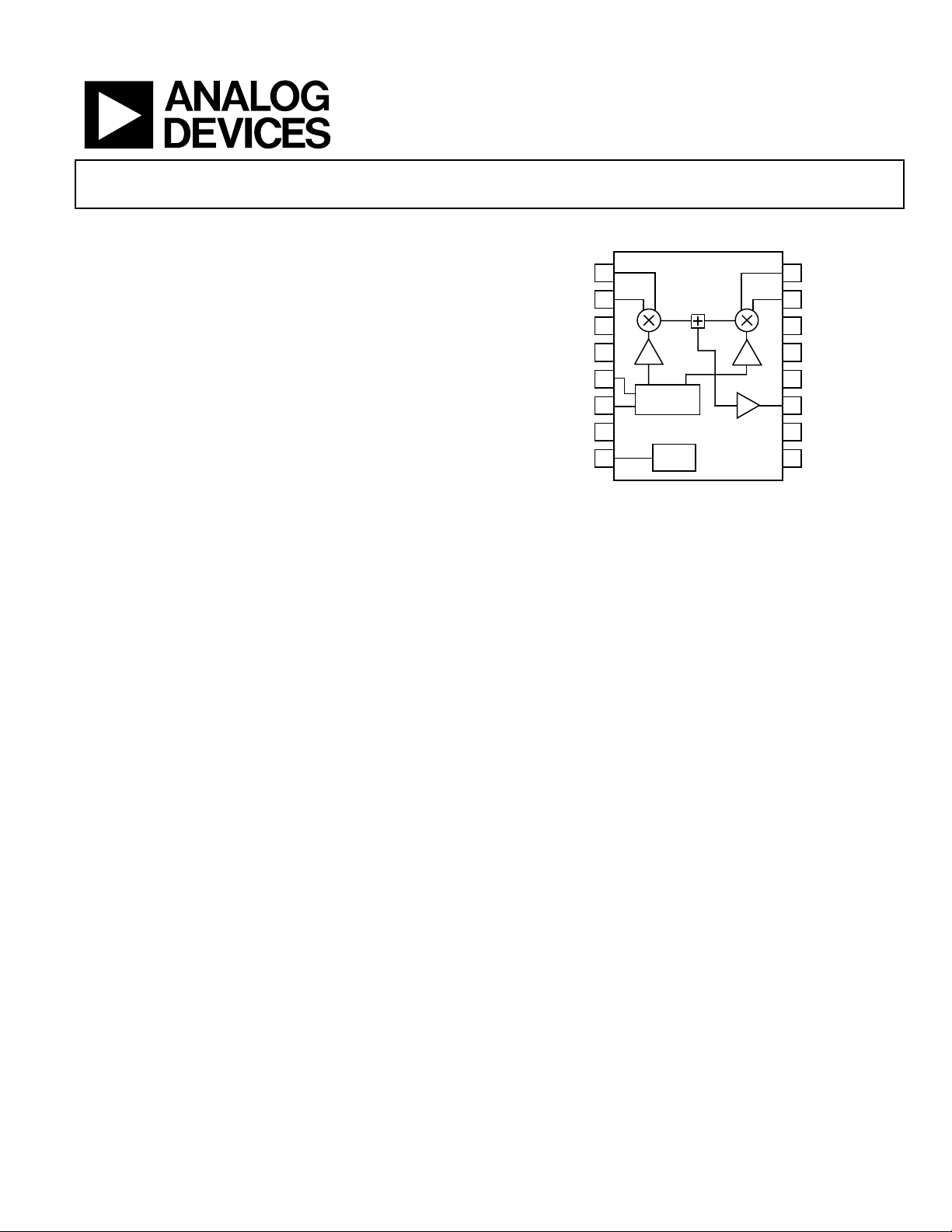

FUNCTIONAL BLOCK DIAGRAM

IBBP

1

IBBN

2

COM1

3

COM1

4

LOIN

5

LOIP

VPS1

ENBL

6

7

8

PHASE

SPLITTER

BIAS

AD8346

Figure 1.

This quadrature modulator can be used as the transmit modulator in digital systems such as PCS, DCS, GSM, CDMA, and

ISM transceivers. The baseband quadrature inputs are directly

modulated by the LO signal to produce various QPSK and

QAM formats at the RF output.

Additionally, this quadrature modulator can be used with direct

digital synthesizers in hybrid phase-locked loops to generate

signals over a wide frequency range with millihertz resolution.

The AD8346 comes in a 16-lead TSSOP package, measuring

6.5 mm × 5.1 mm × 1.1 mm. It is specified to operate over a

−40°C to +85°C temperature range and a 2.7 V to 5.5 V supply

voltage range. The device is fabricated on Analog Devices’ high

performance 25 GHz bipolar silicon process.

QBBP

16

QBBN

15

COM4

14

COM4

13

VPS2

12

VOUT

11

COM3

10

COM2

9

05335-001

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

www.analog.com

Page 2

AD8346

TABLE OF CONTENTS

Specifications..................................................................................... 3

Bias ............................................................................................... 10

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

Equivalent Circuits........................................................................... 6

Typical Performance Characteristics ............................................. 7

Circuit Description......................................................................... 10

Overview...................................................................................... 10

LO Interface................................................................................. 10

V-to-I Converter......................................................................... 10

Mixers .......................................................................................... 10

Differential-to-Single-Ended Converter .................................10

REVISION HISTORY

6/05—Rev. 0 to Rev. A

Updated Format..................................................................Universal

Changes to Figures 30, 31, 32........................................................ 14

Update Outline Dimensions ......................................................... 18

Changes to Ordering Guide.......................................................... 18

Basic Connections...................................................................... 11

LO Drive ...................................................................................... 11

RF Output.................................................................................... 11

Interface to AD9761 TXDAC® .................................................. 12

AC-Coupled Interface ............................................................... 13

Evaluation Board ............................................................................ 14

Characterization Setups................................................................. 16

SSB Setup..................................................................................... 16

CDMA Setup............................................................................... 17

Outline Dimensions ....................................................................... 18

Ordering Guide .......................................................................... 18

3/99—Revision 0: Initial Version

Rev. A | Page 2 of 20

Page 3

AD8346

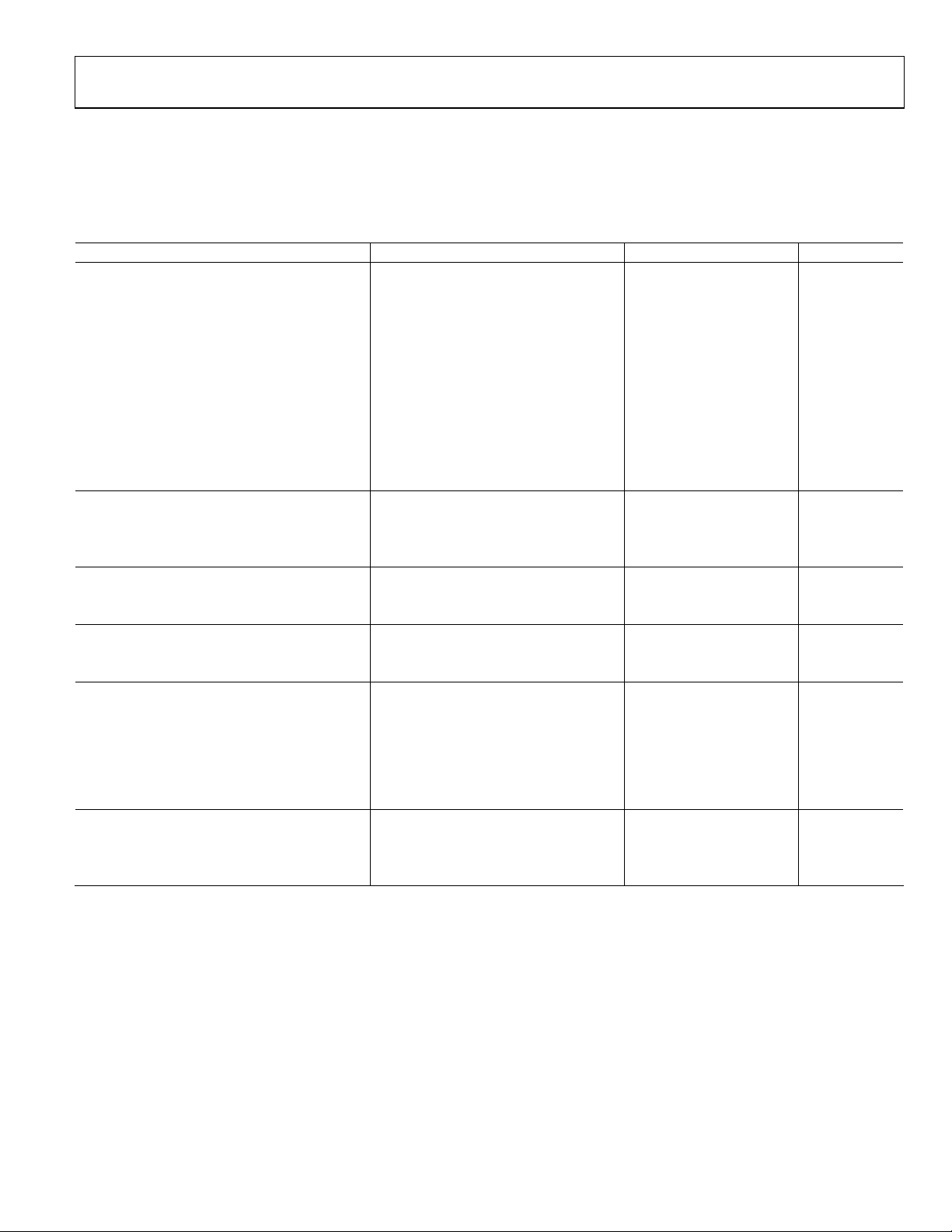

SPECIFICATIONS

VS = 5 V; TA = 25°C; LO frequency = 1900 MHz; LO level = –10 dBm; BB frequency = 100 kHz; BB inputs are dc-biased to 1.2 V; BB input

level = 1.0 V p-p each pin for 2.0 V p-p differential drive; LO source and RF output load impedances are 50 Ω, dBm units are referenced

to 50 Ω unless otherwise noted.

Table 1.

Parameters Conditions Min Typ Max Unit

RF OUTPUT

Operating Frequency 0.8 2.5 GHz

Quadrature Phase Error See Figure 35 for setup 1 Degree rms

I/Q Amplitude Balance See Figure 35 for setup 0.2 dB

Output Power I and Q channels in quadrature −13 −10 −6 dBm

Output VSWR 1.25:1

Output P1 dB −3 dBm

Carrier Feedthrough −42 −35 dBm

Sideband Suppression −36 −25 dBc

IM3 Suppression −60 dBc

Equivalent Output IP3 20 dBm

Output Noise Floor 20 MHz offset from LO −147 dBm/Hz

RESPONSE TO CDMA IS95 BASEBAND SIGNALS

ACPR (Adjacent Channel Power Ratio) See Figure 35 for setup −72 dBc

EVM (Error Vector Magnitude) See Figure 35 for setup 2.5 %

Rho (Waveform Quality Factor) See Figure 35 for setup 0.9974

MODULATION INPUT

Input Resistance 12 kΩ

Modulation Bandwidth −3 dB 70 MHz

LO INPUT

LO Drive Level −12 −6 dBm

Input VSWR 1.9:1

ENABLE

ENBL HI Threshold 2.0 V

ENBL LO Threshold 0.5 V

ENBL Turn-On Time

ENBL Turn-Off Time

POWER SUPPLIES

Voltage 2.7 5.5 V

Current Active (ENBL HI) 35 45 55 mA

Current Standby (ENBL LO) 1 20 μA

Settle to within 0.5 dB of final SSB

output power

Time for supply current to drop below

2 mA

2.5 μs

12 μs

Rev. A | Page 3 of 20

Page 4

AD8346

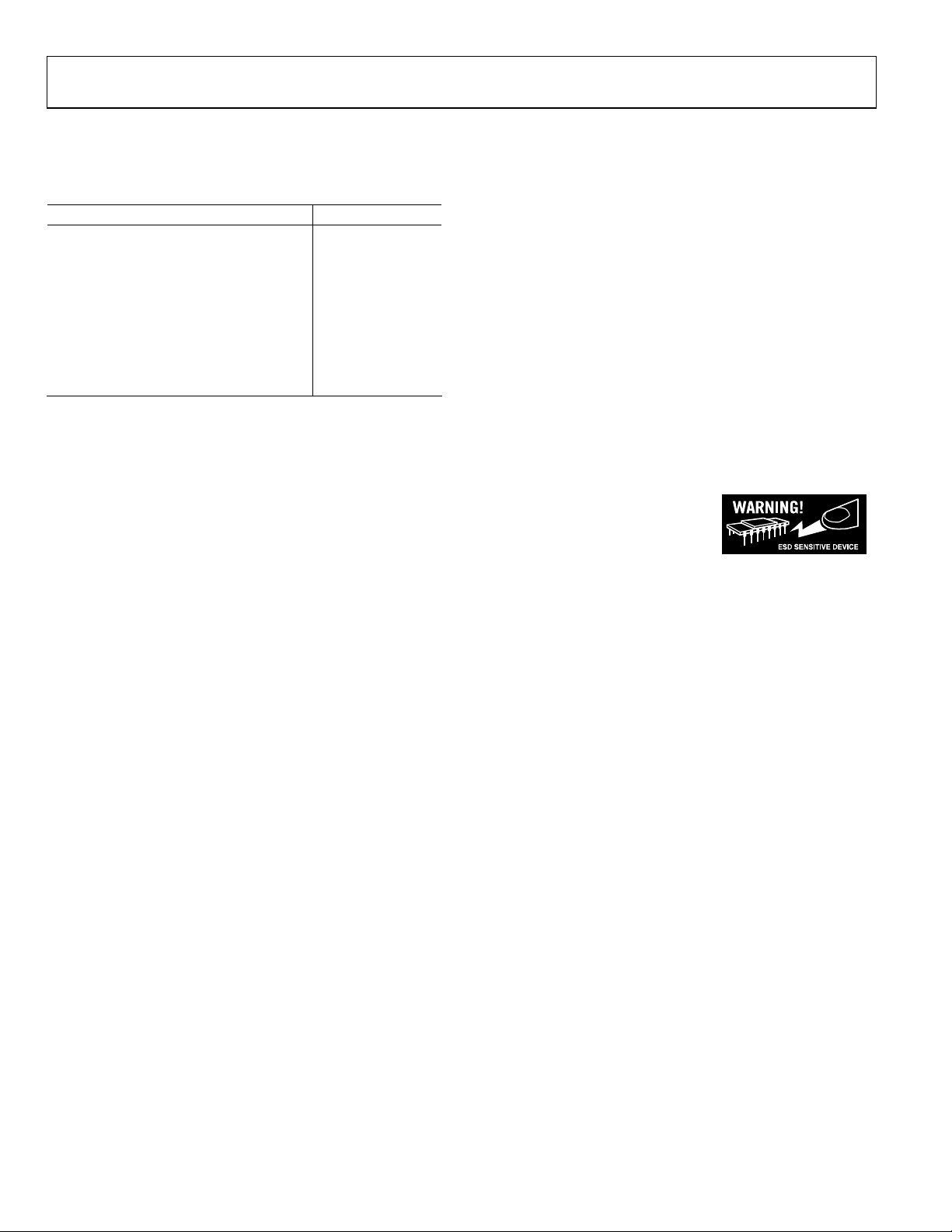

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Min Rating

Supply Voltage VPS1, VPS2 5.5 V

Input Power LOIP, LOIN (relative to 50 Ω) 10 dBm

Min Input Voltage IBBP, IBBN, QBBP, QBBN 0 V

Max Input Voltage IBBP, IBBN, QBBP, QBBN 2.5 V

Internal Power Dissipation 500 mW

θJA 125°C/W

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Lead Temperature (Soldering 60 sec) 300°C

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other condition s above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. A | Page 4 of 20

Page 5

AD8346

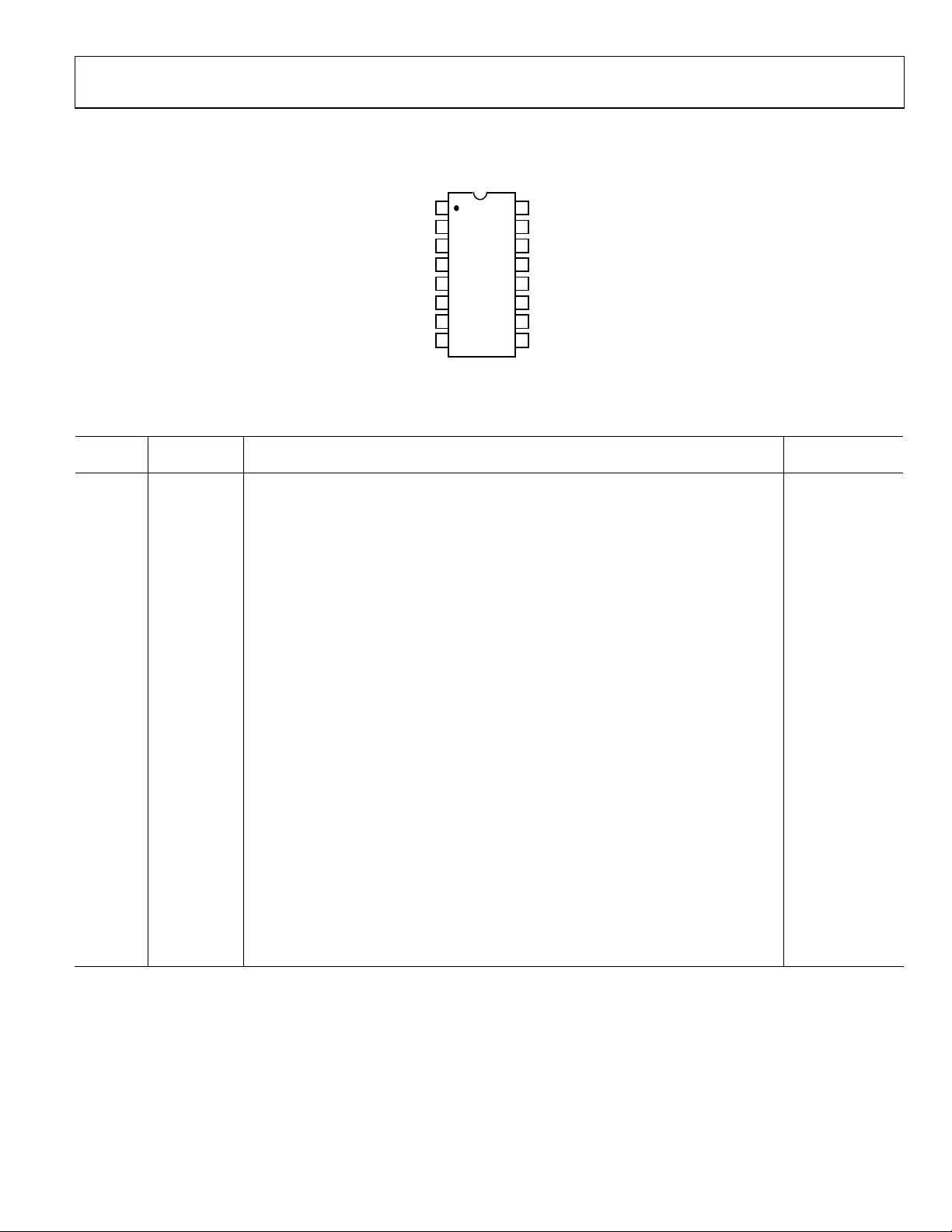

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

IBBP QBBP

2

IBBN QBBN

3

COM1 COM4

4

COM1 COM4

LOIN VPS2

LOIP VOUT

VPS1 COM3

ENBL COM2

AD8346

TOP VIEW

5

(Not to Scale)

6

7

8

16

15

14

13

12

11

10

9

05335-002

Figure 2. Pin Configuration

Table 3. Pin Function Descriptions

Equivalent

Pin No. Mnemonic Description

1 IBBP

I Channel Baseband Positive Input Pin. Input should be dc-biased to approximately 1.2 V.

Circuit

Circuit A

Nominal characterized ac swing is 1 V p-p (0.7 V to 1.7 V). This makes the differential input

2 V p-p when IBBN is 180 degrees out of phase from IBBP.

2 IBBN

I Channel Baseband Negative Input Pin. Input should be dc-biased to approximately 1.2 V.

Circuit A

Nominal characterized ac swing is 1 V p-p (0.7 V to 1.7 V). This makes the differential input

2 V p-p when IBBN is 180 degrees out of phase from IBBP.

3 COM1 Ground Pin for the LO phase splitter and LO buffers.

4 COM1 Ground Pin for the LO phase splitter and LO buffers.

5 LOIN

LO Negative Input Pin. Internal dc bias (approximately VPS1 to 800 mV) is supplied. This

Circuit B

pin must be ac coupled.

6 LOIP

LO Positive Input Pin. Internal dc bias (approximately VPS1 to 800 mV) is supplied. This pin

Circuit B

must be ac-coupled.

7 VPS1

Power Supply Pin for the bias cell and LO buffers. This pin should be decoupled using

local 100 pF and 0.01 μF capacitors.

8 ENBL Enable Pin. A high level enables the device; a low level puts the device in sleep mode. Circuit C

9 COM2 Ground Pin for the input stage of output amplifier.

10 COM3 Ground Pin for the output stage of output amplifier.

11 VOUT 50 Ω DC-Coupled RF Output. User must provide ac coupling on this pin. Circuit D

12 VPS2

Power Supply Pin for baseband input voltage to current converters and mixer core. This

pin should be decoupled using local 100 pF and 0.01 μF capacitors.

13 COM4 Ground Pin for baseband input voltage to current converters and mixer core.

14 COM4 Ground Pin for baseband input voltage to current converters and mixer core.

15 QBBN

Q Channel Baseband Negative Input. Input should be dc biased to approximately 1.2 V.

Circuit A

Nominal characterized ac swing is 1 V p-p. This makes the differential input 2 V p-p when

QBBN is 180° out of phase from QBBP.

16 QBBP

Q Channel Baseband Positive Input. Input should be dc-biased to approximately 1.2 V.

Circuit A

Nominal characterized ac swing is 1 V p-p. This makes the differential input 2 V p-p when

QBBN is 180° out of phase from QBBP.

Rev. A | Page 5 of 20

Page 6

AD8346

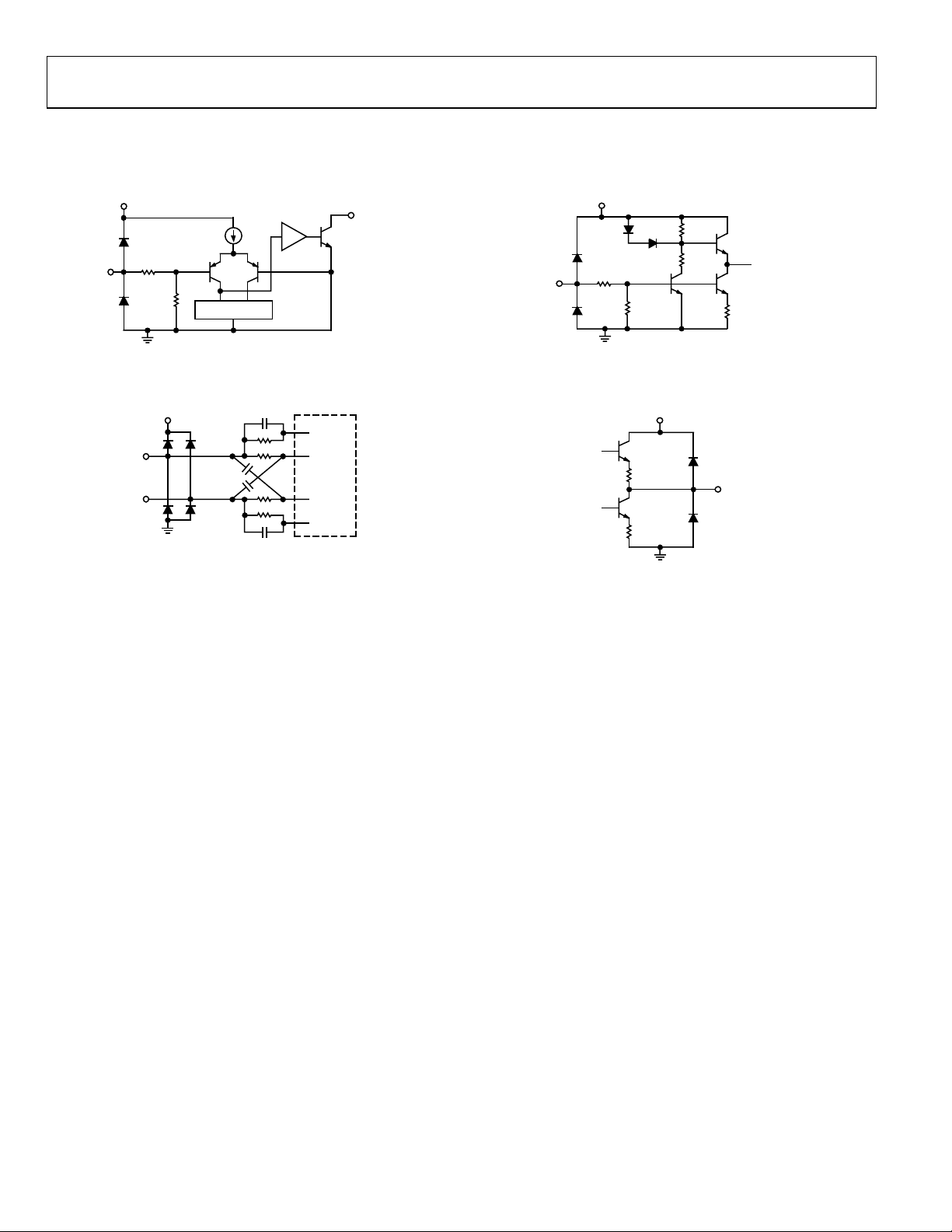

EQUIVALENT CIRCUITS

VPS2

INPUT

9kΩ

3kΩ

ACTIVE LOADS

BUFFER

TO MIXER

CORE

05335-003

ENBL

VPS1

30kΩ

40kΩ

75kΩ

75kΩ

TO BIAS FOR

STARTUP/

SHUTDOWN

780Ω

05335-005

Figure 5. Circuit C

VPS2

43Ω

43Ω

Figure 6. Circuit D

V

OUT

05335-006

LOIN

LOIP

VPS1

Figure 3. Circuit A

Figure 4. Circuit B

PHASE

SPLITTER

CONTINUES

05335-004

Rev. A | Page 6 of 20

Page 7

AD8346

TYPICAL PERFORMANCE CHARACTERISTICS

–6

–7

–8

–9

–10

–11

–12

SSB POWER (dBm)

–13

–14

–15

Figure 7. Single Sideband (SSB) Output Power (P

T = 25°C

1400 1800 22001000

1200 1600 2000 2400800

LO FREQUENCY (MHz)

VP = 5.5V

VP = 5V

VP = 2.7V

OUT

I and Q inputs driven in quadrature at baseband frequency

(F

) = 100 kHz with differential amplitude of 2.00 V p-p.

BB

–6

–7

–8

–9

–10

–11

SSB OUTPUT POWER (dBm)

–12

LO = 1900MHz, –10dBm

LO = 800MHz, –6dBm

LO = 800MHz, –10dBm

LO = 1900MHz, –6dBm

VP = 3V

05335-007

) vs. LO Frequency (FLO).

2

1

0

–1

–2

–3

–4

–5

–6

OUTPUT POWER VARIATION (dB)

–7

–8

0.1

1 100

BASEBAND FREQUENCY (MHz)

Figure 10. I and Q Input Bandwidth. F

driven with differential amplitude of 2.00 V p-p.

–10

SSB OUTPUT P1dB (dBm)

–12

2

0

–2

–4

–6

–8

VP = 2.7V

T = –40°C

VP = 5V

T = +85°C

VP = 2.7V

T = +85°C

10

=1900 MHz, I or Q inputs

LO

VP = 5V

T = –40°C

05335-010

–13

–40 –20 0 20304050607080–30 –10 10

Figure 8. SSB P

OUT

vs. Temperature. I and Q inputs driven in quadrature

TEMPERATURE (°C)

with differential amplitude of 2.00 V p -p at F

–35

–37

–39

–41

–43

–45

–47

–49

CARRIER FEEDTHROUGH (dBm)

–51

–40 –20

–30

VP = 5.5V

VP = 5V

–10 10

0 20304050607080

TEMPERATURE (°C)

Figure 9. Carrier Feedthrough vs. Temperature.

= 1900 MHz, LO input level = –10 dBm.

F

LO

VP = 3V

= 100 kHz.

BB

VP = 2.7V

05335-008

05335-009

Rev. A | Page 7 of 20

–14

1000

800

1200 1400 1600 1800 2000 2200 2400

LO FREQUENCY (MHz)

Figure 11. SSB Output 1 dB Compression Point (OP 1 dB) vs. FLO.

I and Q inputs driven in quadrature at F

= 100 kHz.

BB

30

T

= +85

°C

T

= –40°C

25

20

15

PERCENTAGE

10

5

–90

–860–82–78–74–70–66–62–58–54–50–46

CARRIER FEEDTHROUGH (dBm/

AFTER NULLING TO <–60dBm @ 25°C)

Figure 12. Histogram Showing Carrier Feedthrough Distributions

at the Temperature Extremes after Nulling at Ambient

= 1900 MHz, LO Input Level = –10 dBm.

at F

LO

05335-011

05335-012

Page 8

AD8346

–7

–30

–8

–9

–10

–11

–12

–13

SSB OUTPUT POWER (dBm)

–14

–15

–40 –20 0 20304050607080–30 –10 10

Figure 13. SSB P

VP = 5V

vs. Temperature. FLO = 1900 MHz, I and Q inputs driven in

OUT

VP = 5.5V

VP = 3V

VP = 2.7V

TEMPERATURE (°C)

quadrature with differential amplitude of 2.00 V p-p at F

T = 25°C

–36

–38

–40

–42

–44

–46

–48

–50

CARRIER FEEDTHROUGH (dBm)

–52

–54

1400 1800 22001000

1200 1600 2000 2400800

LO FREQUENCY (MHz)

VP = 3V

VP = 5V

Figure 14. Carrier Feedthrough vs. F

LO input level = –10 dBm.

–32

T = 25°C

–34

–36

–38

–40

–42

–44

SIDEBAND SUPPRESSION (dBc)

–46

–48

VP = 3V

VP = 2.7V

1500 1900 23001100

1300 1700 2100 2500900

LO FREQUENCY (MHz)

Figure 15. Sideband Suppression vs. F

VP = 5.5V

. V

= 2.7 V, I and Q inputs driven in

LO

POS

quadrature with differential amplitude of 2.00 V p-p at F

VP = 2.7V

.

LO

VP = 5V

= 100 kHz.

BB

VP = 5.5V

= 100 kHz.

BB

05335-013

05335-014

05335-015

–32

–34

–36

–38

–40

SB SUPPRESSION (dBc)

–42

–44

2 4 6 8 10 12 14 16 18 20

0

VP = 3V

VP = 5V

BASEBAND FREQUENCY (MHz)

Figure 16. Sideband Suppression vs. F

VP = 5.5V

VP = 2.7V

. FLO = 1900 MHz, I and Q inputs

BB

driven in quadrature with differential amplitude of 2.00 V p-p.

–35

–40

–45

–50

–55

DISTORTION (dBc)

–60

INPUT THIRD HARMONIC

–65

–70

VP = 5V

VP = 5.5V

–40 –20 0 20304050607080–30 –10 10

TEMPERATURE (°C)

VP = 2.7V

VP = 3V

Figure 17. Third Harmonic Distortion vs. Temperature.

=1900 MHz, I and Q inputs driven in quadrature with

F

LO

differential amplitude of 2.00 V p-p at F

= 100 kHz.

BB

0

–2

–4

T = +25

–6

–8

–10

–12

RETURN LOSS (dB)

–14

–16

–18

–20

800 1200 1600 2000

T = +85°C

Figure 18. Return Loss of LOIN Input vs. F

= 5.0 V, LOIP pin ac-coupled to ground.

V

POS

°C

1400 1800 22001000

FREQUENCY (MHz)

T = –40°C

LO

05335-016

05335-017

05335-018

2400

.

Rev. A | Page 8 of 20

Page 9

AD8346

–30

–32

–34

–36

–38

–40

SB SUPPRESSION (dBc)

–42

VP = 5.5V

VP = 5V

VP = 3V

VP = 2.7V

–40

–45

–50

–55

DISTORTION (dB)c

INPUT THIRD HARMONIC

–60

VP = 2.7V

VP = 3V

VP = 5.5V

VP = 5V

–44

–40 –20 0 20304050607080–30 –10 10

TEMPERATURE (°C)

Figure 19. Sideband Suppression vs. Temperature.

= 1900 MHz, I and Q inputs driven in quadrature

F

LO

with differential amplitude of 2.00 V p -p at F

= 100 kHz.

BB

–30

–35

–40

–45

–50

–55

–60

–65

DISTORTION (dBc)

–70

INPUT THIRD HARMONIC

–75

–80

0.5

1.0 1.5 2.0 2.5 3.0

BASEBAND DIFFERENTIAL INPUT

SSB P

OUT

3RD HARMONIC

VOLTAGE (V

p-p)

Figure 20. Third Harmonic Distortion and SSB Output

Power vs. Baseband Differential Input Voltage Level.

F

= 1900 MHz, I and Q inputs driven in quadrature at FBB = 100 kHz.

LO

0

–6

–8

–10

–12

–14

–16

–18

–20

–22

05335-019

SSB OUTPUT POWER (dBm)

05335-020

–65

2468101214161820

0

Figure 22. Third Harmonic Distortion vs. F

=1900 MHz, I and Q inputs driven in quadrature

F

LO

BASEBAND FREQUENCY (MHz)

BB

with differential amplitude of 2.00 V p-p.

52

50

48

46

44

42

SUPPLY CURRENT (mA)

40

38

36

–40 –20 0 20 40 60 80

VP = 5V

VP = 5.5V

VP = 3V

VP = 2.7V

TEMPERATURE (°C)

Figure 23. Power Supply Current vs. Temperature

0

05335-022

.

05335-023

–5

–10

V

POS

T = –40°C

OUT

= 2.7 V.

–15

–20

–25

RETURN LOSS (dB)

–30

–35

–40

800 1200 1600 2000

1400 1800 22001000

FREQUENCY (MHz)

Figure 21. Return Loss of V

T = +25°C

T = +85°C

Output vs. FLO.

2400

05335-021

–5

–10

–15

–20

–25

RETURN LOSS (dB)

–30

–35

–40

800 1200 1600 2000

1400 1800 22001000

FREQUENCY (MHz)

Figure 24. Return Loss of V

V

= 5.0 V.

POS

T = +25°C

OUT

T = –40°C

T = +85°C

Output vs. FLO.

2400

05335-024

Rev. A | Page 9 of 20

Page 10

AD8346

T

CIRCUIT DESCRIPTION

OVERVIEW

The AD8346 can be divided into the following sections: local

oscillator (LO) interface, mixer, voltage-to-current (V-to-I)

converter, differential-to-single-ended (D-to-S) converter, and

bias. A detailed block diagram of the part is shown in

Figure 25.

V-TO-I CONVERTER

Each baseband input pin is connected to an op amp driving an

emitter follower. Feedback at the emitter maintains a current

proportional to the input voltage through the transistor. This

current is fed to the two mixers in differential form.

The LO interface generates two LO signals, with 90° of phase

difference between them, to drive two mixers in quadrature.

Baseband voltage signals are converted into current form in

the V-to-I converters, feeding into two mixers. The output of

the mixers are combined to feed the D-to-S converter which

provides the 50 Ω output interface. Bias currents to each

section are controlled by the Enable (ENBL) signal. Detailed

descriptions of each section follows.

LO INTERFACE

The differential LO inputs allow the user to drive the LO differentially in order to achieve maximum performance. The LO can

be driven single-endedly but the LO feedthrough performance

is degraded, especially towards the higher end of the frequency

range. The LO interface consists of interleaved stages of

polyphase network phase splitters and buffer amplifiers. The

phase-splitter contains resistors and capacitors connected in a

circular manner to split the LO signal into I and Q paths in

precise quadrature with each other. The signal on each path

goes through a buffer amplifier to make up for the loss and high

frequency roll-off. The two signals then go through another

polyphase network to enhance the quadrature accuracy. The

broad operating frequency range of 0.8 GHz to 2.5 GHz is

achieved by staggering the RC time constants in each stage of

the phase-splitters. The outputs of the second phase-splitter are

fed into the driver amplifiers for the mixers’ LO inputs.

MIXERS

There are two double-balanced mixers, one for the in-phase

channel (I-channel) and one for the quadrature channel

(Q channel). Each mixer uses the gilbert cell design with four

cross-connected transistors. The bases of the transistors are

driven by the LO signal of the corresponding channel. The

output currents from the two mixers are summed together in

two resistors in series with two coupled on-chip inductors. The

signal developed across the R-L loads is sent to the D-to-S stage.

DIFFERENTIAL-TO-SINGLE-ENDED CONVERTER

The differential-to-single-ended converter consists of two

emitter followers driving a totem-pole output stage. Output

impedance is established by the emitter resistors in the output

transistors. The output of this stage is connected to the output

(VOUT) pin.

BIAS

A band gap reference circuit based on the Δ-VBE principle

generates the proportional-to-absolute-temperature (PTAT)

currents used by the different sections as references. The band

gap voltage is also used to generate a temperature-stable current

in the V-to-I converters to produce a temperature-independent

slew rate. When the band gap reference is disabled by pulling

down the ENBL pin, all other sections are shut off accordingly.

IBBNIBBP

V-TO-I

AD8346

LOIN

LOIP

ENBL

PHASE

SPLITTER

1

BIAS CELL

PHASE

SPLITTER

2

V-TO-I

QBBP

Figure 25. Detailed Block Diagram

Rev. A | Page 10 of 20

V-TO-I

V-TO-I

MIXER

MIXER

D-TO-S

QBBN

OU

V

05335-025

Page 11

AD8346

BASIC CONNECTIONS

The basic connections for operating the AD8346 are shown in

Figure 27. A single power supply of between 2.7 V and 5.5 V is

applied to pins VPS1 and VPS2. A pair of ESD protection

diodes are connected internally between VPS1 and VPS2 so

these must be tied to the same potential. Both pins should be

individually decoupled using 100 pF and 0.01 μF capacitors,

located as close as possible to the device. For normal operation,

the enable pin, ENBL, must be pulled high. The turn-on

threshold for ENBL is 2 V. To put the device in its power-down

mode, ENBL must be pulled below 0.5 V. Pins COM1 to COM4

should all be tied to a low impedance ground plane.

The I and Q ports should be driven differentially. This is convenient as most modern high speed DACs have differential

outputs. For optimal performance, the drive signal should be a

2 V p-p (differential) signal with a bias level of 1.2 V, that is,

each input swings from 0.7 V to 1.7 V. The I and Q inputs have

input impedances of 12 kΩ. By dc coupling the DAC to the

AD8346 and applying small offset voltages, the LO feedthrough

can be reduced to well below its nominal value of −42 dBm

(see

Figure 12).

have a bias level about 800 mV below supply. An LO drive

level of between −6 dBm and −12 dBm is required. For optimal

performance, a drive level of −10 dBm is recommended,

although a level of −6 dBm results in more stable temperature

performance (see

Figure 8). Higher levels degrade linearity

while lower levels tend to increase the noise floor.

100pF

LO

LOIP

AD8346

100pF

LOIN

05335-026

Figure 26. Single-Ended LO Drive

The LO terminal can be driven single-ended, as shown in

Figure 26 at the expense of slightly higher LO feedthrough.

LOIN is ac coupled to ground using a capacitor and LOIP is

driven through a coupling capacitor from a (single-ended)

50 Ω source (this scheme could also be reversed with LOIP

being ac-coupled to ground).

LO DRIVE

The return loss of the LO port is shown in Figure 18. No additional matching circuitry is required to drive this port from a

50 Ω source. For maximum LO suppression at the output, a

differential LO drive is recommended. In

achieved using a balun (M/A-COM Part Number ETC1-1-13).

The output of the balun is ac-coupled to the LO inputs which

IP

IN

LO

+V

5

4

S

0.01μF

T1

ETC1-1-13

C4

Figure 27, this is

C6

100pF

1

C7

2

100pF

3

C3

100pF

1

IBBP

2

IBBN

3

COM1

4

COM1

5

LOIN

6

LOIP

7

VPS1

8

ENBL

Figure 27. Basic Connections

AD8346

RF OUTPUT

The RF output is designed to drive a 50 Ω load, but must be accoupled, as shown in

in quadrature by 2 V p-p signals, the resulting output power is

about −10 dBm (see

over frequency).

16

QBBP

15

QBBN

14

COM4

13

COM4

12

VPS2

VOUT

COM3

COM2

11

10

9

100pF

Figure 27. If the I and Q inputs are driven

Figure 7 for variations in output power

QP

QN

+V

C1

C5

100pF

C2

0.01μF

S

VOUT

05335-027

Rev. A | Page 11 of 20

Page 12

AD8346

INTERFACE TO AD9761 TXDAC®

Figure 28 shows a dc-coupled current output DAC interface.

The use of dual-integrated DACs, such as the AD9761 with

specified ±0.02 dB and ±0.004 dB gain and offset matching

characteristics, ensures minimum error contribution (over

temperature) from this portion of the signal chain. The use of a

precision thin-film resistor network sets the bias levels precisely

to prevent the introduction of offset errors, which increase LO

feedthrough. For instance, selecting resistor networks with a

0.1% ratio matching characteristics maintains 0.03 dB gain and

offset matching performance.

Using resistive division, the dc bias level at the I and Q inputs

to the AD8346 is set to approximately 1.2 V. Each of the four

current outputs of the DAC delivers a full-scale current of

+5V

DVDD DCOM AVDD

IOUTA

I

IOUTB

DAC

QOUTA

Q

QOUTB

DAC

0.1

μ

Ω

F

Figure 28. AD8346 Interface to AD9761 TxDAC

DAC

DATA

INPUTS

SELECT

WRITE

CLOCK

MUX

CONTROL

LATCH

LATCH

SLEEP FS ADJ REFIO

2

I

Q

×

AD9761

2

×

R

SET

2k

100

100

10 mA, giving a voltage swing of 0 V to 1 V (at the DAC

output). This results in a 0.5 V p-p swing at the I and Q inputs

of the AD8346 (resulting in a 1 V p-p differential swing).

Note that the ratio matching characteristics of the resistive

network, as opposed to its absolute accuracy, is critical in

preserving the gain and offset balance between the I and Q

signal path.

By applying small dc offsets to the I and Q signals from the

DAC, the LO suppression can be reduced from its nominal

value of −42 dBm to as low as −60 dBm while holding to

approximately −50 dBm over temperature (see

a plot of LO feedthrough over temperature for an offset

compensated circuit).

5V

634

Ω

Ω

WITH V

CM

0.1μF

Ω

= 1.2V

IBBP

IBBN

QBBP

QBBN

VPS1 VPS2

Σ

PHASE

SPLITTER

AD8346

C

100

100

FILTER

Ω

Ω

500Ω500

500

Ω

500

Ω

500Ω500

500

C

FILTER

500

Ω

Ω

0.5V p-p EACH PIN

Ω

Ω

Figure 12 for

VOUT

LOIP

LOIN

05335-028

Rev. A | Page 12 of 20

Page 13

AD8346

AC-COUPLED INTERFACE

An ac-coupled interface can also be implemented, as shown in

Figure 29. This is an advantage because there is almost no

voltage loss due to the biasing network, allowing the AD8346

inputs to be driven by the full 2 V p-p differential signal from

the AD9761 (each of the DAC’s 4 outputs delivering 1 V p-p).

The network shown has a high-pass corner frequency of

approximately 14.3 kHz (note that the 12 kΩ input impedance

of the AD8346 has been factored into this calculation).

Increasing the resistors in the network or increasing the

coupling capacitance reduces the corner frequency further.

As in the dc-coupled case, the bias levels on the I and Q inputs

should be set to as precise a level as possible, relative to each

other. This prevents the introduction of additional input offset

voltages. In

Figure 29, the bias level on each input is set to

approximately 1.2 V. The 2.43 kΩ resistors should have a ratio

tolerance of 0.1% or better.

5V

DVDD DCOM AVDD

IOUTA

I

DAC

IOUTB

QOUTA

Q

DAC

QOUTB

0.1μF

Figure 29. AC-Coupled DAC Interface

DAC

DATA

INPUTS

SELECT

WRITE

CLOCK

MUX

CONTROL

LATCH

2 ×

I

AD9761

LATCH

SLEEP FS ADJ REFIO

2 ×

Q

R

SET

2kΩ

Note that the LO suppression can be manually optimized by

replacing a portion of the four top 2.43 kΩ resistors with

potentiometers. In this case, the bottom four resistors in the

biasing network no longer need to be precision devices.

5V

1kΩ

CM

2.43kΩ

= 1.2V

0.1μF

IBBP

IBBN

QBBP

QBBN

VPS1 VPS2

Σ

PHASE

SPLITTER

AD8346

100Ω

C

FILTER

100Ω

100Ω

100Ω

C

FILTER

0.01μF

2.43kΩ

0.01μF

0.01μF

0.01μF

2.43kΩ

2.43kΩ

2.43kΩ

2.43kΩ

2.43kΩ

2.43kΩ

1V p-p EACH PIN

WITH V

VOUT

LOIP

LOIN

05335-029

Rev. A | Page 13 of 20

Page 14

AD8346

EVALUATION BOARD

The schematic of the AD8346 evaluation board is shown in

Figure 30. This is a 4-layer FR4 board; the two center layers are

used as ground planes and the top and bottom layers are used

for signal and power.

shows the silkscreen. The evaluation board circuit closely

follows the basic connections circuit shown in

Figure 31 shows the layout and Figure 32

Figure 27.

All connectors are of the SMA type. The I and Q inputs are

provided with pads for implementing a simple RC filter

network. The local oscillator input is driven through a balun

(M/A-COM Part Number ETC1-1-13).

Slide SW1 to the A position to connect the ENBL pin to +V

S

via the 10 kΩ pull-up resistor REP. Slide SW1 to the B position

to disable the device by grounding the ENOP pin through the

49.9 Ω pull-down resistor REG. The device may be enabled via

an external voltage applied to the SMA connector ENOP or TP2.

CIP

OPEN

REP

10k

T1

0.01

RIP

0

Ω

RIN

0

Ω

CIN

OPEN

RLON

OPEN

1

2

3

C1

μ

F

Ω

CLON

100pF

CLOP

100pF

RLOP

OPEN

ENOP

R7

C2

0

Ω

100pF

RIS

OPEN

TP2

1

2

3

4

5

6

7

8

SW1

Figure 30. Evaluation Board Schematic

LO

IP

IN

ENOP

RLOS

OPEN

+V

S

5

ETC1-1-13

4

IBBP

IBBN

COM1

COM1

LOIN

LOIP

VPS1

ENBL

REG

49.9k

AD8346

A

B

Ω

QBBP

QBBN

COM4

COM4

VPS2

VOUT

COM3

COM2

CQP

RQS

OPEN

100pF

OPEN

CQN

OPEN

C4

CVO

100pF

16

15

14

13

12

11

10

9

RQP

0

Ω

RQN

0

Ω

R2

0

Ω

C3

0.01

μ

F

QP

QN

+V

S

VOUT

05335-030

Rev. A | Page 14 of 20

Page 15

AD8346

Figure 31. Layout of Evaluation Board

05335-031

Figure 32. Silkscreen of Evaluation Board

Rev. A | Page 15 of 20

05335-032

Page 16

AD8346

–

CHARACTERIZATION SETUPS

SSB SETUP

Two main setups were used to characterize this product. These

setups are shown in

the setup used to evaluate the product as an SSB. The AD8346

motherboard had circuitry that converted the single-ended

I and Q inputs from the arbitrary function generator to differential inputs with a dc bias of approximately 1.2 V. In addition,

the motherboard also provided connections for power supply

routing. The HP34970A and its associated plug-in 34901 were

used to monitor power supply currents and voltages being

supplied to the AD8346 evaluation board (a full schematic of

Figure 33 and Figure 35. Figure 33 shows

IEEE

D1 D2 D3

34901 34907 34907

D1 D2 D3

VPS1

VN

GND

VP

P1 IN IP QP QN

IEEE

HP3631

+15V MAX

COM

+25V MAX

–25V MAX

HP34970A

AD8346

MOTHERBOARD

the AD8346 evaluation board can be found in

Figure 30).

The two HP34907 plug-ins were used to provide additional

miscellaneous dc and control signals to the motherboard. The

LO was driven by an RF signal generator (through the balun on

the evaluation board to present a differential LO signal to the

device) and the output was measured with a spectrum analyzer.

With the I channel driven with a sine wave and the Q channel

driven with a cosine wave, the lower sideband is the single

sideband output. The typical SSB output spectrum is shown in

Figure 34.

IN

TEKAFG2020

OUTPUT 1

OUTPUT

2

ARB FUNC. GEN

IEEE

I IN

Q

IEEE

HP8648C

RFOUT

IN

LO

ENBL

IEEE

PC CONTROLLER

IP QP

AD8346

EVAL BOARD

P1

QN

VOUT

HP8593E

SWEEP OUT

RF I/P

CAL OUT

SPECTRUM

ANALYZER

28VOLT

IEEE

05335-033

Figure 33. Evaluation Board SSB Test Setup

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

100

CENTER 1.9GHz

50kHz/ SPAN 500kHz

05335-034

Figure 34. Typical SSB Output Spectrum

Rev. A | Page 16 of 20

Page 17

AD8346

–

–

–

CDMA SETUP

For evaluating the AD8346 with CDMA waveforms, the setup

shown in

Figure 35 was used. This is essentially the same setup

as that used for the single sideband characterization, except that

the AFG2020 was replaced with the AWG2021 for providing the

I and Q input signals, and the spectrum analyzer used to monitor

the output was changed to an FSEA30 Rohde & Schwarz analyzer

with vector demodulation capability. The I/Q input signals for

these measurements were IS95 baseband signals generated with

Tektronix I/Q SIM software and downloaded to the AWG2021.

IEEE

D1 D2 D3

34901 34907 34907

D1 D2 D3

VPS1

VN

GND

VP

P1 IN IP QP QN

IEEE

HP3631

+15V MAX

COM

+25V MAX

–25V MAX

HP34970A

AD8346

MOTHERBOARD

For measuring ACPR, the I/Q input signals used were generated

with Pilot (Walsh Code 00), Sync (WC 32), Paging (WC 01),

and 6 Traffic (WC 08, 09, 10, 11, 12, 13) channels active. The

I/Q SIM software was set for 32× oversampling and was using a

BS equifilter.

Figure 36 shows the typical output spectrum for

this configuration. The ACPR was measured 885 kHz away

from the carrier frequency.

For performing EVM, Rho, phase, and amplitude balance

measurements, the I/Q input signals used were generated with

only the pilot channel (Walsh Code 00) active. The I/Q SIM

software was set for 32× oversampling using a CDMA equifilter.

IN

TEKAFG2020

OUTPUT 1

OUTPUT

2

ARB FUNC. GEN

IEEE

I IN

Q

IP QP

AD8346

EVAL BOARD

PC CONTROLLER

VOUT

P1

QN

FSEA30

RF I/P

SPECTRUM

ANALYZER

IEEE

05335-035

IEEE

HP8648C

RFOUT

IN

LO

ENBL

IEEE

Figure 35. Evaluation Board CDMA Test Setup

–20

–30

–40

–50

–60

–70

–80

–90

100

110

120

CENTER 1.9GHz

CH PWR = –20.7dBm

ACP UPR = –71.8dBc

ACP LWR = –71.7dBc

187.5kHz/ SPAN 1.875MHz

05335-036

Figure 36. Typical CDMA Output Spectrum

Rev. A | Page 17 of 20

Page 18

AD8346

OUTLINE DIMENSIONS

5.10

5.00

4.90

0.15

0.05

4.50

4.40

4.30

PIN 1

16

0.65

BSC

COPLANARITY

COMPLIANT TO JEDEC STANDARDS MO-153AB

0.10

0.30

0.19

9

81

1.20

MAX

SEATING

PLANE

6.40

BSC

0.20

0.09

8°

0°

0.75

0.60

0.45

Figure 37.16-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-16)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD8346ARU −40°C to +85°C 16-Lead Thin Shrink Small Outline Package (TSSOP) RU-16

AD8346ARU-REEL −40°C to +85°C 16-Lead (TSSOP) 13" Tape and Reel RU-16

AD8346ARU-REEL7 −40°C to +85°C 16-Lead (TSSOP) 7" Tape and Reel RU-16

AD8346ARUZ-REEL1 −40°C to +85°C 16-Lead (TSSOP) 13" Tape and Reel RU-16

AD8346ARUZ-REEL7

AD8346-EVAL Evaluation Board

1

Z = Pb-free part.

1

−40°C to +85°C 16-Lead (TSSOP) 7" Tape and Reel RU-16

Rev. A | Page 18 of 20

Page 19

AD8346

NOTES

Rev. A | Page 19 of 20

Page 20

AD8346

NOTES

©2005 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective companies.

C05335–0–6/05(A)

Rev. A | Page 20 of 20

Loading...

Loading...