Page 1

General-Purpose, −55°C to +125°C,

VGA

FEATURES

Low noise

Voltage noise: 3 nV/√Hz

Current noise: 3 pA/√Hz

Small signal BW: 115 MHz

Large signal BW: 2 V p-p = 80 MHz

Slew rate: 550 V/µs, 2 V p-p

Gain ranges (specified)

−14 dB to +46 dB,

0 dB to 60 dB

Gain scaling: 50 dB/V

DC-coupled

Single-ended input and output

Supplies: ±3 V to ±12 V

Temperature Range: −55°C to +125°C

Power

150 mW @ ±3 V, −55°C < T < +125°C

84 mW @ ±3 V, PWRA = 3 V

APPLICATIONS

Industrial process controls

High performance AGC systems

I/Q signal processing

Video

Industrial and medical ultrasound

Radar receivers

Wide Bandwidth, DC-Coupled VGA

AD8336

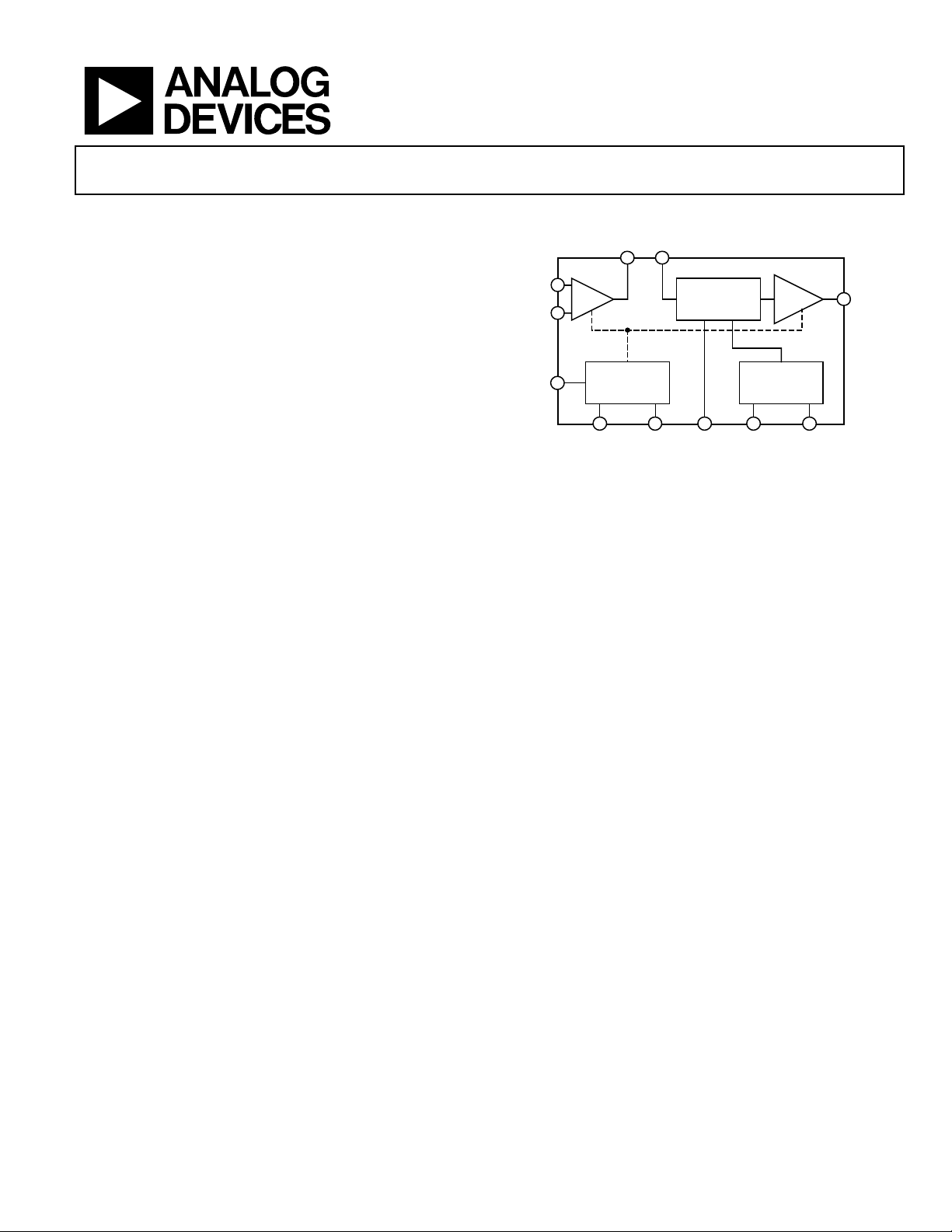

FUNCTIONAL BLOCK DIAGRAM

IPRAO

98

ATTENUATOR

–60dB TO 0dB

BIAS

13 3 11 12

VCOMVPOS GPOS

Figure 1.

34d BPrA

GAIN CONTROL

INTERFACE

GNEG

1

VOUT

06228-001

INPP

INPN

PWR A

AD8336

4

+

–

5

2

10

VNEG

GENERAL DESCRIPTION

The AD8336 is a low noise, single-ended, linear-in-dB, generalpurpose variable gain amplifier, usable over a large range of

supply voltages. It features an uncommitted preamplifier

(preamp) with a usable gain range of 6 dB to 26 dB established

by external resistors in the classical manner. The VGA gain

range is 0 dB to 60 dB, and its absolute gain limits are −26 dB to

+34 dB. When the preamplifier gain is adjusted for 12 dB, the

combined 3 dB bandwidth of the preamp and VGA is 100 MHz,

and the amplifier is fully usable to 80 MHz. With ±5 V supplies,

the maximum output swing is 2 V p-p.

Thanks to its X-Amp® architecture, excellent bandwidth

uniformity is maintained across the entire gain range of the

VGA. Intended for a broad spectrum of applications, the

differential gain control interface provides precise linear-in-dB

gain scaling of 50 dB/V over the temperature span of −55°C to

+125 °C. The differential gain control is easy to interface with a

variety of external circuits within the common-mode voltage

limits of the AD8336.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

The large supply voltage range makes the AD8336 particularly

suited for industrial medical applications and for video circuits.

Dual-supply operation enables bipolar input signals, such as

those generated by photodiodes or photomultiplier tubes.

The fully independent voltage feedback preamp allows both

inverting and noninverting gain topologies, making it a fully

bipolar VGA. The AD8336 can be used within the specified

gain range of −14 dB to +60 dB by selecting a preamp gain

between 6 dB and 26 dB and choosing appropriate feedback

resistors. For the nominal preamp gain of 4×, the overall gain

range is −14 dB to +46 dB.

In critical applications, the quiescent power can be reduced by

about half by using the power adjust pin, PWRA. This is

especially useful when operating with high supply voltages of

up to ±12 V, or at high temperatures.

The operating temperature range is −55°C to +125°C. The

AD8336 is available in a 16-lead LFCSP (4 mm × 4 mm).

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

www.analog.com

Page 2

AD8336

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configuration and Functional Descriptions.......................... 7

Typical Performance Characteristics ............................................. 8

Test Cir c ui t s .....................................................................................17

Theory of Operation ...................................................................... 21

Overview...................................................................................... 21

Preamplifier ................................................................................. 21

VGA.............................................................................................. 21

Setting the Gain.......................................................................... 22

Noise ............................................................................................ 22

Offset Voltage.............................................................................. 22

Applications..................................................................................... 23

Amplifier Configuration ........................................................... 23

Preamplifier................................................................................. 23

Circuit Configuration for Noninverting Gain ................... 23

Circuit Configuration for Inverting Gain........................... 24

Using t he Power Adjust Feature ............................................... 24

Driving Capacitive Loads.......................................................... 24

Evaluation Board ............................................................................ 25

Optional Circuitry...................................................................... 25

Board Layout Considerations................................................... 25

Outline Dimensions ....................................................................... 28

Ordering Guide .......................................................................... 28

REVISION HISTORY

10/06—Revision 0: Initial Version

Rev. 0 | Page 2 of 28

Page 3

AD8336

SPECIFICATIONS

VS = ±5 V, T = 25°C, gain range = −14 dB to +46 dB, preamp gain = 4×, f = 1 MHz, CL = 5 pF, RL = 500 Ω, PWRA = GND, unless

otherwise specified.

Table 1.

Parameter Conditions Min Typ Max Unit

PREAMPLIFIER

−3 dB Small Signal Bandwidth V

−3 dB Large Signal Bandwidth V

Bias Current, Either Input 725 nA

Differential Offset Voltage ±600 μV

Input Resistance 900 kΩ

Input Capacitance 3 pF

PREAMPLIFIER + VGA

–3 dB Small Signal Bandwidth V

V

V

V

–3 dB Large Signal Bandwidth V

V

V

V

Slew Rate V

Short-Circuit Preamp Input Voltage

Noise Spectral Density

Input Current Noise Spectral Density 3.0 pA/√Hz

Output Referred Noise V

V

V

V

V

V

DYNAMIC PERFORMANCE

Harmonic Distortion V

HD2 f = 1 MHz –58 dBc

HD3 f = 1 MHz –68 dBc

HD2 f = 10 MHz –60 dBc

HD3 f = 10 MHz –60 dBc

Input 1 dB Compression Point V

V

Two-Tone Intermodulation V

Distortion (IMD3) V

V

V

Output Third-Order Intercept V

V

V

V

Overdrive Recovery V

Group Delay Variation 1 MHz < f < 10 MHz, full gain range ±1 ns

PrA Gain = 20 × 1 MHz < f < 10 MHz, full gain range ±3 ns

= 10 mV p-p 150 MHz

OUT

= 2 V p-p 85 MHz

OUT

= 10 mV p-p 115 MHz

OUT

= 10 mV p-p, PWRA = 5 V 40 MHz

OUT

= 10 mV p-p, PrA gain = 20× 20 MHz

OUT

= 10 mV p-p, PrA gain = –3× 125 MHz

OUT

= 2 V p-p 80 MHz

OUT

= 2 V p-p, PWRA = 5 V 30 MHz

OUT

= 2 V p-p, PrA gain = 20× 20 MHz

OUT

= 2 V p-p, PrA gain = –3× 100 MHz

OUT

= 2 V p-p 550 V/µs

OUT

±3 V ≤ V

≤ ±12 V

S

= 0.7 V, PrA gain = 4× 600 nV/√Hz

GAIN

= –0.7 V, PrA gain = 4× 190 nV/√Hz

GAIN

= 0.7 V, PrA gain = 20× 2500 nV/√Hz

GAIN

= –0.7 V, PrA gain = 20× 200 nV/√Hz

GAIN

= 0.7 V, –55°C ≤ T ≤ +125°C 700 nV/√Hz

GAIN

= –0.7 V, –55°C ≤ T ≤ +125°C 250 nV/√Hz

GAIN

= 0 V, V

GAIN

= –0.7 V 11 dBm

GAIN

= +0.7 V –23 dBm

GAIN

= 0 V, V

GAIN

= 0 V, V

GAIN

= 0 V, V

GAIN

= 0 V, V

GAIN

= 0 V, V

GAIN

= 0 V, V

GAIN

= 0 V, V

GAIN

= 0 V, V

GAIN

= 0.7 V, VIN = 100 mV p-p to 5 mV p-p 50 ns

GAIN

= 1 V p-p

OUT

= 1 V p-p, f1 = 0.95 MHz, f2 = 1.05 MHz –71 dBc

OUT

= 1 V p-p, f1 = 9.95 MHz, f2 = 10.05 MHz –69 dBc

OUT

= 2 V p-p, f1 = 0.95 MHz, f2 = 1.05 MHz –60 dBc

OUT

= 2 V p-p, f1 = 9.95 MHz, f2 = 10.05 MHz –58 dBc

OUT

= 1 V p-p, f = 1 MHz 34 dBm

OUT

= 1 V p-p, f = 10 MHz 32 dBm

OUT

= 2 V p-p, f = 1 MHz 34 dBm

OUT

= 2 V p-p, f = 10 MHz 33 dBm

OUT

3.0 nV/√Hz

1

Rev. 0 | Page 3 of 28

Page 4

AD8336

Parameter Conditions Min Typ Max Unit

ABSOLUTE GAIN ERROR

−0.6 V < V

−0.5 V < V

−0.5 V < V

−0.5 V < V

−0.5 V < V

0.5 V < V

0.6 V < V

GAIN CONTROL INTERFACE

Gain Scaling Factor 48 49.9 52 dB/V

Intercept Preamp + VGA 16.4 dB

VGA Only 4.5 dB

Gain Range 58 60 62 dB

Input Voltage (V

Input Current 1 μA

Input Capacitance pF

Response Time 60 dB gain change 300 ns

OUTPUT PERFORMANCE

Output Impedance, DC to 10 MHz ±3 V ≤ VS ≤ ±12 V 2.5 Ω

Output Signal Swing RL ≥ 500 Ω (for |V

R

Output Current Linear operation − minimum discernable distortion 20 mA

Short-Circuit Current VS = ±3 V +123/−72 mA

V

V

Output Offset Voltage V

±3 V ≤ VS ≤ ±12 V −200 mV

−55°C ≤ T ≤ +125°C −200 mV

PWRA Pin

Normal Power (Logic Low) VS = ±3 V 0.7 V

Low Power (Logic High) VS = ±3 V 1.5 V

Normal Power (Logic Low) VS = ±5 V 1.2 V

Low Power (Logic High) VS = ±5 V 2.0 V

Normal Power (Logic Low) VS = ±12 V 3.2 V

Low Power (Logic High) VS = ±12 V 4.0 V

POWER SUPPLY

Supply Voltage Operating Range ±3 ±12 V

Quiescent Current

VS = ±3 V 22 25 30

−55°C ≤ T ≤ +125°C 23 to 31 mA

PWRA = 3 V 10 14 18

VS = ±5 V 22 26 30

−55°C ≤ T ≤ +125°C 23 to 31 mA

PWRA = 5 V 10 14 18

VS = ±12 V 23 28 31

−55°C ≤ T ≤ +125°C 24 to 33 mA

PWRA = 5 V 16

2

) Range No foldover −V

GAIN

−0.7 V < V

≥ 1 kΩ (for |V

L

= ±5 V +123/−72 mA

S

= ±12 V +72/−73 mA

S

= 0.7 V, gain = 200× −250 −125 150 mV

GAIN

< −0.6 V 0 1 to 5 6 dB

GAIN

< −0.5 V 0 0.5 to1.5 3 dB

GAIN

< 0.5 V −1.25 ±0.2 +1.25 dB

GAIN

< 0.5 V, ±3 V ≤ VS ≤ ±12 V ±0.5 1.25 dB

GAIN

< 0.5 V, −55 °C ≤ T ≤ +125 °C ±0.5 dB

GAIN

< 0.5 V, PrA gain = −3× ±0.5 dB

GAIN

< 0.6 V −4.0 −1.5 to −3.0 0 dB

GAIN

< 0.7 V −9.0 −1 to −5 0 dB

GAIN

| ≤ ±5V); RL ≥ 1 kΩ above that |V

SUPPLY

| = ±12V) |V

SUPPLY

+V

S

SUPPLY

SUPPLY

S

| − 1.5 V

| − 2.25 V

V

Rev. 0 | Page 4 of 28

Page 5

AD8336

Parameter Conditions Min Typ Max Unit

Power Dissipation VS = ±3 V 150 mW

V

V

PSRR V

1

All dBm values are calculated with 50 Ω reference, unless otherwise noted.

2

Conformance to theoretical gain expression (see the S section). etting the Gain

= ±5 V 260 mW

S

= ±12 V 672 mW

S

= 0.7 V, f = 1 MHz −40 dB

GAIN

Rev. 0 | Page 5 of 28

Page 6

AD8336

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage (VPOS, VNEG)

Input Voltage (INPP, INPN) VPOS, VNEG

Gain Voltage (GPOS, GNEG) VPOS, VNEG

PWRA 5 V, GND

Power Dissipation

VS ≤ ±5 V 0.43 W

±5 V < VS ≤ ±12 V 1.12 W

Operating Temperature Range

±3 V < VS ≤ ±10 V –55°C to +125°C

±10 V < VS ≤ ±12 V –55°C to +85°C

Storage Temperature Range –65°C to +150°C

Lead Temperature (Soldering 60 sec) 300°C

Thermal Data (4-layer JEDEC board, no air

flow, exposed pad soldered to PC board)

θ

JA

θ

JB

θ

JC

Ψ

JT

Ψ

JB

±15 V

58.2°C/W

35.9°C/W

9.2°C/W

1.1°C/W

34.5°C/W

Stresses above those listed under the Absolute Maximum

Ratings may cause permanent damage to the device. This is a

stress rating only; functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 6 of 28

Page 7

AD8336

A

V

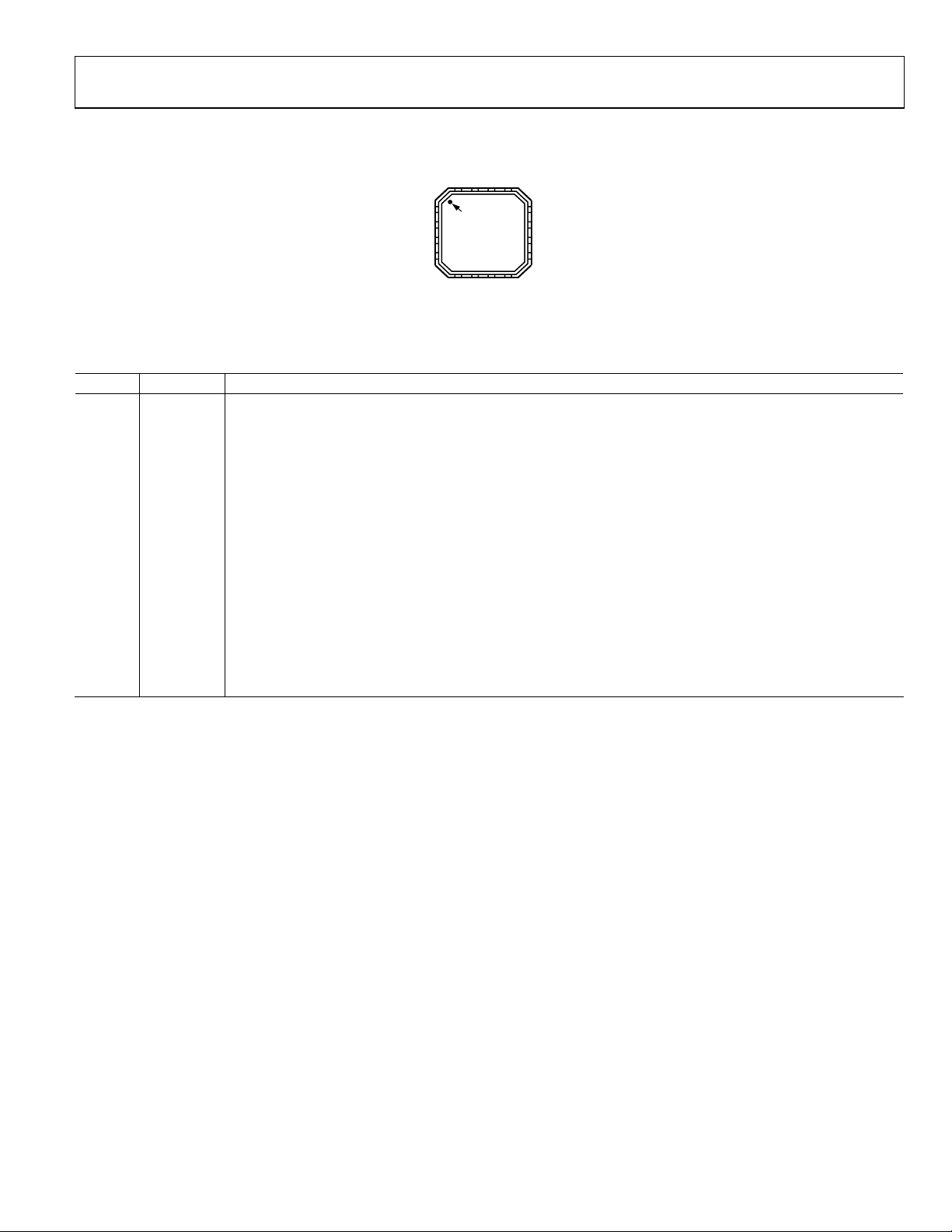

PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

VPOS

NCNCNC

14 131516

1

VOUT

PWR

COM

INPP

NC = NO CONNECT

PIN 1

INDICATOR

2

AD8336

3

TOP VIEW

(Not to Scale)

4

INPN

Figure 2. 16-Lead LFCSP Pin Configuration

Table 3. Pin Function Descriptions

Pin No. Mnemonic Function

1 VOUT Output Voltage.

2 PWRA Power Control. Normal power when grounded; power reduced by half if V

3 VCOM Common-Mode Voltage. Normally GND when using a dual supply.

4 INPP Positive Input to Preamp.

5 INPN Negative Input to Preamp.

6 NC No Connect.

7 NC No Connect.

8 PRAO Preamp Output.

9 VGAI VGA Input.

10 VNEG Negative Supply.

11 GPOS Positive Gain Control Input.

12 GNEG Negative Gain Control Input.

13 VPOS Positive Supply.

14 NC No Connect.

15 NC No Connect.

16 NC No Connect.

NC

NC

12

GNEG

11

GPOS

10

VNEG

9

VGAI

8765

PRAO

06228-002

is pulled high.

PWRA

Rev. 0 | Page 7 of 28

Page 8

AD8336

R

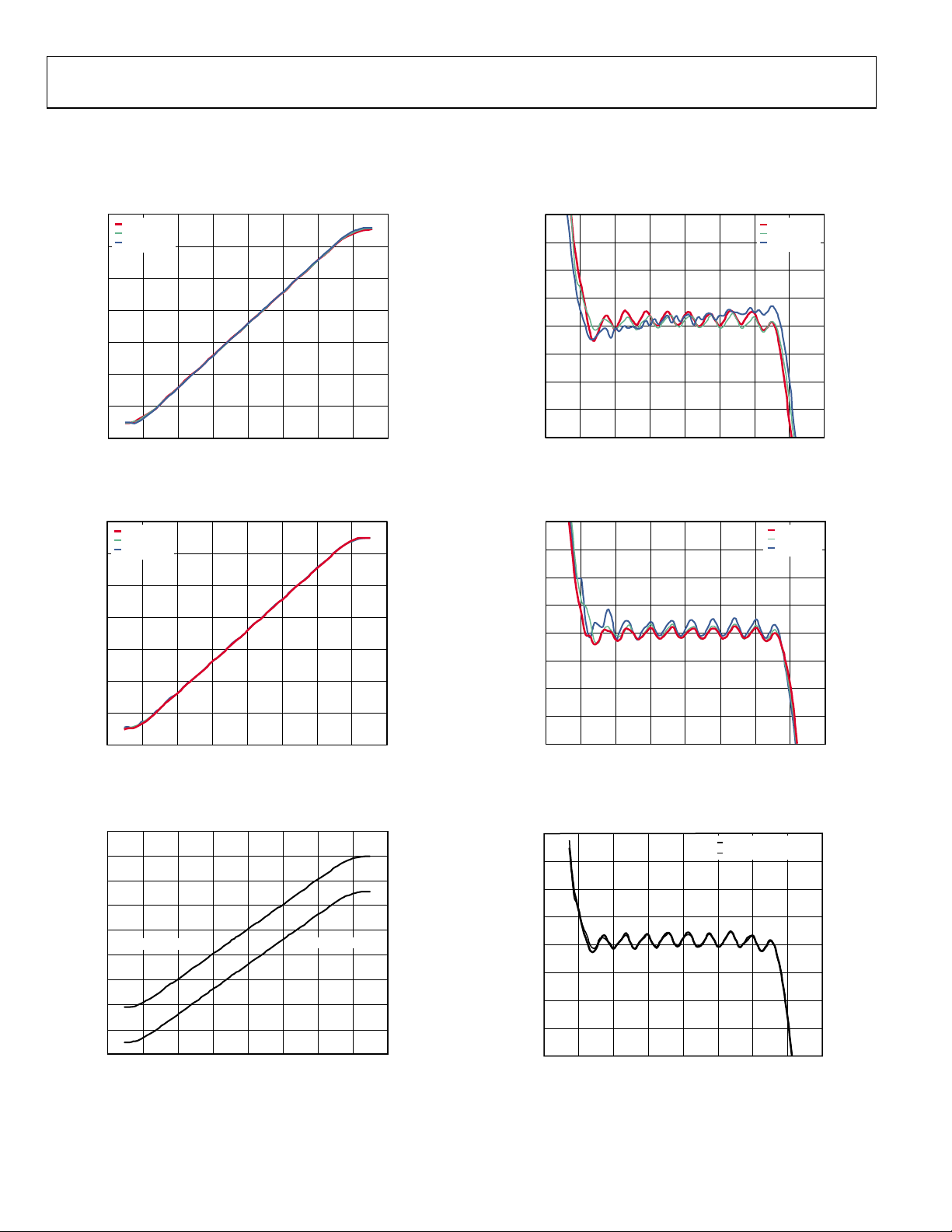

TYPICAL PERFORMANCE CHARACTERISTICS

VS = ±5 V, T = 25°C, gain range = −14 dB to +46 dB, PrA gain = +4×, f = 1 MHz, CL = 5 pF, RL = 500 Ω, PWRA = GND, unless otherwise

specified.

(dB)

–0.5

GAIN ERRO

–1.0

–1.5

2.0

1.5

1.0

0.5

T = +125°C

T = +25°C

T = –55°C

0

GAIN (dB)

–10

50

40

30

20

10

0

T = +125°C

T = +25°C

T = –55°C

–20

–600 –400 –200 200 400 600 800

–800

Figure 3. Gain vs. V

50

VS = ±12V

V

= ±5V

S

V

= ±3V

S

40

30

20

10

GAIN (dB)

0

–10

–20

–600 –400 –200 200 400 600 800

Figure 4. Gain vs. V

70

60

50

40

30

20

GAIN (dB)

10

0

–10

–20

–600 –400 –200 200 400 600 800

Figure 5 Gain vs. V

0

(mV)

V

GAIN

for Three Values of Temperature (T)

GAIN

0–800

V

(mV)

GAIN

for Three Values of Supply Voltage (VS)

GAIN

PREAMP GAIN = 4×PREAMP GAIN = 20×

0–800

V

(mV)

GAIN

for Preamp Gains of 4× and 20×

GAIN

–2.0

06228-003

–600 –400 –200 200 400 600 800

Figure 6. Gain Error vs. V

2.0

1.5

1.0

0.5

0

–0.5

GAIN ERROR (dB)

–1.0

–1.5

–2.0

6228-004

Figure 7. Gain Error vs. V

–0.5

GAIN ERROR (dB)

–1.0

–1.5

–2.0

6228-005

–600 –400 –200 200 400 600 800

GAIN

2.0

1.5

1.0

0.5

0

–600 –400 –200 200 400 600 800

Figure 8. Gain Error vs. V

0–800

V

(mV)

GAIN

for Three Values of Temperature (T)

GAIN

VS = ±12V

V

= ±5V

S

VS = ±3V

0–800

(mV)

V

GAIN

for Three Values of Supply Voltage (VS)

PREAMP GAIN = 20×

PREAMP GAIN = 4×

0–800

(mV)

V

GAIN

for Preamp Gains of 4× and 20×

GAIN

06228-006

06228-007

06228-008

Rev. 0 | Page 8 of 28

Page 9

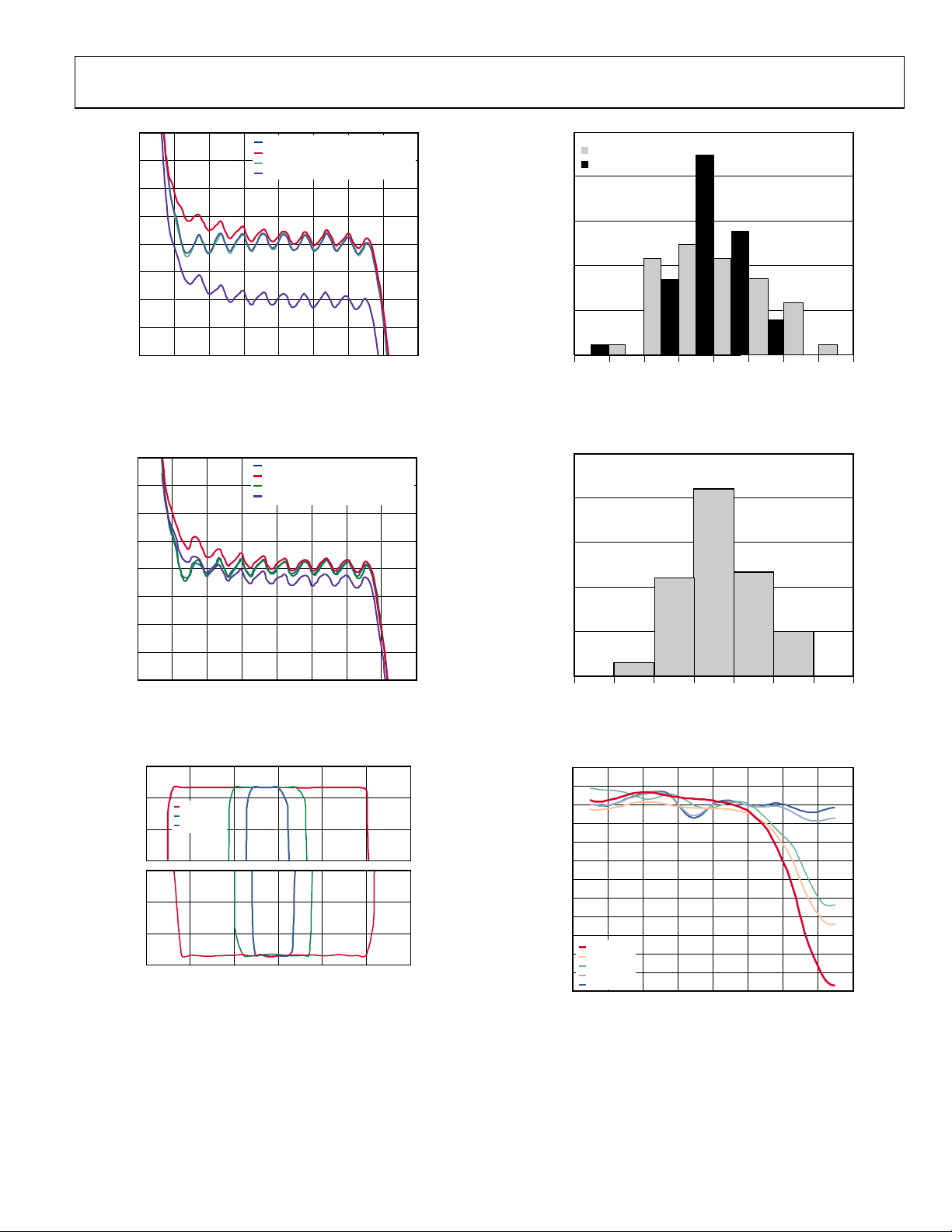

AD8336

2.0

1.5

1.0

PREAMP GAIN = 4×, f = 1MHz

PREAM P GAIN = 4×, f = 10MH z

PREAM P GAIN = 20×, f = 1MHz

PREAM P GAIN = 20×, f = 10MHz

50

40

60 UNITS

V

GAIN

V

GAIN

= –0.3V

= +0.3V

0.5

0

–0.5

GAIN ERROR (dB)

–1.0

–1.5

–2.0

–600 –400 –200 200 400 600 800

Figure 9. Gain Error vs. V

0–800

V

(mV)

GAIN

at 1 MHz and 10 MHz and

GAIN

for Preamp Gains of 4× and 20×

2.0

1.5

1.0

0.5

0

–0.5

GAIN ERROR (dB)

–1.0

–1.5

–2.0

–600 –400 –200 200 400 600 800

Figure 10. Gain Error vs. V

PREAMP GAIN = –3×, f = 1MHz

PREAMP GAIN = –3×, f = 10MHz

PREAMP GAIN = –19×, f = 1MHz

PREAMP GAIN = –19×, f = 10MHz

0–800

(mV)

V

GAIN

at 1 MHz and 10 MHz and

GAIN

for Inverting Preamp Gains of −3× and −19×

50

45

40

35

GAIN (dB)

–5

–10

–15

VS = ±12V

= ±5V

V

S

= ±3V

V

S

0

–15 –10 –5 0 5 10

COMMON-MODE VOLTAGE OF V

GAIN

30

20

% OF UNITS

10

0

–0.12

06228-009

–0.08

0

–0.04

GAIN ERROR (dB)

0.16

0.12

0.08

0.04

06228-012

Figure 12. Gain Error Histogram

50

60 U NITS

–0.3V ≤ V

40

30

20

% OF UNITS

10

0

6228-010

49.6 49.7 49.8 49.9 50.0 50.1 50.2

≤ 0.3V

GAIN

GAIN SCALING (dB/V)

06228-013

Figure 13. Gain Scaling Factor Histogram

20

0

–20

–40

–60

–80

–100

–120

–140

OFFSET VOLTAGE (mV)

–160

T = +125°C

–180

T = +85°C

T = +25°C

15

06228-011

–200

–220

T = –40°C

T = –55°C

V

GAIN

(V)

0.2000.60.4–0.8 –0.6 –0.2–0.4

.8

06228-014

Figure 11. Common-Mode Voltage at Pin V

GAIN

vs. V

GAIN

Rev. 0 | Page 9 of 28

Figure 14. Output Offset Voltage vs. V

Various Values of Temperature (T)

GAIN

for

Page 10

AD8336

%

–100

–120

–140

OFFSET VOLTAGE (mV)

–160

–180

–200

20

0

–20

–40

–60

–80

VS=±12V

V

=±5V

S

V

=±3V

S

–0.8

–0.6 –0.2–0.4 .8

V

GAIN

(V)

0.2000.60.4

06228-015

GAIN (dB)

–10

–20

–30

50

40

30

20

10

0

100k

V

= +0.7V

GAIN

+0.5V

+0.2V

0V

–0.2V

–0.5V

–0.7V

FREQUENCY (Hz)

200M1M 100M10M

06228-018

Figure 15. Output Offset Voltage vs. V

30

SAMPLE SIZE = 60 UNITS

V

= 0.7V

GAIN

20

10

0

30

% OF UNITS

20

10

0

50

40

30

OF UNITS

20

–200–240 –160 –120 –80 –40 0 40 80

= 0V

V

GAIN

–20–24 –16 –12 –8 –4 0 4 8

60 UNITS

Three Values of Supply Voltage (V

GAIN

OUTPUT OFFSET (mV)

OUTPUT OFFSET (mV)

Figure 16. Output Offset Histogram

for

)

S

Figure 18. Frequency Response for Various Values of V

50

40

30

20

10

GAIN (dB)

0

–10

V

= +0.7V

GAIN

+0.5V

+0.2V

0V

–0.2V

–0.5V

–0.7V

GAIN

–20

LOW POWER MODE

–30

100k

06228-016

Figure 19. Frequency Response for Various Values of V

FREQUENCY (Hz)

GAIN

200M1M 100M10M

06228-019

, Low Power Mode

70

V

= +0.7V

60

GAIN

+0.5V

50

40

30

GAIN (dB)

20

+0.2V

0V

–0.2V

10

10

0

0

INTERCEPT (dB)

16.45 16.5516.5016.4016.25 16.30 16.35

06228-017

Figure 17. Intercept Histogram

PREAMP GAIN = 20×

–10

100k

Figure 20. Frequency Response for Various Values of V

–0.5V

–0.7V

1M 200M100M10M

FREQUENCY (Hz)

GAIN

6228-020

when the Preamp Gain is 20×

Rev. 0 | Page 10 of 28

Page 11

AD8336

GAIN (dB )

–10

–20

–30

50

40

30

20

10

100k

V

= +0.7V

GAIN

+0.5V

+0.2V

0V

–0.2V

0

–0.5V

–0.7V

PREAMP GAIN = –3×

1M 200M100M10M

FREQUENCY (Hz)

06228-021

GAIN (dB)

–10

30

25

20

15

10

–5

5

0

100k

VS = ±12V

V

= ±5V

S

V

= ±3V

S

GAIN = 20×

GAIN = 4×

1M 500M100M10M

FREQUENCY (Hz)

6228-024

Figure 21. Frequency Response for Various Values of V

GAIN

for Preamp Gain of −3×

25

V

= 0V

GAIN

20

15

10

5

GAIN (dB)

0

C

=47pF

LOAD

=22pF

C

LOAD

–10

–5

100k

C

C

LOAD

LOAD

=10pF

= 0pF

1M 200M100M10M

FREQUENCY (Hz)

Figure 22. Frequency Response for Various Values of Load Capacitance (C

GAIN (dB)

–10

30

25

20

15

10

–5

5

0

100k

VS = ±12V

V

= ±5V

S

= ±3V

V

S

GAIN = 4×

1M 500M100M10M

FREQUENCY (Hz)

GAIN = 20×

6228-022

LOAD

06228-023

Figure 24. Preamp Frequency Response for Three Values of Supply Voltage (V

)

S

and Inverting Gain Values of −3× and −19×

20

PREAMP GAIN = 20×

PREAMP GAIN = 4×

15

10

GROUP DELAY (ns)

5

0

1M 100M10M

)

Figure 25. Group Delay vs. Frequency for Preamp Gains of 4× and 20×

1k

100

10

1

IMPEDANCE (Ω)

0.1

0.01

100k

FREQUENCY (Hz)

1M 500M100M10M

FREQUENCY (Hz)

6228-025

06228-026

Figure 23. Preamp Frequency Response for Three Values of Supply Voltage (V

and for Preamp Gains of 4× and 20×

Rev. 0 | Page 11 of 28

)

S

Figure 26. Output Resistance vs. Frequency of the Preamplifier

Page 12

AD8336

100

1k

PREAMP GA IN = 4×

10

f = 5MHz

1k

100

10

1

IMPEDANCE (Ω)

0.1

VS = ±12V

= ±5V

V

S

= ±3V

V

S

0.01

100k

1M 500M100M10M

FREQUENCY (Hz)

Figure 27. Output Resistance vs. Frequency of the VGA

for Three Values of Supply Voltage (V

1000

f= 5MHz

900

800

700

600

√Hz)

500

400

NOISE (nV/

300

200

100

0

–600 –200–400 400 600200 800

–800

Figure 28. Output Referred Noise vs. V

3000

f = 5MHz

PREAMP GAIN = 20×

2700

2400

2100

1800

√Hz)

1500

1200

NOISE (nV/

900

600

300

0

–600 –200–400 400 600200 800

V

GAIN

V

0

(mV)

at Various Temperatures (T)

GAIN

0–800

(mV)

GAIN

)

S

T = +125°C

T = +85°C

T = +25°C

T = –40°C

T = –55°C

T = +125°C

T = +85°C

T = +25°C

T = –40°C

T = –55°C

INPUT REFERRED NOISE (nV/√Hz)

1

–600 –200–400 400 600200 800

06228-027

Figure 30. Input Referred Noise vs. V

6

V

= 0.7V

GAIN

5

4

)

√Hz

3

NOISE (nV/

2

1

0

06228-028

100k

PREAM P GAIN = 20×

0–800

V

(mV)

GAIN

for Preamp Gains of 4× and 20×

GAIN

1M 100M10M

FREQUENCY (Hz)

V

S

V

S

V

S

= ±12V

= ±5V

= ±3V

6228-030

06228-031

Figure 31. Short-Circuit Input Referred Noise vs. Frequency at Maximum Gain

for Three Values of Power Supply Voltage (V

6

V

= 0.7V

GAIN

PREAMP GAIN = –3×

5

4

√Hz)

3

NOISE (nV/

2

1

0

100k

06228-029

1M 100M10M

FREQUENCY (Hz)

)n

S

06228-032

Figure 29. Output Referred Noise vs. V

when the Preamp Gain is 20×

at Various Temperatures (T)

GAIN

Figure 32. Short-Circuit Input Referred Noise vs. Frequency

at Maximum Inverting Gain

Rev. 0 | Page 12 of 28

Page 13

AD8336

√

–

–

–

–

100

V

= 0.7V

GAIN

Hz)

10

INPUT REFERRED NOISE

THERMAL NOISE ALONE

1

INPUT NOISE (nV/

0.1

R

S

100 1k

SOURCE RESISTANCE (Ω)

Figure 33. Input Referred Noise vs. Source Resistance

70

60

50

40

30

NOISE FI GURE (dB)

20

10

0

–800 –600 –200–400 400 600200 800

V

GAIN

SIMULATED

DATA

0

(mV)

f = 10MHz

50Ω SOURCE

UNTERMINATED

40

V

= 2V p-p

OUT

= 0V

V

GAIN

f = 5MHz

–45

–50

–55

–60

DISTORTION (dBc)

–65

10k10

06228-033

–70

0

5410 3515 3020

HD2

HD3

LOAD CAPACITANCE (pF)

25

45 50

0

06228-036

Figure 36. Harmonic Distortion vs. Load Capacitance

20

V

= 1V p-p

OUT

–30

–40

–50

–60

DISTORTION (dBc)

HD2 @ 1MHz

–70

HD2 @ 10MHz

HD3 @ 1MHz

HD3 @ 10MHz

–80

6228-034

–600 800–400 600–200 2000

OUTPUT SWING OF PREAMP

LIMITS V

(mV)

V

GAIN

GAIN

400

TO 400mV

06228-037

nd

and 3rd Harmonic Distortion vs. V

20

HD2

f = 5MHz

–30

–40

–50

–60

DISTORTION (dBc)

= 0.5V p-p

V

–70

OUT

V

= 1V p-p

OUT

V

= 2V p-p

OUT

V

= 4V p-p

OUT

–80

–600 800–400 600–200 2000

Figure 38. 2

for Four Values of Output Voltage (V

at 1 MHz and 10 MHz

GAIN

OUTPUT SWING OF PREAMP LIMITS

V

LEVELS

GAIN

V

(mV)

GAIN

nd

Harmonic Distortion vs. V

400

OUT

GAIN

06228-038

)

40

V

V

f = 5MHz

–45

–50

–55

–60

DISTORTION (dBc)

–65

–70

0

Figure 34. Noise Figure vs. V

= 2V p-p

OUT

= 0V

GAIN

200 1.6k400 1.4k600 1.2k800

HD2

HD3

1.0k

LOAD RESISTANCE (Ω)

GAIN

1.8k 2.0k 2.2k

6228-035

Figure 37. 2

Figure 35. Harmonic Distortion vs. Load Resistance

Rev. 0 | Page 13 of 28

Page 14

AD8336

–

–

–30

–40

–50

20

HD3

f = 5MHz

OUTPUT SWING OF PREAMP LIMITS

MINIMUM USABLE V

GAIN

LEVELS

40

35

30

25

20

1MHz 500mV

1MHz 1V

10MHz 500mV

10MHz 1V

–60

DISTORTION (dBc)

V

= 0.5V p-p

OUT

–70

–80

–600 800–400 600–200 2000

V

V

V

OUT

OUT

OUT

= 1V p-p

= 2V p-p

= 4V p-p

Figure 39. 3

for Four Values of Output Voltage (V

20

V

= 2V p-p

OUT

= 0V

V

GAIN

–30

–40

HD (dBc)

–50

–60

–70

1M

(mV)

V

GAIN

rd

Harmonic Distortion vs. V

FREQUENCY (Hz)

400

HD2

HD3

10M

OUT

GAIN

15

OUTPUT IP3 (dBm)

10

V

= 1V p-p

5

OUT

V

= 0V

GAIN

COMPOSIT E INPUTS SEPARATED BY 100kHz

0

–800

–600 800–400 600–200 4000

06228-039

)

IP1dB (dBm)

–10

–20

50M

06228-040

–30

Figure 42. Output Referred IP3 (OIP3) vs. V

at Two Frequencies and Two Input Levels

30

20

10

0

VS = ±12V

VS = ±5V

VS = ±3V

–600 800–400 600–200 4000

V

V

200

(mV)

GAIN

INPUT LEVEL LIMITED

BY GAIN OF PREAMP

200–800

(mV)

GAIN

GAIN

06228-042

06228-043

Figure 40. Harmonic Distortion vs. Frequency

0

V

= 1V p-p

OUT

V

= 0V

GAIN

–10

TONES SEPARATED BY 100kHz

–20

–30

–40

–50

IMD3 (dBc)

–60

–70

–80

–90

1M

Figure 41. IMD3 vs. Frequency

10M

FREQUENCY (Hz)

100M

06228-041

Rev. 0 | Page 14 of 28

Figure 43. Input P1dB (IP1dB) vs. V

3

2

1

0

VO LTAGE (V)

–1

–2

–3

at Three Power Supply Values (VS)

GAIN

VIN (V)

V

(V)

OUT

100 2000

TIME (ns)

Figure 44. Large Signal Pulse Response of the Preamp

300–100

6228-044

Page 15

AD8336

0.6

V

= 0.7V

GAIN

0.4

0.2

0

(mV)

IN

V

–0.2

–0.4

–0.6

–100

–50 150100 25050 300200 350

INPUT

OUTPUT WHEN PWRA = 0

OUTPUT WHEN PWRA = 1

0

TIME (ns)

60

40

20

0

–20

–40

–60

(mV)

OUT

V

06228-045

25

20

15

10

5

0

(mV)

IN

V

–5

–10

–15

–20

–25

0–100

–50 150100 25050 300200 350

OUTPUT

V

= 0.7V

GAIN

PREAMP GAIN = –3

INPUT

TIME (ns)

2.5

2.0

1.5

1.0

0.5

0

–0.5

–1.0

–1.5

–2.0

–2.5

(mV)

OUT

V

06228-048

Figure 45. Noninverting Small Signal Pulse Response for Both Power Levels

0.6

0.4

0.2

0

(mV)

IN

V

–0.2

–0.4

–0.6

–50 150100 25050 300200 350

–100

0

OUTPUT

V

= 0.7V

GAIN

PREAMP GAIN = –3

INPUT

TIME (ns)

60

40

20

0

–20

–40

–60

(mV)

OUT

V

Figure 46. Inverting Gain Small Signal Pulse Response

25

= 0.7V

V

GAIN

20

15

10

5

0

(mV)

IN

V

–5 –0.5

–10

–15

–20

–50 150100 25050 300200 350

INPUT

OUTPUT WHEN PWRA = 0

OUTPUT WHEN PWRA = 1

0–100

TIME (ns)

2.5

2.0

1.5

1.0

0.5

0

–1.0

–1.5

–2.0

–2.5–25

(mV)

OUT

V

Figure 48. Inverting Gain Large Signal Pulse Response

20

V

= 0.7V

GAIN

= ±3V

V

S

15

10

5

0

(mV)

IN

V

–5 –0.5

–10

–15

–20

–100

–50 20015010050 300250

06228-046

0

INPUT

= 0pF

C

L

= 10pF

C

L

= 22pF

C

L

= 47pF

C

L

TIME (ns)

350

400

2.0

1.5

1.0

0.5

0

–1.0

–1.5

–2.0

(V)

OUT

V

06228-049

Figure 49. Large Signal Pulse Response for Various Values of Load

Capacitance Using ±3V Power Supplies

30

V

= 0.7V

GAIN

= ±5V

V

S

20

10

0

(mV)

IN

V

–10

–20

*WITH 20Ω RESISTOR IN SERIES WITH OUTPUT.

–30

06228-047

0–100

–50 150100 25050 300200 350

INPUT

= 0pF

C

L

C

= 10pF

L

= 22pF

C

L

= 47pF*

C

L

TIME (ns)

3

2

1

(mV)

0

OUT

V

–1

–2

–3

6228-050

Figure 47. Large Signal Pulse Response for Both Power Levels

Figure 50. Large Signal Pulse Response for Various Values of Load

Capacitance Using ±5V Power Supplies

Rev. 0 | Page 15 of 28

Page 16

AD8336

30

V

= 0.7V

GAIN

V

= ±12V

S

20

10

0

(mV)

IN

V

–10

–20

*WITH 20Ω RESISTOR IN SERIES WITH OUTPUT

–30

0–100

–50 150100 25050 300200 350

INPUT

C

= 0pF

L

= 10pF*

C

L

= 22pF*

C

L

= 47pF*

C

L

TIME (ns)

3

2

1

(mV)

0

OUT

V

–1

–2

–3

06228-051

10

PSRR

V

V

POS

NEG

V

= 0.7V

0

–10

–20

–30

PSRR (dB)

–40

–50

–60

100k

V

V

GAIN

GAIN

GAIN

= 0V

= –0.7V

FREQUENCY (Hz)

1M 5M

6228-054

Figure 51. Large Signal Pulse Response for Various Values of Load

Capacitance Using ±12V Power Supplies

2.5

1.5

0.5

V

OUT

(V)

V

–0.5

GAIN

–1.5

–2.5

–0.5 0.5

01.51.0

TIME (µs)

2.0

Figure 52. Gain Response

0.5

V

= 0.7V

GAIN

0.4

0.3

0.2

0.1

0

–0.1

INPUT VOLTAGE (V)

–0.2

–0.3

VIN (V)

–0.4

–0.5

(V)

V

OUT

–6–9

–3 306

TIME (µs)

Figure 54 PSRR vs. Frequency for Three Values of V

40

HIGH POWER

30

LOW POWER

10

QUIESCENT SUPPLY CURRENT (mA)

06228-052

Figure 55. I

VS = ±12V

= ±5V

V

S

= ±3V

V

S

0

–45 15–5 25 452055

–65

–25

TEMPERATURE (°C)

vs. Temperature for Three Values of Supply Voltage

Q

GAIN

75 95 125

6228-055

and High and Low Power

5

4

3

2

1

0

–1

–2

OUTPUT VOLTAGE (V)

–3

–4

–5

6228-053

Figure 53. VGA Overdrive Recovery

Rev. 0 | Page 16 of 28

Page 17

AD8336

R

TEST CIRCUITS

NETWORK ANALYZE

NETWORK ANALYZER

4

+

PrA

5

100Ω

–

49.9Ω

Figure 56. Gain vs. V

NETWORK ANALYZ ER

4

+

5

100Ω

PrA

–

301Ω

49.9Ω

Figure 57. Frequency Response

NETWORK ANALYZER

301Ω

50Ω

AD8336

GAIN

50Ω

AD8336

50Ω

9

50Ω

8

50Ω

INOUT

50Ω

453Ω

1

118

12

V

GAIN

and Gain Error vs. V

INOUT

453Ω

1

115

12

INOUT

V

OPTIONAL

GAIN

C

GAIN

LOAD

INOUT

50Ω

50Ω

AD8336

4

+

5

100Ω

–

301Ω

PrA

118

12

9

49.9Ω

06228-056

453Ω

1

06228-059

Figure 59. Group Delay

AD8336

4

+

PrA

–

5

118

12

301Ω

100Ω

06228-057

9

453Ω 50Ω

1

DMM

+

¯

06228-060

Figure 60. Offset Voltage

NETWORK ANALYZER

50Ω

CONFIGURE TO

MEASURE

Z-CONVERTED S22

IN

NC = NO CONNECT

AD8336

4

49.9Ω

5

100Ω

+

PrA

–

301Ω

12

9

1

118

NC

Figure 58. Frequency Response of the Preamp

453Ω

453Ω

NC

06228-058

Rev. 0 | Page 17 of 28

+

PrA

–

301Ω

AD8336

9

12

NC

4

49.9Ω

5

100Ω

NC = NO CONNECT

Figure 61. Output Resistance vs. Frequency

NC

0Ω

0Ω

1

118

06228-061

Page 18

AD8336

R

R

R

4

Ω

CH1

AD8336

8

9

OSCILLOSCOPE

50Ω

50Ω

12

11

0.7V

OSCILLOSCOPE

CH1

50Ω

11

CH2

OPTIONAL

20Ω 453Ω

1

CH2

50Ω

DIFFERENTIAL

FET PROBE

453Ω

1

NC

06228-065

SPECTRUM ANALYZE

IN

50Ω

AD8336

4

+

PrA

–

5

12

9

1

118

301Ω

V

100Ω

GAIN

06228-062

Figure 62. Input Referred Noise and Output Referred Noise

NOISE FIGURE METE

NOISE

NOISE

SOURCE

SOURCE

DRIVE

INPUT

0Ω

AD8336

4

49.9Ω

(OR ∞)

+

PrA

–

5

0Ω

1

1

GENERATOR

9.9

FUNCTION

GENERATOR

SINE

WAVE

PULSE

OUT

PULSE

GENERATOR

SQUARE

WAVE

49.9Ω

POWER

SPLITTER

4

+

PrA

–

5

301Ω

100Ω

Figure 65. Pulse Response

POWER

SPLITTER

AD8336

4

+

PrA

–

5

100Ω

SIGNAL

GENERATOR

LOW-PASS

FILTER

49.9Ω

118

12

301Ω

9

V

GAIN

Figure 63. Noise Figure vs. V

SPECTRUM ANALYZE

INPUT

50Ω

AD8336

4

+

PrA

–

5

118

12

9

301Ω

100Ω

Figure 64. Harmonic Distortion

GAIN

V

GAIN

8

12

9

301Ω

100Ω

06228-063

NC = NO CONNECT

06228-066

Figure 66. Gain Response

OSCILLOSCOPE

CH1

50Ω

CH2

50Ω

R

LOAD

ARBITRARY

WAVEFORM

GENERATOR

–20dB

POWER

SPLITTER

AD8336

4

+

1

C

LOAD

49.9Ω

PrA

–

5

118

12

9

301Ω

100Ω

06228-064

NC = NO CONNECT

0.7V

453Ω

1

NC

06228-067

Figure 67. VGA Overdrive Recovery

Rev. 0 | Page 18 of 28

Page 19

AD8336

R

POWER SUPPLIES

CONNECTED TO

NETWORK ANALYZER

AD8336

4

+

PrA

–

5

9

301Ω

100Ω

Figure 68. Supply Current

DMM

(+I)

13

1

118

12

10

DMM

(–I)

06228-068

BY

CAPACITORS

REMOVED FOR

MEASUREMENT

POWER SUPPLY

PASS

49.9Ω

BENCH

4

5

+

–

100Ω

Figure 71. Power Supply Rejection Ratio

BIAS PORT

VPOS OR VNEG

PrA

8

301Ω

NETWORK ANALYZER

50Ω

50Ω

AD8336

1

9

11

12

V

GAIN

INOUT

DIFFERENTIAL

FET PROBE

06228-071

NETWORK ANALYZER

50Ω

AD8336

4

+

PrA

–

5

100Ω

100Ω

49.9Ω

301Ω

Figure 69. Frequency Response, Inverting Gain

PULSE

GENERATOR

OUT

POWER

SPLITTER

CH1

AD8336

4

+

PrA

–

5

8

301Ω

9

100Ω

100Ω

49.9Ω

Figure 70. Pulse Response, Inverting Gain

INOUT

50Ω

118

12

9

V

OSCILLOSCOPE

50Ω

50Ω

1

11

12

0.7V

1

GAIN

CH2

453Ω

453Ω

SPECTRUM ANALYZE

IN

50Ω

AD8336

4

+

PrA

–

5

8

12

301Ω

9

100Ω

06228-069

1

11

0.7V

06228-072

Figure 72. Input Referred Noise vs. Source Resistance

SPECTRUM ANALYZER

IN

50Ω

AD8336

4

+

PrA

–

5

12

301Ω

06228-070

100Ω

9

1

118

0.7V

06228-073

Figure 73. Short-Circuit Input Noise vs. Frequency

Rev. 0 | Page 19 of 28

Page 20

AD8336

SPECTRUM

ANALYZER

SIGNAL

GENERATOR

OUT

50Ω

22dB

50Ω

IN

OPTIONAL 20dB

ATTENUATOR

AD8336

453Ω

1

118

V

GAIN

06228-074

GAIN

49.9Ω

4

5

100Ω

+

PrA

–

301Ω

Figure 74. IP1dB vs. V

9

12

SPECTRUM

ANALYZER

SIGNAL

GENERATOR

OUT

50Ω

IN

50Ω

–20dB

49.9Ω

AD8336 AMPLIFIER

4

+

PrA

–

5

301Ω

100Ω

1

118

12

9

0.7V

Figure 75. IP1dB vs. V

0Ω

100Ω

, High Signal Level Inputs

GAIN

4

5

AD8336 DUT

+

PrA

–

301Ω

453Ω

1

118

12

9

V

GAIN

06228-075

SPECTRUM ANALYZER

INPUT

50Ω

SIGNAL

GENERATOR

SIGNAL

GENERATOR

+22dB –6dB

+22dB

–6dB

COMBINER

–6dB

49.9Ω

4

5

100Ω

AD8336 DUT

+

PrA

–

301Ω

453Ω

1

9

118

12

V

GAIN

6228-076

Figure 76. IMD and OIP3

Rev. 0 | Page 20 of 28

Page 21

AD8336

*

THEORY OF OPERATION

OVERVIEW

The AD8336 is the first VGA designed for operation over

exceptionally broad ranges of temperature and supply voltage.

Its performance has been characterized from temperatures

extending from −55°C to 125°C, and supply voltages from ±3 V

to ±12 V. It is ideal for applications requiring dc coupling, large

output voltage swings, very large gain ranges, extreme

temperature variations, or a combination thereof.

The simplified block diagram is shown in Figure 77. The

AD8336 includes a voltage feedback preamplifier, an amplifier

with a fixed gain of 34 dB, a 60 dB attenuator, and various bias

and interface circuitry. The independent voltage feedback op

amp can be used in noninverting and inverting configurations,

and functions as a preamplifier to the variable gain amplifier

(VGA). If desired, the op amp output (PRAO) and VGA input

(VGAI) pins provide for connection of an interstage filter to

eliminate noise and offset. The bandwidth of the AD8336 is dc

to 100 MHz with a gain range of 60 dB (−14 dB to +46 dB.)

For applications that require large supply voltages, a reduction

in power is advantageous. The power reduction pin (PWRA)

permits the power and bandwidth to be reduced by about half

in such applications.

R

*

FB2

301Ω

INPP

INPN

R

FB1

100Ω

OPTIONAL DEPEAKING CAPACITOR. SEE TEXT.

PWRA

To maintain low noise, the output stages of both the preamplifier

and the VGA are capable of driving relatively small load

resistances. However, at the largest supply voltages, the signal

current may exceed safe operating limits for the amplifiers and

the load current must not exceed 50 mA. With a ±12 V supply

and ±10 V output voltage at the preamplifier or VGA output,

load resistances as low as 200 Ω are acceptable.

For power supply voltages ≥ ±10 V, the maximum operating

temperature range is derated to +85°C, as the power may exceed

safe limits (see the Absolute Maximum Ratings section).

Since harmonic distortion products may increase for various

combinations of low impedance loads and high output voltage

swings, it is recommended that the user determine load and

drive conditions empirically.

PRAO

VGAI

VNEG

–60dB TO 0dB

ATTENUATOR

AND

GAIN CONTROL

INTERFACE

GNEG VCOMVPOS GPOS

+

PrA

–

BIAS

Figure 77. Simplified Block Diagram

34dB12dB

+

_

VOUT

4.48kΩ

91.43Ω

06228-077

PREAMPLIFIER

The gain of the uncommitted voltage feedback preamplifier is

set with external resistors. The combined preamplifier and VGA

gain is specified in two ranges, between −14 dB to +46 dB and

0 dB to 60 dB. Since the VGA gain is fixed at 34 dB (50×), the

preamp gain is adjusted for gains of 12 dB (4×) and 26 dB (200×).

With low preamplifier gains between 2× and 4×, it may be

desirable to reduce the high frequency gain with a shunt

capacitor across R

, to ameliorate peaking in the frequency

FB2

domain (see Figure 77). To maintain stability, the gain of the

preamplifier must be 6 dB (2×) or greater.

Typical of voltage feedback amplifier configurations, the gainbandwidth product of the AD8336 is fixed (at 400); thus, the

bandwidth decreases as the gain is increased beyond the nominal

gain value of 4×. For example, if the preamp gain is increased to

20×, the bandwidth reduces by a factor-of-five to about 20 MHz.

The −3 dB bandwidth of the preamplifier with a gain of 4× is

about 150 MHz, and for the 20× gain is about 30 MHz.

The preamp gain diminishes for an amplifier configured for

inverting gain, using the same value of feedback resistors as for

a noninverting amplifier, but the bandwidth remains unchanged.

For example, if the noninverting gain is 4×, the inverting gain is

−3×, but the bandwidth stays the same as in the noninverting

gain of 4×. However, because the output referred noise of the

preamplifier is the same in both cases, the input referred noise

increases as the ratio of the two gain values. For the previous

example, the input referred noise will increase by a factor of 4/3.

VGA

The architecture of the variable gain amplifier (VGA) section

of the AD8336 is based on the Analog Devices, Inc., X-AMP

(exponential amplifier), found in a wide variety of Analog

Devices variable gain amplifiers. This type of VGA combines a

ladder attenuator and interpolator, followed by a fixed-gain

amplifier.

The gain control interface is fully differential, permitting positive

or negative gain slopes. Note that the common-mode voltage of

the gain control inputs increases with increasing supply.

The gain slope is 50 dB/V and the intercept is 16.4 dB when the

nominal preamp gain is 4× (12 dB). The intercept changes with

the preamp gain; for example, when the preamp gain is set to

20× (26 dB) the intercept becomes 30.4 dB.

Pin VGAI is connected to the input of the ladder attenuator.

The ladder ratio is R/2R and the nominal resistance is 320 Ω. To

reduce preamp loading and large-signal dissipation, the input

resistance at Pin VGAI is 1.28 kΩ. Safe current density and

power dissipation levels are maintained even when large dc

signals are applied to the ladder.

The tap resistance of the resistors within the R/2R ladder is

640 Ω/3 or 213.3 Ω, the Johnson noise source of the attenuator.

Rev. 0 | Page 21 of 28

Page 22

AD8336

SETTING THE GAIN NOISE

The overall gain of the AD8336 is the sum (in dB) or the

product (magnitude) of the preamp gain and the VGA gain.

The preamp gain is calculated as with any op amp, as seen in

the Applications section. It is most convenient to think of the

device gain in exponential terms (that is, in dB) since the VGA

responds linearly-in-dB with changes in control voltage V

GAIN

at

the gain pins.

The gain equation for the VGA is

⎤

dB50

V

dB4.4

⎥

⎦

where

⎡

(V)(dB) +

VGainVGA

⎢

⎣

V

= V

GPOS

− V

GNEG

G

×=

AING

The gain and gain range of the VGA are both fixed at 34 dB and

60 dB, respectively; thus, the composite device gain is changed

by adjusting the preamp gain. For a preamp gain of 12 dB (4×),

the composite gain is −14 dB to +46 dB. Thus, the calculation

for the composite gain (in dB) is

VGGainComposite

GPRA

dB4.4/V]Bd9.49(V)[ +×+=

For example, the midpoint gain when the preamp gain is 12 dB is

dB4.16dB4.4/V]Bd9.49V0[dB12 =+×+

Figure 3 is a plot of gain in dB vs. V

in mV, when the

GAIN

preamp gain is 12 dB (4×). Note that the computed result

closely matches the plot of actual gain.

In Figure 3, the gain slope flattens at the limits of the V

input.

G

The gain response is linear-in-dB over the center 80% of the

control range of the device. Figure 78 shows the ideal gain

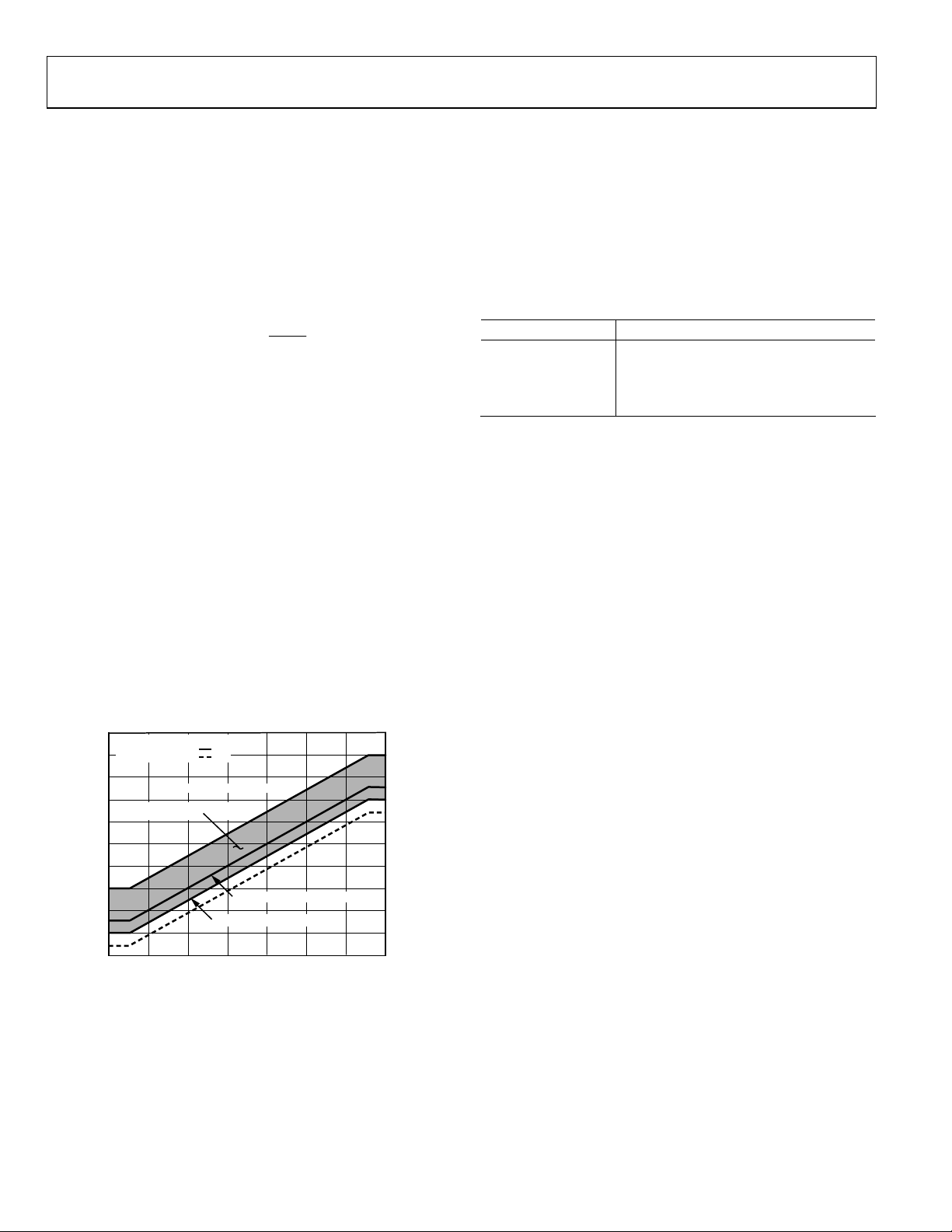

characteristics for the VGA stage and composite VGA + preamp.

70

GAIN CHARACTERISTICS

COMPOSITE GAIN

60

VGA STAGE GAIN

50

40

USABLE GAIN RANGE OF

AD

8336

30

20

GAIN (dB)

10

0

–10

–20

–30

Figure 78. Ideal Gain Characteristics of the AD8336

FOR PREAMP GAIN = 26dB

FOR PREAMP G AIN = 12dB

FOR PREAMP GAIN = 6dB

VG (V)

0.5 0.70.30.1–0.1–0.3–0.5–0.7

06228-078

The noise of the AD8336 is dependent on the value of the VGA

gain. At maximum V

preamp but shifts to the VGA as V

, the dominant noise source is the

GAIN

diminishes.

GAIN

The input referred noise at the highest VGA gain and a preamp

gain of 4×, with R

=100 Ω and R

FB1

= 301 Ω, is 3 nV/√Hz, and

FB2

determined by the preamp and its gain setting resistors. See

Table 4 for the noise components for the preamp.

Table 4. AD8336 Noise Components for Preamp Gain = 4×

Noise Component Noise Voltage (nV/√Hz)

Op Amp (Gain = 4×) 2.6

R

= 100 Ω 0.96

FB1

R

= 301 Ω 0.55

FB2

VGA 0.77

Using the listed values, the total noise of the AD8336 is slightly

less than 3 nV/√Hz, referred to the input. Although the output

noise VGA is 3.1 nV/√Hz, the input referred noise is 0.77 nV/√Hz

when divided by the preamplifier gain of 4×

At other than maximum gain, the noise of the VGA is determined

from the output noise. The noise in the center of the gain range

is about 150 nV/√Hz. Since the gain of the fixed gain amplifier

that is part of the VGA is 50×, the VGA input referred noise is

approximately 3 nV/√Hz, the same value as the preamp and

VGA combined. This is expected since the input referred noise

is the same at the input of the attenuator at maximum gain.

However, the noise referred to the VGAI pin (the preamp

output) increases by the amount of attenuation through the

ladder network. The noise at any point along the ladder

network is primarily comprised of the ladder resistance noise,

the noise of the input devices, and the feedback resistor network

noise. The ladder network and the input devices are the largest

noise sources.

At minimum gain, the output noise increases slightly to about

180 nV/√Hz because of the finite structure of the X-AMP.

OFFSET VOLTAGE

Extensive cancellation circuitry included in the variable gain

amplifier section minimizes locally generated offset voltages.

However when operated at very large values of gain, dc voltage

errors at the output can still result from small dc input voltages.

When configured for the nominal gain range of −14 dB to 46 dB,

the maximum gain is 200× and an offset of only 100 μV at the

input generates 20 mV at the output.

The primary source for dc offset errors is the preamplifier;

ac coupling between the PRAO and VGAI pins is the simplest

solution. In applications where dc coupling is essential, a

compensating current can be injected at the INPN input (Pin 5)

to cancel preamp offset. The direction of the compensating

current depends on the polarity of the offset voltage.

Rev. 0 | Page 22 of 28

Page 23

AD8336

V

O

APPLICATIONS

AMPLIFIER CONFIGURATION

The AD8336 amplifiers can be configured in various options.

In addition to the 60 dB gain range variable gain stage, an

uncommitted voltage gain amplifier is available to the user as a

preamplifier. The preamplifier connections are separate to

enable noninverting or inverting gain configurations or the use

of interstage filtering. The AD8336 can be used as a cascade

connected VGA with preamp input, as a standalone VGA, or as

a standalone preamplifier. This section describes some of the

possible applications.

GAI

PRA

9

8

INPP

4

INPN

PWRA

+

PrA

–

5

2

AD8336

BIAS

10

VNEG

Figure 79. Application Block Diagram

13

ATTENUATOR

–60dB TO 0dB

3

VCOMVPOS

34dB

GAIN CONTROL

INTERFACE

11

GPOS

12

GNEG

VOUT

1

PREAMPLIFIER

While observing just a few constraints, the uncommitted

voltage feedback preamplifier of the AD8336 can be connected

in a variety of standard high frequency op amp configurations.

The amplifier is optimized for a gain of 4×, (12 dB) and has a

gain bandwidth product of 600 MHz. At a gain of 4×, the

bandwidth is 150 MHz. The preamplifier gain can be adjusted

to a minimum gain of 2×; however, there will be a small peak in

the response at high frequencies. At higher preamplifier gains,

the bandwidth diminishes proportionally in conformance to the

classical voltage gain amplifier GBW relationship.

While setting the overall gain of the AD8336, the user needs to

consider the input referred offset voltage of the preamplifier.

Although the offset of the attenuator and postamplifier are

almost negligible, the preamplifier offset voltage, if uncorrected,

is increased by the combined gain of the preamplifier and

postamplifier. Thus for a maximum gain of 60 dB, an input offset

voltage of only 200 μV results in an error of 200 mV at the output.

06228-079

Circuit Configuration for Noninverting Gain

The noninverting configuration is shown in Figure 80. The

preamp gain is described by the classical op amp gain equation

R

2

FB

1

Gain

+=

R

1

FB

The practical gain limits for this amplifier are 6 dB to 26 dB.

The gain bandwidth product is about 600 MHz, so that at 150

MHz, the maximum achievable gain is 12 dB (4×). The minimum

gain is established internally by fixed loop compensation, and is

6 dB (2×). This amplifier is not designed for unity gain operation.

Table 5 shows the gain bandwidth for the noninverting gain

configuration.

CIRCUIT CONFIGURATION FOR NONINVERTING GAIN

4

5

PRAO

8

AD8336

PREAMPLIFIER

–60dB TO 0dB

PWRA

VGAI

9

VCOM

10

2 3

–5V

34dB

1

VOUT

VPOSVNEG

13

+5V

R

R

FB1

100Ω

301Ω

GAIN = 12dB

INPP

INPN

FB2

Figure 80. Circuit Configuration for Noninverting Gain

The preamplifier output reliably sources and sinks currents up

to 50 mA. When using ±5 V power supplies, the suggested sum

of the output resistor values is 400 Ω total for the optimal tradeoff between distortion and noise. Much of the low gain value

device characterization was performed with resistor values of

301 Ω and 100 Ω, resulting in a preamplifier gain of 12 dB (4×).

With supply voltages between ±5 V and ±12 V, the sum of the

output resistance should be increased accordingly and a total

resistance of 1 kΩ is recommended. Larger resistance values,

subject to a trade-off in higher noise performance, can be used

if circuit power and load driving is an issue. When considering

the total power dissipation, remember that the input ladder

resistance of the VGA is part of the preamp load.

Table 5. Gain vs. Bandwidth for Noninverting Preamplifier

Configuration.

Preamp Gain

Numerical dB

Preamp BW

(MHz)

Composite

Gain (dB)

4× 12 150 −14 to +46

8× 18 60 −8 to +52

16× 24 30 −2 to +58

20× 26 25 0 to 60

06228-080

Rev. 0 | Page 23 of 28

Page 24

AD8336

Circuit Configuration for Inverting Gain

The preamplifier can also be used in an inverting configuration,

as shown in Figure 81.

CIRCUIT CONFIGURATION FOR INVERTING GAIN

AD8336

PREAMPLIFIER

INPP

4

GAIN = 9.6dB INPN

R

R

FB1

FB2

100Ω

301Ω

+

–

5

PRAO

8

–60dB TO 0dB

PWRA

9

2 3

–5V

34dB

VCOM

10

1

VOUT

VPOSVNEG

13

+5V

Figure 81. Circuit Configuration for Inverting Gain

The same considerations regarding total resistance vs. distortion,

noise, and power as noted in the noninverting case apply, except

that the amplifier can be operated at unity inverting gain. The

signal gain is reduced while the noise gain is the same as for the

noninverting configuration:

R

FB

GainSignal =

R

12FB

and

R

2

FB

GainNoise

R

1

+=

1

FB

06228-081

USING THE POWER ADJUST FEATURE

The AD8336 has the provision to operate at lower power with

a trade-off in bandwidth. The power reduction applies to the

preamp and the VGA sections, and the bandwidth is reduced

equally between them. Reducing the power is particularly useful

when operating with higher supply voltages and lower values of

output loading that would otherwise stress the output amplifiers.

When Pin PWRA is grounded, the amplifiers operate in their

default mode, and the combined 3 dB bandwidth is 80 MHz

with the preamp gain adjusted to 4×. When the voltage on

Pin PWRA is between 1.2 V and 5 V, the power is reduced by

approximately half and the 3 dB bandwidth reduces to

approximately 35 MHz. The voltage at pin PWRA must not

exceed 5 V.

DRIVING CAPACITIVE LOADS

The output stages of the AD8336 are stable with capacitive loads

up to 47 pF for a supply voltage of ±3 V, and capacitive loads up

to 10 pF for supply voltages up to ±8 V. For larger combined

values of load capacitance and/or supply voltage, a 20 Ω series

resistor is recommended for stability.

The influence of capacitance and supply voltage are shown in,

Figure 50 and Figure 51, where representative combinations of

load capacitance and supply voltage requiring a 20 Ω resistor

are marked with an asterisk. No resistor is required for the ±3 V

plots in Figure 49, while a resistor is required for most of the

±12 V plots in Figure 51.

Rev. 0 | Page 24 of 28

Page 25

AD8336

EVALUATION BOARD

An evaluation board, AD8336-EVALZ, is available online for

the AD8336. Figure 82 is a photo of the board.

The board is shipped from the factory, configured for a preamp

gain of 4×. To change the value of the gain of the preamp or the

gain polarity to inverting is a matter of changing component

values, or installing components in alternate locations provided.

All components are standard 0603 size, and the board is designed

for RoHS compliancy. Figure 83 shows the locations of

components provided for changing the amplifier configuration

to inverting gain. Simply install the components shown in red

and remove those in gray.

OPTIONAL CIRCUITRY

The AD8336 features differential inputs for the gain control,

permitting nonzero or floating gain control inputs. In order to

avoid any delay in making the board operational, the gain input

circuit is shipped with Pin GNEG connected to ground via a

0 Ω resistor in location R17. The user can simply adjust the gain

of the device by driving the GPOS test loop with a power supply

or voltage reference. Resistor networks are provided for fixed

gain bias voltages at Pin GNEG and Pin GPOS for commonmode voltages other than 0 V. If it is desired to drive the gain

control with an active input such as a ramp, SMA connectors

can be installed in the locations GAIN− and GAIN+. Provision

is made for an optional SMA connector at PRVG for monitoring

the preamp output or driving the VGA from an external source.

Remove the 0 Ω resistor at R9 to isolate the preamp from an

external generator.

Figure 82. AD8336 Evaluation Board

6228-083

BOARD LAYOUT CONSIDERATIONS

The evaluation board uses four layers, with power and ground

planes located between two conductor layers. This arrangement

is highly recommended for customers and several views of the

board are provided as reference for board layout details. When

laying out a printed circuit board for the AD8336, remember to

provide a pad beneath the device to solder the exposed pad of

the matching device. The pad in the board should have at least

five vias in order to provide a thermal path for the chip scale

package. Unlike leaded devices, the thermal pad is the primary

means to remove heat dissipated within the device.

Table 6 is a bill of materials for the evaluation board.

Figure 83. Components for Inverting Gain Operation

6228-084

Rev. 0 | Page 25 of 28

Page 26

AD8336

06228-088

Figure 84. Component Side Copper

6228-085

Figure 87. Internal Ground Plane

Figure 85. Secondary Side Copper

Figure 86. Component Side Silk Screen

06228-086

06228-087

Rev. 0 | Page 26 of 28

Figure 88. Internal Power Plane

6228-089

Page 27

AD8336

V

GND1 GND4GND3GND2

(BLK LOOPS IN

4 CORNERS)

C8

0.1µF

VIN1

R1

0Ω

VOUTD

R3

0Ω

R5

W1

16 131415

NC NC NC

112

VOUT

2

PWRA

VCOM

INPP

INPN

5876

AD8336

NC NC

3

R4

0Ω

R6

R7

100Ω

VOUT

VOUTL

VP

R16

4.99kΩ

CR1

5.1V

VIN

R2

49.9Ω

NC = NO CONNECT

10µF

25V

U1

R8

301Ω

C1

POS

+

C4

VPOS

GNEG

GPOS

VNEG

VGAI

PRAO

L2

120nH

R9

0Ω

C3

0.1µF

11

10

94

49.9Ω

0.1µF

R10

C5

R11

0Ω

GNEG

GPOS

R12

0Ω

C6

1nF

C7

1nF

L1

120nH

PRVG

R15

R14

GAIN–

GAIN+

06228-082

R17

0Ω

R13

VNEG

C2

10µF

+

25V

Figure 89. AD8336-EVALZ Schematic Shown as Shipped, Configured for a Noninverting Gain of 4×

Table 6. AD8336 Evaluation Board Bill of Materials

Reference

Qty Name Description

Designator Manufacturer Mfg. Part Number

2 Capacitor Tantalum 10 μF, 25 V C2, C4 Nichicon F931E106MCCC

3 Capacitor 0.1 μF, 16 V, 0603, X7R C3, C5, C8 KEMET C0603C104K4RSCTU

1 Capacitor 1 nF, 50 V, 0603, X7R C7 Panasonic ECJ-1VB2A102K

1 Diode Zener, 5.1 V, 1 W CR1 Diodes, Inc. DFLZ5V1-7

2 Connector SMA Fem, RA, PC Mt VIN, VOUT Amphenol 901-143-6RFX

4 Test Loop Black

GND, GND1,

Components Corporation TP-104-01-00

GND2, GND3

2 Test Loop Violet GNEG, GPOS Components Corporation TP-104-01-07

2 Inductor Ferrite Bead L1, L2 Murata BLM18BA750SN1D

6 Resistor 0 Ω, 5%, 0603

R1, R3, R4, R9,

Panasonic ERJ-2GE0R00X

R11, R17

1 Resistor 49.9 Ω 1% 1/16 W 0603 R2 Panasonic ERJ-3EKF49R9V

1 Resistor 100 Ω 1% 1/16 W 0603 R7 Panasonic ERJ-3EKF1000V

1 Resistor 301 Ω 1/16 W 1% 0603 R8 Panasonic ERJ-3EKF3010V

1 Resistor 4.99 kΩ 1/16 W 1% 0603 R16 Panasonic ERJ-3EKF4991V

1 Test Loop Green VNEG Components Corporation TP-104-01-05

1 Test Loop Red VPOS Components Corporation TP-104-01-02

1 Header 0.1” Center W1 Molex 22-10-2031

1 Integrated Circuit VGA Z1 Analog Devices AD8336ACPZ

4 Rubber Bumper Foot NA 3M SJ67A11

Rev. 0 | Page 27 of 28

Page 28

AD8336

C

OUTLINE DIMENSIONS

INDI

PIN 1

ATO R

1.00

0.85

0.80

12° MAX

SEATING

PLANE

4.00

BSC SQ

TOP

VIEW

0.80 MAX

0.65 TYP

0.60 MAX

3.75

BSC SQ

0.35

0.20 REF

0.30

0.25

COMPLIANT TO JEDEC STANDARDS MO-220-VGGC

0.65 BSC

0.05 MAX

0.02 NOM

COPLANARITY

0.75

0.60

0.50

0.08

0.60 MAX

(BOTTOM VIEW)

13

12

EXPOSED

9

8

1.95 BSC

PIN 1

16

PAD

5

THE EXPOSED PAD IS NOT CO NNECTED

INTERNAL LY. FOR INCREASED RELI ABILI T Y

OF THE SO LDER JOI NTS AND MAXI MUM

THERMA L CAPABILIT Y, IT IS RECO MMENDED

THAT THE PADDLE BE SOLDERED TO THE

GROUND PLANE .

INDICATOR

1

4

5

2

.

2

10

.

2

5

9

.

1

0.25 MIN

S

Q

100506-A

Figure 90. 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

4 mm × 4 mm Body, Very Thin Quad

(CP-16-4)

Dimensions shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD8336ACPZ

AD8336ACPZ-R71 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ] CP-16-4

AD8336ACPZ-RL1 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ] CP-16-4

AD8336ACPZ-WP1 −40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ] CP-16-4

AD8336-EVALZ1 Evaluation Board

1

Z = Pb-free part.

1

−40°C to +85°C 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ] CP-16-4

©2006 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06228-0-10/06(0)

Rev. 0 | Page 28 of 28

Loading...

Loading...