Precision Dual-Channel,

–

+

+

B

www.BDTIC.com/ADI

FEATURES

With no external resistors

Difference amplifier: gains of 0.5, 1, or 2

Single ended amplifiers: over 40 different gains

Set reference voltage at midsupply

Excellent ac specifications

15 MHz bandwidth

30 V/μs slew rate

High accuracy dc performance

0.08% maximum gain error

10 ppm/°C maximum gain drift

80 dB minimum CMRR (G = 2)

Two channels in small 4 mm × 4 mm LFCSP

Supply current: 2.5 mA per channel

Supply range: ±2.5 V to ±18 V

APPLICATIONS

Instrumentation amplifier building blocks

Level translators

Automatic test equipment

High performance audio

Sine/Cosine encoders

GENERAL DESCRIPTION

The AD8270 is a low distortion, dual-channel amplifier with

internal gain setting resistors. With no external components,

it can be configured as a high performance difference amplifier

with gains of 0.5, 1, or 2. It can also be configured in over 40 singleended configurations, with gains ranging from −2 to +3.

The AD8270 is the first dual-difference amplifier in the small

4 mm × 4 mm

single-difference amplifier. The smaller package allows a 2×

increase in channel density and a lower cost per channel, all

with no compromise in performance.

The AD8270 operates on both single and dual supplies and

equires only 2.5 mA maximum supply current for each ampli-

r

fier. It is specified over the industrial temperature range of

−40°C to +85°C and is fully RoHS compliant.

LFCSP. It requires the same board area as a typical

Difference Amplifier

AD8270

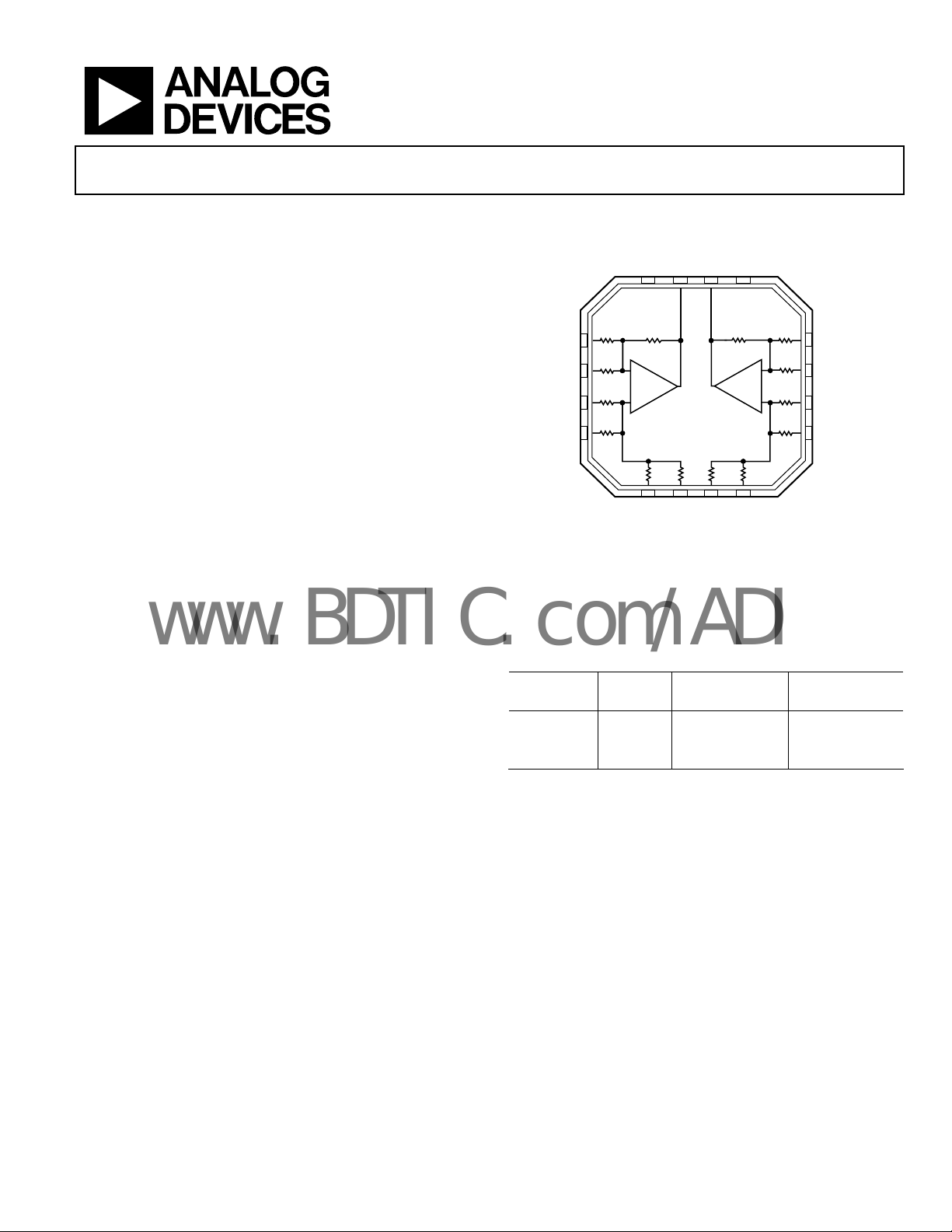

FUNCTIONAL BLOCK DIAGRAM

S

OUTA

+V

15

16

10kΩ 10kΩ 10kΩ 10kΩ

1–IN1A

10kΩ

10kΩ

10kΩ

_

+

AD8270

20kΩ 20kΩ20kΩ20kΩ

5

6

REF1A

REF2A

Figure 1.

IN2A

IN2A

IN1A

2

3

4

Table 1. Difference Amplifiers by Category

High

Speed

High

V

oltage

Single-Supply

Unidirectional

AD8270 AD628 AD8202 AD8205

AD8273 AD629 AD8203 AD8206

AMP03 AD8216

S

OUT

–V

14

13

12 –IN1B

10kΩ

_

+

8

7

REF2B

REF1B

10kΩ

10kΩ

11 –IN 2B

10 +IN2B

9+IN1B

Single-Supply

Bidirectional

6979-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

AD8270

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Difference Amplifier Configurations ........................................ 3

Absolute Maximum Ratings............................................................ 5

Thermal Resistance ...................................................................... 5

Maximum Power Dissipation ..................................................... 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics ............................................. 7

Theory of Operation ...................................................................... 13

Circuit Information.................................................................... 13

Driving the AD8270................................................................... 13

Package Considerations............................................................. 13

Power Supplies ............................................................................ 13

Input Voltage Range................................................................... 14

Applications Information.............................................................. 15

Difference Amplifier Configurations ...................................... 15

Single-Ended Configurations ................................................... 15

Differential Output .................................................................... 17

Driving an ADC ......................................................................... 18

Driving Cabling.......................................................................... 18

Outline Dimensions ....................................................................... 19

Ordering Guide .......................................................................... 19

REVISION HISTORY

1/08—Revision 0: Initial Version

Rev. 0 | Page 2 of 20

AD8270

www.BDTIC.com/ADI

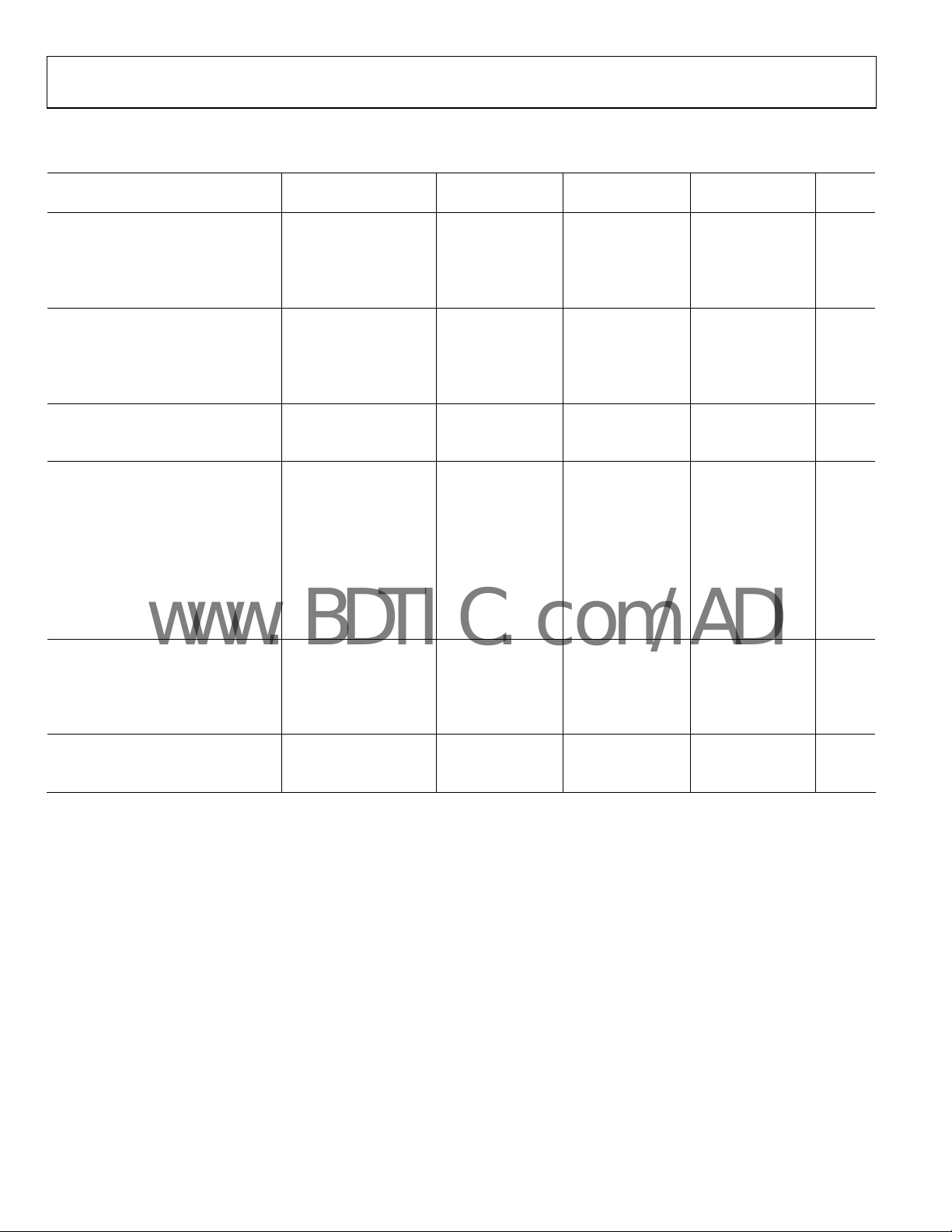

SPECIFICATIONS

DIFFERENCE AMPLIFIER CONFIGURATIONS

VS = ±15 V, V

Table 2.

G = 0.5 G = 1 G = 2

Parameter Conditions Min Typ Max Min Typ Max Min Typ Max Unit

DYNAMIC PERFORMANCE

Bandwidth 20 15 10 MHz

Slew Rate 30 30 30 V/μs

Settling Time to 0.01% 10 V step on output 700 800 700 800 700 800 ns

Settling Time to 0.001% 10 V step on output 750 900 750 900 750 900 ns

NOISE/DISTORTION

Harmonic Distortion

Voltage Noise1 f = 0.1 Hz to 10 Hz 2 1.5 1 μV p-p

f = 1 kHz 52 38 26 nV/√Hz

GAIN

Gain Error 0.08 0.08 0.08 %

Gain Drift TA = −40°C to +85°C 1 10 1 10 1 10 ppm/°C

INPUT CHARACTERISTICS

OUTPUT CHARACTERISTICS

Sinking 60 60 60 mA

POWER SUPPLY

T

1

2

3

4

2

Offset

Average Temperature Drift TA = −40°C to +85°C 3 2 1.5 μV/°C

Common-Mode Rejection

Ratio

Power Supply Rejection Ratio 2 10 2 10 2 10 μV/V

Input Voltage Range

Common-Mode Resistance4 7.5 10 7.5 kΩ

Bias Current 500 500 500 nA

Output Swing −13.8 +13.8 −13.8 +13.8 −13.8 +13.8 V

T

Short-Circuit Current Limit Sourcing 100 100 100 mA

Supply Current

(per Amplifier)

Includes amplifier voltage and current noise, as well as noise of internal resistors.

Includes input bias and offset errors.

At voltages beyond the rails, internal ESD diodes begin to turn on. In some configurations, the input voltage range may be limited by the internal op amp (see the

Input Voltage Range section for details).

Internal resistors are trimmed to be ratio matched but have ±20% absolute accuracy. Common-mode resistance was calculated with both inputs in parallel. Common-

mode impedance at only one input is 2× the resistance listed.

= 0 V, TA = 25°C, R

REF

3

= 2 kΩ, specifications referred to input, unless otherwise noted.

LOAD

f = 1 kHz, V

= 600 Ω

R

LOAD

450 1500 300 1000 225 750 μV

DC to 1 kHz 70 86 76 92 80 98 dB

−15.4 +15.4 −15.4 +15.4 −15.4 +15.4 V

= −40°C to +85°C −13.7 +13.7 −13.7 +13.7 −13.7 +13.7 V

A

2.3 2.5 2.3 2.5 2.3 2.5 mA

= −40°C to +85°C 3 3 3 mA

A

= 10 V p-p,

OUT

84 145 95 dB

Rev. 0 | Page 3 of 20

AD8270

www.BDTIC.com/ADI

VS = ±5 V, V

Table 3.

G = 0.5 G = 1 G = 2

Parameter Conditions Min Typ Max Min Typ Max Min Typ Max Unit

DYNAMIC PERFORMANCE

Bandwidth 20 15 10 MHz

Slew Rate 30 30 30 V/μs

Settling Time to 0.01% 5 V step on output 550 650 550 650 550 650 ns

Settling Time to 0.001% 5 V step on output 600 750 600 750 600 750 ns

NOISE/DISTORTION

Harmonic Distortion

Voltage Noise1 f = 0.1 Hz to 10 Hz 2 1.5 1 μV p-p

f = 1 kHz 52 38 26 nV/√Hz

GAIN

Gain Error 0.08 0.08 0.08 %

Gain Drift TA = −40°C to +85°C 1 10 1 10 1 10 ppm/°C

INPUT CHARACTERISTICS

Offset

Average Temperature Drift TA = −40°C to +85°C 3 2 1.5 μV/°C

Common-Mode Rejection Ratio DC to 1 kHz 70 86 76 92 80 98 dB

= 0 V, TA = 25°C, R

REF

2

= 2 kΩ, specifications referred to input, unless otherwise noted.

LOAD

f = 1 kHz, V

= 600 Ω

R

LOAD

= 5 V p-p,

OUT

101 141 112 dB

450 1500 300 1000 225 750 μV

Power Supply Rejection Ratio 2 10 2 10 2 10 dB

Input Voltage Range

Common-Mode Resistance

3

4

−5.4 +5.4 −5.4 +5.4 −5.4 +5.4 V

7.5 10 7.5 kΩ

Bias Current 500 500 500 nA

OUTPUT CHARACTERISTICS

Output Swing −4 +4 −4 +4 −4 +4 V

T

= −40°C to +85°C −3.9 +3.9 −3.9 +3.9 −3.9 +3.9 V

A

Short-Circuit Current Limit Sourcing 100 100 100 mA

Sinking 60 60 60 mA

POWER SUPPLY

Supply Current (per Amplifier) 2.3 2.5 2.3 2.5 2.3 2.5 mA

T

1

Includes amplifier voltage and current noise, as well as noise of internal resistors.

2

Includes input bias and offset errors.

3

At voltages beyond the rails, internal ESD diodes begin to turn on. In some configurations, the input voltage range may be limited by the internal op amp (see the

Input Voltage Range section for details).

4

Internal resistors are trimmed to be ratio matched but have ±20% absolute accuracy. Common-mode resistance was calculated with both inputs in parallel. Common-

mode impedance at only one input is 2× the resistance listed.

= −40°C to +85°C 3 3 3 mA

A

Rev. 0 | Page 4 of 20

AD8270

www.BDTIC.com/ADI

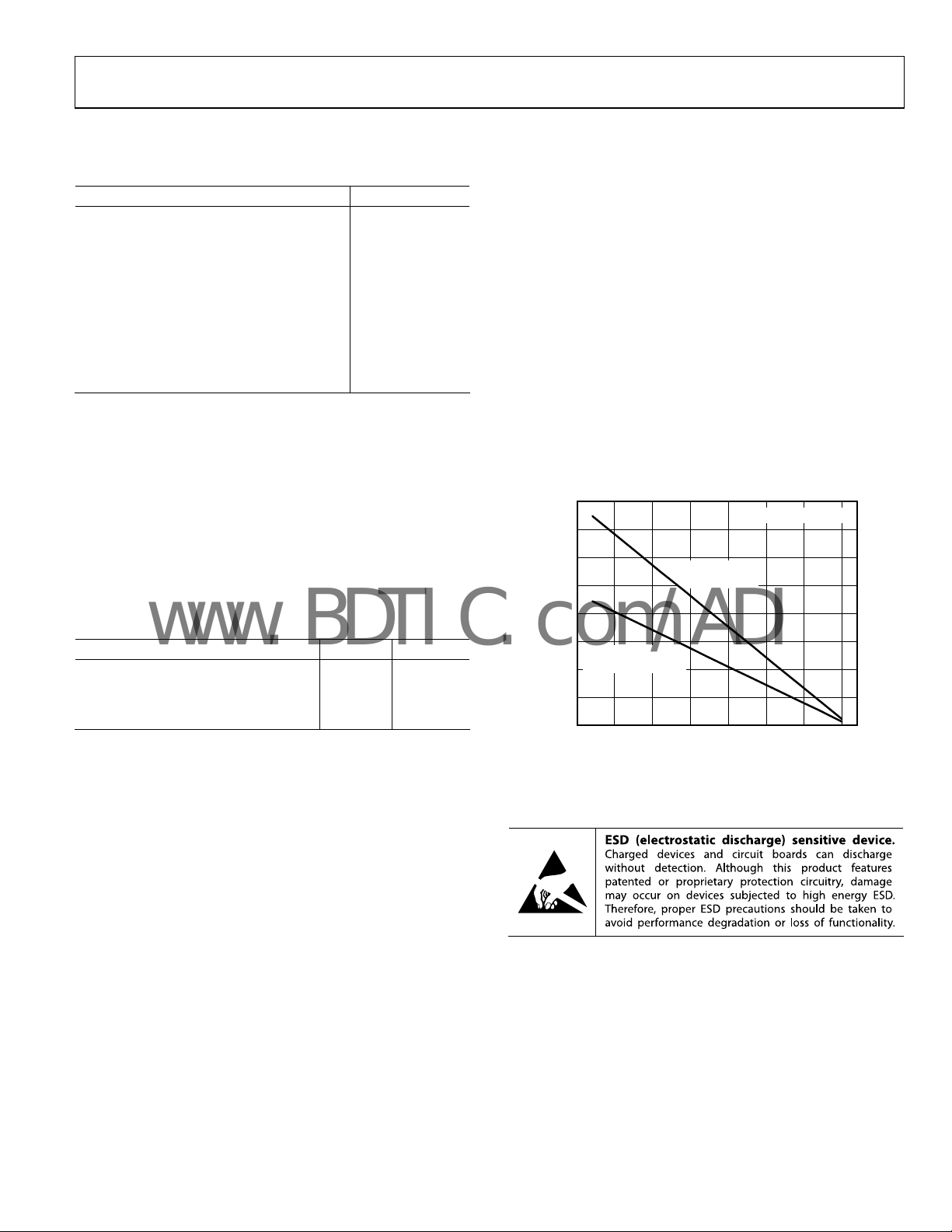

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage ±18 V

Output Short-Circuit Current

Input Voltage Range ±V

See derating

ve in Figure 2

cur

S

Storage Temperature Range −65°C to +130°C

Specified Temperature Range −40°C to +85°C

Package Glass Transition Temperature (TG) 130°C

ESD (Human Body Model) 1 kV

ESD (Charge Device Model) 1 kV

ESD (Machine Model) 0.1 kV

Stresses above those listed under Absolute Maximum Ratings

y cause permanent damage to the device. This is a stress

ma

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

Table 5. Thermal Resistance

Thermal Pad θ

16-Lead LFCSP with Thermal Pad

JA

57 °C/W

Soldered to Board

16-Lead LFCSP with Thermal Pad

96 °C/W

Not Soldered to Board

The θJA values in Tabl e 5 assume a 4-layer JEDEC standard

board with zero airflow. If the thermal pad is soldered to the

board, it is also assumed it is connected to a plane. θ

exposed pad is 9.7°C/W.

Unit

at the

JC

MAXIMUM POWER DISSIPATION

The maximum safe power dissipation for the AD8270 is limited

by the associated rise in junction temperature (T

approximately 130°C, which is the glass transition temperature,

the plastic changes its properties. Even temporarily exceeding

this temperature limit may change the stresses that the package

exerts on the die, permanently shifting the parametric performance

of the amplifiers. Exceeding a temperature of 130°C for an

extended period of time can result in a loss of functionality.

The AD8270 has built-in, short-circuit p

output current to approximately 100 mA (see Figure 19 for

ore information). While the short-circuit condition itself does

m

not damage the part, the heat generated by the condition can

cause the part to exceed its maximum junction temperature,

with corresponding negative effects on reliability.

3.2

2.8

2.4

2.0

1.6

1.2

PAD NOT SOLDERED

0.8

MAXIMUM POWER DISSIPATION (W)

0.4

0

–50 –25 0 25 50 75 100 1 25

Figure 2. Maximum Power Dissipation vs. Ambient Temperature

ESD CAUTION

PAD SOLDERED

= 57°C/W

θ

JA

= 96°C/W

θ

JA

AMBIENT TEMPERATURE (°C)

) on the die. At

J

rotection that limits the

TJ MAXIMUM = 130°C

06979-003

Rev. 0 | Page 5 of 20

AD8270

B

www.BDTIC.com/ADI

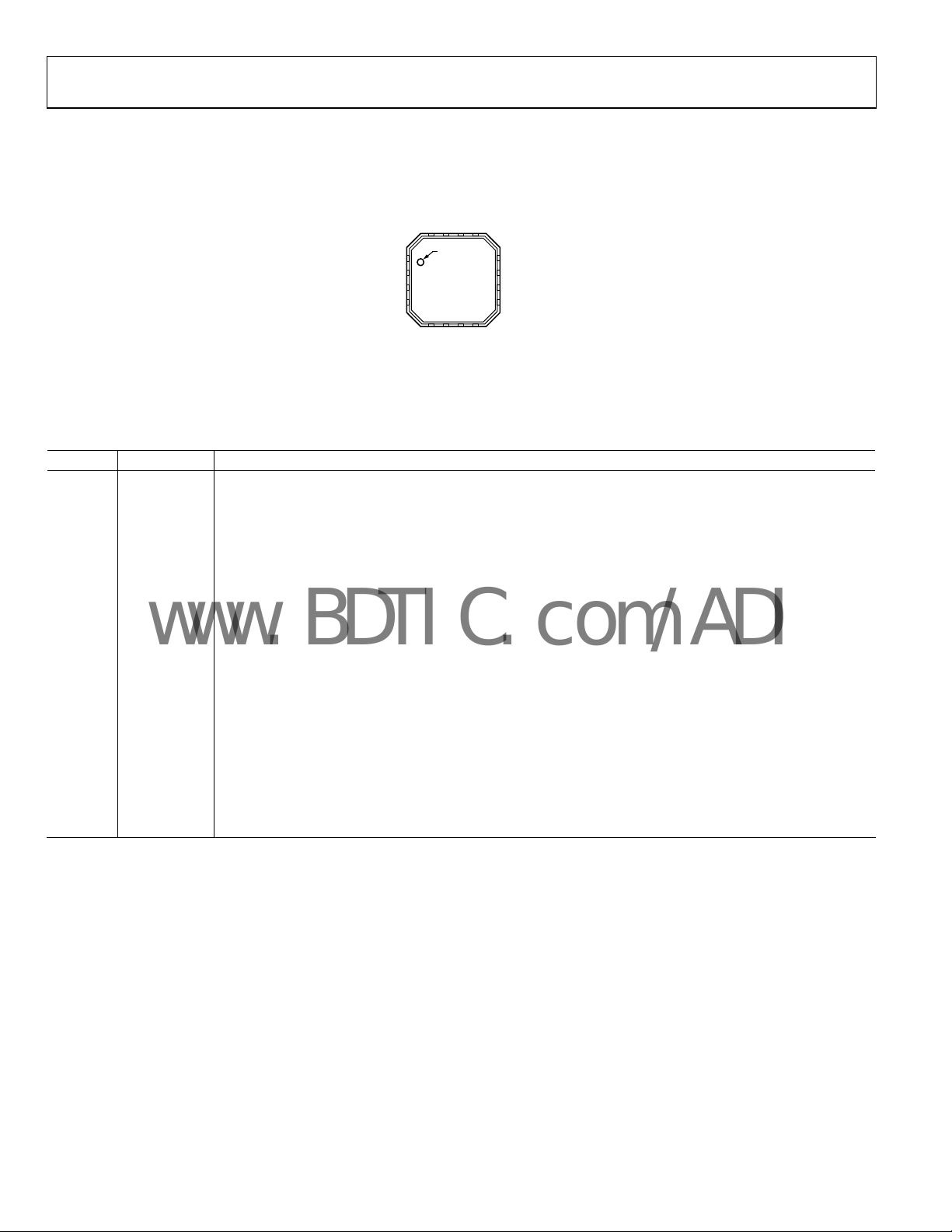

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

S

S

–V

OUTA

+V

OUT

14

13

15

16

PIN 1

1–IN1A

2–IN2A

3+IN2A

4+IN1A

INDICATOR

AD8270

TOP VIEW

(Not to Scale)

5

6

12 –IN1B

11 –I N2B

10 +IN2B

9+IN1B

8

7

REF1A

REF2A

REF2B

REF1B

Figure 3. Pin Configuration

06979-002

Table 6. Pin Function Descriptions

Pin No. Mnemonic Description

1 −IN1A 10 kΩ Resistor Connected to Negative Terminal of Op Amp A.

2 −IN2A 10 kΩ Resistor Connected to Negative Terminal of Op Amp A.

3 +IN2A 10 kΩ Resistor Connected to Positive Terminal of Op Amp A.

4 +IN1A 10 kΩ Resistor Connected to Positive Terminal of Op Amp A.

5 REF1A

6 REF2A

7 REF2B

8 REF1B

20 kΩ Resistor Connected to Positive Terminal of Op Amp A. Most configurations use this pin as a reference

oltage input.

v

20 kΩ Resistor Connected to Positive Terminal of Op Amp A. Most configurations use this pin as a reference

oltage input.

v

20 kΩ Resistor Connected to Positive Terminal of Op Amp B. Most configurations use this pin as a reference

oltage input.

v

20 kΩ Resistor Connected to Positive Terminal of Op Amp B. Most configurations use this pin as a reference

oltage input.

v

9 +IN1B 10 kΩ Resistor Connected to Positive Terminal of Op Amp B.

10 +IN2B 10 kΩ Resistor Connected to Positive Terminal of Op Amp B.

11 −IN2B 10 kΩ Resistor Connected to Negative Terminal of Op Amp B.

12 −IN1B 10 kΩ Resistor Connected to Negative Terminal of Op Amp B.

13 −V

S

Negative Supply.

14 OUTB Op Amp B Output.

15 OUTA Op Amp A Output.

16 +V

S

Positive Supply.

Rev. 0 | Page 6 of 20

AD8270

www.BDTIC.com/ADI

TYPICAL PERFORMANCE CHARACTERISTICS

VS = ±15 V, TA = 25°C, difference amplifier configuration, unless otherwise noted.

160

140

120

100

N: 1043

MEAN: –0.003

SD: 0.28

20

15

(–7.5, +7.5) (+7.5, +7.5)

10

5

(0, +15)

80

60

NUMBER OF UNITS

40

20

0

–0.9 –0.6 –0.3 0 0.3 0.6 0.9

Figure 4. Typical Distribution of

180

150

120

90

NUMBER OF UNIT S

60

30

0

SYSTEM OFFSET VOLTAGE (mV)

System Offset Voltage, G = 1

–100–150 –50 0 50 100 150

CMRR (µV/V)

Figure 5. Typical Distribution of CMRR, G = 1

400

350

300

N: 984

MEAN: –1.01

SD: 27

N: 1043

MEAN: –0.015

SD: 0.0068

0

–5

–10

(–7.5, –7.5) (+7.5, –7.5)

COMMO N-MODE INPUT VOLT AGE ( V)

–15

–20

06979-004

–10 –5 0 5 10

(0, –15)

OUTPUT VO LTAGE ( V)

06979-007

Figure 7. Common-Mode Input Voltage vs. Output Voltage,

Gain = 0.5, ±15 V Supplies

6

4

(–2.5, +2. 5) (+2.5, +2. 5)

2

(–1.25, –1.25) (+1.25, +1.25)

0

(–1.25, –1.25) (+1.25, –1. 25)

–2

(–2.5, –2.5) (+2.5, –2.5)

–4

COMMON-MO DE INPUT VOL TAGE (V)

–6

06979-005

–3 –2 –1 0 1 2 3

(0, +5)

(0, +2.5)

VS = ±2.5 VS = ±5

(0, –2.5)

(0, –5)

OUTPUT VO LTAGE (V )

06979-008

Figure 8. Common-Mode Input Voltage vs. Output Voltage,

Gain

= 0.5, ±5 V and ±2.5 V Supplies

20

15

(–14.3, +7. 85) (+14.3, +7.85)

10

(0, +15)

250

200

150

NUMBER OF UNITS

100

50

0

–0.04 –0.02 0 0. 02 0.04

GAIN ERROR (%)

Figure 6. Typical Distribution of Gain Error, G = 1

06979-006

5

0

–5

–10

(–14.3, –7.85) (+14.3, –7.85)

COMMON-MO DE INPUT VOL TAGE (V)

–15

–20

–20 –15 –10 –5 0 5 10 15 20

Figure 9. Common-Mode Input Voltage vs. Output Voltage,

Gain = 1, ±15 V Supplies

Rev. 0 | Page 7 of 20

(0, –15)

OUTPUT VOLTAGE (V)

06979-009

AD8270

www.BDTIC.com/ADI

6

4

2

0

–2

–4

COMMON-MO DE INPUT VOL TAGE (V)

–6

–5 –4 –3 –2 –1 0 1 2 3 4 5

(–1.6, +1. 7) (+ 1.6, +1.7)

(–1.6, –1.7) (+1.6, –1.7)

(–4.3, +2. 85)

(–4.3, –2.85) (+4.3, –2. 85)

(0, +5)

(+4.3, +2.85)(–4.3, +2. 85)

(0, +2.5)

VS = ±2.5 VS = ±5

(0, –2.5)

(0, –5)

OUTPUT VOL TAGE (V)

Figure 10. Common-Mode Input Voltage vs. Output Voltage,

Gain = 1, ±5 V and ±2.5 V Supplies

20

15

(–14.3, + 11.4)

10

5

0

–5

–10

COMMON-MODE INPUT VOLTAGE (V)

–15

–20

–20 –15 –10 –5 0 5 10 15 20

(0, +15)

(+14.3, + 11.4)

(+14.3, –11.4)(–14.3, –11.4)

(0, –15)

OUTPUT VO LTAGE (V )

06979-010

06979-011

140

GAIN = 2, 0.5

120

100

GAIN = 1

80

60

POSITIVE PSRR (dB)

40

20

0

10 100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 13. Positive PSRR vs. Frequency

140

GAIN = 2, 0.5

120

GAIN = 1

100

80

60

NEGATIVE PSRR (dB)

40

20

0

10 100 1k 10k 100k 1M

FREQUENCY (Hz)

06979-015

06979-016

Figure 11. Common-Mode Input Volt

age vs. Output Voltage,

Gain = 2, ±15 V Supplies

6

(–4, +4) (+4, +4)

4

2

0

–2

–4

COMMON-MO DE INPUT VOL TAGE (V)

–6

–5 –4 –3 –2 –1 0 1 2 3 4 5

(–1.6, +2. 1) (+ 1.6, +2.1)

(–1.6, –2.1) (+1.6, –2.1)

(–4, –4) (+4, –4)

Figure 12. Common-Mode Input Volt

(0, +5)

(0, +2.5)

VS = ±2.5 VS = ±5

(0, –2.5)

(0, –5)

OUTPUT VOL TAGE (V)

age vs. Output Voltage,

Gain = 2, ±5 V and ±2.5 V Supplies

06979-012

Rev. 0 | Page 8 of 20

Figure 14. Negative PSRR vs. Frequency

32

VS = ±15V

28

24

20

16

12

VS = ±5V

8

OUTPUT VOLTAGE SWING (V p-p)

4

0

100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 15. Output Voltage Swing vs. Large Signal Frequency Response

06979-017

AD8270

V

V

www.BDTIC.com/ADI

10

GAIN = 2

5

0

–5

GAIN (dB)

–10

–15

–20

100 1k 10k 100k 1M 10M 100M

GAIN = 1

GAIN = 0.5

FREQUENCY (Hz)

Figure 16. Gain vs. Frequency

06979-018

120

100

80

60

40

20

0

–20

–40

–60

SHORT-CIRCUIT CURRENT (mA)

–80

–100

–120

–40 –20 0 20 40 60 80 100 120

I

SHORT+

I

SHORT–

TEMPERATURE ( °C)

Figure 19. Short-Circuit Current vs. Temperature

06979-021

100

GAIN = 2, 0.5

90

80

GAIN = 1

70

60

50

40

CMRR (dB)

30

20

10

0

10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 17. CMRR vs. Frequency

0

–20

–40

–60

–80

–100

CHANNEL SEPARATIO N (dB)

–120

–140

10 100 1k 10k 100k

FREQUENCY (Hz)

CROSSTALK (G = 1)

Figure 18. Channel Separation vs. Frequency

+

S

+125° C

+VS– 2

+V

– 4

S

–V

+ 2

S

OUTPUT VOLTAGE SWING (V)

–V

+ 4

S

–V

06979-019

–40°C

0

+125°C

+85°C

+25°C

–40°C

S

1k200 10k

R

Figure 20. Output Voltage Swing vs. R

+

S

+VS – 3

– 6

+V

S

0

–VS + 6

OUTPUT VO LTAGE SWING (V)

–V

+ 3

S

–V

S

0 2040608010

06979-013

+125°C

CURRENT (mA)

Figure 21. Output Voltage Swing vs. Current (I

+25°C

LOAD

(Ω)

+85°C

+85°C

+125°C

+25°C

–40°C

LOAD

–40°C

OUT

+25°C

+85°C

)

06979-022

0

6979-023

Rev. 0 | Page 9 of 20

AD8270

V

V

V

www.BDTIC.com/ADI

VS = ±15V

100pF

18pF

0pF

50mV/DI

1µs/DIV

Figure 22. Small Signal Step Response, Gain = 0.5

VS = ±15V

220pF

33pF

0pF

50mV/DI

06979-024

160

140

120

100

80

60

OVERSHOOT (%)

40

20

0

0 102030405060708090100

VS = ±2.5V

CAPACITIVE L OAD (pF)

VS = ±5V

VS = ±15V

VS = ±10V

VS = ±18V

Figure 25. Small Signal Overshoot with Capacitive Load, Gain = 0.5

80

70

60

50

40

30

OVERSHOOT (%)

20

10

VS = ±2.5V

VS = ±15V

V

VS = ±18V

= ±5V

S

VS = ±10V

06979-030

1µs/DIV

Figure 23. Small Signal Step Response, Gain = 1

VS = ±15V

470pF

100pF

0pF

50ms/DI

1µs/DIV

Figure 24. Small Signal Step Response, Gain = 2

06979-025

0

0 50 100 150 200

CAPACITIVE L OAD (pF)

06979-031

Figure 26. Small Signal Overshoot with Capacitive Load, Gain = 1

80

70

60

50

40

30

OVERSHOOT (%)

20

10

06979-026

VS = ±2.5V

0

VS = ±5V

CAPACITIVE L OAD (pF)

VS = ±10V

VS = ±15V

250 300 350 400 4500 50 100 150 200

VS = ±18V

06979-032

Figure 27. Small Signal Overshoot with Capacitive Load, Gain = 2

Rev. 0 | Page 10 of 20

AD8270

V

V

V

www.BDTIC.com/ADI

VS = ±15V

V

= ±5V

IN

1V/DI

1µs/DIV

Figure 28. Large Signal Pulse Response Gain = 0.5

06979-033

45

40

35

30

25

20

15

OUTPUT SL EW RATE (V/ µs)

10

5

0

–35 –15 15 35 55 75 95 115 125–45 –25 –5 5 25 45 65 85 105

+SR

–SR

TEMPERATURE (°C)

Figure 31. Output Slew Rate vs. Temperature

06979-036

VS = ±15V

V

= ±5V

IN

2V/DI

1µs/DIV

Figure 29. Large Signal Pulse Response Gain = 1

VS = ±15V

V

= ±5V

IN

5V/DI

1k

GAIN = 2

100

GAIN = 1

VOLTAGE NOISE (nV/√Hz)

GAIN = 0.5

06979-034

10

1 10 100 1 k 10k 100k

FREQUENCY (Hz)

06979-041

Figure 32. Voltage Noise Spectral Density vs. Frequency, Referred to Output

GAIN = 2

GAIN = 1

GAIN = 1/2

1µV/DIV 1s/DIV

1µs/DIV

Figure 30. Large Signal Pulse Response, Gain = 2

06979-035

Figure 33. 0.1 Hz to 10 Hz Voltage Noise, Referred to Output

Rev. 0 | Page 11 of 20

06979-042

AD8270

www.BDTIC.com/ADI

210

180

150

120

90

NUMBER OF UNIT S

60

30

0

–600 –400 –200 0 200 400 600

V

(µV)

OSI

Figure 34. Typical Distribution of Op Amp Voltage Offset

N: 1043

MEAN: 4.6

SD: 134.5

OFFSET (10µV/ DIV)

06979-014

012345 6 78 910

Figure 37. Change in Op Amp Offset Voltag

TIME (s)

e vs. Warm-Up Time

06979-044

100

80

60

40

NUMBER OF UNITS

20

0

310 315 320 325 330 335 340

I

BIAS

(nA)

Figure 35. Typical Distribution of Op Amp Bias Current

160

140

120

100

80

60

NUMBER OF UNIT S

40

20

0

–9 –6 –3 0 3 6 9 12

I

OFFSET

(nA)

Figure 36. Typical Distribution of Op Amp Offset Current

N: 1043

MEAN: 321.6

SD: 6.9

N: 1043

MEAN: 0.31

SD: 2.59

50pA/DIV 1s/DIV

06979-020

06979-028

Figure 38. 0.1 Hz to 10 Hz Current Noise of Internal Op Amp

10

1

CURRENT NOISE (pA/√Hz)

0.1

06979-027

1 10 100 1k 10k 100k

FREQUENCY (Hz)

06979-029

Figure 39. Current Noise Spectral Density of Internal Op Amp

Rev. 0 | Page 12 of 20

AD8270

–

–

+

+

B

www.BDTIC.com/ADI

THEORY OF OPERATION

Size

The AD8270 fits two op amps and 14 resistors in a 4 mm ×

4 mm package.

DRIVING THE AD8270

The AD8270 is easy to drive, with all configurations presenting

at least several kilohms (kΩ) of input resistance. The AD8270

should be driven with a low impedance source: for example,

another amplifier. The gain accuracy and common-mode rejection

of the AD8270 depend on the matching of its resistors. Even

source resistance of a few ohms can have a substantial effect on

these specifications.

PACKAGE CONSIDERATIONS

The AD8270 is packaged in a 4 mm × 4 mm LFCSP. Beware of

blindly copying the footprint from another 4 mm × 4 mm LFCSP

part; it may not have the same thermal pad size and leads. Refer

to the

Outline Dimensions section to verify that the PCB symbol

as the correct dimensions.

h

The 4 mm × 4 mm LFCSP of the AD8270 comes with a thermal

p

ad. This pad is connected internally to −V

. Connecting to this

S

pad is not necessary for electrical performance; the pad can be

left unconnected or can be connected to the negative supply rail.

Connecting the pad to the negative supply rail is recommended

n high vibration applications or when good heat dissipation is

i

required (for example, with high ambient temperatures or when

driving heavy loads). For best heat dissipation performance, the

negative supply rail should be a plane in the board. See the

Absolute Maximum Ratings section for thermal coefficients

th and without the pad soldered.

wi

Space between the leads and thermal pad should be as wide as

p

ossible to minimize the risk of contaminants affecting performance. A thorough washing of the board is recommended after the

soldering process, especially if high accuracy performance is

required at high temperatures.

POWER SUPPLIES

A stable dc voltage should be used to power the AD8270. Noise

on the supply pins can adversely affect performance. A bypass

capacitor of 0.1 μF should be placed between each supply pin

and ground, as close as possible to each supply pin. A tantalum

capacitor of 10 μF should also be used between each supply and

ground. It can be farther away from the supply pins and, typically,

it can be shared by other precision integrated circuits.

The AD8270 is specified at ±15 V and ±5 V, but it can be used with

u

nbalanced supplies, as well. For example, −V

The difference between the two supplies must be kept below 36 V.

= 0 V, +VS = 20 V.

S

IN1A

IN2A

IN2A

IN1A

S

OUTA

+V

15

16

10kΩ 10kΩ 10kΩ 10kΩ

1

10kΩ

2

3

4

_

10kΩ

+

10kΩ

Figure 40. Functional Block Diagram

20kΩ 20kΩ20kΩ20kΩ

5

REF1A

AD8270

6

REF2A

S

OUT

–V

14

13

12 –IN1B

10kΩ

_

+

8

7

REF2B

REF1B

10kΩ

10kΩ

11 –IN 2B

10 +I N2B

9+IN1B

6979-059

CIRCUIT INFORMATION

The AD8270 has two channels, each consisting of a high precision,

low distortion op amp and seven trimmed resistors. These resistors can be connected to make a wide variety of amplifier

configurations: difference, noninverting, inverting, and more.

The resistors on the chip can be connected in parallel for a wider

range of options. Using the on-chip resistors of the AD8270

provides the designer several advantages over a discrete design.

DC Performance

Much of the dc performance of op amp circuits depends on the

accuracy of the surrounding resistors. The resistors on the AD8270

are laid out to be tightly matched. The resistors of each part are

laser trimmed and tested for their matching accuracy. Because

of this trimming and testing, the AD8270 can guarantee high

accuracy for specifications such as gain drift, common-mode

rejection, and gain error.

AC Performance

Because feature size is much smaller in an integrated circuit than

on a PCB board, the corresponding parasitics are smaller, as well.

The smaller feature size helps the ac performance of the AD8270.

For example, the positive and negative input terminals of the

AD8270 op amp are not pinned out intentionally. By not

connecting these nodes to the traces on the PCB board, the

capacitance remains low, resulting in both improved loop

stability and common-mode rejection over frequency.

Production Costs

Because one part, rather than several, is placed on the PCB

board, the board can be built more quickly.

Rev. 0 | Page 13 of 20

AD8270

www.BDTIC.com/ADI

INPUT VOLTAGE RANGE

The AD8270 has a true rail-to-rail input range for the majority

of applications. Because most AD8270 configurations divide down

the voltage before they reach the internal op amp, the op amp sees

only a fraction of the input voltage.

f how the voltage division works in the difference amplifier

o

configuration.

R2

(V

+IN

R1 + R2

R3

R1

R2

Figure 41. Voltage Division in the Difference Amplifier Configuration

Figure 41 shows an example

)

R4

R2

(V

)

+IN

R1 + R2

06979-061

The internal op amp voltage range may be relevant in the

following applications, and calculating the voltage at the

internal op amp is advised.

• Dif

ference amplifier configurations using supply voltages

of less than ±4.5 V

ference amplifier configurations with a reference

• Dif

voltage near the rail

gle-ended amplifier configurations

• Sin

For correct operation, the input voltages at the internal op amp

m

ust stay within 1.5 V of either supply rail.

Voltages beyond the supply rails should not be applied to the

p

art. The part contains ESD diodes at the input pins, which

conduct if voltages beyond the rails are applied. Currents greater

than 5 mA can damage these diodes and the part. For a similar

part that can operate with voltages beyond the rails, see the

AD8273 data sheet.

Rev. 0 | Page 14 of 20

AD8270

–

–

www.BDTIC.com/ADI

APPLICATIONS INFORMATION

DIFFERENCE AMPLIFIER CONFIGURATIONS

The AD8270 can be placed in difference amplifier configurations

with gains of 0.5, 1, and 2. Figure 42 through Figure 44 show the

ifference amplifier configurations, referenced to ground. The

d

AD8270 can also be referred to a combination of reference voltages.

For example, the reference could be set at 2.5 V, using just 5 V

and GND. Some of the possible configurations are shown in

Figure 45 through Figure 47.

The layout for Channel A is shown in Figure 42 through Figure 47.

The l

ayout for Channel B is symmetrical. Tab le 7 shows the pin

co

nnections for Channel A and Channel B.

SINGLE-ENDED CONFIGURATIONS

The AD8270 can be configured for a wide variety of singleended configurations with gains ranging from −2 to +3.

Tabl e 8 shows a subset of the possible configurations.

Many signal gains have more than one configuration choice,

ich allows freedom in choosing the op amp closed-loop gain.

wh

In general, for designs that need to be stable with a large capacitive

load on the output, choose a configuration with high loop gain.

Otherwise, choose a configuration with low loop gain, because

these configurations typically have lower noise, lower offset,

and higher bandwidth.

1

2

3

4

S

1

2

3

4

1

2

3

4

16 15

10kΩ 10kΩ

10kΩ

10kΩ

10kΩ

20kΩ 20kΩ

56

+V

16 15

10kΩ 10kΩ

10kΩ

10kΩ

10kΩ

20kΩ 20kΩ

56

–VS+V

16 15

10kΩ 10kΩ

10kΩ

10kΩ

10kΩ

20kΩ 20kΩ

56

–VS+V

5kΩ

10kΩ

–IN

=

10kΩ

+IN

5kΩ

+VS + –V

S

10kΩ

10kΩ

+VS + –V

5kΩ

5kΩ

+VS + –V

2

2

2

10kΩ

10kΩ

10kΩ

S

10kΩ

S

06979-056

06979-057

06979-058

S

–IN

=

+IN

S

–IN

=

+IN

S

+IN

16 15

10kΩ 10kΩ

1

10kΩ

2

IN

10kΩ

3

10kΩ

4

20kΩ 20kΩ

56

GND

10kΩ

–IN

=

10kΩ

+IN

GND

5kΩ

5kΩ

06979-053

Figure 42. Gain = 0.5 Difference Amplifier, Referenced to Ground

10kΩ 10kΩ

1

–IN

10kΩ

2

NC

10kΩ

3

NC

10kΩ

4

+IN

20kΩ 20kΩ

NC = NO CONNECT

16 15

56

GND

–IN

=

+IN

10kΩ

10kΩ

GND

10kΩ

10kΩ

06979-054

Figure 43. Gain = 1 Difference Amplifier, Referenced to Ground

–IN

+IN

10kΩ 10kΩ

1

10kΩ

2

10kΩ

3

10kΩ

4

20kΩ 20kΩ

16 15

56

GND

–IN

=

+IN

5kΩ

5kΩ

GND

10kΩ

10kΩ

06979-055

Figure 44. Gain = 2 Difference Amplifier, Referenced to Ground

–IN

+IN

–V

Figure 45. Gain = 0.5 Difference Amplifier, Referenced to Midsupply

–IN

NC

NC

+IN

NC = NO CONNECT

Figure 46. Gain = 1 Difference Amplifier, Referenced to Midsupply

IN

+IN

Figure 47. Gain = 2 Difference Amplifier, Referenced to Midsupply

Table 7. Pin Connections for Difference Amplifier Configurations

Channel A Channel B

Gain and Reference Pin 1 Pin 2 Pin 3 Pin 4 Pin 5 Pin 6 Pin 12 Pin 11 Pin 10 Pin 9 Pin 8 Pin 7

Gain of 0.5, Referenced to Ground OUT −IN +IN GND GND GND OUT −IN +IN GND GND GND

Gain of 0.5, Referenced to Midsupply OUT −IN +IN −V

+V

S

+V

S

OUT −IN +IN −VS+VS+V

S

S

Gain of 1, Referenced to Ground −IN NC NC +IN GND GND −IN NC NC +IN GND GND

Gain of 1, Referenced to Midsupply −IN NC NC +IN −V

+V

S

−IN NC NC +IN −VS+V

S

S

Gain of 2, Referenced to Ground −IN −IN +IN +IN GND GND −IN −IN +IN +IN GND GND

Gain of 2, Referenced to Midsupply −IN −IN +IN +IN −V

+V

S

−IN −IN +IN +IN −VS+V

S

S

Rev. 0 | Page 15 of 20

AD8270

www.BDTIC.com/ADI

Table 8. Selected Single-Ended Configurations

Electrical Performance Pin Connections

Op Amp

Signal Gain

−2 3 5 kΩ IN IN GND GND GND GND

−1.5 3 4.8 kΩ IN IN GND GND GND IN

−1.4 3 5 kΩ IN IN GND GND NC IN

−1.25 3 5.333 kΩ IN IN GND NC GND IN

−1 3 5 kΩ IN IN GND GND IN IN

−0.8 3 5.556 kΩ IN IN IN GND NC GND

−0.667 2 8 kΩ IN NC GND GND GND IN

−0.6 2 8.333 kΩ IN NC GND GND NC IN

−0.5 2 8.889 kΩ IN NC GND NC GND IN

−0.333 2 7.5 kΩ IN NC GND GND IN IN

−0.25 1.5 8 kΩ OUT IN GND GND GND IN

−0.2 1.5 8.333 kΩ OUT IN GND GND NC IN

−0.125 1.5 8.889 kΩ OUT IN GND NC GND IN

+0.1 1.5 8.333 kΩ OUT IN IN GND NC GND

+0.2 2 10 kΩ IN NC GND IN NC IN

+0.25 1.5 24 kΩ OUT GND GND GND GND IN

+0.3 1.5 25 kΩ OUT GND GND GND NC IN

+0.333 2 24 kΩ GND NC GND GND GND IN

+0.375 1.5 26.67 kΩ OUT GND GND NC GND IN

+0.4 2 25 kΩ GND NC GND GND NC IN

+0.5 3 24 kΩ GND GND GND GND GND IN

+0.5 1.5 15 kΩ OUT GND GND GND IN IN

+0.6 3 25 kΩ GND GND GND GND NC IN

+0.6 1.5 16.67 kΩ OUT GND IN GND NC GND

+0.625 1.5 16 kΩ OUT IN NC IN IN GND

+0.667 2 15 kΩ GND NC GND GND IN IN

+0.7 1.5 16.67 kΩ OUT IN IN IN NC GND

+0.75 3 26.67 kΩ GND GND GND NC GND IN

+0.75 1.5 13.33 kΩ OUT GND GND IN GND IN

+0.8 2 16.67 kΩ GND NC IN GND NC GND

+0.9 1.5 16.67 kΩ OUT GND GND IN NC IN

+1 1.5 15 kΩ OUT GND IN IN GND GND

+1 1.5 >1 GΩ OUT IN IN IN IN IN

+1 3 >1 GΩ IN IN IN IN IN IN

+1.125 1.5 26.67 kΩ OUT GND NC IN IN GND

+1.2 3 16.67 kΩ GND GND IN GND NC GND

+1.2 1.5 25 kΩ OUT GND IN IN NC GND

+1.25 1.5 24 kΩ OUT GND IN IN IN GND

+1.333 2 15 kΩ GND NC IN IN GND GND

+1.5 3 13.33 kΩ GND GND GND IN GND IN

+1.5 1.5 >1 GΩ OUT GND IN IN IN IN

+1.6 2 25 kΩ GND NC IN IN NC GND

+1.667 2 24 kΩ GND NC IN IN IN GND

+1.8 3 16.67 kΩ GND GND GND IN NC IN

+2 2 >1 GΩ GND NC IN IN IN IN

+2.25 3 26.67 kΩ GND GND NC IN IN GND

+2.4 3 25 kΩ GND GND IN IN NC GND

+2.5 3 24 kΩ GND GND IN IN IN GND

+3 3 >1 GΩ GND GND IN IN IN IN

Closed-Loop Gain

Input

Resistance

10 kΩ −

Pin 1

Rev. 0 | Page 16 of 20

10 kΩ −

Pin 2

10 kΩ +

Pin 3

10 kΩ +

Pin 4

20 kΩ +

Pin 5

20 kΩ +

Pin 6

AD8270

–IN+

–

–IN+

–

www.BDTIC.com/ADI

The AD8270 Specifications section and Ty pi cal Perfor m a n c e

Characteristics section show the performance of the part primarily

hen it is in the difference amplifier configuration. To get a good

w

estimate of the performance of the part in a single-ended

configuration, refer to the difference amplifier configuration

with the corresponding closed-loop gain (see

Tabl e 9 ).

Table 9. Closed-Loop Gain of the Difference Amplifiers

Difference Amplifier Gain Closed-Loop Gain

0.5 1.5

1 2

2 3

Gain of 1 Configuration

The AD8270 is designed to be stable for loop gains of 1.5 and

greater. Because a typical voltage follower configuration has

a loop gain of 1, it may be unstable. Several stable G = 1 configurations are listed in Tabl e 8 .

DIFFERENTIAL OUTPUT

The AD8270 can easily be configured for differential output.

Figure 48 shows the configuration for a G = 1 differential output

plifier. The OCM node in the figure sets the common-mode

am

output voltage. Figure 49 shows the configuration for a G = 1

d

ifferential output amplifier, where the average of two voltages

sets the common-mode output voltage. For example, this

configuration can be used to set the common mode at 2.5 V,

using just a 5 V reference and GND.

OUT+OUT

13

14

15

16

10kΩ 10kΩ 10kΩ 10kΩ

1

10kΩ

_

2

10kΩ

3

IN

+

10kΩ

4

AD8270

20kΩ 20kΩ20kΩ20kΩ

5

6

OCM

10kΩ

_

10kΩ

+

10kΩ

8

7

Figure 48. Differential Output, G = 1

12

11

10

9

V

– V

= V

+OUT

– V

+OUT

–OUT

+ V

–OUT

V

OCM

+OUT

–OUT

+IN

–IN

+IN

–IN

V

= V

OCM

+IN

=

–IN

OCM

, Common-Mode Output Voltage

Set with Reference Voltage

OUT+OUT

13

14

15

16

10kΩ 10kΩ 10kΩ 10kΩ

1

10kΩ

_

2

10kΩ

3

IN

+

10kΩ

4

AD8270

20kΩ 20kΩ20kΩ20kΩ

5

6

B

10kΩ

_

10kΩ

+

10kΩ

8

7

Figure 49. Differential Output, G = 1

12

11

10

9

V

– V

= V

–OUT

B

– V

+OUT

–OUT

VA + V

B

=

2

V

OCM

+OUT

–OUT

+IN

–IN

AA

+IN

–IN

V

+ V

+OUT

+IN

=

–IN

+ V

V

A

2

, Common-Mode Output Voltage

Set as the Average of Two Voltages

Note that these two configurations are based on the G = 0.5

difference amplifier configurations shown in Figure 42 and

Figure 45. A similar technique can be used to create differential

output

with a gain of 2 or 4, using the G = 1 and G = 2 difference

amplifier configurations, respectively.

06979-062

06979-063

Rev. 0 | Page 17 of 20

AD8270

V

–12V

www.BDTIC.com/ADI

DRIVING AN ADC

The AD270 high slew rate and drive capability, combined with

its dc accuracy, make it a good ADC driver. The AD8270 can

drive both single-ended and differential input ADCs. Many

converters require the output to be buffered with a small value

resistor combined with a high quality ceramic capacitor. See the

converter data sheet for more details.

in dif

ferential configuration, driving the AD7688 ADC. The

AD8270

s

precisely where the

divides down the 5 V reference voltage from the ADR435,

o that the common-mode output voltage is 2.5 V, which is

AD7688 needs it.

Figure 51 shows the AD8270

To reduce the peaking, use a resistor between the AD8270 and the

ble. Because cable capacitance and desired output response vary

ca

widely, this resistor is best determined empirically. A good starting

point is 20 Ω.

AD8270

(DIFF OUT)

DRIVING CABLING

All cables have a certain capacitance per unit length, which varies

widely with cable type. The capacitive load from the cable may

cause peaking or instability in output response, especially when the

AD8270 is operating in a gain of 0.5.

+12

16 13

10kΩ

–IN

+IN

5V_REF

0.1µF

–IN

+IN

2

10kΩ

3

10kΩ

4

20kΩ

5

20kΩ

6

20kΩ

7

20kΩ

8

10kΩ

9

10kΩ

10

10kΩ

11

10kΩ

10kΩ

AD8270

10kΩ

10kΩ

Figure 51. Driving an ADC

AD8270

(SINGLE OUT)

06979-060

Figure 50. Driving Cabling

NOTE:

1

15

14

12

POWER SUPPLY DECOUPLING

NOT SHO WN.

33Ω

33Ω

2.7nF

COG

2.7nF

COG

+12V

2

V

IN

V

ADR435

GND

4

OUT

3

+IN

4

–IN

AD7688

5

REF

10µF

1

0.1µF

5V_REF

06979-037

Rev. 0 | Page 18 of 20

AD8270

www.BDTIC.com/ADI

OUTLINE DIMENSIONS

4.00

PIN 1

INDICATOR

1.00

0.85

0.80

12° MAX

SEATING

PLANE

BSC SQ

TOP

VIEW

0.80 MAX

0.65 TYP

COMPLIANT TO JEDEC STANDARDS MO-220-VGG C

0.35

0.30

0.25

3.75

BSC SQ

0.20 REF

0.60 MAX

0.65 BSC

0.05 MAX

0.02 NOM

COPLANARIT Y

0.50

0.40

0.30

0.08

Figure 52. 16-Lead Lead Frame Chip Scale Package [LFCSP_VQ]

4

mm × 4 mm Body, Very Thin Quad

(CP-16-10)

Dimensions are shown in millimeters

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD8270ACPZ-R7

AD8270ACPZ-RL

AD8270ACPZ-WP

1

Z = RoHS Compliant Part.

1

1

1

−40°C to +85°C 16-Lead LFCSP_VQ CP-16-10

−40°C to +85°C 16-Lead LFCSP_VQ CP-16-10

−40°C to +85°C 16-Lead LFCSP_VQ CP-16-10

0.60 MAX

13

12

EXPOSED

(BOTTOM VIEW)

9

8

PAD

16

1

5

1.95 BSC

PIN 1

INDICATOR

2.50

2.35 SQ

2.20

4

0.25 MIN

010606-0

Rev. 0 | Page 19 of 20

AD8270

www.BDTIC.com/ADI

NOTES

©2008 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D06979-0-1/08(0)

Rev. 0 | Page 20 of 20

Loading...

Loading...