Instrumentation Amplifier

AD8237

Rev. PrA

Trademarks and registered trademarks are the property of their respective owners.

Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved.

BW

1

+IN

2

–IN

3

–V

S

4

V

OUT

8

FB

7

REF

6

+V

S

5

AD8237

TOP VIEW

(Not to Scale)

+

–

–

+

10289-001

AD8421

AD8237

AD620

AD8237

AD8250

AD8221/AD8222

AD8231

AD621

AD8420

AD8251

AD8220/AD8224

AD8293

AD524

AD8235/AD8236

AD8253

AD8228

AD8553

AD526

AD627

AD8231

AD8295

AD8556

AD624

AD8226

AD8557

6

5

4

3

2

1

–1

0

0 1 2 3 4 5

INPUT COMMON MODE VOLTAGE (V)

OUTPUT VOLTAGE (V)

TRADITI ONAL IN-AMP

(RAIL-TO-RAIL OUT)

AD8237

10289-002

G = 100

V

S

= 5V

V

REF

= 2.5V

Preliminary Technical Data

FEATURES

Gain set with 2 external resistors

Can achieve low gain drift at all gains

Ideal for portable systems

Maximum supply current: 130 µA

Rail-to-rail input and output

Zero input crossover distortion

Designed for excellent dc performance

Minimum CMRR: 110 dB

Maximum offset voltage drift: 0.2 µV/°C

Maximum gain error: 0.005% (all gains)

Maximum gain drift: 0.5 ppm/°C (all gains)

Single-supply operation: 1.8 V to 5.5 V

8-lead MSOP package

APPLICATIONS

Bridge amplification

Pressure measurement

Medical instrumentation

Portable systems

Current measurement

GENERAL DESCRIPTION

The AD8237 is a micropower, zero drift, rail-to-rail input and

output instrumentation amplifier. The relative match of two

resistors sets any gain from 1 to 1000. The AD8237 has excellent

gain accuracy performance that can be preserved at any gain

with two ratio-matched resistors.

The AD8237 uses a novel indirect current-feedback architecture to

achieve a true rail-to-rail capability. Unlike conventional in-amps,

the AD8237 can fully amplify signals with common-mode voltage

at or even slightly beyond its supplies. This enables applications

with high common-mode voltages to use smaller supplies and

save power.

The AD8237 is an excellent choice for portable systems. With a

minimum supply voltage of 1.8 V, a 115 µA typical supply current,

and wide input range, the AD8237 makes full use of a limited

power budget, while still offering bandwidth and drift performance

suitable for bench-top systems.

The AD8237 is available in an 8-lead MSOP package. Performance

is specified over the full temperature range of −40°C to +125°C.

Micropower, Zero Drift, True Rail-to-Rail

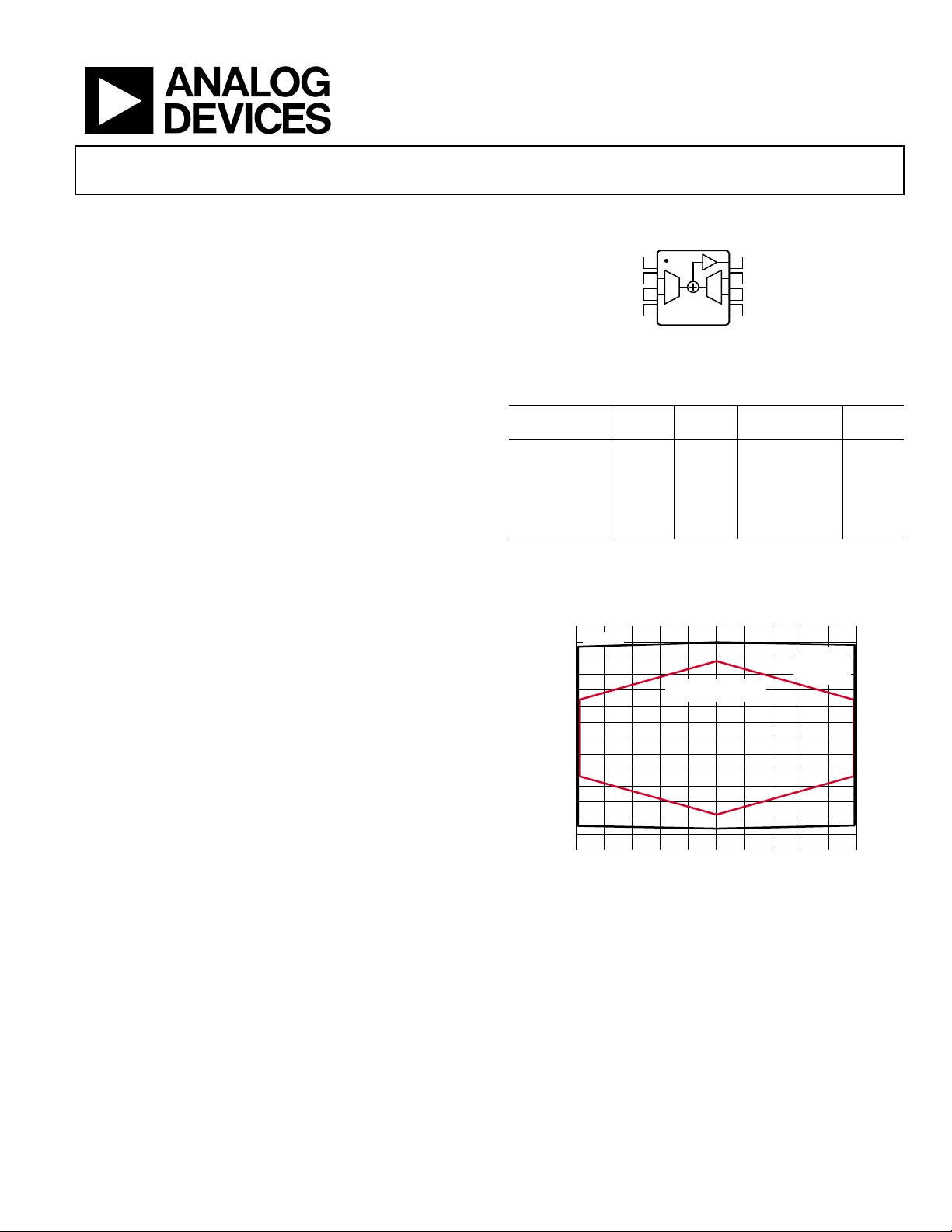

PIN CONFIGURATION

Figure 1.

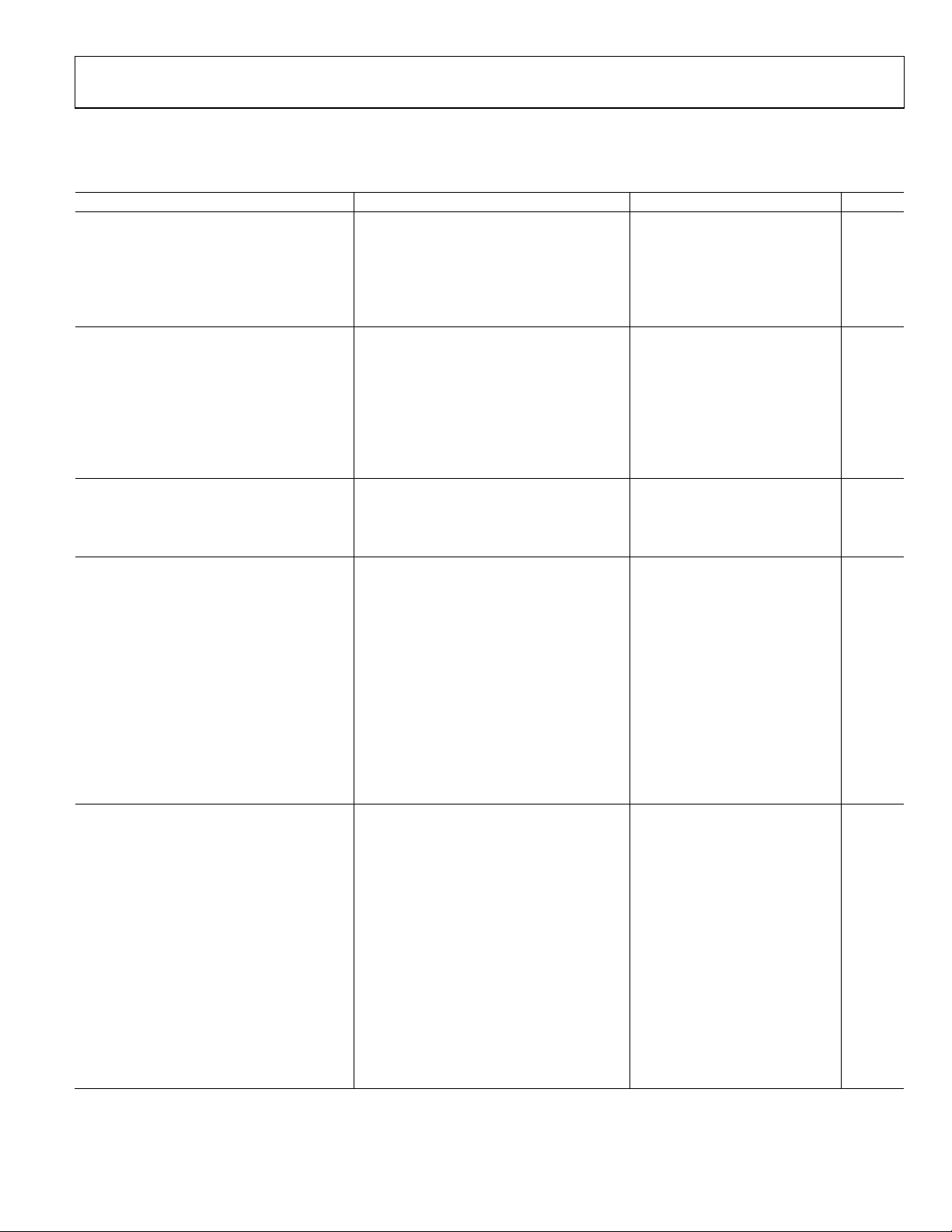

Table 1. Instrumentation Amplifiers by Category

General

Purpose

1

See www.analog.com for the latest instrumentation amplifiers.

Zero

Drift

Military

Grade Micropower

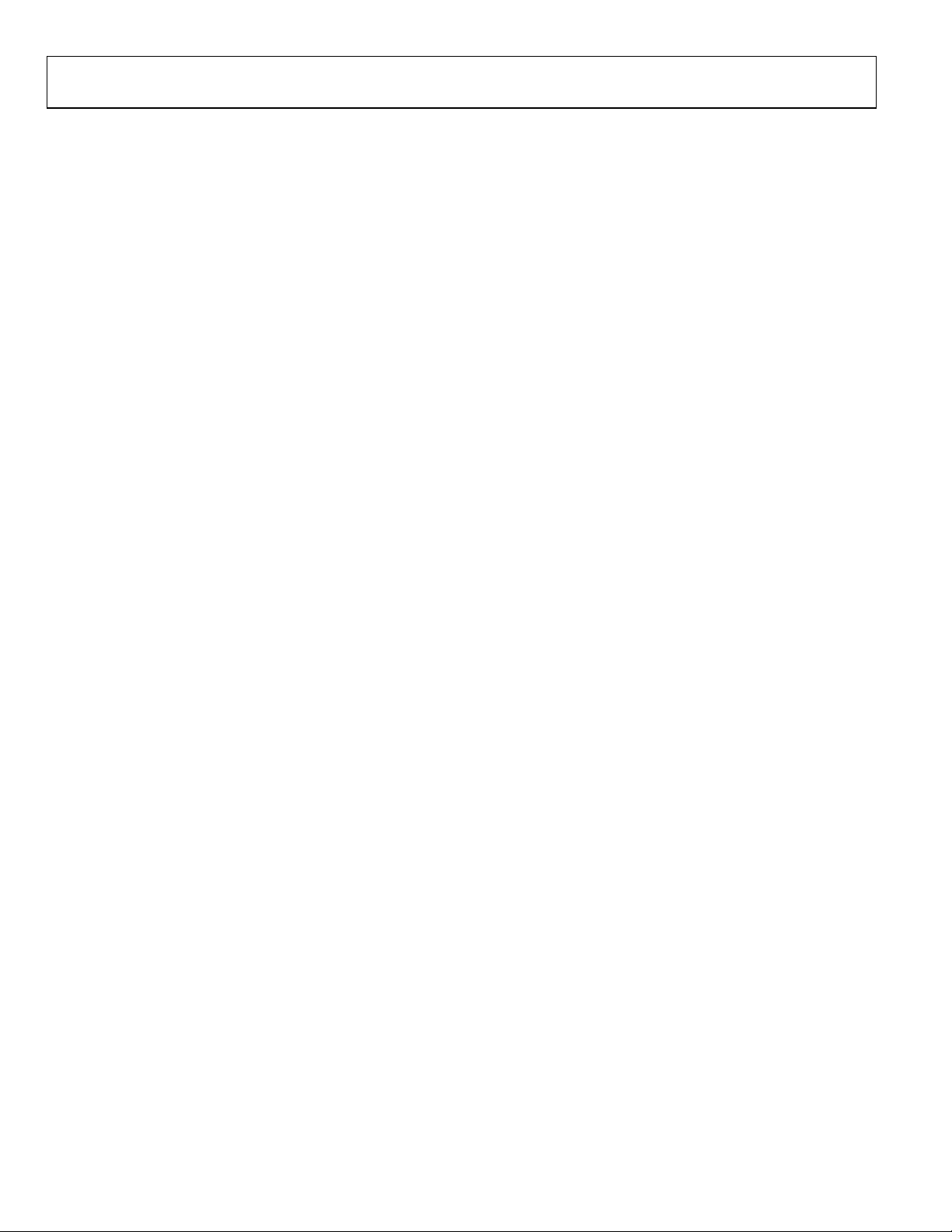

Figure 2. Input Common-Mode Voltage vs. Output Voltage, +V

1

Digital

Gain

= 5 V, G = 100

S

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

AD8237 Preliminary Technical Data

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Pin Configuration ............................................................................. 1

Specifications ..................................................................................... 3

Absolute Maximum Ratings ............................................................ 7

Thermal Resistance ...................................................................... 7

ESD Caution .................................................................................. 7

Pin Configuration and Function Descriptions ............................. 8

Theory of Operation ........................................................................ 9

Architecture ................................................................................... 9

Setting the Gain ............................................................................ 9

Gain Accuracy ............................................................................ 10

Clock Feedthrough ..................................................................... 10

Input Voltage Range ................................................................... 10

Input Protection ......................................................................... 10

Filtering Radio Frequency Interference .................................. 11

Using the Reference Pin ............................................................ 11

Layout .......................................................................................... 11

Input Bias Current Return Path ............................................... 12

Outline Dimensions ....................................................................... 13

Rev. PrA | Page 2 of 13

Preliminary Technical Data AD8237

COMMON-MODE REJECTION RATIO (CMRR)

VCM = 0.2 V to 4.8 V

CMRR at 1 kHz

80

dB

INPUTS1

Valid for REF and FB pair, as well as +IN and −IN

Small Signal Bandwidth

–3 dB

SPECIFICATIONS

+VS = +5 V, − VS = 0 V, V

otherwise noted.

Table 2.

Parameter Test Conditions/Comments Min Typ Max Unit

CMRR DC to 60 Hz

G = 1, G = 10 110 120 dB

G = 100, G = 1000 120 140 dB

Over Temperature (G = 1) TA = −40°C to +125°C 106 dB

NOISE

Voltage Noise

Spectral Density f = 1 kHz 70 nV/√Hz

Peak to Peak f = 0.1 Hz to 10 Hz 1.5 µV p-p

Current Noise

Spectral Density f = 1 kHz 100 fA/√Hz

Peak to Peak f = 0.1 Hz to 10 Hz TBD pA p-p

VOLTAGE OFFSET

Offset 60 µV

Average Temperature Coefficient TA = −40°C to +125°C 0.2 µV/°C

Offset RTI vs. Supply (PSR) 106 dB

= 2.5 V, V

REF

= 2.5 V, TA = 25°C, G = 1 to 1000, RL = 10 kΩ to ground, specifications referred to input, unless

CM

Input Bias Current TA = +25°C 0.5 nA

TA = −40°C to +85°C 1 nA

TA = +125°C 15 nA

Input Offset Current TA = +25°C 0.5 nA

TA = −40°C to +85°C 1 nA

TA = +125°C 5 nA

Input Impedance

Differential 200||5 MΩ||pF

Common Mode 600||10 MΩ||pF

Differential Input Operating Voltage TA = –40°C to +125°C −3.8 3.8 V

Input Operating Voltage (+IN, −IN, or REF) TA = +25°C −VS − 0.3 +VS + 0.3 V

DYNAMIC RESPONSE

Low Bandwidth Mode Pin 1 connected to −VS

G = 1 200 kHz

G = 10 20 kHz

G = 100 2 kHz

G = 1000 0.2 kHz

High Bandwidth Mode Pin 1 connected to +VS

G = 10 100 kHz

G = 100 10 kHz

G = 1000 1 kHz

T

= –40°C to +125°C −VS − 0.2 +VS + 0.2 V

A

Rev. PrA | Page 3 of 13

AD8237 Preliminary Technical Data

G = 100

440 µs

Gain vs. Temperature

TA = −40°C to +125°C

0.5

ppm/°C

Parameter Test Conditions/Comments Min Typ Max Unit

Settling Time 0.01% 4 V output step

Low Bandwidth Mode Pin 1 connected to −VS

G = 1 80 µs

G = 10 100 µs

G = 1000 4 ms

High Bandwidth Mode Pin 1 connected to +VS

G = 10 80 µs

G = 100 100 µs

G = 1000 820 µs

Slew Rate

Low Bandwidth Mode 0.05 V/µs

High Bandwidth Mode 0.15 V/µs

EMI Filter Frequency 6 MHz

GAIN2 G = 1 + (R2/R1)

Gain Range3 1 1000 V/V

Gain Error V

Gain Error vs. V

CM

= 0.2 V to 3.3 V, G = 1 to G = 1000 0.005 %

OUT

TBD ppm

Gain Nonlinearity V

= 0.2 V to 4.8 V, RL = 10 kΩ to ground

OUT

G = 1, G = 10 3 ppm

G = 100 6 ppm

G = 1000 10 ppm

OUTPUT

Output Swing

RL = 10 kΩ to midsupply

TA = +25°C −VS + 0.05 +VS − 0.05 V

TA = −40°C to 125°C −VS + 0.07 +VS − 0.07 V

RL = 100 kΩ to midsupply

TA = +25°C −VS + 0.02 +VS − 0.02 V

TA = −40°C to 125°C −VS + 0.03 +VS − 0.03 V

Short-Circuit Current 4 mA

POWER SUPPLY

Operating Range 1.8 5.5 V

Quiescent Current TA = +25°C 115 130 µA

TA = −40°C to +125°C 150 µA

TEMPERATURE RANGE

Specified −40 +125 °C

1

Specifications apply to input voltages between 0 V and 5 V. When measuring voltages beyond the supplies, there is additional offset error, bias currents increase and

input impedance decrease, especially at higher temperatures.

2

For G > 1, errors from the external resistors, R1 and R2, must be added to these specifications, including error from the FB pin bias current.

3

The AD8237 has only been characterized for gains of 1 to 1000; however, higher gains are possible.

Rev. PrA | Page 4 of 13

Preliminary Technical Data AD8237

G = 1, G = 10

106

120 dB

TA = −40°C to +85°C

1

nA

G = 1

200 kHz

+VS = 1.8 V, −VS = 0 V, V

otherwise noted.

Table 3.

Parameter Test Conditions/Comments Min Typ Max Unit

COMMON-MODE REJECTION RATIO (CMRR) VCM = 0.2 V to 1.6 V

CMRR DC to 60 Hz

G = 100, G = 1000 120 140 dB

Over Temperature (G = 1) TA = −40°C to +125°C 104 dB

CMRR at 1 kHz 80 dB

NOISE

Voltage Noise

Spectral Density f = 1 kHz, V

Peak to Peak f = 0.1 Hz to 10 Hz, V

Current Noise

Spectral Density f = 1 kHz 100 fA/√Hz

Peak to Peak f = 0.1 Hz to 10 Hz TBD pA p-p

VOLTAGE OFFSET

Offset 60 µV

Average Temperature Coefficient TA = −40°C to +125°C 0.2 µV/°C

Offset RTI vs. Supply (PSR) 106 dB

INPUTS1 Valid for REF and FB pair, as well as +IN and −IN

Input Bias Current TA = +25°C 0.5 nA

= 0.9 V, VCM = 0.9 V, TA = 25°C, G = 1 to 1000, RL = 10 kΩ to ground, specifications referred to input, unless

REF

≤ 100 mV 70 nV/√Hz

DIFF

≤ 100 mV 1.5 µV p-p

DIFF

TA = +125°C 15 nA

Input Offset Current TA = +25°C 0.5 nA

TA =−40°C to +85°C 1 nA

TA = −125°C 5 nA

Input Impedance

Differential 200||5 MΩ||pF

Common Mode 600||10 MΩ||pF

Differential Input Operating Voltage TA = −40°C to +125°C −0.7 +0.7 V

Input Operating Voltage (+IN, −IN, REF, or FB) TA = +25°C −VS − 0.3 +VS + 0.3 V

T

= −40°C to +125°C −VS − 0.2 +VS + 0.2 V

A

DYNAMIC RESPONSE

Small Signal Bandwidth −3 dB

Low Bandwidth Mode Pin 1 connected to −VS

G = 10 20 kHz

G = 100 2 kHz

G = 1000 0.2 kHz

High Bandwidth Mode Pin 1 connected to +VS

G = 10 100 kHz

G = 100 10 kHz

G = 1000 1 kHz

Slew Rate

Low Bandwidth Mode 0.05 V/µs

High Bandwidth Mode 0.15 V/µs

EMI Filter Frequency 6 MHz

Rev. PrA | Page 5 of 13

AD8237 Preliminary Technical Data

Gain vs. Temperature

TA = −40°C to +125°C

0.5

ppm/°C

TA = −40°C to 125°C

−VS + 0.07

+VS − 0.07

V

Parameter Test Conditions/Comments Min Typ Max Unit

GAIN2 G = 1 + (R2/R1)

Gain Range3 1 1000 V/V

Gain Error V

Gain Error vs. V

CM

= 0.2 V to 1.0 V, G = 1 to G = 1000 0.005 %

OUT

TBD ppm

Gain Nonlinearity V

= 0.2 V to 1.6 V

OUT

G = 1, G = 10 3 ppm

G = 100 6 ppm

G = 1000 10 ppm

OUTPUT

Output Swing

RL = 10 kΩ to midsupply

TA = +25°C −VS + 0.05 +VS − 0.05 V

RL = 100 kΩ to midsupply

TA = +25°C −VS + 0.02 +VS − 0.02 V

TA = −40°C to 125°C −VS + 0.03 +VS − 0.03 V

Short-Circuit Current 4 mA

POWER SUPPLY

Operating Range 1.8 5.5 V

Quiescent Current TA = +25°C 115 130 µA

TA = −40°C to +125°C 150 µA

TEMPERATURE RANGE

Specified −40 +125 °C

1

Specifications apply to input voltages between 0 V and 1.8 V. When measuring voltages beyond the supplies, there is additional offset error, bias currents increase,

and input impedance decrease, especially at higher temperatures.

2

For G > 1, errors from the external resistors, R1 and R2, must be added to these specifications, including error from the FB pin bias current.

3

The AD8237 has only been characterized for gains of 1 to 1000; however, higher gains are possible.

Rev. PrA | Page 6 of 13

Preliminary Technical Data AD8237

Human Body Model

8 kV

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage 6 V

Output Short-Circuit Current Duration Indefinite

Maximum Voltage at −IN, +IN, FB, or REF1 +VS + 0.3 V

Minimum Voltage at −IN, +IN, FB, or REF1 −VS − 0.3 V

Storage Temperature Range −65°C to +150°C

Junction Temperature Range −65°C to +150°C

ESD

Charge Device Model 1.25 kV

Machine Model 0.2 kV

1

If input voltages beyond the specified minimum or maximum voltages are

expected, place resistors in series with the inputs to limit the current to 5 mA.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for a device in free air.

Table 5.

Package θJA Unit

8-Lead MSOP, 4-Layer JEDEC Board 135 °C/W

ESD CAUTION

Rev. PrA | Page 7 of 13

AD8237 Preliminary Technical Data

BW

1

+IN

2

–IN

3

–V

S

4

V

OUT

8

FB

7

REF

6

+V

S

5

AD8237

TOP VIEW

(Not to Scale)

+

–

–

+

10289-003

4

−VS

Negative Supply.

5

+VS

Positive Supply.

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

Table 6. Pin Function Descriptions

Pin No. Mnemonic Description

1 BW Connect this pin to +VS for high bandwidth mode, and connect this pin to −VS for low bandwidth mode.

2 +IN Positive Input.

3 −IN Negative Input.

6 REF Reference Input.

7 FB Feedback Input.

8 V

Output.

OUT

Rev. PrA | Page 8 of 13

Preliminary Technical Data AD8237

+IN

–IN

g

m1

I2

I1

I1 – I2

+

–

R2

R1

V

OUT

FB

REF

AD8237

g

m2

RFI

FILTER

TIA

+

–

+

–

RFI

FILTER

ALS

ALS

+

–

INTERNAL

IN-AMP

V

CM

=

V

S

2

V

CM

=

V

S

2

–IN

FB

TO g

m2

TO g

m1

+V

S

–V

S

+V

S

–V

S

RFI

FILTER

RFI

FILTER

+

–

+

–

+V

S

–V

S

+V

S

–V

S

10289-067

R1

R2

1+=G

49.9

49.9

2.00

20

80.6

5.03

THEORY OF OPERATION

ARCHITECTURE

The AD8237 is based on an indirect current feedback topology

consisting of three amplifiers: two matched transconductance

amplifiers that convert voltage to current, and one transimpedance

amplifier that converts current to voltage.

To understand how the AD8237 works, first consider only the

internal in-amp. Assume a positive differential voltage is applied

across the inputs of the transconductance amplifier, g

voltage is converted into a differential current, I1, by the g

Initially, I2 is zero; therefore, I1 is fed into the TIA, causing the

output to increase. If there is feedback from the output of the TIA

to the negative terminal of g

2, and the positive terminal is held

m

constant, the increasing output of the TIA causes I2, as shown, to

increase. When it is assumed that the TIA has infinite gain, the

loop is satisfied when I2 equals I1. Because the gain of g

are matched, this means that the differential input voltage across

g

1 appears across the inputs of gm2. This behavioral model is all

m

that is needed for proper operation of the AD8237, and the rest of

the circuit is for optimization of performance.

The AD8237 employs a novel adaptive level shift (ALS) technique.

This is a switched capacitor method that shifts the common-mode

level of the input signal to the optimal level for the in-amp while

preserving the differential signal. Once this is accomplished,

additional performance benefits can be achieved by using the

internal in-amp to compare +IN to FB and −IN to REF. This is

only practical because the signals coming out of the ALS blocks

are all referred to the same common-mode potential.

In traditional instrumentation amplifiers, the input common-mode

voltage can limit the available output swing, typically depicted in a

hexagon plot. Because of this limit, there are very few instrumentation

amplifiers that can measure small signals near either supply rail. The

AD8237 employs the indirect current feedback topology and ALS

to achieve a truly rail-to-rail characteristic.

m

Figure 4. Simplified Schematic

1. This input

.

m

1 and gm2

m

Rev. PrA | Page 9 of 13

The AD8237 includes an RFI filter to remove high frequency outof-band signals without affecting input impedance and CMRR over

frequency. Additionally, there is a bandwidth mode pin to adjust

the compensation. For gains greater than or equal to 10, the mode

pin (BW) can be tied to +V

to change the compensation and increase

S

the gain bandwidth product of the amplifier to 1 MHz. Otherwise,

connect the mode pin to −V

for a 200 kHz gain bandwidth product.

S

SETTING THE GAIN

There are several ways to configure the AD8237. The transfer

function of the AD8237 in the configuration in Figure 4 is

V

= G(V

OUT

where:

Table 7. Suggested Resistors for Various Gains (1% Resistors)

R1 (kΩ) R2 (kΩ) Gain

None Short 1.00

10 90.9 10.09

5 95.3 20.06

2 97.6 49.8

1 100 101

1 200 201

1 499 500

1 1000 1001

While the ratio of R2 to R1 sets the gain, the designer determines

the absolute value of the resistors. Larger values reduce power

consumption and output loading; smaller values limit the FB input

bias current and offset current error. If the parallel combination

of R1 and R2 is greater than about 30 kΩ, the resistors start to

contribute to the noise. For best output swing and linearity, keep

(R1 + R2) || R

≥ 10 kΩ.

L

IN+

− V

IN−

) + V

REF

AD8237 Preliminary Technical Data

AD8237

+IN

–IN

REF

FB

V

OUT

G = 1 +

R2

R1

IB+

I

B

–

V

REF

R1 R2

R1||

R2

+

–

IBR

I

B

F

10289-068

AD8237

+IN

–IN

REF

FB

V

OUT

R1 R2

V

IN

R

S

R

IN

R

IN

IF R1||R2 = R

S

,

V

OUT

= V

IN

× (1 +

R2

R1

)

V

+IN

= V

IN

×

R

IN

RS+ R

IN

10289-069

AD8237

R

PROTECT

R

PROTECT

V

IN+

+

–

V

IN–

+

–

+V

S

–V

S

POSITIVE VOLTAGE PROTECTION:

R

PROTECT

>

V

IN

– +V

S

5mA

NEGATIVE VOLTAGE PROTECTION:

R

PROTECT

>

–V

S

– V

IN

5mA

10289-070

FB bias current error can be reduced by placing a resistor of value

R1||R2 in series with the REF terminal, as shown in Figure 5. At

higher gains, this resistor can simply be the same value as R1.

Although there is internal ripple-suppression circuitry, trace

amounts of these clock frequencies and their harmonics can be

observed at the output in some configurations. These ripples are

typically 100 µV RTI when the bandwidth is greater than the clock

frequency. They can be larger after a transient but settle back to

nominal, which is included in the settling time specifications. The

amount of feedthrough at the output is dependent upon the gain

and bandwidth mode. The worst case is in high bandwidth mode

when the gain can be almost 40 before the clock ripple is outside

the bandwidth of the amplifier. For some applications, it may be

necessary to use additional filtering after the AD8237 to remove

this ripple.

Figure 5. Cancelling Error from FB Input Bias Current

Some applications may be able to take advantage of the symmetry of

the input transconductance amplifiers by canceling input impedance

errors, as shown in Figure 6. If the source resistance is well known,

setting the parallel combination of R1 and R2 equal to R

S

accomplishes this. Pay careful attention to output loading and

noise to determine if this is practical.

Figure 6. Canceling Input Impedance Errors

GAIN ACCURACY

Unlike most instrumentation amplifiers, the relative match of the

two gain setting resistors determines the gain accuracy of the AD8237

rather than a single external resistor. For example, if two resistors

have exactly the same absolute error, there is no error in gain.

Conversely, two 1% resistors can cause approximately 2% maximum

gain error at high gains. Temperature coefficient mismatch of the

gain setting resistors increases the gain drift of the instrumentation

amplifier circuit according to the gain equation. Because these

external resistors do not have to match any on-chip resistors,

resistors with good TC tracking can achieve excellent gain drift.

INPUT VOLTAGE RANGE

The allowable input range of the AD8237 is much simpler than

traditional architectures. For the transfer function of the AD8237 to

be valid, the input voltage must follow two rules

• Keep the differential input voltage within ±(Total Supply

Volta ge – 1.2) V.

• Keep the voltage of the inputs (including the REF and FB pins)

and the output within the specified voltage range, which are

approximately the supply rails.

Because the output swing is completely independent of the input

common-mode voltage, there are no hexagonal figures or complicated

formulas to follow, and no limitation for the output swing the

amplifier has for input signals with changing common mode.

INPUT PROTECTION

If no external protection is used, keep the inputs of the AD8237

within the voltages specified in the absolute maximum ratings. If the

application requires voltages beyond these ratings, input protection

resistors can be placed in series with the inputs of the AD8237 to

limit the current to 5 mA. For example, if +V

overload voltage can occur at the inputs, place a protection resistor of

at least (10 V − 3 V)/5 mA = 1.4 kΩ in series with inputs.

is 3 V and a 10 V

S

CLOCK FEEDTHROUGH

The AD8237 uses nonoverlapping clocks to perform the chopping

and ALS functions. The input voltage-to-current amplifiers are

chopped at approximately 27 kHz.

Figure 7. Protection Resistors for Large Input Voltages

Rev. PrA | Page 10 of 13

Preliminary Technical Data AD8237

+IN

+V

S

–V

S

C

C

1nF

5%

C

D

10nF

C

C

1nF

5%

10µF

10µF

0.1µF

0.1µF

R

10kΩ

1%

R

10kΩ

1%

AD8237

–IN

10289-071

DIFFERENTIAL FILTER CUTOFF =

1

2 R (2C

D

+ CC)

COMMON-MODE FILTER CUTOFF =

1

2 R C

C

AD8237

+IN

–IN

REF

FB

V

OUT

R2

R1

V

OUT

= (V

REF

+ V

+IN

– V

–IN

) (1 +

R2

R1

)

10289-072

AD8237

+IN

–IN

REF

FB

V

OUT

G = 1 +

R2 + R

REF

R1

V

REF

R1

R2

R

REF

10289-073

AD8237

+IN

–IN

REF

FB

V

OUT

G = 1 +

R2 + R3

||

R4

R1

R1 R2

R3

R4

V

S

10289-074

FILTERING RADIO FREQUENCY INTERFERENCE

The AD8237 contains an on-chip RFI filter that is sufficient for a

majority of applications. For applications where additional radio

frequency immunity is needed, an external RFI filter can also be

applied as shown in Figure 8.

Traditional instrumentation amplifier architectures require the

reference pin to be driven with a low impedance source. In these

traditional architectures, impedance at the reference pin degrades

both CMRR and gain accuracy. With the AD8237 architecture,

resistance at the reference pin has no effect on CMRR.

USING THE REFERENCE PIN

In general, instrumentation amplifier reference pins can be useful

for a few reasons. They provide a means of physically separating the

input and output grounds to reject ground bounce common to the

inputs. They can also be used to precisely level-shift the output signal.

In the configuration shown in Figure 4 through Figure 6, the gain of

the reference pin to the output is unity, as is common in a typical inamp. Because the reference pin is functionally no different from the

positive input, it can be used with gain, as shown in Figure 9. This can

be very useful in certain cases, such as dc-removal servo loops,

which typically use inverting integrators. This requires special

attention to the input range (especially at REF) and the output range.

All three input voltages are referred to the one ground shown, which

may need to be a low impedance midsupply.

Figure 8. Adding Extra RFI Filtering

Figure 9. Applying Gain to the Reference Voltage

Rev. PrA | Page 11 of 13

Figure 10. Calculating Gain with Reference Resistance

Resistance at the reference pin does affect the gain of the AD8237;

howe ver, if this resistance is constant, the gain setting resistors can be

adjusted to compensate. For example, the AD8237 can be driven

with a voltage divider, as shown in Figure 11.

Figure 11. Using Resistor Divider to Set Reference Voltage

LAYOUT

Common-Mode Rejection Ratio over Frequency

Poor layout can cause some of the common-mode signal to be

converted to a differential signal before reaching the in-amp. This

conversion can occur when the path to the positive input pin has

a different frequency response than the path to the negative input

pin. For best CMRR vs. frequency performance, closely match the

impedance of each path. Place additional source resistance in the

input path (for example, for input protection) close to the in-amp

inputs to minimize their interaction with the parasitic capacitance

from the printed circuit board (PCB) traces.

Power Supplies

Use a stable dc voltage to power the instrumentation amplifier. Noise

on the supply pins can adversely affect performance.

AD8237 Preliminary Technical Data

R1

R2

AD8237

+V

S

+IN

–IN

0.1µF

10µF

0.1µF

10µF

–V

S

V

OUT

10289-075

CAPACITIV E LY COUPLED

+V

S

C

R

R

C

–V

S

AD8237

1

f

HIGH-PASS

=

2πRC

THERMOCOUPLE

+V

S

–V

S

10MΩ

AD8237

TRANSFORMER

+V

S

–V

S

AD8237

CORRECT

V

OUT

V

OUT

THERMOCOUPLE

+V

S

–V

S

AD8237

CAPACITIV E LY COUPLED

+V

S

C

C

–V

S

AD8237

TRANSFORMER

+V

S

–V

S

AD8237

INCORRECT

V

OUT

V

OUT

V

OUT

V

OUT

10289-076

Place a 0.1 µF capacitor as close as possible to each supply pin. As

shown in Figure 12, a 10 µF tantalum capacitor can be used farther

away from the part. This capacitor, which is intended to be effective at

low frequencies, can usually be shared by other precision integrated

circuits. Keep the traces between these integrated circuits short to

minimize interaction of the trace parasitic inductance with the

shared capacitor. If a single supply is used, decoupling capacitors

at –V

can be omitted.

S

Reference

The output voltage of the AD8237 is developed with respect to the

potential on the reference terminal. Take c are to tie REF to the

appropriate local ground.

INPUT BIAS CURRENT RETURN PATH

The input bias current of the AD8237 must have a return path to

ground. When the source, such as a thermocouple, cannot provide

a return current path, create one, as shown in Figure 13.

Figure 12. Supply Decoupling, REF, and Output Referred to Local Ground

Figure 13. Creating an I

Rev. PrA | Page 12 of 13

BIAS

Path

Preliminary Technical Data AD8237

COMPLIANT TO JEDEC STANDARDS MO-187-AA

0.80

0.60

0.40

8°

0°

4

8

1

5

PIN 1

0.65 BSC

SEATING

PLANE

0.38

0.22

1.10 MAX

3.20

3.00

2.80

COPLANARITY

0.10

0.23

0.08

3.20

3.00

2.80

5.15

4.90

4.65

0.15

0.00

0.95

0.85

0.75

©2012 Analog Devices, Inc. All rights reserved. Trademarks and

OUTLINE DIMENSIONS

Figure 14. 8-Lead Mini Small Outline Package [MSOP]

(RM-8)

Dimensions shown in millimeters

registered trademarks are the property of their respective owners.

PR10289-0-6/12(PrA)

Rev. PrA | Page 13 of 13

Loading...

Loading...