24-Bit, 625 kSPS, 109 dB Sigma-Delta

V

V

ADC with On-Chip Buffers, Serial Interface

FEATURES

120 dB dynamic range at 78 kHz output data rate

109 dB dynamic range at 625 kHz output data rate

112 dB SNR at 78 kHz output data rate

107 dB SNR at 625 kHz output data rate

625 kHz maximum fully filtered output word rate

Programmable oversampling rate (32× to 256×)

Flexible serial interface

Fully differential modulator input

On-chip differential amplifier for signal buffering

Low-pass finite impulse response (FIR) filter with default

or user-programmable coefficients

Overrange alert bit

Digital offset and gain correction registers

Low power and power-down modes

SYNC

Synchronization of multiple devices via

2

I

S interface mode

APPLICATIONS

Data acquisition systems

Vibration analysis

Instrumentation

pin

V

REF+

REFGND

MCLK

MCLKGND

SYNC

RESET

SH2:0

ADR2:0

CDIV

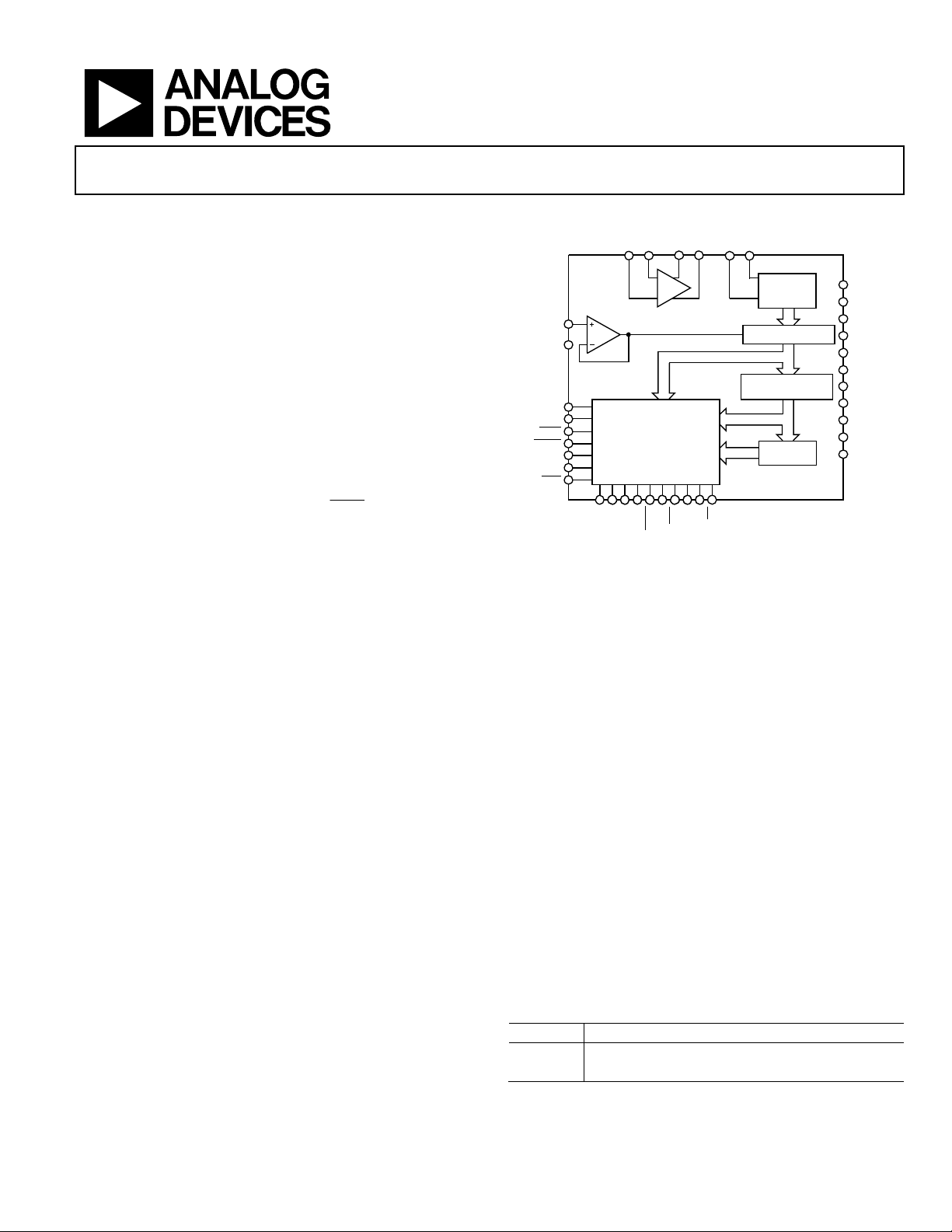

AD7763

FUNCTIONAL BLOCK DIAGRAM

IN+

IN–

MULTIBIT

Σ-Δ

MODULATOR

RECONSTRUCTION

PROGRAMMABLE

DECIMATION

FIR FILTER

ENGINE

BUF

AD7763

CONTROL L OGIC

OFFSET AND GAIN

S

2

I

SCP

I/O

REGISTERS

SDL

SCR

DRDY

DIFF

SCO

FSO

SDO

Figure 1.

FSI

SDI

AV

DD1

AV

DD2

AV

DD3

AV

DD4

DECAPA

DECAPB

R

BIAS

AGND

V

DRIVE

DV

DD

DGND

05476-001

GENERAL DESCRIPTION

The AD7763 high performance, 24-bit, Σ-Δ analog-to-digital

converter (ADC) combines wide input bandwidth and high

speed with the benefits of Σ-Δ conversion, as well as performance

of 107 dB SNR at 625 kSPS, making it ideal for high speed data

acquisition. A wide dynamic range, combined with significantly

reduced antialiasing requirements, simplifies the design process.

An integrated buffer to drive the reference, a differential amplifier for signal buffering and level shifting, an overrange flag,

internal gain and offset registers, and a low-pass, digital FIR

filter make the AD7763 a compact, highly integrated data

acquisition device requiring minimal peripheral component

selection. In addition, the device offers programmable

decimation rates and a digital FIR filter, which can be userprogrammed to ensure that its characteristics are tailored for the

user’s application. The AD7763 is ideal for applications demanding

high SNR without necessitating the design of complex, frontend signal processing.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

The differential input is sampled at up to 40 MSPS by an analog

modulator. The modulator output is processed by a series

of low-pass filters, the final filter having default or userprogrammable coefficients. The sample rate, filter corner

frequencies, and output word rate are set by a combination of

the external clock frequency and the configuration registers of

the AD7763.

The reference voltage supplied to the AD7763 determines the

analog input range. With a 4 V reference, the analog input range

is ±3.2 V differential-biased around a common mode of 2 V.

This common-mode biasing can be achieved using the on-chip

differential amplifiers, further reducing the external signal

conditioning requirements.

The AD7763 is available in an exposed paddle, 64-lead TQFP_EP

and is specified over the industrial temperature range from

−40°C to +85°C.

Table 1. Related Devices

Part No. Description

AD7760 24-bit, 2.5 MSPS, 100 dB Σ-Δ, parallel interface

AD7762 24-bit, 625 kSPS, 109 dB Σ-Δ, parallel interface

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005–2009 Analog Devices, Inc. All rights reserved.

AD7763

TABLE OF CONTENTS

Features .............................................................................................. 1

Example 2 .................................................................................... 19

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Timing Specifications ....................................................................... 5

Timing Diagrams .......................................................................... 6

Absolute Maximum Ratings ............................................................ 7

ESD Caution .................................................................................. 7

Pin Configuration and Function Descriptions ............................. 8

Terminology .................................................................................... 10

Typical Performance Characteristics ........................................... 11

Theory of Operation ...................................................................... 14

AD7763 Interface ............................................................................ 15

Reading Data Using the SPI Interface ..................................... 15

Driving the AD7763 ....................................................................... 20

Using the AD7763 ...................................................................... 21

Bias Resistor Selection ............................................................... 21

Decoupling and Layout Recommendations................................ 22

Supply Decoupling ..................................................................... 23

Additional Decoupling .............................................................. 23

Reference Voltage Filtering ....................................................... 23

Differential Amplifier Components ........................................ 23

Exposed Paddle ........................................................................... 23

Layout Considerations ............................................................... 23

Programmable FIR Filter ............................................................... 24

Downloading a User-Defined Filter ............................................ 25

Example Filter Download ......................................................... 26

Registers ........................................................................................... 27

Control Register 1—Address 0x001 ......................................... 27

Synchronization .......................................................................... 15

Sharing the Serial Bus ................................................................ 15

Writing to the AD7763 .............................................................. 16

Reading Status and Other Registers ......................................... 17

Reading Data Using the I2S Interface ....................................... 18

Clocking the AD7763 ..................................................................... 19

Example 1 .................................................................................... 19

REVISION HISTORY

11/09—Rev. 0 to Rev. A

Changes to Figure 5 .......................................................................... 8

Changes to Sharing the Serial Bus Section .................................. 15

Changes to Figure 26 ...................................................................... 16

Updated Outline Dimensions ....................................................... 29

Changes to Ordering Guide .......................................................... 29

10/05—Revision 0: Initial Version

Control Register 2—Address 0x002 ......................................... 27

Status Register (Read Only) ...................................................... 28

Offset Register—Address 0x003 ............................................... 28

Gain Register—Address 0x004 ................................................. 28

Overrange Register—Address 0x005 ....................................... 28

Outline Dimensions ....................................................................... 29

Ordering Guide .......................................................................... 29

Rev. A | Page 2 of 32

AD7763

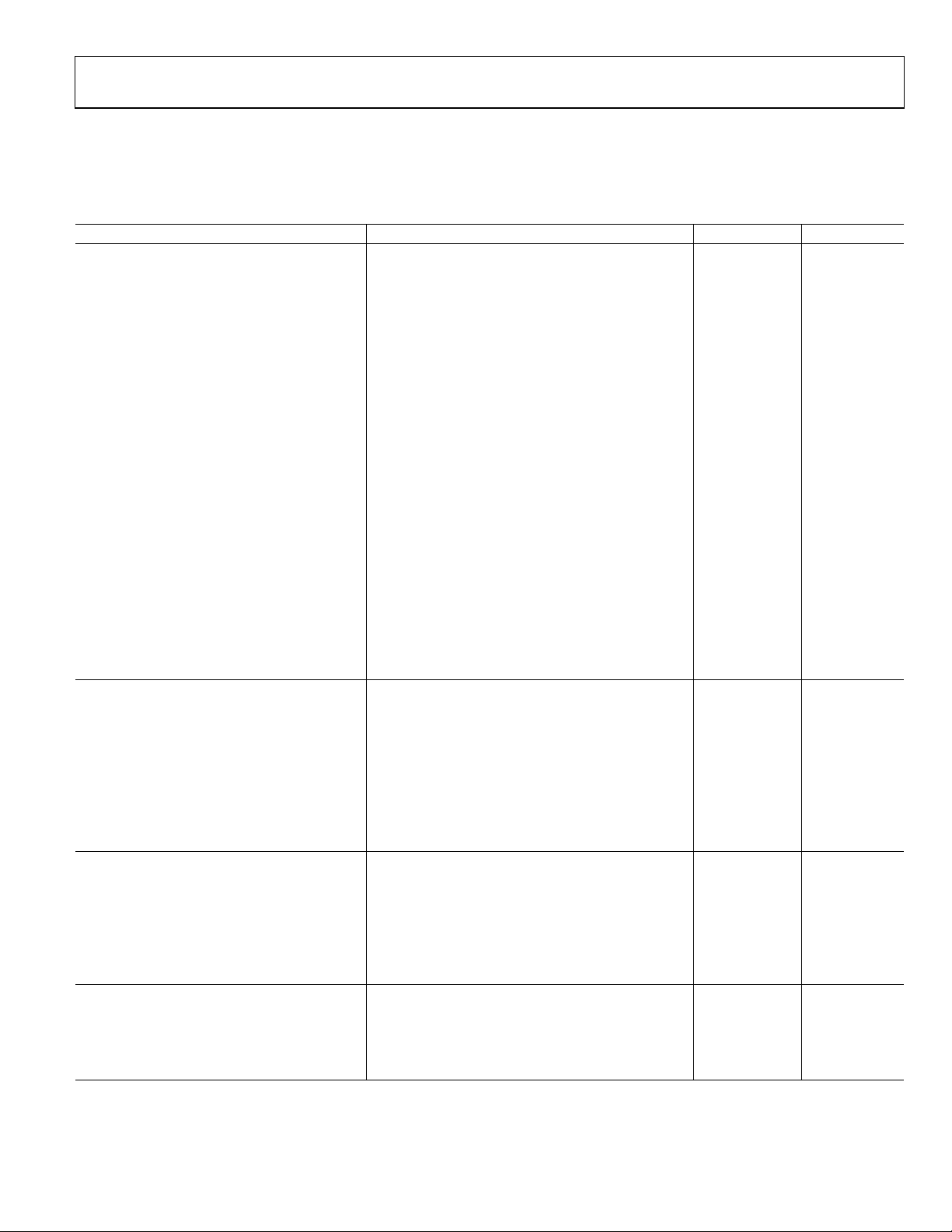

SPECIFICATIONS

AV

= DVDD = V

DD1

using on-chip amplifier with components as shown in Table 1 0, unless otherwise noted.

Table 2.

Parameter Test Conditions/Comments Specification Unit

DYNAMIC PERFORMANCE

Decimate × 256 MCLK = 40 MHz, ODR = 78 kHz, FIN = 1 kHz

Dynamic Range Modulator inputs shorted 119

Signal-to-Noise Ratio (SNR)2 Input amplitude = −0.5 dBFS 112 dB typ

Input amplitude = −60 dB 59 dBc typ

Spurious-Free Dynamic Range (SFDR)

Total Harmonic Distortion (THD)

Decimate × 64 MCLK = 40 MHz, ODR = 312.5 kHz, FIN = 1 kHz

Dynamic Range Modulator inputs shorted 112

Signal-to-Noise Ratio (SNR)2 Input amplitude = −0.5 dBFS 109.5 dB typ

Spurious-Free Dynamic Range (SFDR) Nonharmonic, input amplitude = −6 dB 126 dBc typ

Decimate × 32 MCLK = 40 MHz, ODR = 625 kHz, FIN = 100 kHz

Dynamic Range Modulator inputs shorted 108

Signal-to-Noise Ratio (SNR)2 Input amplitude = −0.5 dBFS 107 dB typ

Spurious-Free Dynamic Range (SFDR)

Total Harmonic Distortion (THD)

DC ACCURACY

Resolution 24 Bits

Differential Nonlinearity Guaranteed monotonic to 24 bits

Integral Nonlinearity 0.00076 % typ

Zero Error 0.014 % typ

Gain Error 0.018 % typ

Zero Error Drift 10 %FS/°C typ

Gain Error Drift 0.0002 %FS/°C typ

DIGITAL FILTER RESPONSE

Decimate × 32

Group Delay MCLK = 40 MHz 47 µs typ

Decimate × 64

Group Delay MCLK = 40 MHz 91.5 µs typ

Decimate × 256

Group Delay MCLK = 40 MHz 358 µs typ

ANALOG INPUT

Differential Input Voltage

V

Input Capacitance At internal buffer inputs 5 pF typ

At modulator inputs 55 pF typ

= 2.5 V; AV

DRIVE

DD2

= AV

DD3

= AV

= 5 V; V

DD4

= 4.096 V; MCLK amplitude = 5 V; TA = 25°C; normal mode,

REF

1

dB min

120.5

dB typ

Nonharmonic, input amplitude = −6 dB 126 dBc typ

Input amplitude = −60 dB 77 dBc typ

Input amplitude = −0.5 dBFS −105 dB typ

Input amplitude = −6 dB −106 dBc typ

Input amplitude = −60 dB −75 dBc typ

dB min

113

dB typ

dB min

109.5

dB typ

Nonharmonic, input amplitude = −6 dB 120 dBc typ

Input amplitude = −0.5 dBFS −105 dB typ

Input amplitude = −6 dB −107 dBc typ

0.02 % max

VIN(+) – VIN(−), V

(+) – Vin(−), V

IN

Rev. A | Page 3 of 32

= 2.5 V ±2 V p-p

REF

= 4.096 V ±3.25 V p-p

REF

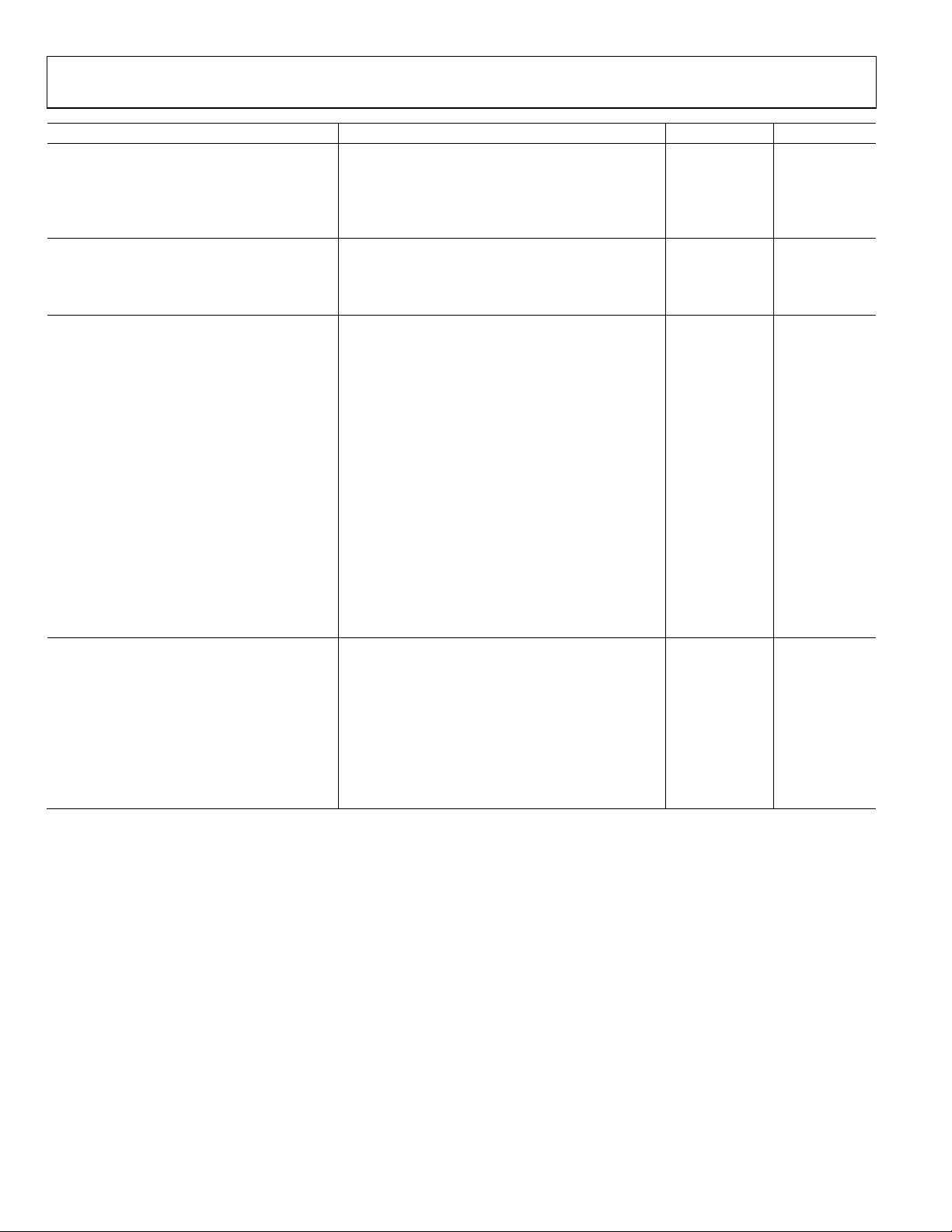

AD7763

Parameter Test Conditions/Comments Specification Unit

REFERENCE INPUT

V

Input Voltage V

REF

V

V

Input DC Leakage Current ±1 µA max

REF

V

Input Capacitance 5 pF max

REF

POWER DISSIPATION

Total Power Dissipation Normal power mode 955.5 mW max

Low power mode 651 mW max

Standby Mode Clock stopped 6.35 mW typ

POWER REQUIREMENTS

AV

(Modulator Supply) ±5% +2.5 V

DD1

AV

(General Supply) ±5% +5 V

DD2

AV

(Differential Amplifier Supply) +3.15/+5.25 V min/max

DD3

AV

(Reference Buffer Supply) +3.15/+5.25 V min/max

DD4

DVDD ±5% +2.5 V

V

+1.65/+2.7 V min/max

DRIVE

Normal Mode

AI

(Modulator) 49/52 mA typ/max

DD1

AI

(General) 40/43 mA typ/max

DD2

AI

(Reference Buffer) AV

DD4

Low Power Mode

AI

(Modulator) 26/28 mA typ/max

DD1

AI

(General) 20/23 mA typ/max

DD2

AI

(Reference Buffer) AV

DD4

AI

(Diff Amp) AV

DD3

DIDD Both modes 56/62 mA typ/max

DIGITAL I/O

MCLK Input Amplitude3 5 V typ

Input Capacitance 7.3 pF typ

Input Leakage Current ±1 A/pin max

Three-State Leakage Current (SDO) ±1 A max

V

0.7 × V

INH

V

0.3 × V

INL

4

V

1.5 V min

OH

VOL 0.1 V max

1

See the Terminology section.

2

SNR specifications in dB are referred to a full-scale input, FS, and tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

3

While the AD7763 can function with an MCLK amplitude of less than 5 V, this is the recommended amplitude to achieve the performance as stated.

4

Tested with a 400 A load current.

= 3.3 V ± 5% +2.5 V max

DD3

= 5 V ± 5% +4.096 V max

DD3

= 5 V 35/37 mA typ/max

DD4

= 5 V 10/11 mA typ/max

DD4

= 5 V, both modes 41/45 mA typ/max

DD3

V min

DRIVE

V max

DRIVE

Rev. A | Page 4 of 32

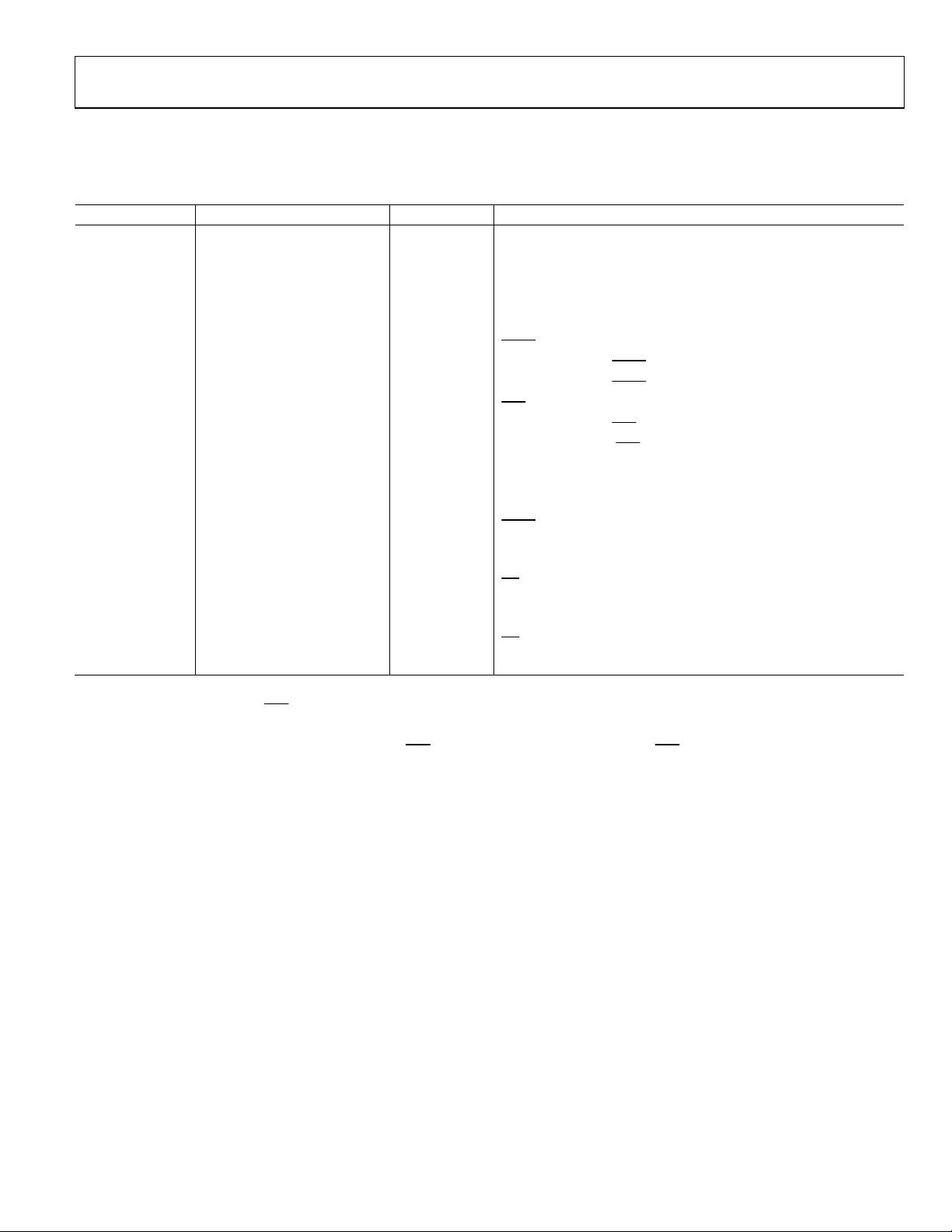

AD7763

TIMING SPECIFICATIONS

AV

= DVDD = V

DD1

Table 3.

Parameter Limit at T

f

1 MHz min Applied master clock frequency

MCLK

40 MHz max

f

500 kHz min Internal modulator clock derived from MCLK

ICLK

20 MHz max

1

t

1 × t

1

1

t

1 × t

2

t3 t

4

t

2 ns typ

3A

4

t

3 ns typ

3B

5

t

32 × t

4

4, 5

t

1 ns typ

4A

4, 5

t

2 ns typ

4B

t5 6.5 ns max Initial data access time

4

t

5 ns max SCO rising edge to SDO valid

6

t7 0.5 × t

t8 16 × t

t9 t

t10 5.5 ns max SDO three-state to SCO rising edge

t11 1 × t

t12 12 ns min SDI setup time

t13 10 ns min SDI hold time

t14 12 ns min

t15 16 × t

1

t

= 1/f

ICLK

2

3

4

5

ICLK.

SCO frequency selected by SCR and

t

= t1 + t2.

SCO

All edges mentioned refer to SCP = 0. Invert SCO edges for SCP = 1.

In decimate × 32 mode, this time specification applies only when

signal is constantly logic low.

= 2.5 V, AV

DRIVE

or 0.5 × t

ICLK

or 0.5 × t

ICLK

3

typ

SCO

MIN

= AV

DD2

, T

Unit Description

MAX

ICLK

ICLK

= AV

DD3

2

typ SCO high period

2

typ SCO low period

= 5 V, TA = 25°C, normal mode, unless otherwise noted.

DD4

DRDY

SCO rising edge to DRDY

SCO rising edge to DRDY

3

typ

SCO

FSO

SCO rising edge to FSO

SCO falling edge to FSO

3

ns min SDO valid after SCO falling edge

SCO

3

typ

SCO

3

typ SDL pulse width

SCO

3

min

SCO

3

typ SDL falling edge to SDL falling edge

SCO

CDIV

pins.

CDIV

= 0 and SCR =1. For all other combinations of

DRDY

low period

FSI

setup time

FSI

low period

falling edge

rising edge

low period

falling edge

rising edge

rising edge to SDL falling edge

CDIV

and SCR in decimate × 32 mode, the FSO

Rev. A | Page 5 of 32

AD7763

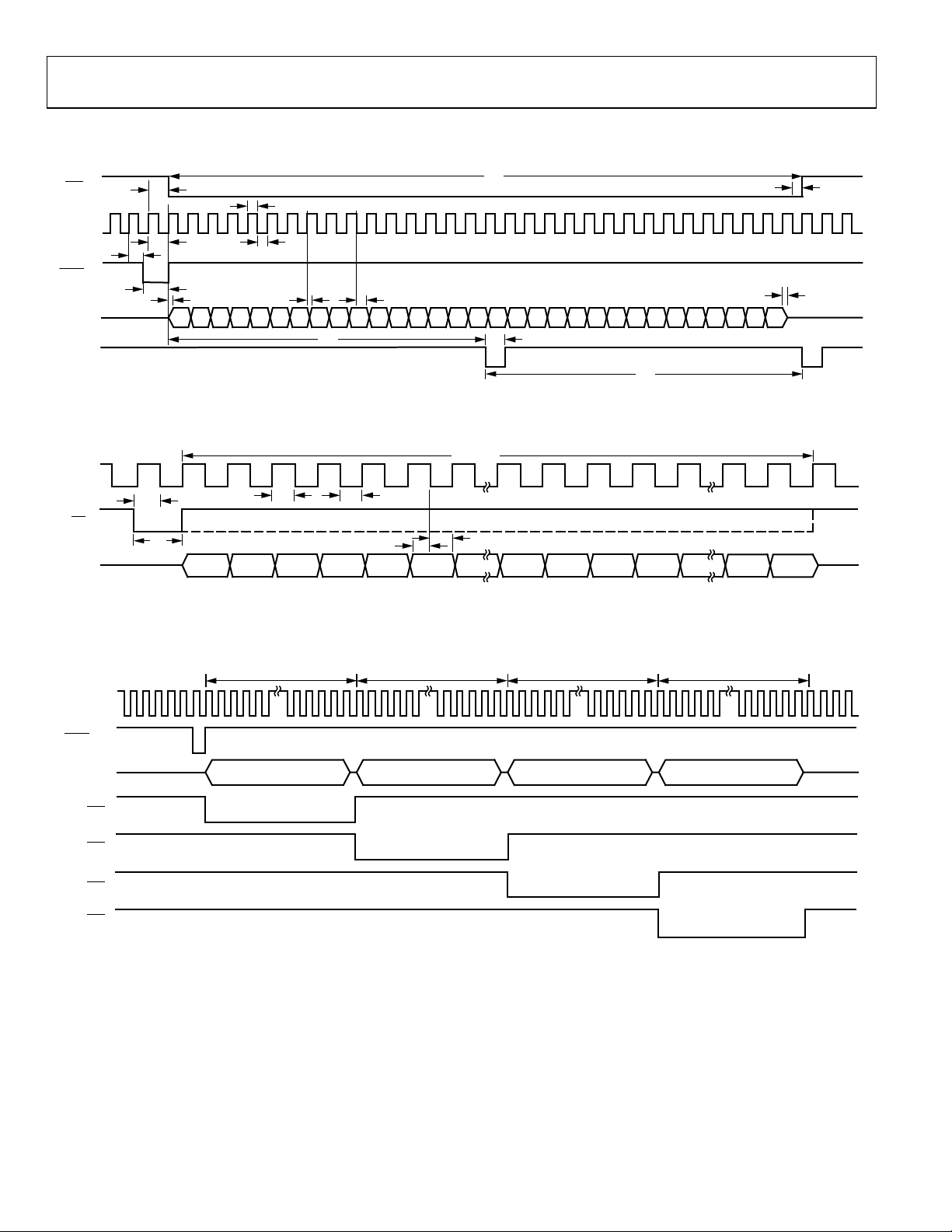

TIMING DIAGRAMS

t

32 ×

4

t

9

t

15

t

SCO

t

13

t

4B

t

10

FSO (O)

SCO (O)

DRDY (O)

SDO (O)

SDL (O)

SCO (O)

FSI (I)

SDI (I)

t

4A

t

t

3A

3B

t

3

t

5

t

1

t

2

t

D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 ST6 ST5 ST4 ST3 ST2 ST1 ST0

6

t

8

t

7

Figure 2. SPI® Interface Serial Read Timing Diagram

t

t

14

t

11

ALL ADR2 ADR1 ADR0 RA11 RA10 RA1 RA0 D15 D14 D1 D0

1

t

2

t

12

05476-002

SCO (O)

DRDY A (O)

SDO (O)

FSO A

FSO B

FSO C

FSO D

Figure 3. Register Write

32 ×

t

SCO

SERIAL DATA F ROM ADC A

32 ×

t

SCO

SERIAL DATA F ROM ADC B S ERIAL DATA FROM ADC C SERI AL DATA FROM ADC D

32 ×

t

SCO

Figure 4. SPI Interface Serial Read Timing with Multiple AD7763 Devices Sharing the Serial Bus

32 ×

05476-003

t

SCO

05476-004

Rev. A | Page 6 of 32

AD7763

ABSOLUTE MAXIMUM RATINGS

= 25°C, unless otherwise noted.

T

A

Table 4.

Parameter Rating

AV

to GND −0.3 V to +3 V

DD1

(AV

, AV

, AV

DD2

DD3

) to GND −0.3 V to +6 V

DD4

DVDD to GND −0.3 V to +3 V

V

to GND −0.3 V to +3 V

DRIVE

V

, V

to GND −0.3 V to +6 V

IN+

IN–

Digital Input Voltage to GND1 −0.3 V to DV

+ 0.3 V

DD

MCLK to MCLKGND −0.3 V to +6 V

V

to GND2 −0.3 V to AV

REF

+ 0.3 V

DD4

AGND to DGND −0.3 V to +0.3 V

Input Current to Any Pin

Except Supplies

3

Operating Temperature Range

±10 mA

−40°C to +85°C

Commercial

Storage Temperature Range −65°C to +150°C

Junction Temperature 150°C

TQFP_EP Exposed Paddle

θJA Thermal Impedance 92.7°C/W

θJC Thermal Impedance 5.1°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

ESD 600 V

1

Absolute maximum voltage on digital inputs is 3.0 V or DVDD + 0.3 V,

whichever is lower.

2

Absolute maximum voltage on V

whichever is lower.

3

Transient currents of up to 200 mA do not cause SCR latch-up.

input is 6.0 V or AV

REF

+ 0.3 V,

DD4

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. A | Page 7 of 32

AD7763

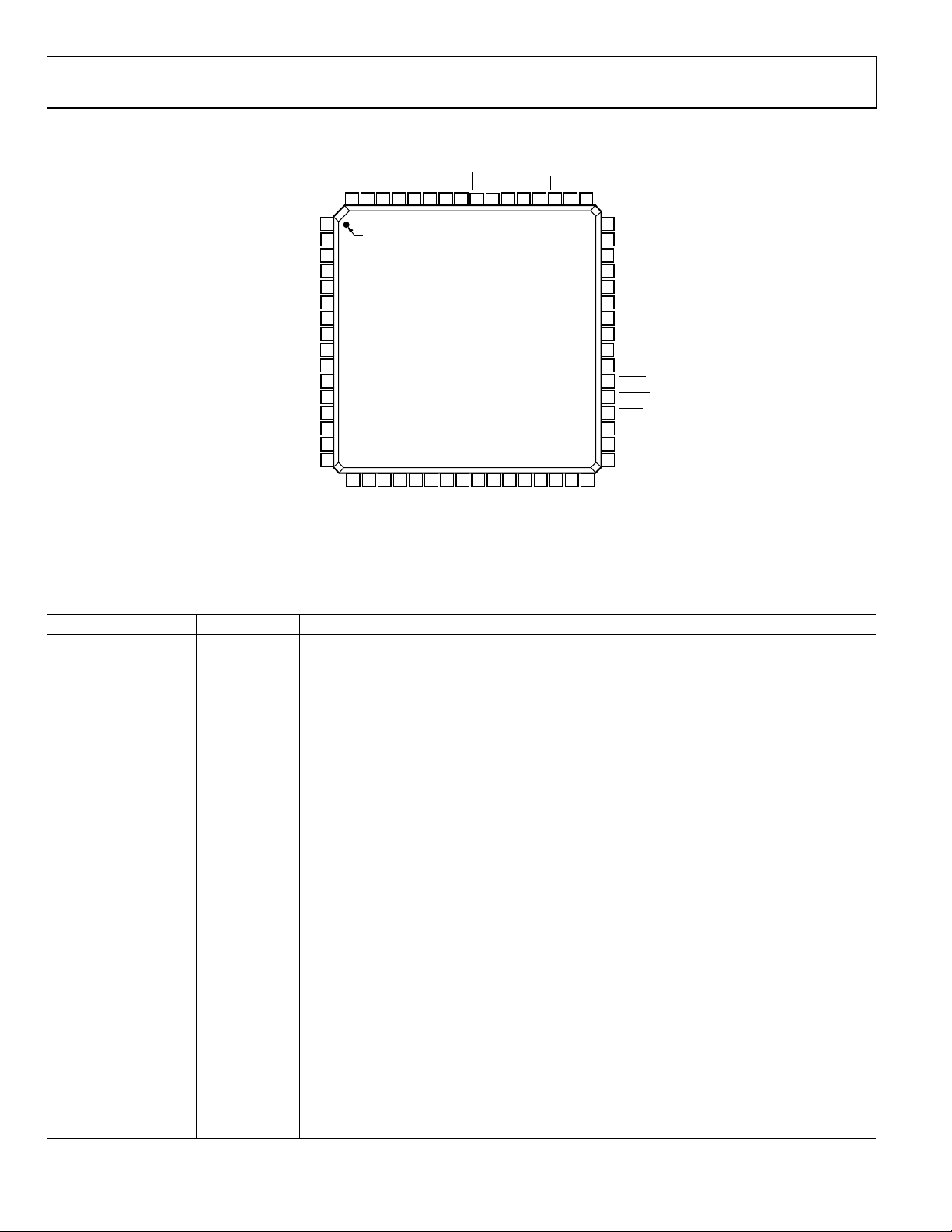

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

S

DRIVE

2

DGND63V

DGND61I

64

1

DGND

MCLKGND

MCLK

AV

DD2

AGND2

AV

DD1

AGND1

DECAPA

REFGND

V

REF+

AGND4

AV

DD4

AGND2

AV

DD2

AV

DD2

AGND2

NOTES

1. THE PADDLE M US T BE CONNECTED DIRECT LY TO T HE GROUND PLANE O F

THE PCB USING MULTIPLE VIAS.

PIN 1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

BIAS

R

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

6, 33 AV

DD1

Power Supply for Modulator, 2.5 V. These pins should be decoupled to AGND1 with 100 nF and

10 µF capacitors on each pin.

4, 14, 15, 27 AV

DD2

Power Supply, 5 V. These pins should be decoupled to AGND2 with 100 nF capacitors on each of

Pin 4, Pin 14, and Pin 15. Pin 27 should be connected to Pin 14 via an 8.2 nH inductor.

24 AV

DD3

Power Supply for Differential Amplifier, 3.3 V to 5 V. This pin should be decoupled to AGND3

with a 100 nF capacitor.

12 AV

DD4

Power Supply for Reference Buffer, 3.3 V to 5 V. This pin should be decoupled to AGND4

with a 10 nF capacitor in series with a 10 Ω resistor.

7, 34 AGND1 Power Supply Ground for Analog Circuitry Powered by AV

5, 13, 16, 18, 28 AGND2 Power Supply Ground for Analog Circuitry Powered by AV

23, 29, 31, 32 AGND3 Power Supply Ground for Analog Circuitry Powered by AV

11 AGND4 Power Supply Ground for Analog Circuitry Powered by AV

9 REFGND Reference Ground. Ground connection for the reference voltage.

41 DVDD

Power Supply for Digital Circuitry and FIR Filter, 2.5 V. This pin should be decoupled to DGND

with a 100 nF capacitor.

44, 63 V

DRIVE

Logic Power Supply Input, 1.8 V to 2.5 V. The voltage supplied at these pins determines

the operating voltage of the logic interface. These pins must be connected together and

tied to the same supply. Each pin should also be decoupled to DGND with a 100 nF capacitor.

1, 35, 42, 43, 53, 57, 59,

DGND Ground Reference for Digital Circuitry.

62, 64

19 VINA+ Positive Input to Differential Amplifier.

20 VINA− Negative Input to Differential Amplifier.

21 V

22 V

A− Negative Output from Differential Amplifier.

OUT

A+ Positive Output from Differential Amplifier.

OUT

25 VIN+ Positive Input to the Modulator.

26 VIN− Negative Input to the Modulator.

10 V

REF+

Reference Input. The input range of this pin is determined by the reference buffer

supply voltage (AV

SCR59DGND58CDIV57DGND56FSO55SCO54SDO53DGND52SDI51FSI50SDL49SCP

62

60

AD7763

TOP VIEW

(Not to S cale)

19

20

21

22

23

24

25

26

A–

A–

A+

A+

IN

IN

V

V

AGND2

OUT

V

V

+

IN

DD3

V

AV

OUT

AGND3

Figure 5. Pin Configuration

). See the Reference Voltage Filtering section for more details.

DD4

48

ADR0

47

ADR1

46

ADR2

45

SH0

44

V

DRIVE

43

DGND

42

DGND

41

DV

DD

40

SH1

39

SH2

38

DRDY

37

RESET

36

SYNC

35

DGND

34

AGND1

33

AV

DD1

27

28

30

AGND229AGND3

31

AGND332AGND3

DECAPB

05476-005

.

DD1

.

DD2

.

DD3

.

DD4

–

IN

DD2

V

AV

Rev. A | Page 8 of 32

AD7763

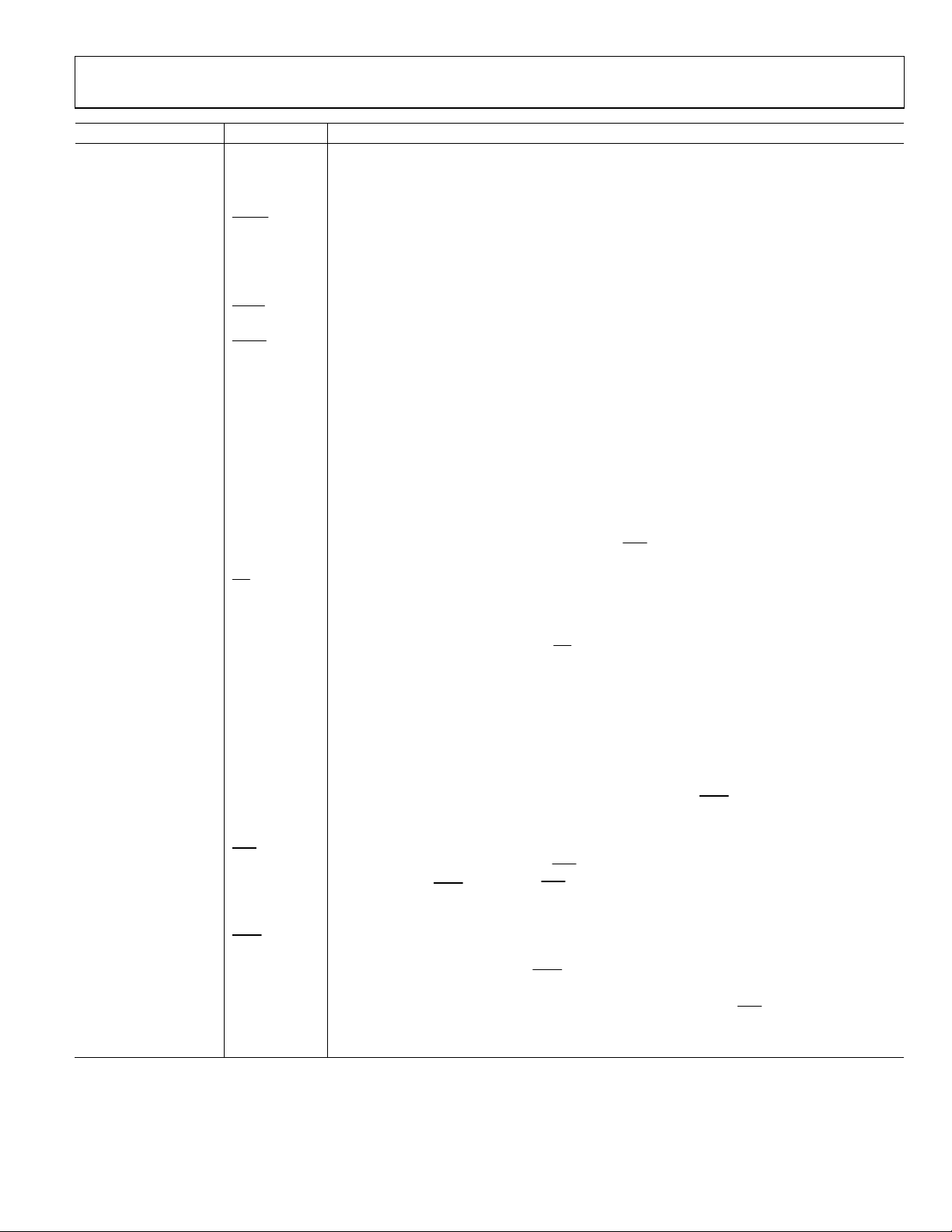

Pin No. Mnemonic Description

8 DECAPA Decoupling Pin. A 100 nF capacitor must be inserted between this pin and AGND1.

30 DECAPB Decoupling Pin. A 33 pF capacitor must be inserted between this pin and AGND3.

17 R

37

3 MCLK

2 MCLKGND Master Clock Ground Sensing Pin.

36

38

39, 40, 45 SH2:0

46 to 48 ADR2:0

49 SCP

50 SDL

51

52 SDI

54 SDO

55 SCO

56

58

60 SCR

61 I2S

BIAS

Bias Current Setting. A resistor must be inserted between this pin and AGND.

See the Bias Resistor Selection section.

RESET

A falling edge on this pin resets all internal digital circuitry. Holding this pin low

keeps the AD7763 in a reset state.

Master Clock Input. A low jitter digital clock must be applied to this pin. The output data rate

depends on the frequency of this clock. See the Clocking the AD7763 section.

SYNC

Synchronization Input. A falling edge on this pin resets the internal filter. This can be used

to synchronize multiple devices in a system.

DRDY

Data Ready Output. Each time new conversion data is available, an active low pulse,

½ ICLK period wide, is produced on this pin. See the AD7763 Interface section.

Share Pins 2:0. For multiple AD7763 devices sharing a common serial bus. Each device is wired

with the binary value that represents the number of devices sharing the serial bus. SH2 is the

MSB. See the Sharing the Serial Bus section.

Address 2:0. Allows multiple AD7763 devices to share a common serial bus. Each device must be

programmed with an individual address using these three pins. See the Sharing the Serial Bus

section.

Serial Clock Polarity. Determines on which edge of SCO the data bits are clocked out and on

which edge they are valid. All timing diagrams are shown with SCP = 0, and all SCO edges

shown should be inverted for SCP = 1.

Serial Data Latch. A pulse is output on this pin after every 16 data bits. The pulse is one SCO

period wide and can be used in conjunction with FSO as an alternative framing method for

serial transfers requiring a framing signal more frequent than every 32 bits.

FSI

Frame Sync In. The status of this pin is checked on the falling edge of SCO. If this pin is low, then

the first data bit is latched in on the next SCO falling edge when SCP = 0 or on the rising edge of

SCO if SCP = 1.

Serial Data In. The first data bit (MSB) must be valid on the next SCO falling edge when SCP = 0

(or SCO rising edge SCP = 1) after the FSI event has been latched. Each write requires 32 bits: the

ALL bit, 3 address bits, and 12 register address bits, followed by the remaining 16 bits of data to

be written to the device.

Serial Data Out. Address, status, and data bits are clocked out on this line during each serial

transfer.

If SCP = 0, each bit is clocked out on an SCO rising edge and is valid on the falling edge. When

2

S pin is set to logic high, this pin outputs the signal defined as SD in the I2S bus

the I

specification. See the Reading Data Using the I

2

S Interface section for details.

Serial Clock Out. This clock signal is derived from the internal ICLK signal. The frequency of SCO

is equal to either ICLK or ICLK/2, depending on the state of the CDIV

2

S pin is logic high, this pin outputs the signal defined as

Reading Data Using the I2S Interface

FSO

occurs in decimate × 32 mode, where, for certain

FSO

signal is constantly logic low. See the

Reading Data Using the I2S Interface

FSO

AD7763 Interface

SCK by the I

Frame Sync Out. This signal frames the serial data output and is 32 SCO periods wide. The

section). When the I

2

S bus specification. See the section.

exception to the framing behavior of

combinations of CDIV

Using the SPI Interface

defined as WS in the I

Clock Divider. This pin is used to select the ratio of MCLK to ICLK. See the AD7763 Interface

CDIV

and SCR, the

section. When the I2S pin is set to logic high, this pin outputs the signal

2

S bus specification. See the section.

and SCR pins (see the

Reading Data

section.

Serial Clock Rate. This pin and the CDIV

2

S Select. A Logic 1 on this pin changes the serial data-out mode from SPI to I2S. The SDO pin

I

outputs as the SD signal, the SCO pin outputs the SCK signal, and the

signal. When writing to the AD7763, the I

See the section for further details. Reading Data Using the I

pin program the SCO frequency (see ). Table 7

2

2

S pin is set to logic low and the SPI interface is used.

S Interface

FSO

pin outputs the WS

Rev. A | Page 9 of 32

AD7763

TERMINOLOGY

Signal-to-Noise Ratio (SNR) Integral Nonlinearity (INL)

The ratio of the rms value of the actual input signal to the rms

sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is

expressed in decibels.

The ratio of the rms sum of harmonics to the fundamental. For

the AD7763, it is defined as

22222

VVVVV

++++

54

THD

()

log20dB

=

32

V

1

6

where:

V

is the rms amplitude of the fundamental.

1

V

, V3, V4, V5, and V6 are the rms amplitudes of the second

2

to the sixth harmonic.

Nonharmonic Spurious-Free Dynamic Range (SFDR)

The ratio of the rms signal amplitude to the rms value of the

peak spurious spectral component, excluding harmonics.

Dynamic Range

The ratio of the rms value of the full scale to the rms noise

measured with the inputs shorted together. The value for

dynamic range is expressed in decibels.

The maximum deviation from a straight line passing through

the endpoints of the ADC transfer function.

Differential Nonlinearity (DNL)

The difference between the measured and the ideal 1 LSB

change between any two adjacent codes in the ADC.

Total Harmonic Distortion (THD)

Zero Error

The difference between the ideal midscale input voltage (0 V)

and the actual voltage producing the midscale output code.

Zero Error Drift

The change in the actual zero error value due to a temperature

change of 1°C. It is expressed as a percentage of full scale at room

temperature.

Gain Error

The first transition (from 100…000 to 100…001) should occur

for an analog voltage 1/2 LSB above the nominal negative full

scale. The last transition (from 011…110 to 011…111) should

occur for an analog voltage 1 1/2 LSB below the nominal full

scale. The gain error is the deviation of the difference between

the actual level of the last transition and the actual level of the

first transition, from the difference between the ideal levels.

Gain Error Drift

The change in the actual gain error value due to a temperature

change of 1°C. It is expressed as a percentage of full scale at

room temperature.

Rev. A | Page 10 of 32

AD7763

TYPICAL PERFORMANCE CHARACTERISTICS

AV

= DVDD = V

DD1

are generated from 65536 samples using a 7-term Blackman-Harris window.

0

= 2.5 V, AV

DRIVE

DD2

= AV

DD3

= AV

= 5 V, V

DD4

= 4.096 V, TA = 25°C, normal mode, unless otherwise noted. All FFTs

REF

0

–50

–100

–150

AMPLITUDE ( dB)

–200

–250

0 5000 1500010000 30000 350002500020000

FREQUENCY (Hz)

Figure 6. Normal Mode FFT, 1 kHz, −0.5 dB Input Tone, 256× Decimation

0

–50

–100

–150

AMPLITUDE (dB)

–200

–50

–100

–150

AMPLITUDE ( dB)

–200

05476-007

–250

0 5000 1500010000 30000 350002500020000

FREQUENCY (Hz)

05476-006

Figure 9. Low Power FFT, 1 kHz, −0.5 dB Input Tone, 256× Decimation

0

–50

–100

–150

AMPLITUDE (dB)

–200

–250

0 5000 1500010000 30000 350002500020000

FREQUENCY (Hz)

Figure 7. Normal Mode FFT, 1 kHz, −0.6 dB Input Tone, 256× Decimation

0

–50

–100

–150

AMPLITUDE (dB)

–200

–250

0 5000 1500010000 30000 350002500020000

FREQUENCY (Hz)

Figure 8. Normal Mode FFT, 1 kHz, −60 dB Input Tone, 256× Decimation

Rev. A | Page 11 of 32

05476-011

–250

0 5000 1500010000 30000 350002500020000

FREQUENCY (Hz)

05476-010

Figure 10. Low Power FFT, 1 kHz, −6 dB Input Tone, 256× Decimation

0

–50

–100

–150

AMPLITUDE (dB)

–200

05476-032

–250

0 5000 1500010000 30000 350002500020000

FREQUENCY (Hz)

05476-031

Figure 11. Low Power FFT, 1 kHz, −60 dB Input Tone, 256× Decimation

AD7763

0

–50

–100

–150

AMPLITUDE (dB)

–200

–250

0 50000 150000100000 300000250000200000

FREQUENCY (Hz)

Figure 12. Normal Mode FFT, 100 kHz, −0.5 dB Input Tone, 32× Decimation

0

–50

–100

–150

AMPLITUDE (dB)

0

–50

–100

–150

AMPLITUDE (dB)

–200

05476-009

–250

0 50000 150000100000 300000250000200000

FREQUENCY (Hz)

05476-008

Figure 15. Low Power FFT, 100 kHz, −0.5 dB Input Tone, 32× Decimation

0

–50

–100

–150

AMPLITUDE (dB)

–200

–250

0 50000 150000100000 300000250000200000

FREQUENCY (Hz)

05476-030

Figure 13. Normal Mode FFT, 100 kHz, −6 dB Input Tone, 32× Decimation

120

118

116

114

112

SNR (dBFS)

110

108

106

064

DECIMATIO N RAT E (×)

–60dB

–6dB

–0.5dB

192128 256

05476-036

Figure 14. Normal Mode SNR vs. Decimation Rate, 1 kHz Input Tone

–200

–250

0 50000 150000100000 300000250000200000

FREQUENCY (Hz)

Figure 16. Low Power FFT, 100 kHz, −6 dB Input Tone, 32× Decimation

116

–60dB

114

112

110

SNR (dBFS)

108

106

104

064

DECIMATIO N RAT E (×)

–6dB

–0.5dB

192128 256

Figure 17. Low Power SNR vs. Decimation Rate, 1 kHz Input Tone

05476-029

05476-033

Rev. A | Page 12 of 32

AD7763

4500

4000

3500

3000

2500

2000

OCCURENCE

1500

1000

500

0

8385341 838540183853918385381838537183853618385351

24-BIT CODE

05476-035

Figure 18. Normal Mode, 24-Bit Histogram, 256× Decimation Figure 21. Low Power 24-Bit Histogram, 256× Decimation

0.0010

6000

5000

4000

3000

OCCURENCE

2000

1000

0

8383091 83831918383171838315183831318383111

0.0015

+85

05476-034

24-BIT CODE

°

C

0.0005

INL (%)

–0.0005

–0.0010

+85°C

+25°C

0

0 16777216

–40°C

4194304 8388608 12582912

24-BIT CODE

Figure 19. 24-Bit INL, Normal Power Mode Figure 22. 24-Bit INL, Low Power Mode

0.65

0.4

0.2

0

DNL (LSB)

–0.2

–0.4

0.0010

0.0005

INL (%)

–0.0005

05476-037

–0.0010

°

C

+25

0

–40

°

C

0 16777216

4194304 8388608 12582912

24-BIT CODE

05476-038

–0.6

0 16777216

4194304 8388608 12582912

24-BIT CODE

05476-039

Figure 20. 24-Bit DNL

Rev. A | Page 13 of 32

AD7763

THEORY OF OPERATION

The AD7763 employs a Σ- conversion technique to convert

the analog input into an equivalent digital word. The modulator

samples the input waveform and outputs an equivalent digital

word to the digital filter at a rate equal to ICLK.

The second filter allows the decimation rate to be chosen from

8× to 32×. The third filter has a fixed decimation rate of 2x, is

user programmable, and has a default configuration (see the

Programmable FIR Filter section). This filter can be bypassed.

Due to the high oversampling rate, which spreads the quanti-

f

zation noise from 0 to

, the noise energy contained in the

ICLK

band of interest is reduced (see Figure 23). To further reduce

quantization noise, a high order modulator is employed to shape

the noise spectrum; thus, most of the noise energy is shifted out

of the band of interest (see Figure 24).

The digital filtering that follows the modulator removes the

large out-of-band quantization noise (see Figure 25), while

f

also reducing the data rate from

f

/32 or less at the output of the filter, depending on the

to

ICLK

at the input of the filter

ICLK

decimation rate used.

Digital filtering has certain advantages over analog filtering.

It does not introduce significant noise or distortion and can

be made perfectly linear phase.

The AD7763 employs three finite impulse response (FIR) filters

in series. By using different combinations of decimation ratios

and filter selection, data can be obtained from the AD7763 at

four different data rates. The first filter receives data from the

modulator at ICLK

data at (ICLK/4)

MHz, where it is decimated × 4 to output

MHz.

Table 6 shows some characteristics of the default filter. The group

delay of the filter is defined as the delay to the center of the

impulse response and is equal to the computation plus filter

delays. The delay until valid data is available (the DVALID status bit

is set) is equal to 2× the filter delay plus the computation delay.

QUANTIZATION NOISE

f

/2

ICLK

f

f

ICLK

ICLK

05476-024

/2

05476-025

/2

05476-012

BAND OF INTERE S T

Figure 23. Σ-Δ ADC, Quantization Noise

NOISE SHAPI NG

BAND OF INTERE S T

Figure 24. Σ-Δ ADC, Noise Shaping

DIGITAL FILTER CUTOFF FREQ UE NCY

BAND OF INTERE S T

Figure 25. Σ-Δ ADC, Digital Filter Cutoff Frequency

Table 6. Configuration With Default Filter

ICLK

Frequency

Filter 1 Filter

2 Filter 3 Data State

Computation

Delay

Filter

Delay

Pass Band

Bandwidth

Output Data Rate

(ODR)

20 MHz 4× 4× 2× Fully filtered 1.775 µs 44.4 µs 250 kHz 625 kHz

20 MHz 4× 8× Bypassed

Partially

2.6 µs 10.8 µs 140.625 kHz

625 kHz

filtered

20 MHz 4× 8× 2× Fully filtered 2.25 µs 87.6 µs 125 kHz

20 MHz 4× 16× Bypassed

Partially

4.175 µs 20.4 µs 70.3125 kHz

312.5 kHz

312.5 kHz

filtered

20 MHz 4× 16× 2× Fully filtered 3.1 µs 174 µs 62.5 kHz

20 MHz 4× 32× Bypassed

Partially

7.325 µs 39.6 µs 35.156 kHz

156.25 kHz

156.25 kHz

filtered

20 MHz 4× 32× 2× Fully filtered 4.65 µs 346.8 µs 31.25 kHz

12.288 MHz 4× 8× 2× Fully filtered 3.66 µs 142.6 µs 76.8 kHz

12.288 MHz 4× 16× 2× Fully filtered 5.05 µs 283.2 µs 38.4 kHz

12.288 MHz 4× 32× Bypassed

Partially

11.92 µs 64.45 µs 21.6 kHz

78.125 kHz

192 kHz

96 kHz

96 kHz

filtered

12.288 MHz 4× 32× 2× Fully filtered 7.57 µs 564.5 µs 19.2 kHz 48 kHz

Rev. A | Page 14 of 32

AD7763

AD7763 INTERFACE

READING DATA USING THE SPI INTERFACE

The timing diagram in Figure 2 shows how the AD7763 transmits

its conversion results using the SPI-compatible serial interface.

The data being read from the AD7763 is clocked out using the

serial clock output, SCO. The SCO frequency is dependent on

the state of the serial clock output rate pin, SCR, and the clock

divider mode chosen by the state of the clock divider pin,

(see the section). shows both the

Clocking the AD7763 Tabl e 7

CDIV

SCO frequency and the ICLK frequency for the AD7763, resulting

from the states of both the

CDIV

and SCR pins.

Table 7. SCO Frequency

Clock Divide

Mode

Divide by 1 1 0 MCLK MCLK

1 MCLK MCLK

Divide by 2 0 0 MCLK/2 MCLK/2

1 MCLK1 MCLK/2

1

In decimate × 32 mode, when

32 SCO clock cycles, as shown in . For all other combinations of Figure 2

and SCR in decimate × 32 mode,

CDIV

SCR

CDIV

SCO

Frequency

= 0 and SCR = 1,

FSO

is continuously low.

ICLK

Frequency

FSO

pulses low for

CDIV

An active low pulse of one SCO period on the data-ready output,

DRDY

, indicates a new conversion result is available at the

AD7763 serial data output, SDO.

Each bit of the new conversion result is clocked onto the SDO

line on the rising SCO edge and is valid on the falling SCO edge

(for SCP = 0). The conversion result spans 32 SCO clock cycles

and consists of 24 data bits in twos complement form, followed

by 7 status bits.

D6 D5 D4 D3 D2 D1 D0

ADR2 ADR1 ADR0 DVALID OVR LPWR FILTER_OK

The conversion result output on the SDO line is framed by the

frame synchronization output,

32 SCO cycles following the rising edge of the

, which is sent logic low for

FSO

DRDY

signal.

Note that the SDO line is in three-state for one clock cycle

before the

signal returns to logic high, which means that

FSO

only 31 actual data bits are output in each conversion.

The first three status bits, ADR[2:0], are the device address bits.

The DVALID bit is asserted when the data being clocked out on

the SDO line is valid. Table 19 contains descriptions of the other

status bits: OVR, LPWR, and FILTER_OK.

There is an exception to the behavior of

operates in decimate × 32 mode (see Endnote 1 of ). If SCR

CDIV

and

are chosen so that the SCO frequency output has the

when the AD7763

FSO

Table 7

capability to clock through only 32 SCO cycles before the MSB

of the next conversion result is output, then

stays logic low

FSO

continuously.

The AD7763 also features a serial data latch output, SDL, which

outputs a pulse every 16 data bits. The SDL output offers an

alternative framing signal for serial transfers, which require

a framing signal more frequent than every 32 bits.

SYNCHRONIZATION

SYNC

The

input to the AD7763 provides a synchronization

function that allows the user to begin gathering samples of the

analog front-end input from a known point in time.

SYNC

The

the same master clock and using the same

function allows multiple AD7763s, operated from

SYNC

signal, to be

synchronized so that each ADC simultaneously updates its

output register.

SYNC

Using a common

signal to all AD7763 devices in a

system allows synchronization to occur. On the falling edge of

SYNC

the

signal, the digital filter sequencer is reset to 0. The

filter is held in reset state until a rising edge of the SCO senses

SYNC

high. Thus, to perform a synchronization of devices, a

SYNC

pulse of a minimum of 2.5 ICLK cycles in length can be

applied, synchronous to the falling edge of SCO. On the first

SYNC

rising edge of SCO after

goes logic high, the filter is taken

out of reset, and the multiple parts gather input samples

synchronously.

Following a

SYNC

, the digital filter needs time to settle before

valid data can be read from the AD7763. The user knows there

is valid data on the SDO line by checking the DVALID status bit

(see D3 in the status bits listing) that is output with each conversion

result. The time from the rising edge of SYNC until the DVALID

bit is asserted is dependent on the filter configuration used. See the

Theory of Operation Table 6

section and the figures listed in for

details on calculating the time until DVALID is asserted.

SHARING THE SERIAL BUS

The AD7763 functionality allows up to eight devices to share

the same serial bus, SDO, depending on the decimation rate

that is chosen.

Table 8 details the maximum number of devices that can share

the same SDO line for each decimation rate (×32, ×64, ×128,

×256).

Table 8. Maximum Number of Devices Sharing SDO

Maximum Number of

Devices Sharing SDO

Decimation Rate

SCO

(MHz)

40

20

×32 ×64 ×128 ×256

2

N/A 4 2 8 4

8

8

Rev. A | Page 15 of 32

AD7763

The Share Pins SH[2:0] of all the devices sharing the serial bus

must be programmed for the correct number of devices that are

sharing the serial bus. A binary value of N − 1 should be applied

to the SH[2:0] bits, where N equals the number of devices in the

chain. For example if there are 4 devices in the chain set SH[2:0]

= 011.

Using the Address Pins ADR[2:0], all devices that share the

serial bus are assigned binary addresses from 000 to 111

(depending on the number of devices in the share scheme). The

address assigned to each device must not have a value greater

than the number of devices sharing the serial bus. Thus,

ADR[2:0] ≤ SH[2:0]. This applies to all the devices that share the

serial bus. Note also that each of the devices in the share scheme

must have a different individual address.

WRITING TO THE AD7763

Figure 3 shows the AD7763 write operation. The serial writing

operation is synchronous to the SCO signal. The status of the

FSI

frame sync input,

signal. If the

FSI

the next SCO falling edge.

DEVICE

ADDRESS

000

011

MCLK

, is checked on the falling edge of the SCO

line is low, then the first data is latched in on

AD7763

(000)

ADR[2:0] FSO FS O A

A

SH[2:0]SH[2:0]

SDO

DRDY DRDY

MCLK

For the device in the share scheme with an address of 000, the

SDO line comes out of three-state on the first rising edge of SCO

DRDY

after the

pulse and returns to three-state 5.5 ns before

the 31st SCO rising edge. For the next device sharing the serial

bus, Address 001, the SDO line comes out of three-state on the

33rd SCO rising edge (that is, the first SCO rising edge of the

next conversion output cycle). Thus, the SDO line goes into tristate for one SCO cycle in between data being clocked onto SDO

by two different devices that share the SDO line. This means

that a bus contention issue is avoided. This pattern of behavior

continues for the rest of the devices sharing the serial bus.

Each AD7763 device sharing the serial bus outputs its own

FSO

signal.

Figure 26 shows an example of four devices sharing the same

serial bus. All the devices in the share chain shown in Figure 26

operate in decimate × 64 mode (selected by writing to Control

Register 1—Address 0x001) and use a maximum SCO signal of

40 MHz (see the Clocking the AD7763 section).

The Share Pins SH[2:0] of all the devices shown in Figure 26

are set to 011, corresponding to the four devices that are in the

share configuration. Each AD7763 is hardwired with a different

binary address ranging from 000 to 011, using the Address Pins

ADR[2:0].

The timing diagram for the share configuration shown in

Figure 26 is detailed in Figure 4. Device A outputs its 32-bit

conversion result on the SDO line during the first 32 SCO

cycles (as per the format shown in the Reading Data Using the

SPI Interface s

re

sult during the next 32 SCO cycles, and so on for Device C

ection). Device B then outputs its conversion

and Device D. Note the way in which the SDO line is threestated, separating data from each of the devices sharing the

DRDY

serial bus. The provision of two framing signals,

FSO

, ensures that the AD7763 offers flexible data output

and

framing options, which are further enhanced by the availability

of the SDL output. The user can select the framing output that

best suits the application.

DEVICE

ADDRESS

001

DEVICE

ADDRESS

010

DEVICE

ADDRESS

011

Figure 26. Four AD7763 Devices Sharing the Serial Bus

The active edge of the

AD7763

(001)

ADR[2:0] FSO FS O B

B

SH[2:0] SDO

MCLK

SHARED

SERIAL DAT A OUTPUT

AD7763

(010)

ADR[2:0] FSO FS O C

C

SH[2:0] SDO

MCLK

AD7763

(011)

ADR[2:0] FSO FS O D

D

SH[2:0] SDO

MCLK

FSI

signal should be set to occur at a position

(SDO)

05476-013

when the SCO signal is high or low and which also allows setup

and hold time from the SCO falling edge to be met. The width

FSI

of the

periods wide. A second or subsequent

signal can be set to between 1 SCO period and 32 SCO

FSI

falling edge, which

occurs before 32 SCO periods have elapsed, is ignored.

Figure 3 also shows the format for the serial data written to the

AD7763. A write operation requires 32 bits. The first 16 bits select

the device and register address for which the data written is

intended. The second 16 bits contain the data for the selected

register. When using multiple devices that share the same serial bus,

Rev. A | Page 16 of 32

AD7763

FSO

all

and SDI pins can be tied together and each device written

to individually by setting the appropriate address bits in the serial

32-bit word. The exception to this is when all devices can be written

to at the same time by setting the ALL bit to logic high.

Thus, if this bit is set to logic high, every device on the serial

bus accepts the data written, regardless of the address bits. This

feature is particularly attractive if, for example, four devices are

being configured with the same user-defined filter. Instead of

having to download the filter configuration four times, only one

write is required. See the Downloading a User-Defined Filter

section for further details.

Writing to AD7763 is allowed at any time, even while reading a

conversion result. Note that after writing to the devices, valid

data is not output until after the settling time for the filter has

elapsed. The DVALID status bit is asserted at this point to

indicate that the filter has settled and that valid data is available

at the output.

READING STATUS AND OTHER REGISTERS

The AD7763 features a number of programmable registers. To

read back the contents of these registers or the status register,

the user must first write to the control register of the device,

setting a bit corresponding to the register to be read. The next

read operation then outputs the contents of the selected register

instead of a conversion result.

To ensure that the next read cycle contains the contents of the

register that has been written to, the write operation to the register

in question must be completed a minimum of 8 × t

the falling edge of

read cycle.

More information on the relevant bits in the control register is

provided in the Registers section.

DRDY

, which indicates the start of the next

SCO

before

Rev. A | Page 17 of 32

AD7763

READING DATA USING THE I2S INTERFACE

The AD7763 has the capability of operating using an I2S

interface. The interface is functional only for the output of

stereo data and does not apply to writing to control registers,

programming coefficients for the digital filter, or the reading of

any information contained in the AD7763 onboard registers.

All of these operations must be undertaken using the normal

serial interface.

2

S interface operates using two AD7763 devices. The pins

The I

shown in Tabl e 9 are used as the output pins for the SCK (serial

clock), SD (serial data), and WS (word select) signals for the I

interface.

Table 9.

SPI Pins I2S Signals

FSO

WS

SDO SD

SCO SCK

To enable the I2S interface, the I2S pin is set to logic high. The

Share Pins SH[2:0] of both AD7763 devices that use the I

interface are set to 001. The Address Pins ADR[2:0] of the two

devices must also be set to 000 and 001, respectively.

The WS and SCK signals that are used for the interface can be

taken from either AD7763 device. Note that the device that is

assigned Address 000 is defined as the left channel, and its data

is output on the SD line when WS is logic low.

The WS and SCK signals can be taken from the appropriate

2

pins on either of the AD7763 devices using the I

S interface.

The SD pins of both devices must be connected together, as

shown in Figure 27.

Data is clocked out on the SD line in accordance with Figure 28.

Because Device A is assigned Address 000, it is defined as the

left channel. The 32-bit conversion result from the left channel

is clocked out when WS is logic low, with the MSB being clocked

out first. Each 32-bit result consists of 24 data bits in twos

complement format, followed by eight status bits, as shown in

the following bit map.

D7 D6 D5 D4 D3 D2 D1

DVALID OVR UFILTER LPWR FILTER_OK ADR0 0

2

S

2

S

D0

ThreeState

LEFT C HANN E L

AD7763

DEVICE

ADDRESS

000

1

DEVICE

ADDRESS

001

001

1

SH[2:0]

MCLK

Figure 27. Two AD7763 Devices Operating Using the I

(000)

ADR[2:0] FSO

A

I2S

SH[2:0]

SH[2:0] SDO

I2S

ADR[2:0]

RIGHT CHANNE L

MCLK

MCLK

B

AD7763

(001)

SCO

SDO

WS

SCK

SD

2

S Interface

3-WIRE

2

I

S INTERFACE

Conversion results from Device B, assigned Address 001, are

clocked out on the SD line when WS is logic high. The SD line

goes into three-state on the falling edge of the 32nd SCK after

the falling edge of WS (left channel data) and also on the falling

edge of the 32nd SCK after the rising edge of WS (right channel

data). This permits swapping of the SD bus between the left and

right channel devices without contention.

2

In decimate × 32 mode the I

CDIV

when

= 0 and SCR = 1. The interface operates for all

combinations of SCR and

S interface is operational only

CDIV

in all other modes of

decimation.

DRDY

The

pulse still operates as in the normal serial SPI-type

interface, pulsing low immediately prior to the falling edge of

WS but having no meaning in the I

2

S interface specification.

05476-026

SCK A (O)

WS A (O)

SD (O)

THREE-

STATE

RIGHT CHANNEL

DEVICE B

(WORD n – 1)

D23

ST1ST2

LEFT CHANNE L

DEVICE A

(WORD n)

Figure 28. Timing Diagram for I

Rev. A | Page 18 of 32

THREESTATE

D23D21D22

2

S Interface

D22

RIGHT CHANNEL

DEVICE B

(WORD n + 1)

THREE-

ST1ST2D21

STATE

LEFT CHANNE L

DEVICE A

(WORD n + 2)

05476-027

AD7763

CLOCKING THE AD7763

The AD7763 requires an external, low jitter clock source. This

signal is applied to the MCLK pin, and the MCLKGND pin is

used to sense the ground from the clock source. An internal

clock signal (ICLK) is derived from the MCLK input signal.

The ICLK controls the internal operations of the AD7763. The

maximum ICLK frequency is 20 MHz, but due to an internal

clock divider, a range of MCLK frequencies can be used. There

are two ways to generate the ICLK:

ICLK = MCLK (

ICLK = MCLK/2 (

CDIV

CDIV

= 1)

= 0)

This option is pin selectable (Pin 58). On power-up, the default

is ICLK = MCLK/2 to ensure that the part can handle the maximum MCLK frequency of 40 MHz. For output data rates equal to

those used in audio systems, a 12.288 MHz ICLK frequency can

be used. As shown in Tabl e 6 , output data rates of 192 kHz, 96 kHz,

and 48 kHz are achievable with this ICLK frequency. As mentioned

previously, this ICLK frequency can be derived from different

MCLK frequencies.

The MCLK jitter requirements depend on a number of factors

and are determined by

f

OSR

IN

)dB(

SNR

20

102

××π×

=

t

)(

rmsj

EXAMPLE 2

Following is a second example from Tab le 6, where:

ODR = 48 kHz.

f

= 12.288 MHz.

ICLK

f

(maximum) = 19.2 kHz.

IN

SNR = 120 dB.

=

t

rmsj

)(

256

=

63

10102.192

×××π×

The input amplitude also has an effect on these jitter figures.

If, for example, the input level is 3 dB below full scale, the allowable

jitter is increased by a factor of √2, increasing the first example

to 2.53 ps rms. This happens when the maximum slew rate is

decreased by a reduction in amplitude. Figure 29 and Figure 30

illustrate this point, showing the maximum slew rate of a sine

wave of the same frequency but with different amplitudes.

1.0

0.5

0

ps133

Where:

f

OSR = oversampling ratio =

f

= maximum input frequency.

IN

ICLK

ODR

.

SNR(dB) = target SNR.

EXAMPLE 1

This example is taken from Table 6, where:

ODR = 625 kHz.

f

= 20 MHz.

ICLK

f

(maximum) = 250 kHz.

IN

SNR = 108 dB.

=

t

rmsj

)(

32

π

=

63

10102502

××××

This is the maximum allowable clock jitter for a full-scale,

250 kHz input tone with the given ICLK and output data rate.

ps6.3

–0.5

–1.0

Figure 29. Maximum Slew Rate of Sine Wave with Amplitude of 2 V p-p

1.0

0.5

0

–0.5

–1.0

Figure 30. Maximum Slew Rate of Same Frequency Sine Wave

with Amplitude of 1 V p-p

05476-014

05476-015

Rev. A | Page 19 of 32

AD7763

–

+

V0V–

V

+

V0V–

V

–

V

DRIVING THE AD7763

The AD7763 has an on-chip differential amplifier that operates

with a supply voltage (AV

) from 3.15 V to 5.25 V. For a 4.096 V

DD3

reference, the supply voltage must be 5 V.

To achieve the specified performance in normal mode, the

differential amplifier should be configured as a first-order

antialias filter, as shown in Figure 31. Any additional filtering

should be carried out in previous stages using low noise, high

performance op amps, such as the AD8021.

Suitable component values for the first-order filter are shown in

Table 10. The values in Table 1 0 yield a 10 dB attenuation at the

first alias point of 19 MHz.

C

FB

R

FB

R

IN

A

C

B

R

IN

A1

S

R

FB

C

FB

R

M

V

IN

R

M

V

+

IN

5476-016

Figure 31. Differential Amplifier Configuration

Table 10. Normal Mode Component Values

V

RIN R

REF

R

FB

C

M

C

S

FB

4.096 V 1 kΩ 655 Ω 18 Ω 5.6 pF 33 pF

Figure 32 shows the signal conditioning that occurs using the

circuit in Figure 18 with a ±2.5 V input signal biased around

ground and having the component values and conditions in

Table 10.

The differential amplifier always biases the output signal to sit

on the optimum common mode of V

/2, in this case, 2.048 V.

REF

The signal is also scaled to give the maximum allowable voltage

swing with this reference value. This is calculated as 80% of

; that is, 0.8 × 4.096 V ≈ 3.275 V p-p on each input.

V

REF

To obtain maximum performance from the AD7763, it is

advisable to drive the ADC with differential signals. Figure 33

shows how a bipolar, single-ended signal biased around ground

can drive the AD7763 with the use of an external op amp, such as

the AD8021.

2.5

A

2.5

2.5

B

2.5

Figure 32. Differential Amplifier Signal Conditioning

V

IN

2R

R

Figure 33. Single-Ended-to-Differential Conversion

+

IN

CPA

SS1

SH1

SS2

SH2

CPB1

CPB2

Figure 34. Equivalent Input Circuit

The AD7763 employs a double sampling front end, as shown in

Figure 34. For simplicity, only the equivalent input circuit for

+ is shown. The equivalent input circuitry for VIN− is the same.

V

IN

2R

AD8021

CS1

CS2

+3.685V

+2.048V

+0.410V

+3.685V

+2.048V

+0.410V

SS3

SS4

V

+

IN

V

–

IN

C

FB

R

FB

R

IN

C

R

IN

S

SH3

SH4

A1

R

FB

C

FB

MODULATOR

ANALOG

R

M

V

IN

R

M

VIN+

05476-019

05476-017

5476-018

With a 4.096 V reference, a 5 V supply must be provided to the

reference buffer (AV

must be provided to AV

). With a 2.5 V reference, a 3.3 V supply

DD4

.

DD4

Rev. A | Page 20 of 32

AD7763

SYNC

Sampling Switch SS1 and Sampling Switch SS3 are driven by ICLK,

whereas Sampling Switch SS2 and Sampling Switch SS4 are driven

by

. When ICLK is high, the analog input voltage is connected

ICLK

to CS1. On the falling edge of ICLK, the SS1 and SS3 switches

open, and the analog input is sampled on CS1. Similarly, when

ICLK is low, the analog input voltage is connected to CS2. On

the rising edge of ICLK, the SS2 and SS4 switches open, and the

analog input is sampled on CS2.

Capacitor CPA, Capacitor CPB1, and Capacitor CPB2 represent

parasitic capacitances that include the junction capacitances

associated with the MOS switches.

Table 11. Equivalent Component Values

Mode CS1 CS2 CPA CPB1/CPB2

Normal 51 pF 51 pF 12 pF 20 pF

Low Power 13 pF 13 pF 12 pF 5 pF

USING THE AD7763

Following is the recommended sequence for powering up and

using the AD7763.

Apply power.

1.

2.

Start clock oscillator, applying MCLK.

RESET

Ta k e

3.

4.

Wait a minimum of 2 MCLK cycles after

released.

5.

Write to Control Register 2 to power up the ADC and the

differential amplifier, as required.

low for a minimum of 1 MCLK cycle.

RESET

has been

The following are conditions for applying the

• The issuing of a

SYNC

pulse to the part must not coincide

with a write to the part.

SYNC

• The

of 2.5 ICLK cycles after the

pulse should be applied a minimum

FSI

signal for the previous write

to the part has returned to logic high.

• Ensure that the

SYNC

pulse is taken low for a minimum of

2.5 ICLK cycles.

Data can now be read from the part using the default filter,

offset, gain, and overrange threshold values. The conversion

data read is not valid, however, until the settling time of the

filter has passed. When this has occurred, the DVALID bit read

is set, indicating that the data is indeed valid.

The user can then download a user-defined filter, if required

(see Downloading a User-Defined Filter). Values for gain, offset,

and overrange threshold registers can also be written or read at

this stage.

BIAS RESISTOR SELECTION

The AD7763 requires a resistor to be connected between the

R

pin and AGND. The value for this resistor is dependent on

BIAS

the reference voltage being applied to the device. The resistor

value should be selected to give a current of 25 µA through the

resistor to ground. For a 2.5 V reference voltage, the correct

resistor value is 100 k

correct resistor value is 160 k

Ω; for a 4.096 V reference voltage, the

Ω.

pulse:

Write to Control Register 1 to set up the output data rate.

6.

7.

In circumstances where multiple parts are being

SYNC

synchronized, a

otherwise, no

SYNC

pulse must be applied to the parts;

pulse is required.

Rev. A | Page 21 of 32

AD7763

DECOUPLING AND LAYOUT RECOMMENDATIONS

Due to the high performance nature of the AD7763, correct decoupling and layout techniques are required to obtain the performance as

stated within this data sheet. Figure 35 shows a simplified connection diagram for the AD7763.

PIN 14

PIN 15

PIN 4

PIN 12

PIN 6

PIN 33

PIN 24

PIN 27

PIN 44

PIN 63

PIN 41

AV

PIN 4

(RHS)

DD2

C48

100nF

14154

1263324274463

100nF

INA+

INA–

OUTA–

OUTA+

C64

C7

33pF

VIN+

VIN–

19

20

21

22

8

30

25

26

VINA+

A–

V

IN

A–

V

OUT

A+

V

OUT

DECAPA

DECAPB

+

V

IN

–

V

IN

DD2AVDD2AVDD2

AV

DD4AVDD1AVDD1AVDD3AVDD2

AV

DRIVEVDRIVE

V

AD7763BSV

10

+

VREF

R19

160kΩ

L1

PIN 15

(VBIAS)

C50

100nF

L3

L2

PIN 14

(LHS) PI N 27

C62

100nF

L9

9

17

1

35

42

43

53

57

59

62

64

AV

PIN 12

(VBUF)

V

REF

REFGND

R

BIAS

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

DD4

R38

10Ω

C59

10nF

AGND1

AGND1

AGND2

AGND2

AGND2

AGND2

AGND2

AGND3

AGND3

AGND3

7

5

34

AV

L4

(VMOD1)

DD1

PIN 5

C52

100nF

L5

131618

PIN 33

(VMOD2)

28

L11

C53

100nF

232931

AGND3

32

AV

DD3

PIN 24

(VDIF1)

41

DV

AGND4

11

C54

100nF

DD

L6

U2

SCR

CDIV

FSO

SCO

SDO

SDL

SCP

ADR0

ADR1

ADR2

SH0

SH1

SH2

RESET

SYNC

DRDY

MCLK

MCLKGND

V

DRIVE

PIN 44

(VDRV1)

I

SDI

FSI

2

S

61

60

58

56

55

54

52

51

50

49

48

47

46

45

40

39

37

36

38

3

2

C56

100nF

I2S

SCR

CDIV

FSO

SCO

SDO

SDI

FSI

SDL

SCP

ADR0

ADR1

ADR2

SH0

SH1

SH2

RESET

SYNC

DRDY

MCLK

DV

DD

L7

PIN 63

(VDRV2)

L12

C57

100nF

PIN 41

(DVDD)

C58

100nF

L8

05476-028

Figure 35. Simplified Connection Diagram

Rev. A | Page 22 of 32

AD7763

SUPPLY DECOUPLING

Every supply pin must be connected to the appropriate supply

via a ferrite bead and decoupled to the correct ground pin with

a 100 nF, 0603 case size, X7R dielectric capacitor. There are two

exceptions

• Pin 12 (AV

) must have a 10 resistor inserted between

DD4

the pin and a 10 nF decoupling capacitor.

• Pin 27 (AV

) does not require a separate decoupling

DD2

capacitor or a direct connection to the supply; instead,

it is connected to Pin 14 via an 8.2 nH inductor.

The ferrite beads that are used to connect each supply pin to the

appropriate power supply should have a characteristic impedance

of 600 to 1 M at frequencies around 100 MHz, a dc impedance

of 1 or less, and a rated current of 200 mA.

ADDITIONAL DECOUPLING

There are two other decoupling pins on the AD7763: Pin 8

(DECAPA) and Pin 30 (DECAPB). Pin 8 should be decoupled

with a 100 nF capacitor, and Pin 30 requires a 33 pF capacitor.

REFERENCE VOLTAGE FILTERING

A low noise reference source, such as the ADR431 (2.5 V) or

ADR434 (4.096 V), is suitable for use with the AD7763. The

reference voltage supplied to the AD7763 should be decoupled

and filtered, as shown in Figure 36.

The recommended scheme for the reference voltage supply

is a 100 series resistor connected to a 100 F tantalum

capacitor, followed by a series resistor of 10 , and finally, a

C11

pin.

REF

R17

10Ω

+

C46

10nF

10 nF decoupling capacitor very close to the V

U3

ADR434

12V PIN 10VOUT

+

C15

10μFC9100nF

2

+VIN

GND

4

Figure 36. Reference Connection

6

100nF

C10

R30

100Ω

100μF

05476-021

DIFFERENTIAL AMPLIFIER COMPONENTS

The correct components for use around the on-chip differential

amplifier are shown in Tab le 10. Matching the components on

both sides of the differential amplifier is important to minimize

distortion of the signal applied to the amplifier. A tolerance of

0.1% or better is required for these components. Symmetrical

routing of the tracks on both sides of the differential amplifier

also assists in achieving stated performance.

EXPOSED PADDLE

The AD7763 64-lead TQFP_EP employs a 6 mm × 6 mm exposed

paddle (see Figure 39). The paddle reduces the thermal

resistance of the package by providing a path of low thermal

resistance to the PCB and, in turn, increases the heat transfer

efficiency from the AD7763 package. Soldering the exposed

paddle to the AGND plane of the PCB is fundamental in

creating the conditions that allow the AD7763 package to

perform to the highest specifications possible.

LAYOUT CONSIDERATIONS

While using the correct components is essential to achieve

optimum performance, the correct layout is just as important.

Design Tools section of the AD7763 product page on

The

the Analog Devices website contains the Gerber files for the

AD7763 evaluation board. These files should be used as a

reference when designing any system using the AD7763.

The location and orientation of some of the components

mentioned in previous sections are critical, and particular

attention must be paid to the components that are located close

to the AD7763. Locating these components farther away from

the devices can have a direct impact on the maximum

performance achievable.

The use of ground planes should also be carefully considered.

To ensure that the return currents through the decoupling

capacitors are flowing to the correct ground pin, the ground

side of the capacitors should be as close as possible to the ground

pin associated with that supply. A ground plane should not be

relied upon as the sole return path for decoupling capacitors,

because the return current path using ground planes is not

easily predicted.

Rev. A | Page 23 of 32

AD7763

PROGRAMMABLE FIR FILTER

As discussed in the Theory of Operation section, the third FIR

filter on the AD7763 can be programmed by the user. The default

coefficients that are loaded on reset are shown in Tab le 12. This

gives the frequency response shown in Figure 37. The frequencies

shown in Figure 37 scale directly with the output data rate.

Table 12. Default Filter Coefficients

#

Decimal

Value

Hex

Value

#

Decimal

Value

Hex

Value

0 +53656736 332BCA0 24 +700847 AB1AF

1 +25142688 17FA5A0 25 −70922 401150A

2 −4497814 444A196 26 −583959 408E917

3 −11935847 4B62067 27 −175934 402AF3E

4 −1313841 4140C31 28 +388667 5EE3B

5 +6976334 6A734E 29 +294000 47C70

6 +3268059 31DDDB 30 −183250 402CBD2

7 −3794610 439E6B2 31 −302597 4049E05

8 −3747402 4392E4A 32 +16034 3EA2

9 +1509849 1709D9 33 +238315 3A2EB

10 +3428088 344EF8 34 +88266 158CA

11 +80255 1397F 35 −143205 4022F65

12 −2672124 428C5FC 36 −128919 401F797

13 −1056628 4101F74 37 +51794 CA52

14 +1741563 1A92FB 38 +121875 1DC13

15 +1502200 16EBF8 39 +16426 402A

16 −835960 40CC178 40 −90524 401619C

17 −1528400 4175250 41 −63899 400F99B

18 +93626 16DBA 42 +45234 B0B2

19 +1269502 135EFE 43 +114720 1C020

20 +411245 6466D 44 +102357 18FD5

21 −864038 40D2F26 45 +52669 CDBD

22 −664622 40A242E 46 +15559 3CC7

23 +434489 6A139 47 +1963 7AB

The default filter should be sufficient for most applications.

It is a standard brick wall filter with a symmetrical impulse

response. The default filter has a length of 96 taps and is

nonaliasing, with 120 dB of attenuation at Nyquist. This filter

not only performs signal antialiasing but also suppresses out-ofband quantization noise produced by the analog-to-digital

conversion process. Any significant relaxation in the stop-band

attenuation or transition bandwidth relative to the default filter

can result in failure to meet the SNR specifications.

To create a user-defined filter, note the following:

• The filter must be even, symmetrical FIR.

• The coefficients are 27 bits in length. All coefficients are

in sign-and-magnitude format. The sign bit coded as

positive = 0 is followed by 26 magnitude bits.

• The filter length must be between 12 taps and 96 taps in

steps of 12.

• Because the filter is symmetrical, the number of coefficients

that must be downloaded is half the filter length. The default

filter coefficients are an example of this, with only 48

coefficients listed for a 96-tap filter.

• Coefficients are written from the center of impulse response

(adjacent to the point of symmetry) outward.

• The coefficients are scaled so that the in-band gain

of the filter is equal to 134217726, with the coefficients

rounded to the nearest integer. For a low-pass filter, this is the

equivalent of having the coefficients sum arithmetically

(including sign) to +67108863 (0x3FFFFFF) positive value

over the half-impulse-response coefficient set (maximum 48

coefficients). Any deviation from this results in the

introduction of a gain error.

0

–20

–40

–60

–80

–100

AMPLITUDE (dB)

–120

–140

–160

0 100 400 500300200 600

Figure 37. Default Filter Frequency Response (625 kHz ODR)

PASS-BAND RIPPLE = 0.05dB

–0.1dB FREQUENCY = 251kHz

–3dB FREQUE NCY = 256kHz

STOP BAND = 312.5kHz

FREQUENCY ( kHz)

05476-022

To download a user-defined filter, see the Downloading a UserDefined Filter section.

Rev. A | Page 24 of 32

AD7763

DOWNLOADING A USER-DEFINED FILTER

As discussed in the Programmable FIR Filter section, each of

the filter coefficients is 27 bits in length: one sign bit and 26 magnitude bits. To download coefficients for a user-specific FIR filter, a

32-bit word is written to the AD7763 for each coefficient.