Poly Phase Multifunction Energy Metering

V

V

V

Data Sheet

FEATURES

Highly accurate; supports IEC 60687, IEC 61036, IEC 61268,

IEC 62053-21, IEC 62053-22, and IEC 62053-23

Compatible with 3-phase/3-wire, 3-phase/4-wire, and other

3-phase services

Less than 0.1% active energy error over a dynamic range of

1000 to 1 at 25°C

Supplies active/reactive/apparent energy, voltage rms,

current rms, and sampled waveform data

Two pulse outputs, one for active power and the other

selectable between reactive and apparent power with

programmable frequency

Digital power, phase, and rms offset calibration

On-chip, user-programmable thresholds for line voltage SAG

and overvoltage detections

An on-chip, digital integrator enables direct interface-to-

current sensors with di/dt output

A PGA in the current channel allows direct interface to

current transformers

An SPI®-compatible serial interface with

PGA2

+

–

PGA2

+

–

PGA2

+

–

4kΩ

REF

ADC

ADC

ADC

ADC

ADC

ADC

AGND

IN/OUT

12

11

AVRMSGAI N[11:0]

HPF

Φ

APHCAL[6:0]

ACTIVE/REACTIVE/AP PARENT ENERGIES

AND VOLTAGE/CURRENT RMS CALCUL ATION

(SEE PHASE A FOR DETAILED SIGNAL PATH)

ACTIVE/REACTIVE/AP PARENT ENERGIES

AND VOLTAGE/CURRENT RMS CALCUL ATION

(SEE PHASE A FOR DETAILED SIGNAL PATH)

IAP

IAN

AP

IBP

IBN

BP

ICP

ICN

CP

VN

AVD D

4

POWER

SUPPLY

MONITOR

2.4V

REF

PGA1

5

+

–

6

16

PGA1

7

+

–

8

15

PGA1

9

+

–

10

14

13

IRQ

|X|

dt

INTEGRATOR

FOR PHASE B

FOR PHASE C

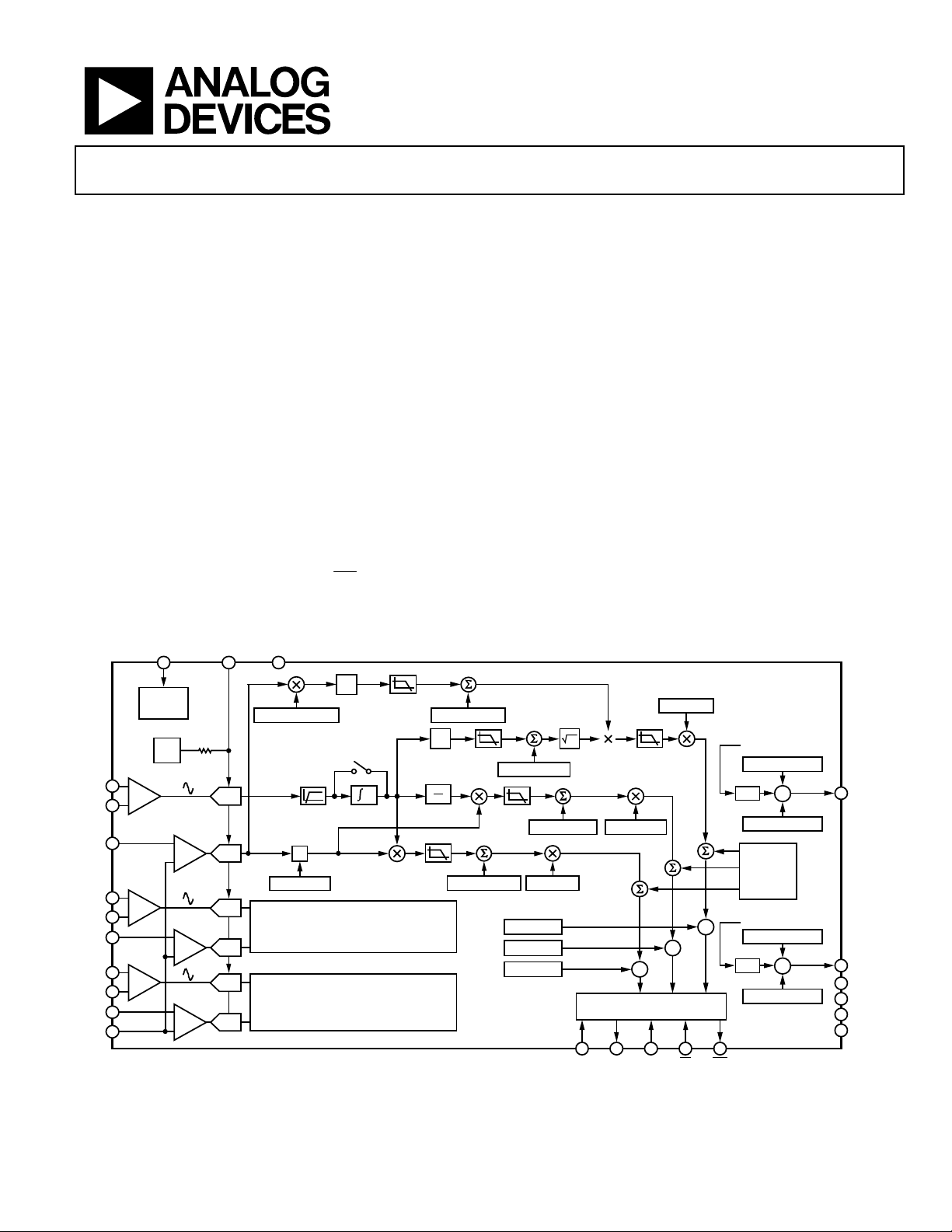

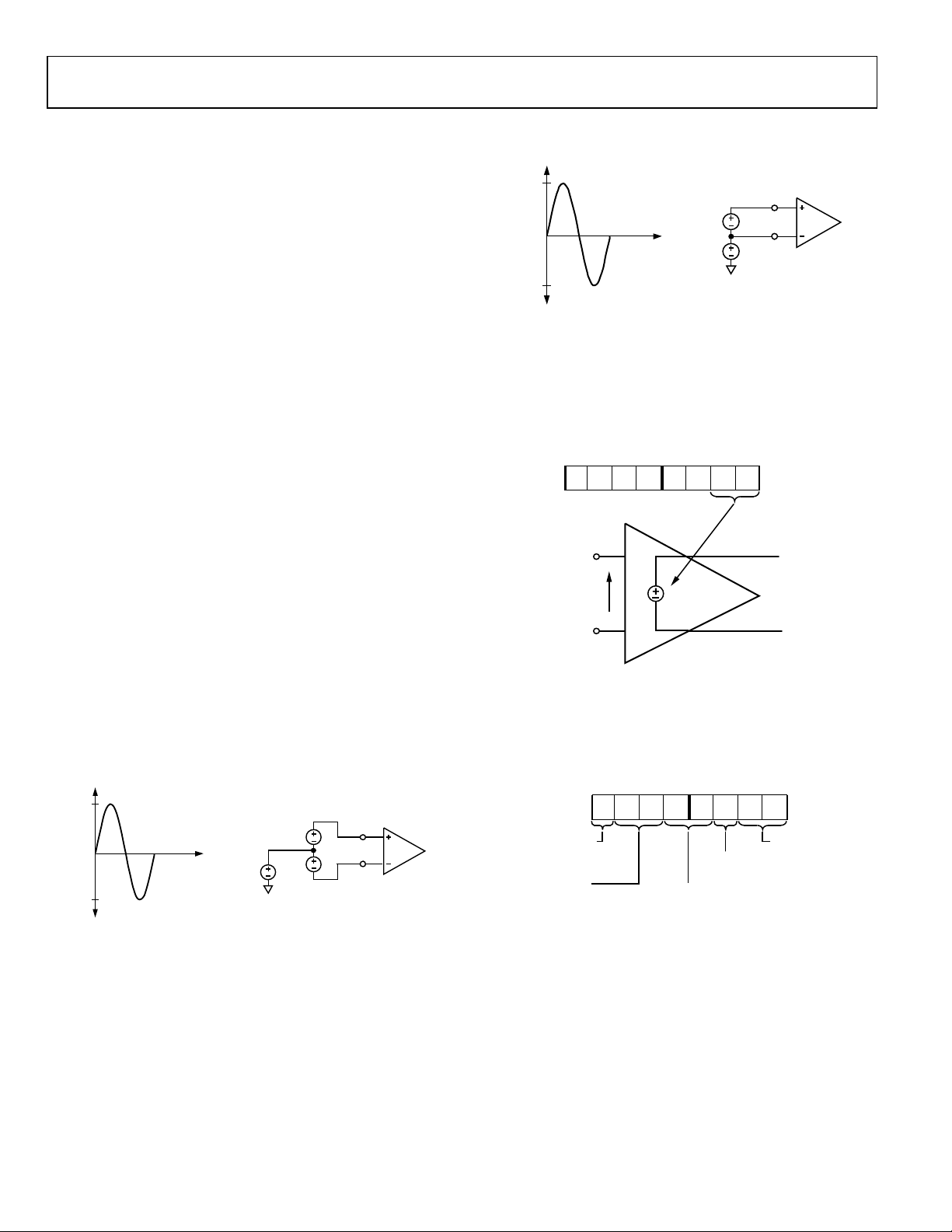

FUNCTIONAL BLOCK DIAGRAM

AVRMSOS[ 11:0]

2

X

90° PHASE

SHIFTING FILTER

π

2

LPF2

AWATT OS[ 11: 0] AWG [11:0 ]

IC with Per Phase Information

ADE7758

Proprietary ADCs and DSP provide high accuracy over large

variations in environmental conditions and time

Reference 2.4 V (drift 30 ppm/°C typical) with external

overdrive capability

Single 5 V supply, low power (70 mW typical)

GENERAL DESCRIPTION

The ADE7758 is a high accuracy, 3-phase electrical energy

measurement IC with a serial interface and two pulse outputs.

The ADE7758 incorporates second-order Σ-∆ ADCs, a digital

integrator, reference circuitry, a temperature sensor, and all the

signal processing required to perform active, reactive, and

apparent energy measurement and rms calculations.

The ADE7758 is suitable to measure active, reactive, and

apparent energy in various 3-phase configurations, such as

WYE or DELTA services, with both three and four wires. The

ADE7758 provides system calibration features for each phase,

that is, rms offset correction, phase calibration, and power

calibration. The APCF logic output gives active power

information, and the VARCF logic output provides instantaneous

reactive or apparent power information.

ADE7758

AVAG [11: 0]

REACTIVE OR

%

APPARENT POWER

VARC FNUM [ 11:0 ]

DFC

÷

VARCFDEN[11:0]

PHASE B

AND

PHASE C

DATA

ACTIVE POWER

APCFNUM[ 11:0]

DFC

÷

APCFDEN[ 11:0]

Figure 1.

AIRMSOS[ 11:0]

LPF2

AVAR OS[ 11 :0] AVARG [11 :0]

VADI V[7 :0]

VARD IV[ 7:0 ]

WDIV[7:0]

22

DIN24DOUT23SCLK21CS18IRQ

LPF

%

%

ADE7758 REGISTERS AND

SERIAL INTER FACE

17

1

3

2

19

20

VARC F

APCF

DVDD

DGND

CLKIN

CLKOUT

04443-001

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2004–2011 Analog Devices, Inc. All rights reserved.

ADE7758 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

General Description......................................................................... 1

Functional Block Diagram ..............................................................1

General Description......................................................................... 4

Specifications..................................................................................... 5

Timing Characteristics ................................................................ 6

Timing Diagrams.............................................................................. 7

Absolute Maximum Ratings............................................................ 8

ESD Caution.................................................................................. 8

Pin Configuration and Function Descriptions............................. 9

Terminology ....................................................................................11

Typical Performance Characteristics........................................... 12

Test Circuits..................................................................................... 17

Theory of Operation ......................................................................18

Antialiasing Filter....................................................................... 18

Analog Inputs..............................................................................18

Current Channel ADC............................................................... 19

di/dt Current Sensor and Digital Integrator............................... 20

Peak Current Detection............................................................. 21

Overcurrent Detection Interrupt .............................................21

Voltage Channel ADC ...............................................................22

Zero-Crossing Detection........................................................... 23

Phase Compensation.................................................................. 23

Period Measurement.................................................................. 25

Line Voltage SAG Detection..................................................... 25

SAG Level Set.............................................................................. 26

Peak Voltage Detection.............................................................. 26

Phase Sequence Detection......................................................... 26

Power-Supply Monitor............................................................... 27

Reference Circuit........................................................................ 27

Temperature Measurement....................................................... 27

Root Mean Square Measurement............................................. 28

Active Power Calculation.......................................................... 30

Reactive Power Calculation ......................................................35

Apparent Power Calculation..................................................... 39

Energy Registers Scaling ........................................................... 41

Waveform Sampling Mode ....................................................... 41

Calibration................................................................................... 42

Checksum Register..................................................................... 55

Interrupts..................................................................................... 55

Using the Interrupts with an MCU.......................................... 56

Interrupt Timing........................................................................ 56

Serial Interface............................................................................ 56

Serial Write Operation............................................................... 57

Serial Read Operation................................................................ 59

Accessing the On-Chip Registers............................................. 59

Registers........................................................................................... 60

Communications Register......................................................... 60

Operational Mode Register (0x13) .......................................... 64

Measurement Mode Register (0x14) ....................................... 64

Waveform Mode Register (0x15) ............................................. 65

Computational Mode Register (0x16)..................................... 66

Line Cycle Accumulation Mode Register (0x17)................... 67

Interrupt Mask Register (0x18)................................................ 68

Interrupt Status Register (0x19)/Reset Interrupt Status

Register (0x1A)........................................................................... 69

Outline Dimensions....................................................................... 70

Ordering Guide .......................................................................... 70

Revision History

10/11—Rev. D to Rev. E

Changes to Figure 1.......................................................................... 1

Changes to Figure 41...................................................................... 19

Changes to Figure 60...................................................................... 27

Added Figure 61; Renumbered Sequentially .............................. 27

Changes to Phase Sequence Detection Section ..........................27

Changes to Power-Supply Monitor Section................................ 27

Changes to Figure 62...................................................................... 28

Changes to Figure 67...................................................................... 32

Changes to Figure 68...................................................................... 32

Rev. E | Page 2 of 72

Changes to Equation 25................................................................. 34

Changes to Figure 69...................................................................... 34

Changes to Table 17 ....................................................................... 62

Change to Table 18 ......................................................................... 64

Changes to Table 24 ....................................................................... 69

Changes to Ordering Guide.......................................................... 70

10/08—Rev. C to Rev. D

Changes to Figure 1...........................................................................1

Changes to Phase Sequence Detection Section and Figure 60. 27

Data Sheet ADE7758

Changes to Current RMS Calculation Section............................28

Changes to Voltage Channel RMS Calculation Section and

Figure 63...........................................................................................29

Changes to Table 17 ........................................................................60

Changes to Ordering Guide...........................................................70

7/06—Rev. B to Rev. C

Updated Format..................................................................Universal

Changes to Figure 1...........................................................................1

Changes to Table 2 ............................................................................6

Changes to Table 4 ............................................................................9

Changes to Figure 34 and Figure 35 .............................................17

Changes to Current Waveform Gain Registers Section and

Current Channel Sampling Section ..............................................19

Changes to Voltage Channel Sampling Section ..........................22

Changes to Zero-Crossing Timeout Section...............................23

Changes to Figure 60 ......................................................................27

Changes to Current RMS Calculation Section............................28

Changes to Current RMS Offset Compensation Section and

Voltage Channel RMS Calculation Section .................................29

Added Table 7 and Table 9; Renumbered Sequentially..............29

Changes to Figure 65 ......................................................................30

Changes to Active Power Offset Calibration Section.................31

Changes to Reactive Power Frequency Output Section.............38

Changes to Apparent Power Frequency Output Section and

Waveform Sampling Mode Section ..............................................41

Changes to Gain Calibration Using Line

Accumulation Section ....................................................................49

Changes to Example: Power Offset Calibration Using Line

Accumulation Section ....................................................................53

Changes to Calibration of IRMS and VRMS Offset Section.....54

Changes to Table 18 ........................................................................64

Changes to Table 20 ........................................................................65

11/05—Rev. A to Rev. B

Changes to Table 1 ............................................................................5

Changes to Figure 23 Caption .......................................................14

Changes to Current Waveform Gain Registers Section .............19

Changes to di/dt Current Sensor and Digital

Integrator Section............................................................................20

Changes to Phase Compensation Section....................................23

Changes to Figure 57 ......................................................................25

Changes to Figure 60 ......................................................................27

Changes to Temperature Measurement Section

and Root Mean Square Measurement Section ............................28

Inserted Table 6................................................................................28

Changes to Current RMS Offset Compensation Section ..........29

Inserted Table 7................................................................................29

Added Equation 17 .........................................................................31

Changes to Energy Accumulation Mode Section.......................33

Changes to the Reactive Power Calculation Section..................35

Added Equation 32...........................................................................36

Changes to Energy Accumulation Mode Section.......................38

Changes to the Reactive Power Frequency Output Section......38

Changes to the Apparent Energy Calculation Section...............40

Changes to the Calibration Section..............................................42

Changes to Figure 76 through Figure 84............................... 43–54

Changes to Table 15 ........................................................................59

Changes to Table 16 ........................................................................63

Changes to Ordering Guide...........................................................69

9/04—Rev. 0 to Rev. A

Changed Hexadecimal Notation...................................... Universal

Changes to Features List...................................................................1

Changes to Specifications Table ......................................................5

Change to Figure 25........................................................................16

Additions to the Analog Inputs Section.......................................19

Added Figures 36 and 37; Renumbered Subsequent Figures....19

Changes to Period Measurement Section....................................26

Change to Peak Voltage Detection Section .................................26

Added Figure 60..............................................................................27

Change to the Current RMS Offset Compensation Section .....29

Edits to Active Power Frequency Output Section ......................33

Added Figure 68; Renumbered Subsequent Figures ..................33

Changes to Reactive Power Frequency Output Section.............37

Added Figure 73; Renumbered Subsequent Figures ..................38

Change to Gain Calibration Using Pulse Output Example.......44

Changes to Equation 37 .................................................................45

Changes to Example—Phase Calibration of Phase A

Using Pulse Output.........................................................................45

Changes to Equations 56 and 57...................................................53

Addition to the ADE7758 Interrupts Section .............................54

Changes to Example-Calibration of RMS Offsets ......................54

Addition to Table 20 .......................................................................66

1/04—Revision 0: Initial Version

Rev. E | Page 3 of 72

ADE7758 Data Sheet

GENERAL DESCRIPTION

The ADE7758 has a waveform sample register that allows access

to the ADC outputs. The part also incorporates a detection

circuit for short duration low or high voltage variations. The

voltage threshold levels and the duration (number of half-line

cycles) of the variation are user programmable. A zero-crossing

detection is synchronized with the zero-crossing point of the

line voltage of any of the three phases. This information can be

used to measure the period of any one of the three voltage

inputs. The zero-crossing detection is used inside the chip for

the line cycle energy accumulation mode. This mode permits

faster and more accurate calibration by synchronizing the

energy accumulation with an integer number of line cycles.

Data is read from the ADE7758 via the SPI serial interface. The

interrupt request output (

output. The

interrupt events have occurred in the . A status register

indicates the nature of the interrupt. The is available

in a 24-lead SOIC package.

output goes active low when one or more

IRQ

) is an open-drain, active low logic

IRQ

ADE7758

ADE7758

Rev. E | Page 4 of 72

Data Sheet ADE7758

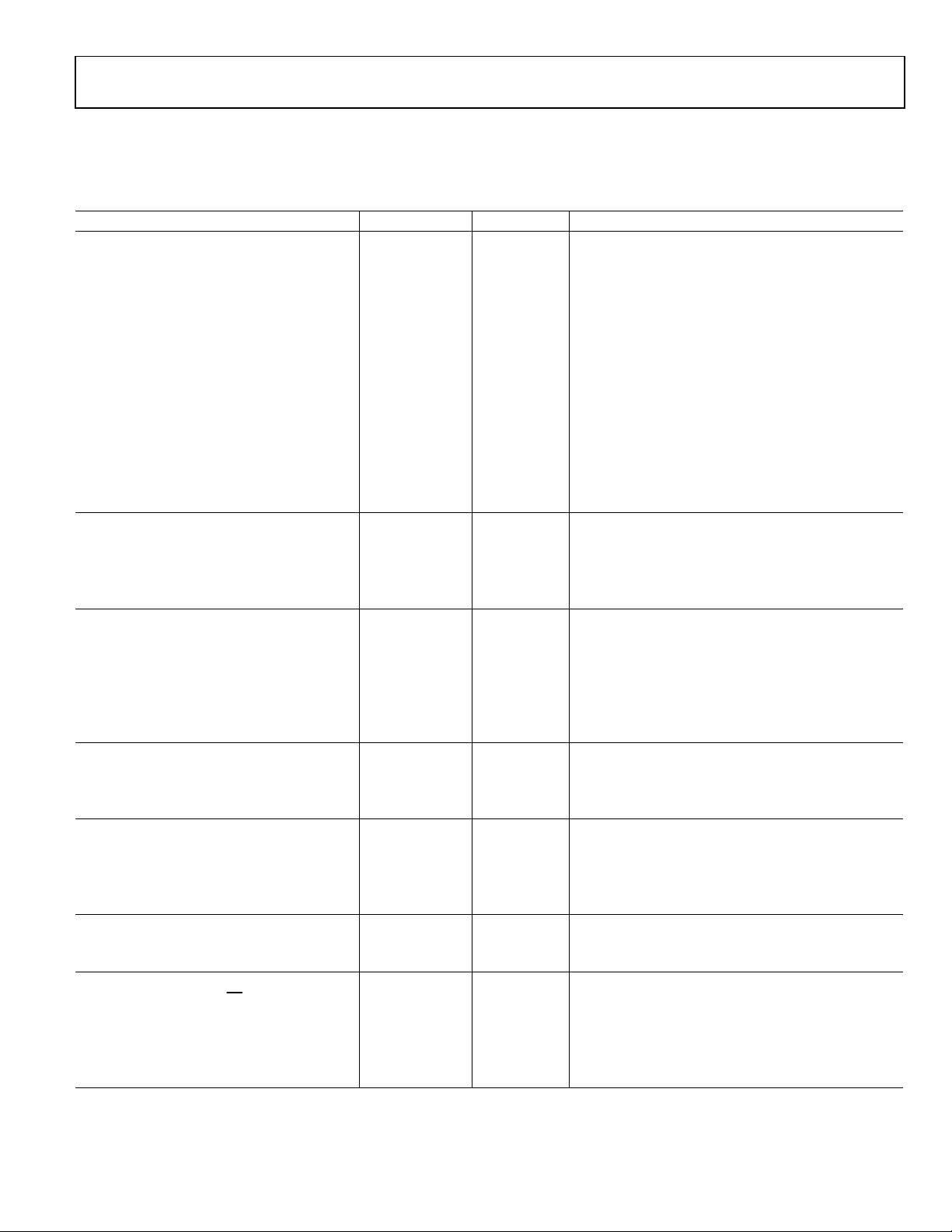

SPECIFICATIONS

AVDD = DVDD = 5 V ± 5%, AGND = DGND = 0 V, on-chip reference, CLKIN = 10 MHz XTAL, T

MIN

to T

= −40°C to +85°C.

MAX

Table 1.

Parameter

1, 2

Specification Unit Test Conditions/Comments

ACCURACY

Active Energy Measurement Error

0.1 % typ Over a dynamic range of 1000 to 1

(per Phase)

Phase Error Between Channels Line frequency = 45 Hz to 65 Hz, HPF on

PF = 0.8 Capacitive ±0.05 °max Phase lead 37°

PF = 0.5 Inductive ±0.05 °max Phase lag 60°

AC Power Supply Rejection AVDD = DVDD = 5 V + 175 mV rms/120 Hz

Output Frequency Variation 0.01 % typ V1P = V2P = V3P = 100 mV rms

DC Power Supply Rejection AVDD = DVDD = 5 V ± 250 mV dc

Output Frequency Variation 0.01 % typ V1P = V2P = V3P = 100 mV rms

Active Energy Measurement Bandwidth 14 kHz

IRMS Measurement Error 0.5 % typ Over a dynamic range of 500:1

IRMS Measurement Bandwidth 14 kHz

VRMS Measurement Error 0.5 % typ Over a dynamic range of 20:1

VRMS Measurement Bandwidth 260 Hz

ANALOG INPUTS See the Analog Inputs section

Maximum Signal Levels ±500 mV max Differential input

Input Impedance (DC) 380 kΩ min

ADC Offset Error3 ±30 mV max Uncalibrated error, see the Terminology section

Gain Error3 ±6 % typ External 2.5 V reference

WAVEFORM SAMPLING Sampling CLKIN/128, 10 MHz/128 = 78.1 kSPS

Current Channels See the Current Channel ADC section

Signal-to-Noise Plus Distortion 62 dB typ

Bandwidth (−3 dB) 14 kHz

Voltage Channels See the Voltage Channel ADC section

Signal-to-Noise Plus Distortion 62 dB typ

Bandwidth (−3 dB) 260 Hz

REFERENCE INPUT

REF

Input Voltage Range 2.6 V max 2.4 V + 8%

IN/OUT

2.2 V min 2.4 V − 8%

Input Capacitance 10 pF max

ON-CHIP REFERENCE Nominal 2.4 V at REF

IN/OUT

pin

Reference Error ±200 mV max

Current Source 6 μA max

Output Impedance 4 kΩ min

Temperature Coefficient 30 ppm/°C typ

CLKIN All specifications CLKIN of 10 MHz

Input Clock Frequency 15 MHz max

5 MHz min

LOGIC INPUTS

DIN, SCLK, CLKIN, and CS

Input High Voltage, V

Input Low Voltage, V

Input Current, I

INH

0.8 V max DVDD = 5 V ± 5%

INL

±3 μA max Typical 10 nA, VIN = 0 V to DVDD

IN

2.4 V min DVDD = 5 V ± 5%

Input Capacitance, CIN 10 pF max

Rev. E | Page 5 of 72

ADE7758 Data Sheet

Parameter

1, 2

Specification Unit Test Conditions/Comments

LOGIC OUTPUTS DVDD = 5 V ± 5%

IRQ, DOUT, and CLKOUT

Output High Voltage, VOH 4 V min I

Output Low Voltage, VOL 0.4 V max I

IRQ is open-drain, 10 kΩ pull-up resistor

SOURCE

SINK

= 5 mA

= 1 mA

APCF and VARCF

Output High Voltage, V

Output Low Voltage, VOL 1 V max I

4 V min I

OH

SOURCE

= 5 mA

SINK

= 8 mA

POWER SUPPLY For specified performance

AVDD 4.75 V min 5 V − 5%

5.25 V max 5 V + 5%

DVDD 4.75 V min 5 V − 5%

5.25 V max 5 V + 5%

AIDD 8 mA max Typically 5 mA

DIDD 13 mA max Typically 9 mA

1

See the Typical Performance Characteristics.

2

See the Terminology section for a definition of the parameters.

3

See the Analog Inputs section.

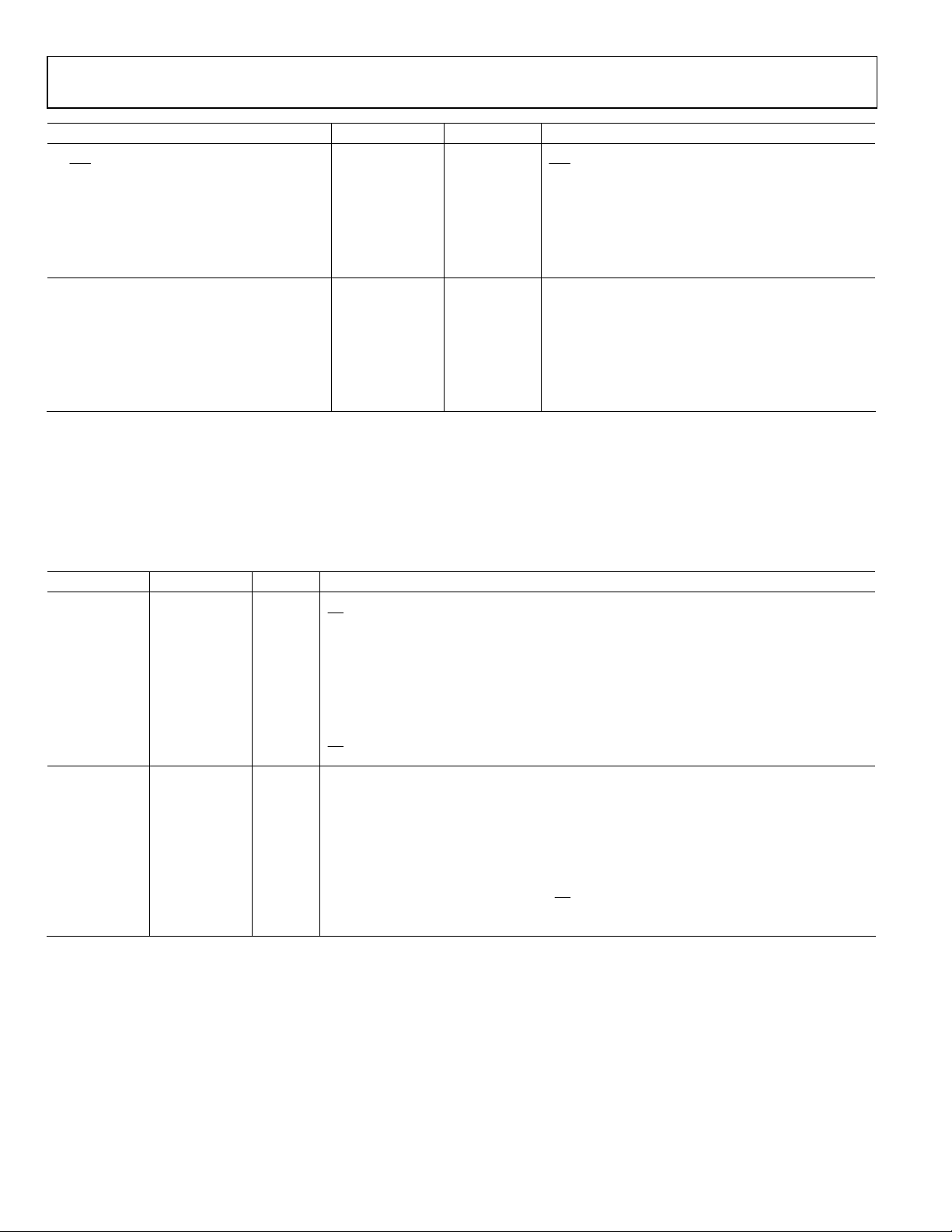

TIMING CHARACTERISTICS

AVDD = DVDD = 5 V ± 5%, AGND = DGND = 0 V, on-chip reference, CLKIN = 10 MHz XTAL, T

Table 2.

Parameter

1, 2

Specification Unit Test Conditions/Comments

WRITE TIMING

t1 50 ns (min)

falling edge to first SCLK falling edge

CS

t2 50 ns (min) SCLK logic high pulse width

t3 50 ns (min) SCLK logic low pulse width

t4 10 ns (min) Valid data setup time before falling edge of SCLK

t5 5 ns (min) Data hold time after SCLK falling edge

t6 1200 ns (min) Minimum time between the end of data byte transfers

t7 400 ns (min) Minimum time between byte transfers during a serial write

t8 100 ns (min)

hold time after SCLK falling edge

CS

READ TIMING

3

t

4 μs (min)

9

Minimum time between read command (that is, a write to communication register) and

data read

t10 50 ns (min) Minimum time between data byte transfers during a multibyte read

4

t

30 ns (min) Data access time after SCLK rising edge following a write to the communications register

11

5

t

100 ns (max) Bus relinquish time after falling edge of SCLK

12

10 ns (min)

5

t

100 ns (max)

13

Bus relinquish time after rising edge of CS

10 ns (min)

1

Sample tested during initial release and after any redesign or process change that may affect this parameter. All input signals are specified with tr = tf = 5 ns (10% to

90%) and timed from a voltage level of 1.6 V.

2

See the timing diagrams in Figure 3 and Figure 4 and the Serial Interface section.

3

Minimum time between read command and data read for all registers except waveform register, which is t9 = 500 ns min.

4

Measured with the load circuit in Figure 2 and defined as the time required for the output to cross 0.8 V or 2.4 V.

5

Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit in Figure 2. The measured number is then extrapolated back

to remove the effects of charging or discharging the 50 pF capacitor. This means that the time quoted here is the true bus relinquish time of the part and is

independent of the bus loading.

MIN

to T

= −40°C to +85°C.

MAX

Rev. E | Page 6 of 72

Data Sheet ADE7758

SCLK

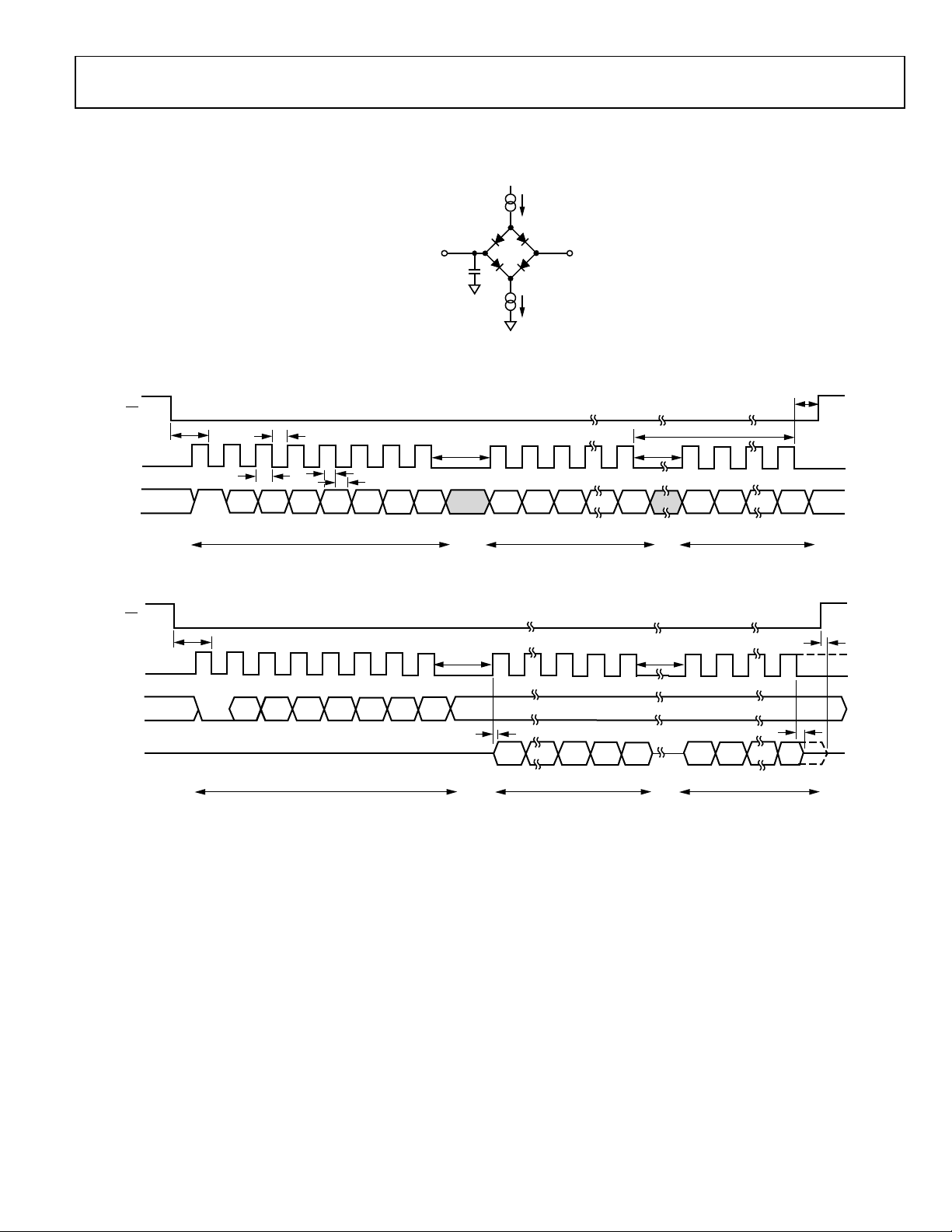

TIMING DIAGRAMS

TO OUTPUT

PIN

50pF

C

200µA I

L

1.6mA I

OL

2.1V

OH

04443-002

Figure 2. Load Circuit for Timing Specifications

t

8

CS

DIN

t

1

1

A6

t

3

t

2

A4A5 A3

COMMAND BYTE

DB0

t

7

t

7

t

4

t

5

A2

A0

A1

DB7

MOST SIGNIFICANT BYTE

t

6

DB7

LEAST SIGNIFICANT BYTE

DB0

04443-003

Figure 3. Serial Write Timing

CS

t

SCLK

1

t

9

t

10

t

13

DIN

DOUT

A6

A4A5 A3

COMMAND BYTE

A2

A0

A1

t

t

11

DB7

MOST SIGNIFICANT BYTE

DB0

DB7

LEAST SIGNIFICANT BYTE

12

DB0

04443-004

0

Figure 4. Serial Read Timing

Rev. E | Page 7 of 72

ADE7758 Data Sheet

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 3.

Parameter Rating

AVDD to AGND –0.3 V to +7 V

DVDD to DGND –0.3 V to +7 V

DVDD to AVDD –0.3 V to +0.3 V

Analog Input Voltage to AGND,

IAP, IAN, IBP, IBN, ICP, ICN, VAP,

VBP, VCP, VN

Reference Input Voltage to AGND –0.3 V to AVDD + 0.3 V

Digital Input Voltage to DGND –0.3 V to DVDD + 0.3 V

Digital Output Voltage to DGND –0.3 V to DVDD + 0.3 V

Operating Temperature

Industrial Range –40°C to +85°C

Storage Temperature Range –65°C to +150°C

Junction Temperature 150°C

24-Lead SOIC, Power Dissipation 88 mW

θJA Thermal Impedance 53°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

–6 V to +6 V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. E | Page 8 of 72

Data Sheet ADE7758

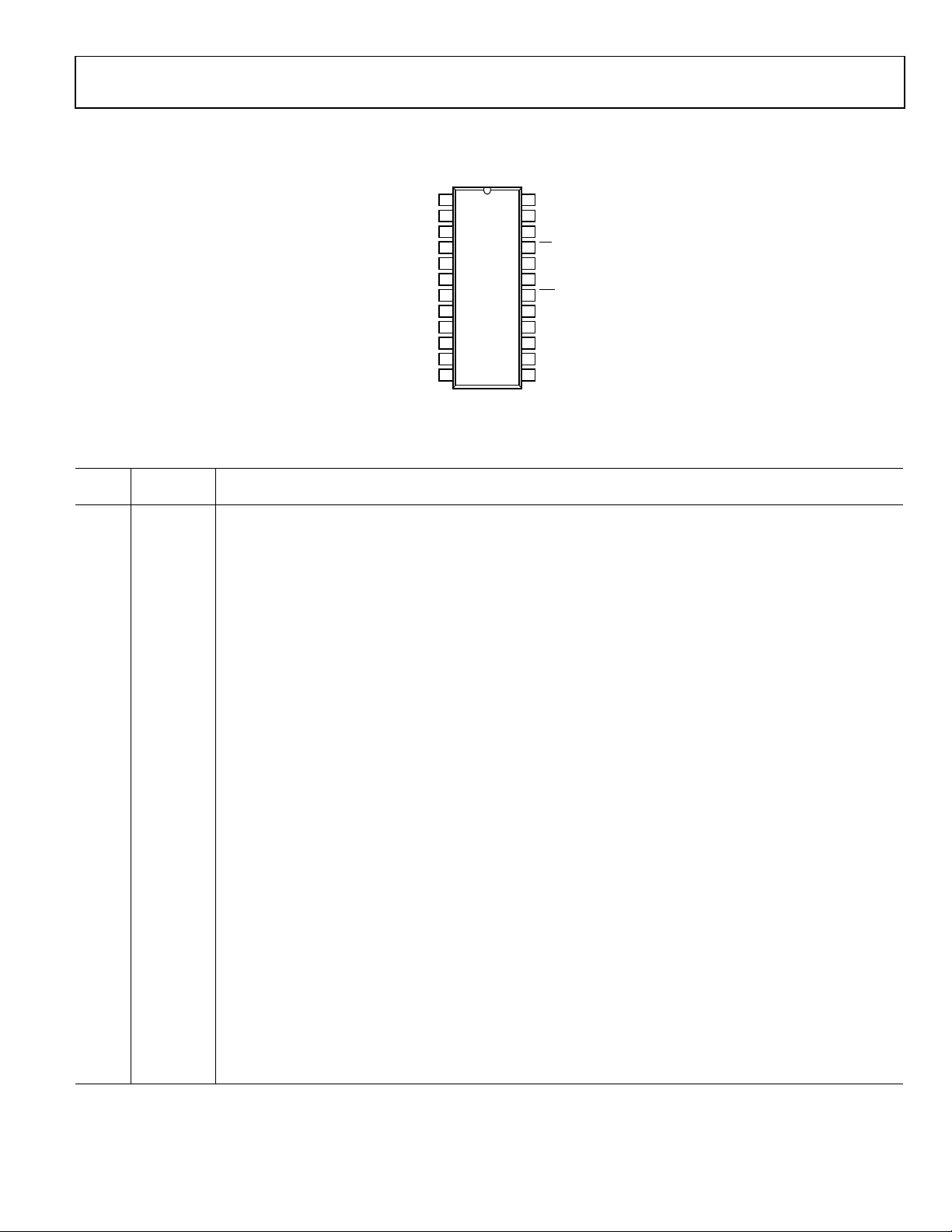

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 4. Pin Function Descriptions

Pin

No. Mnemonic Description

1 APCF

Active Power Calibration Frequency (APCF) Logic Output. It provides active power information. This output

is used for operational and calibration purposes. The full-scale output frequency can be scaled by writing to

the APCFNUM and APCFDEN registers (see the Active Power Frequency Output section).

2 DGND

This provides the ground reference for the digital circuitry in the ADE7758, that is, the multiplier, filters, and

digital-to-frequency converter. Because the digital return currents in the ADE7758 are small, it is acceptable to

connect this pin to the analog ground plane of the whole system. However, high bus capacitance on the DOUT

pin can result in noisy digital current that could affect performance.

3 DVDD

Digital Power Supply. This pin provides the supply voltage for the digital circuitry in the ADE7758. The supply

voltage should be maintained at 5 V ± 5% for specified operation. This pin should be decoupled to DGND with

a 10 μF capacitor in parallel with a ceramic 100 nF capacitor.

4 AVDD

Analog Power Supply. This pin provides the supply voltage for the analog circuitry in the ADE7758. The supply

should be maintained at 5 V ± 5% for specified operation. Every effort should be made to minimize power

supply ripple and noise at this pin by the use of proper decoupling. The Typical Performance Characteristics

show the power supply rejection performance. This pin should be decoupled to AGND with a 10 μF capacitor

in parallel with a ceramic 100 nF capacitor.

5, 6,

7, 8,

9, 10

IAP, IAN,

IBP, IBN,

ICP, ICN

Analog Inputs for Current Channel. This channel is used with the current transducer and is referenced in this

document as the current channel. These inputs are fully differential voltage inputs with maximum differential

input signal levels of ±0.5 V, ±0.25 V, and ±0.125 V, depending on the gain selections of the internal PGA (see

the Analog Inputs section). All inputs have internal ESD protection circuitry. In addition, an overvoltage

of ±6 V can be sustained on these inputs without risk of permanent damage.

11 AGND

This pin provides the ground reference for the analog circuitry in the ADE7758, that is, ADCs, temperature sensor,

and reference. This pin should be tied to the analog ground plane or the quietest ground reference in the system.

This quiet ground reference should be used for all analog circuitry, for example, antialiasing filters, current, and

voltage transducers. To keep ground noise around the ADE7758 to a minimum, the quiet ground plane should be

connected to the digital ground plane at only one point. It is acceptable to place the entire device on the analog

ground plane.

12 REF

IN/OUT

This pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of

2.4 V ± 8% and a typical temperature coefficient of 30 ppm/°C. An external reference source can also be

connected at this pin. In either case, this pin should be decoupled to AGND with a 1 μF ceramic capacitor.

13, 14,

15, 16

VN, VCP,

VBP, VAP

Analog Inputs for the Voltage Channel. This channel is used with the voltage transducer and is referenced as

the voltage channels in this document. These inputs are single-ended voltage inputs with the maximum signal

level of ±0.5 V with respect to VN for specified operation. These inputs are voltage inputs with maximum input

signal levels of ±0.5 V, ±0.25 V, and ±0.125 V, depending on the gain selections of the internal PGA (see the

Analog Inputs section). All inputs have internal ESD protection circuitry, and in addition, an overvoltage of

±6 V can be sustained on these inputs without risk of permanent damage.

1

APCF

DGND

2

DVDD

3

AVDD

4

ADE7758

IAP

5

TOP VIEW

6

IAN

(Not to Scale)

IBP

7

IBN

8

ICP

9

ICN

10

11

AGND

IN/OUT

12

REF

Figure 5. Pin Configuration

24

23

22

21

20

19

18

17

16

15

14

13

DOUT

SCLK

DIN

CS

CLKOUT

CLKIN

IRQ

VARCF

VAP

VBP

VCP

VN

04443-005

Rev. E | Page 9 of 72

ADE7758 Data Sheet

Pin

No. Mnemonic Description

17 VARCF

18

19 CLKIN

20 CLKOUT

21

22 DIN

23 SCLK

24 DOUT

Interrupt Request Output. This is an active low open-drain logic output. Maskable interrupts include: an active

IRQ

Chip Select. Part of the 4-wire serial interface. This active low logic input allows the ADE7758 to share the serial

CS

Reactive Power Calibration Frequency Logic Output. It gives reactive power or apparent power information

depending on the setting of the VACF bit of the WAVMODE register. This output is used for operational and

calibration purposes. The full-scale output frequency can be scaled by writing to the VARCFNUM and VARCFDEN

registers (see the Reactive Power Frequency Output section).

energy register at half level, an apparent energy register at half level, and waveform sampling up to 26 kSPS (see

the Interrupts section).

Master Clock for ADCs and Digital Signal Processing. An external clock can be provided at this logic input.

Alternatively, a parallel resonant AT crystal can be connected across CLKIN and CLKOUT to provide a clock

source for the ADE7758. The clock frequency for specified operation is 10 MHz. Ceramic load capacitors of

a few tens of picofarad should be used with the gate oscillator circuit. Refer to the crystal manufacturer’s

data sheet for the load capacitance requirements

A crystal can be connected across this pin and CLKIN as previously described to provide a clock source for

the ADE7758. The CLKOUT pin can drive one CMOS load when either an external clock is supplied at CLKIN or

a crystal is being used.

bus with several other devices (see the Serial Interface section).

Data Input for the Serial Interface. Data is shifted in at this pin on the falling edge of SCLK (see the Serial Interface

section).

Serial Clock Input for the Synchronous Serial Interface. All serial data transfers are synchronized to this clock

(see the Serial Interface section). The SCLK has a Schmidt-trigger input for use with a clock source that has a slow

edge transition time, for example, opto-isolator outputs.

Data Output for the Serial Interface. Data is shifted out at this pin on the rising edge of SCLK. This logic output

is normally in a high impedance state, unless it is driving data onto the serial data bus (see the Serial Interface

section).

Rev. E | Page 10 of 72

Data Sheet ADE7758

TERMINOLOGY

Measurement Error

The error associated with the energy measurement made by the

ADE7758 is defined by

=

ErrortMeasuremen

EnergyTrueADE7758byRegisteredEnergy

EnergyTrue

Phase Error Between Channels

The high-pass filter (HPF) and digital integrator introduce a

slight phase mismatch between the current and the voltage

channel. The all-digital design ensures that the phase matching

between the current channels and voltage channels in all three

phases is within ±0.1° over a range of 45 Hz to 65 Hz and ±0.2°

over a range of 40 Hz to 1 kHz. This internal phase mismatch

can be combined with the external phase error (from current

sensor or component tolerance) and calibrated with the phase

calibration registers.

Power Supply Rejection (PSR)

This quantifies the ADE7758 measurement error as a

percentage of reading when the power supplies are varied. For

the ac PSR measurement, a reading at nominal supplies (5 V) is

taken. A second reading is obtained with the same input signal

levels when an ac signal (175 mV rms/100 Hz) is introduced

onto the supplies. Any error introduced by this ac signal is

expressed as a percentage of reading—see the Measurement

Error definition.

(1)

%100–×

For the dc PSR measurement, a reading at nominal supplies

(5 V) is taken. A second reading is obtained with the same input

signal levels when the power supplies are varied ±5%. Any error

introduced is again expressed as a percentage of the reading.

ADC Offset Error

This refers to the dc offset associated with the analog inputs to

the ADCs. It means that with the analog inputs connected to

AGND that the ADCs still see a dc analog input signal. The

magnitude of the offset depends on the gain and input range

selection (see the Typical Perfor mance Charac teristics section).

However, when HPFs are switched on, the offset is removed

from the current channels and the power calculation is not

affected by this offset.

Gain Error

The gain error in the ADCs of the ADE7758 is defined as the

difference between the measured ADC output code (minus the

offset) and the ideal output code (see the Current Channel ADC

section and the Voltage Channel ADC section). The difference

is expressed as a percentage of the ideal code.

Gain Error Match

The gain error match is defined as the gain error (minus the

offset) obtained when switching between a gain of 1, 2, or 4. It is

expressed as a percentage of the output ADC code obtained

under a gain of 1.

Rev. E | Page 11 of 72

ADE7758 Data Sheet

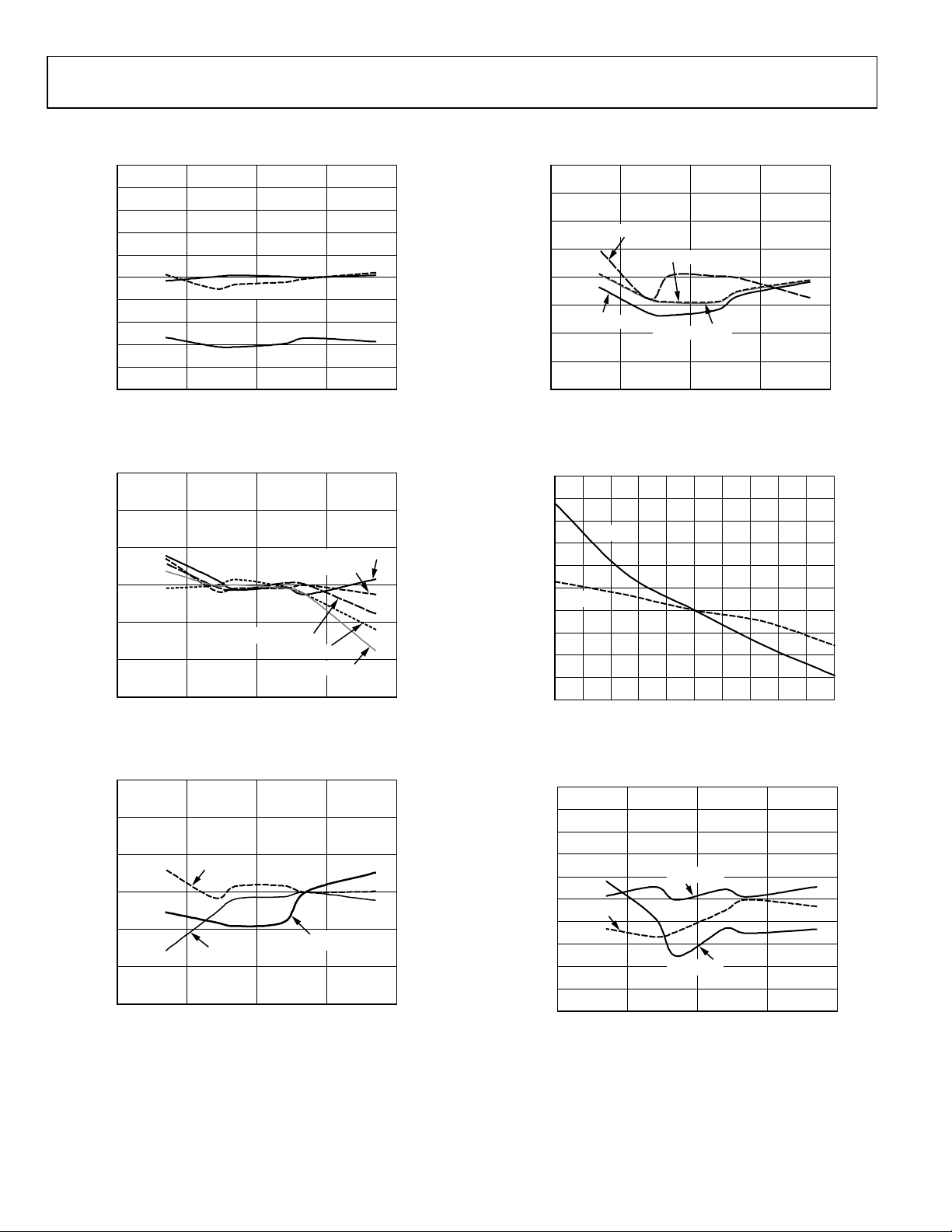

TYPICAL PERFORMANCE CHARACTERISTICS

0.5

PF = 1

0.4

0.3

0.2

0.1

0

–0.1

–0.2

PERCENT ERROR (%)

–0.3

–0.4

–0.5

0.01 0.1 1 10 100

+25°C

–40°C

+85°C

04443-006

PERCENT FULL-SCALE CURRENT (%)

Figure 6. Active Energy Error as a Percentage of Reading (Gain = +1) over

Temperature with Internal Reference and Integrator Off

0.3

0.2

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

0.01 0.1 1 10 100

PERCENT FULL-SCALE CURRENT (%)

PF = –0.5, +25°C

PF = +0.5, +25°C

PF = +1, +25°C

PF = +0.5, +85°C

PF = +0.5, –40°C

04443-007

Figure 7. Active Energy Error as a Percentage of Reading (Gain = +1) over

Power Factor with Internal Reference and Integrator Off

0.3

PF = 1

0.2

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

0.01 0.1 1 10 100

GAIN = +4

GAIN = +1

GAIN = +2

04443-008

PERCENT FULL-SCALE CURRENT (%)

0.20

0.15

0.10

0.05

0

–0.05

PERCENT ERROR (%)

–0.10

–0.15

–0.20

0.01 0.1 1 10 100

PF = +0.5, –40°C

PF = –0.5, +25°C

PF = +0.5, +85°C

PERCENT FULL-SCALE CURRENT (%)

PF = +0.5, +25°C

04443-009

Figure 9. Active Energy Error as a Percentage of Reading (Gain = +1) over

Temperature with External Reference and Integrator Off

0.6

0.5

0.4

0.3

0.2

0.1

0

–0.1

PERCENT ERROR (%)

WITH RESPECT TO 55Hz

–0.2

–0.3

–0.4

PF = 1

PF = 0.5

04443-010

45 47 49 51 53 55 57 59 61 63 65

LINE FREQUENCY (Hz)

Figure 10. Active Energy Error as a Percentage of Reading (Gain = +1) over

Frequency with Internal Reference and Integrator Off

0.10

PF = 1

0.08

0.06

0.04

0.02

0

VDD=5V

–0.02

–0.04

PERCENT ERROR (%)

WITH RESPECT TO 5V; 3A

–0.06

–0.08

–0.10

0.01 0.1 1 10 100

PERCENT FULL-SCALE CURRENT (%)

VDD= 5.25V

VDD= 4.75V

04443-011

Figure 8. Active Energy Error as a Percentage of Reading over

Gain with Internal Reference and Integrator Off

Figure 11. Active Energy Error as a Percentage of Reading (Gain = +1) over

Power Supply with Internal Reference and Integrator Off

Rev. E | Page 12 of 72

Data Sheet ADE7758

0.25

PF = 1

0.20

0.15

0.10

0.05

0

–0.05

–0.10

PERCENT ERROR (%)

–0.15

–0.20

–0.25

0.01 0.1 1 10 100

PHASE A

PHASE B

PERCENT FULL-SCALE CURRENT (%)

ALL PHASES

PHASE C

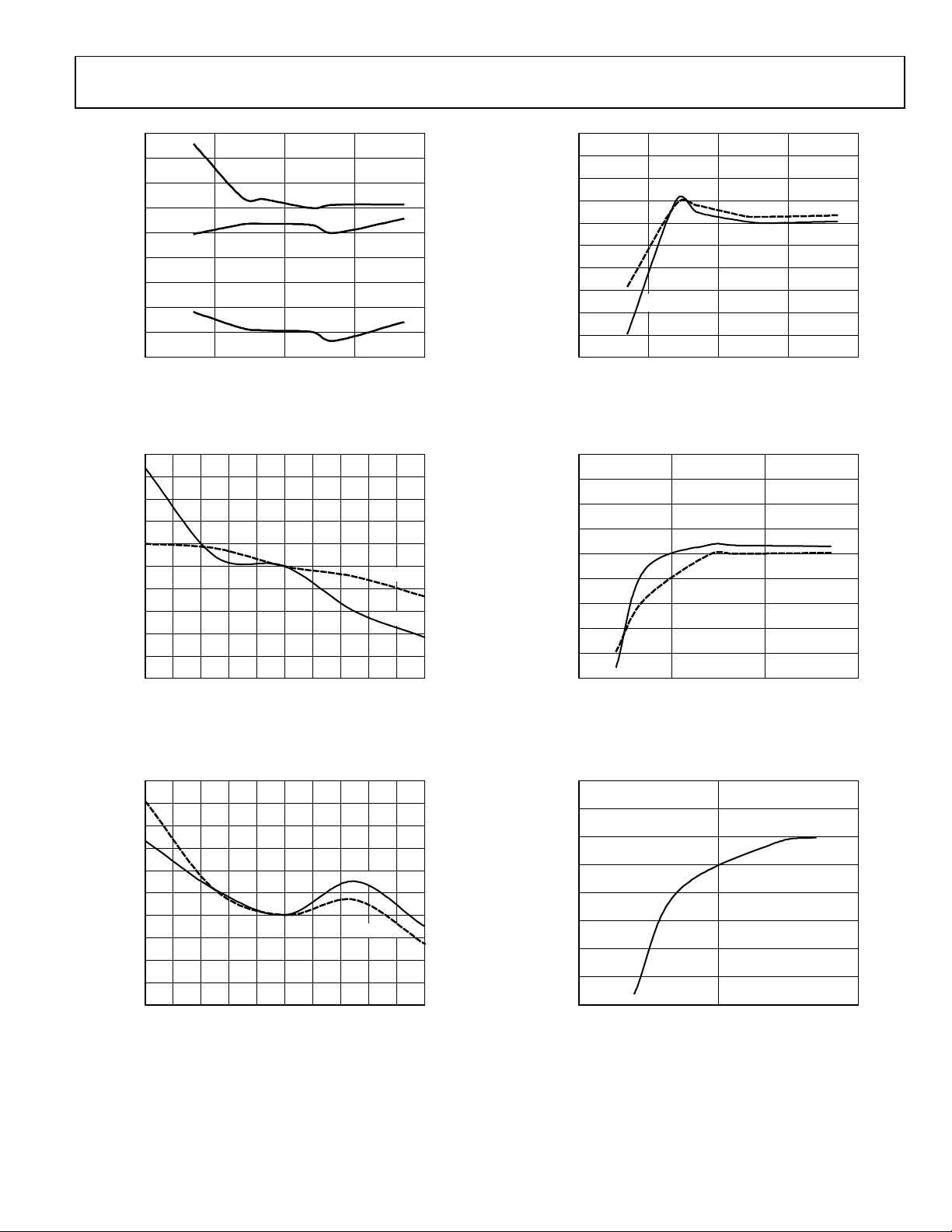

Figure 12. APCF Error as a Percentage of Reading (Gain = +1)

with Internal Reference and Integrator Off

0.4

04443-012

0.3

0.2

0.1

PF = 0, +85°C

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

0.01 0.1 1 10 100

PF = 0, +25°C

PF = 0, –40°C

PERCENT FULL-SCALE CURRENT (%)

04443-015

Figure 15. Reactive Energy Error as a Percentage of Reading (Gain = +1) over

Temperature with External Reference and Integrator Off

0.3

0.3

0.2

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

–0.4

0.01 0.1 1 10 100

PERCENT FULL-SCALE CURRENT (%)

PF = 0, +25°C

PF = 0, –40°C

PF = 0, +85°C

04443-013

Figure 13. Reactive Energy Error as a Percentage of Reading (Gain = +1) over

Temperature with Internal Reference and Integrator Off

0.8

0.6

0.4

0.2

PF = –0.866, +25°C

0

–0.2

PERCENT ERROR (%)

–0.4

–0.6

–0.8

0.01 0.1 1 10 100

PF = +0.866, –40°C

PF = +0.866, +85°C

PERCENT FULL-SCALE CURRENT (%)

PF = 0, +25°C

PF = +0.866, +25°C

04443-014

Figure 14. Reactive Energy Error as a Percentage of Reading (Gain = +1) over

Power Factor with Internal Reference and Integrator Off

0.2

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

0.01 0.1 1 10 100

PF = +0.866, +85°C

PERCENT FULL-SCALE CURRENT (%)

PF = +0.866, –40°C

PF = –0.866, +25°C

PF = 0, +25°C

PF = +0.866, +25°C

04443-016

Figure 16. Reactive Energy Error as a Percentage of Reading (Gain = +1) over

Power Factor with External Reference and Integrator Off

0.8

0.6

0.4

PF = 0

0.2

0

PF = 0.866

–0.2

PERCENT ERROR (%)

WITH RESPECT TO 55Hz

–0.4

–0.6

–0.8

45 47 49 51 53 55 57 59 61 63 65

LINE FREQUENCY (Hz)

04443-017

Figure 17. Reactive Energy Error as a Percentage of Reading (Gain = +1) over

Frequency with Internal Reference and Integrator Off

Rev. E | Page 13 of 72

ADE7758 Data Sheet

0.10

0.08

0.06

0.04

0.02

0

–0.02

–0.04

PERCENT ERROR (%)

WITH RESPECT TO 5V; 3A

–0.06

–0.08

–0.10

0.01 0.1 1 10 100

4.75V

PERCENT FULL-SCALE CURRENT (%)

5.25V

5V

04443-018

Figure 18. Reactive Energy Error as a Percentage of Reading (Gain = +1) over

Supply with Internal Reference and Integrator Off

0.3

PF = 0

0.2

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

0.01 0.1 1 10 100

GAIN = +2

GAIN = +4

GAIN = +1

PERCENT FULL-SCALE CURRENT (%)

04443-019

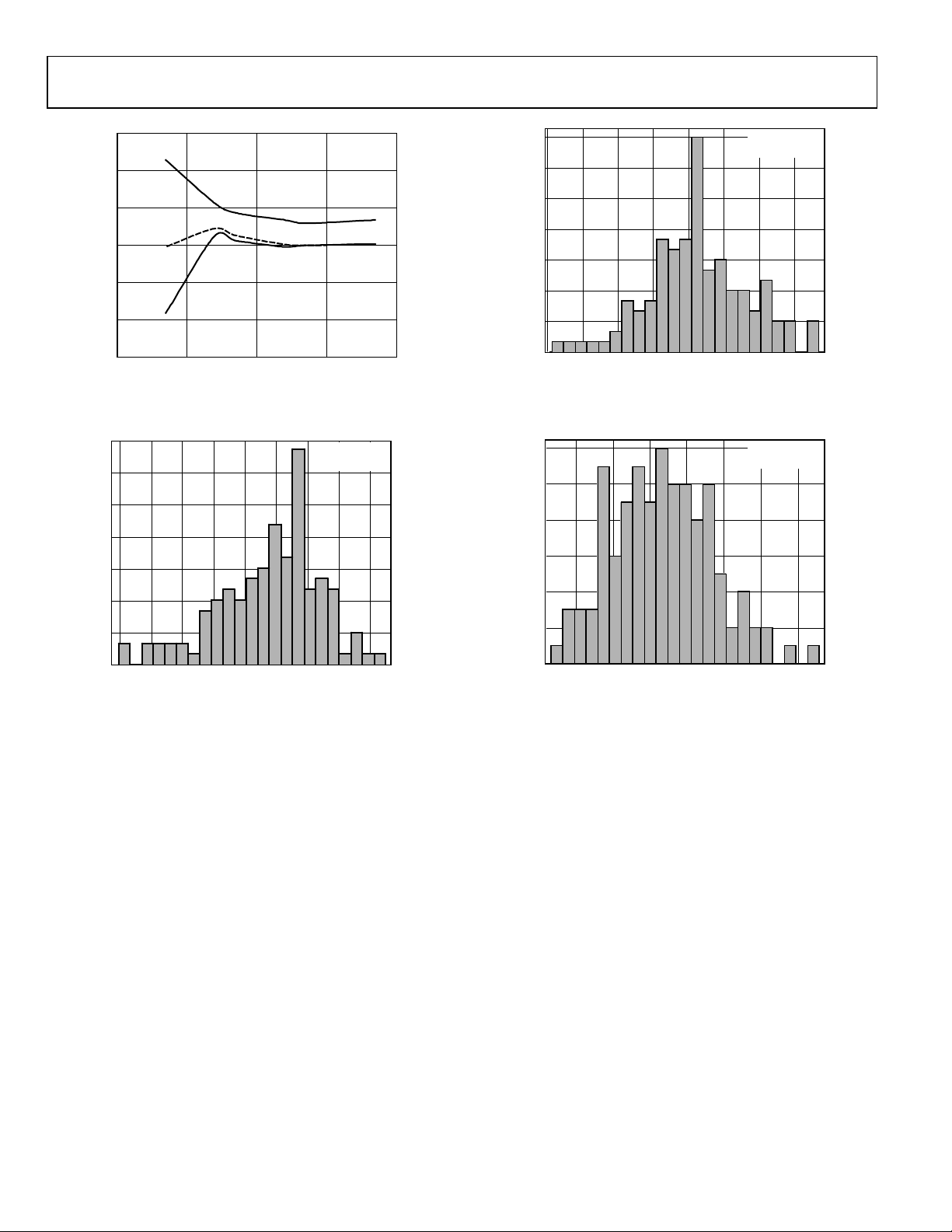

0.3

0.2

–40

°

+25°C

+85

C

°

C

04443-021

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

0.01 0.1 1 10 100

PERCENT FULL-SCALE CURRENT (%)

Figure 21. Active Energy Error as a Percentage of Reading (Gain = +4) over

Temperature with Internal Reference and Integrator On

0.5

0.4

0.3

0.2

PF = +0.5, +25

0.1

0

–0.1

–0.2

PERCENT ERROR (%)

–0.3

–0.4

–0.5

0.01 0.1 1 10 100

°

C

PF = +1, +25°C

PF = +0.5, +85

PERCENT FULL-SCALE CURRENT (%)

°

C

PF = +0.5, –40

PF = –0.5, +25

°

C

°

C

04443-022

Figure 19. Reactive Energy Error as a Percentage of Reading over Gain with

Internal Reference and Integrator Off

0.4

PF = 1

0.3

0.2

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

–0.4

0.01 0.1 1 10 100

ALL PHASES

PHASE C

PHASE B

PHASE A

PERCENT FULL-SCALE CURRENT (%)

04443-020

Figure 20. VARCF Error as a Percentage of Reading (Gain = +1)

with Internal Reference and Integrator Off

Rev. E | Page 14 of 72

Figure 22. Active Energy Error as a Percentage of Reading (Gain = +4) over

Power Factor with Internal Reference and Integrator On

0.8

0.6

°

°

C

C

PF = –0.866, +25

PF = –0.866, +85

°

C

°

C

04443-023

0.4

0.2

0

–0.2

PERCENT ERROR (%)

–0.4

–0.6

–0.8

0.01 0.1 1 10 100

PF = –0.866, –40

PF = 0, +25°C

PF = +0.866, +25

PERCENT FULL-SCALE CURRENT (%)

Figure 23. Reactive Energy Error as a Percentage of Reading (Gain = +4) over

Power Factor with Internal Reference and Integrator On

Data Sheet ADE7758

0.4

0.3

0.2

0.1

0

–0.1

–0.2

PERCENT ERROR (%)

–0.3

–0.4

–0.5

0.01 0.1 1 10 100

PERCENT FULL-SCALE CURRENT (%)

–40

+25°C

+85

PF = 0

°

C

°

C

04443-024

Figure 24. Reactive Energy Error as a Percentage of Reading (Gain = +4) over

Temperature with Internal Reference and Integrator On

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

PERCENT ERROR (%)

–0.3

–0.4

–0.5

45 47 49 51 53 55 57 59 61 63 65

LINE FREQUENCY (Hz)

PF = 0.5

PF = 1

04443-025

Figure 25. Active Energy Error as a Percentage of Reading (Gain = +4) over

Frequency with Internal Reference and Integrator On

1.2

1.0

0.8

0.6

0.4

0.2

0

–0.2

PERCENT ERROR (%)

–0.4

–0.6

–0.8

45 47 49 51 53 55 57 59 61 63 65

LINE FREQUENCY (Hz)

PF = 0

PF = 0.866

04443-026

Figure 26. Reactive Energy Error as a Percentage of Reading (Gain = +4) over

Frequency with Internal Reference and Integrator On

0.8

0.6

0.4

0.2

0

–0.2

PF = 0.5

–0.4

–0.6

PERCENT ERROR (%)

–0.8

–1.0

–1.2

0.01 0.1 1 10 100

PF = 1

PERCENT FULL-SCALE CURRENT (%)

Figure 27. IRMS Error as a Percentage of Reading (Gain = +1)

with Internal Reference and Integrator Off

0.8

0.6

0.4

0.2

0

–0.2

–0.4

PERCENT ERROR (%)

–0.6

–0.8

–1.0

0.1 1 10 100

PERCENT FULL-SCALE CURRENT (%)

PF = –0.5

PF = +1

Figure 28. IRMS Error as a Percentage of Reading (Gain = +4)

with Internal Reference and Integrator On

0.4

0.3

0.2

0.1

0

–0.1

PERCENT ERROR (%)

–0.2

–0.3

–0.4

1 10 100

VOLTAGE (V)

Figure 29. VRMS Error as a Percentage of Reading (Gain = +1)

with Internal Reference

04443-027

04443-028

04443-029

Rev. E | Page 15 of 72

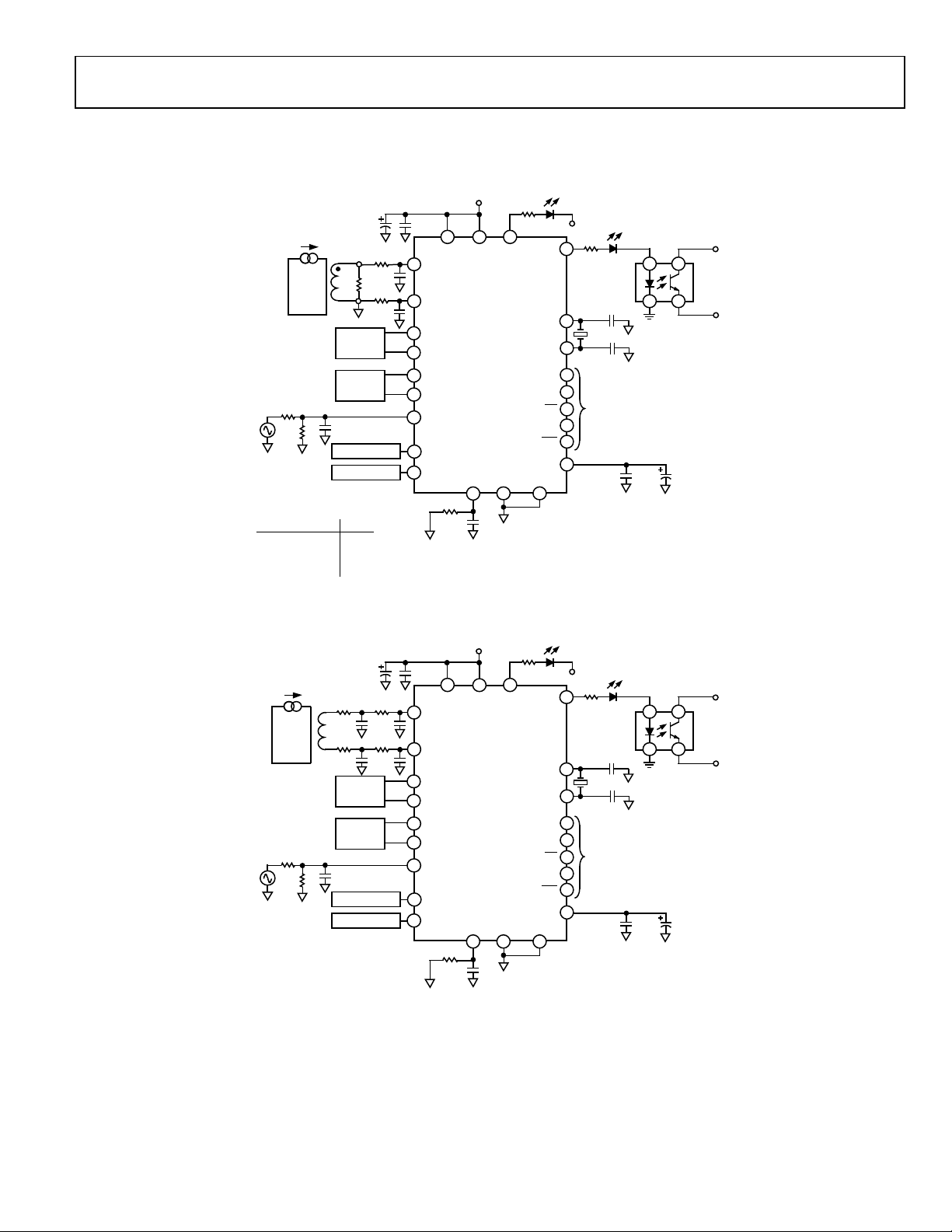

ADE7758 Data Sheet

1.5

1.0

0.5

0

–0.5

PERCENT ERROR (%)

–1.0

+85

+25

°

C

–40

°

C

°

C

21

18

15

12

HITS

MEAN: 6.5149

SD: 2.816

9

6

3

–1.5

0.01 1 100.1 100

PERCENT FULL-SCALE CURRENT (%)

Figure 30. Apparent Energy Error as a Percentage of Reading

(Gain = +1) over Temperature with Internal Reference and Integrator Off

MEAN: 5.55393

18

15

12

HITS

9

6

3

0

–4–2024681012

CH 1 PhA OFFSET (mV)

SD: 3.2985

Figure 31. Phase A Channel 1 Offset Distribution

04443-030

04443-031

0

–2024681012

CH 1 PhB OFFSET (mV)

04443-032

Figure 32. Phase B Channel 1 Offset Distribution

12

10

HITS

8

6

4

2

0

246810 1412

CH 1 PhC OFFSET (mV)

MEAN: 6.69333

SD: 2.70443

04443-033

Figure 33. Phase C Channel 1 Offset Distribution

Rev. E | Page 16 of 72

Data Sheet ADE7758

V

V

V

V

TEST CIRCUITS

DD

CURRENT

TRANSFORMER

I

1MΩ

220

1kΩ

CT TURN RATIO 1800:1

CHANNEL 2 GAI N = +1

CHANNEL 1 GAI N R

110Ω

25Ω

42.5Ω

81.25Ω

10µF

1kΩ

RB

SAME AS

I

, I

AP

AN

SAME AS

I

, I

AP

AN

33nF

SAME AS V

SAME AS V

B

33nF

1kΩ

33nF

100nF

IAP

5

IAN

6

IBP

7

IBN

8

ICP

9

10

ICN

16

VAP

15

VBP

AP

VCP

14

AP

34

AVDD DVDD

ADE7758

VN

13 11 2

1kΩ

17

APCF

VARC F

CLKOUT

CLKIN

DOUT

SCLK

REF

IN/OUT

AGND DGND

CS

DIN

IRQ

1

20

19

24

23

21

22

18

12

825Ω

22pF

10MHz

22pF

TO SPI BUS

100nF

PS2501-1

14

23

10µF

TO FREQ .

COUNTER

33nF

04443-034

Figure 34. Test Circuit for Integrator Off

DD

1kΩ

33nF

1kΩ

33nF

100nF

IAP

5

IAN

6

IBP

7

IBN

8

ICP

9

10

ICN

16

VAP

15

VBP

AP

14

VCP

AP

34

AVDD DVDD

ADE7758

VN

13 11 2

1kΩ

17

APCF

VARC F

CLKOUT

CLKIN

DOUT

SCLK

REF

IN/OUT

AGND DGND

CS

DIN

IRQ

1

20

19

24

23

21

22

18

12

825Ω

10MHz

TO SPI BUS

100nF

33nF

22pF

22pF

PS2501-1

14

23

10µF

TO FREQ .

COUNTER

04443-035

di/dt SENSOR

220

I

1kΩ

33nF

1kΩ

33nF

SAME AS

I

AP

SAME AS

I

AP

1MΩ

1kΩ

33nF

SAME AS V

SAME AS V

CHANNEL 1 GAI N = +8

CHANNEL 2 GAI N = +1

10µF

, I

, I

AN

AN

Figure 35. Test Circuit for Integrator On

Rev. E | Page 17 of 72

ADE7758 Data Sheet

V

V

V

V

THEORY OF OPERATION

ANTIALIASING FILTER

This filter prevents aliasing, which is an artifact of all sampled

systems. Input signals with frequency components higher than

half the ADC sampling rate distort the sampled signal at a frequency below half the sampling rate. This happens with all ADCs,

regardless of the architecture. The combination of the high

sampling rate ∑-∆ ADC used in the ADE7758 with the relatively

low bandwidth of the energy meter allows a very simple lowpass filter (LPF) to be used as an antialiasing filter. A simple RC

filter (single pole) with a corner frequency of 10 kHz produces

an attenuation of approximately 40 dB at 833 kHz. This is usually

sufficient to eliminate the effects of aliasing.

ANALOG INPUTS

The ADE7758 has six analog inputs divided into two channels:

current and voltage. The current channel consists of three pairs

of fully differential voltage inputs: IAP and IAN, IBP and IBN,

and ICP and ICN. These fully differential voltage input pairs

have a maximum differential signal of ±0.5 V. The current

channel has a programmable gain amplifier (PGA) with possible

gain selection of 1, 2, or 4. In addition to the PGA, the current

channels also have a full-scale input range selection for the ADC.

The ADC analog input range selection is also made using the

gain register (see Figure 38). As mentioned previously, the

maximum differential input voltage is ±0.5 V. However, by

using Bit 3 and Bit 4 in the gain register, the maximum ADC

input voltage can be set to ±0.5 V, ±0.25 V, or ±0.125 V on the

current channels. This is achieved by adjusting the ADC reference

(see the Reference Circuit section).

Figure 36 shows the maximum signal levels on the current

channel inputs. The maximum common-mode signal is

±25 mV, as shown in Figure 37.

+

1

2

+500mV

DIFFERENTIAL INPUT

+ V2 = 500mV MAX PEAK

V

V

–500mV

CM

1

COMMON-MODE

±25mV MAX

V

CM

Figure 36. Maximum Signal Levels, Current Channels, Gain = 1

The voltage channel has three single-ended voltage inputs: VAP,

VBP, and VCP. These single-ended voltage inputs have a

maximum input voltage of ±0.5 V with respect to VN. Both the

current and voltage channel have a PGA with possible gain

selections of 1, 2, or 4. The same gain is applied to all the inputs

of each channel.

Figure 37 shows the maximum signal levels on the voltage

channel inputs. The maximum common-mode signal is

±25 mV, as shown in Figure 36.

V

V

1

2

IAP, IBP,

OR ICP

IAN, IBN,

OR ICN

2

+500m

V

–500mV

SINGLE-E NDED INPUT

CM

±500mV MAX PEAK

COMMON-MODE

±25mV MAX

AGND

VA P, V B P,

OR VCP

V2

V

CM

V

N

04443-037

Figure 37. Maximum Signal Levels, Voltage Channels, Gain = 1

The gain selections are made by writing to the gain register.

Bit 0 to Bit 1 select the gain for the PGA in the fully differential

current channel. The gain selection for the PGA in the singleended voltage channel is made via Bit 5 to Bit 6. Figure 38

shows how a gain selection for the current channel is made

using the gain register.

GAIN[7:0]

GAIN (K)

IN

SELECTION

04443-038

IAP, IBP, ICP

V

IN

IAN, IBN, ICN

K × V

Figure 38. PGA in Current Channel

Figure 39 shows how the gain settings in PGA 1 (current

channel) and PGA 2 (voltage channel) are selected by various

bits in the gain register.

CURRENT AND VOLT AGE CHANNEL PG A CONTROL

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0

INTEGRATOR ENABLE

0 = DISABLE

1 = ENABLE

PGA 2 GAIN SELECT

04443-036

00 = ×1

01 = ×2

10 = ×4

1

REGISTE R CONTENTS SHOW POWER-ON DEFAULTS

GAIN REGISTER

CURRENT INPUT FUL L-SCALE SELECT

00 = 0.5V

01 = 0.25V

10 = 0.125V

Figure 39. Analog Gain Register

1

RESERVED

ADDRESS: 0x23

PGA 1 GAIN SELECT

00 = ×1

01 = ×2

10 = ×4

04443-039

Bit 7 of the gain register is used to enable the digital integrator

in the current signal path. Setting this bit activates the digital

integrator (see the DI/DT Current Sensor and Digital Integrator

section).

Rev. E | Page 18 of 72

Data Sheet ADE7758

V

V

CURRENT CHANNEL ADC

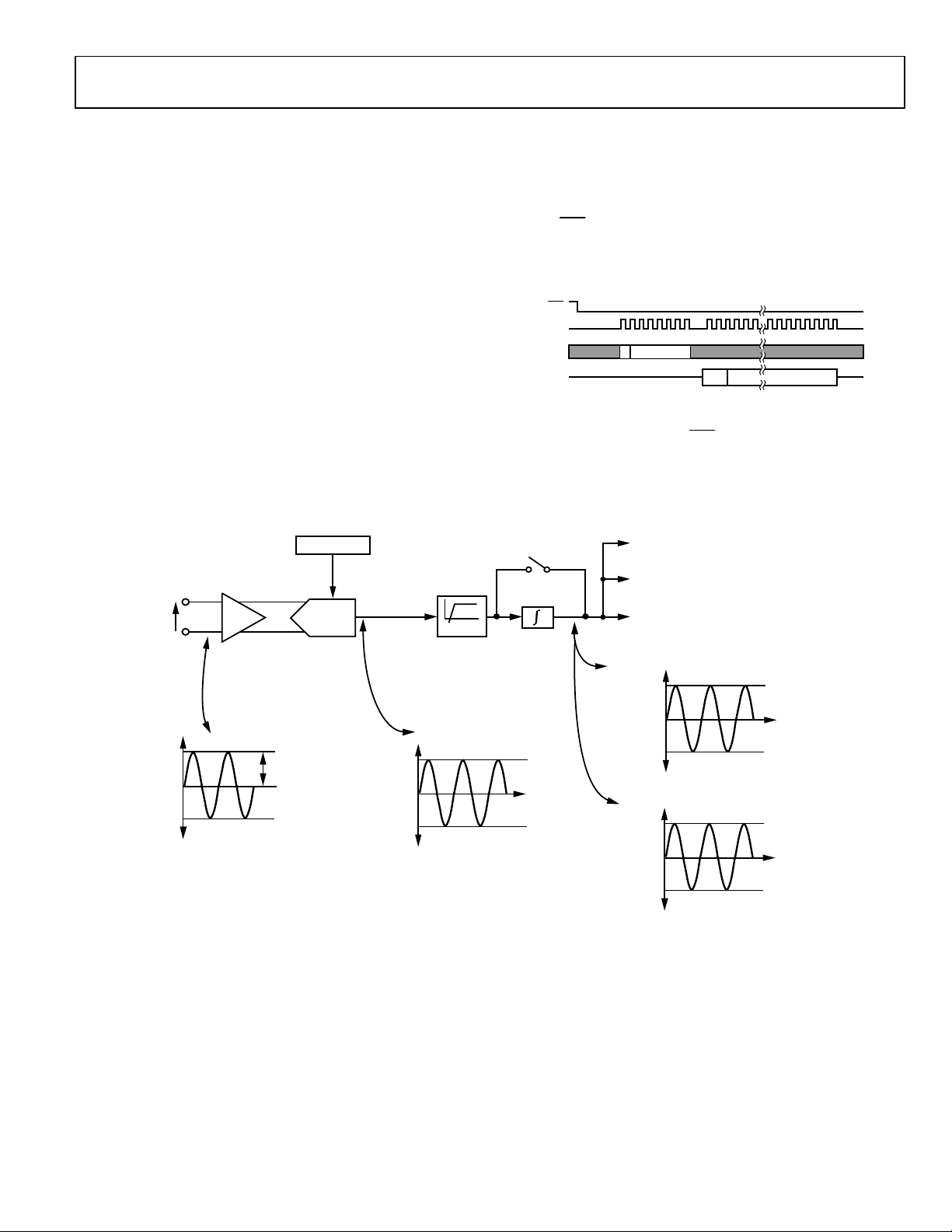

Figure 41 shows the ADC and signal processing path for the

input IA of the current channels (same for IB and IC). In

waveform sampling mode, the ADC outputs are signed twos

complement 24-bit data-words at a maximum of 26.0 kSPS

(thousand samples per second). With the specified full-scale

analog input signal of ±0.5 V, the ADC produces its maximum

output code value (see Figure 41). This diagram shows a fullscale voltage signal being applied to the differential inputs IAP

and IAN. The ADC output swings between 0xD7AE14

(−2,642,412) and 0x2851EC (+2,642,412).

Current Channel Sampling

The waveform samples of the current channel can be routed to

the WFORM register at fixed sampling rates by setting the

WAVSEL[2:0] bit in the WAVMODE register to 000 (binary)

(see Table 20). The phase in which the samples are routed is set

by setting the PHSEL[1:0] bits in the WAVMODE register.

Energy calculation remains uninterrupted during waveform

sampling.

GAIN[4:3]

2.42V, 1.21V, 0.6V

REFERENCE

IAP

V

IN

IAN

GAIN[1:0]

×1, ×2, ×4

PGA1

ADC

HPF

When in waveform sample mode, one of four output sample

rates can be chosen by using Bit 5 and Bit 6 of the WAVMODE

register (DTRT[1:0]). The output sample rate can be 26.04 kSPS,

13.02 kSPS, 6.51 kSPS, or 3.25 kSPS. By setting the WFSM bit in

the interrupt mask register to Logic 1, the interrupt request

output

timing is shown in . The 24-bit waveform samples are

transferred from the one byte (8-bits) at a time, with

goes active low when a sample is available. The

IRQ

Figure 40

ADE7758

the most significant byte shifted out first.

IRQ

SCLK

DIN

DOUT

READ FROM WAVEFORM

0x12

0

SGN

CURRENT CHANNE L DATA–24 BITS

Figure 40. Current Channel Waveform Sampling

The interrupt request output

stays low until the interrupt

IRQ

routine reads the reset status register (see the section). Interrupts

GAIN[7]

DIGITAL

INTEGRATOR

1

CURRENT RMS (IRMS)

CALCULATION

WAVEFORM SAMPLE

REGISTER

ACTIVE AND REACTIVE

POWER CALCULATION

CHANNEL 1 (CURRENT WA

DATA RANGE AFTER INTEGRATOR

50Hz

(50Hz AND AIGAIN[11:0] = 0x000)

0x34D1B8

EFORM)

4443-040

V

0V

IN

ANALOG

INPUT

RANGE

0x2851EC

0x000000

0xD7AE14

0.5V/GAIN

0.25V/GAIN

0.125V/GAIN

1

WHEN DIGITAL INTEGRATOR IS ENABLED, FULL-SCALE OUTPUT DATA IS

ATTENUATED DEPENDING ON THE SIGNAL FREQUENCY BECAUSE THE

INTEGRATOR HAS A –20dB/DECADE FREQUENCY RESPONSE. WHEN DISABLED,

THE OUTPUT WILL NOT BE FURTHER ATTENUATED.

CHANNEL 1

(CURRENT WAVEFORM)

DATA RANGE

ADC OUTPUT

WORD RANG E

Figure 41. Current Channel Signal Path

Rev. E | Page 19 of 72

0x000000

0xCB2E48

60Hz

0x2BE893

0x000000

0xD4176D

CHANNEL 1 (CURRENT WA

DATA RANGE AFTER INTEGRATOR

(60Hz AND AIGAIN[11:0] = 0x000)

EFORM)

04443-041

ADE7758 Data Sheet

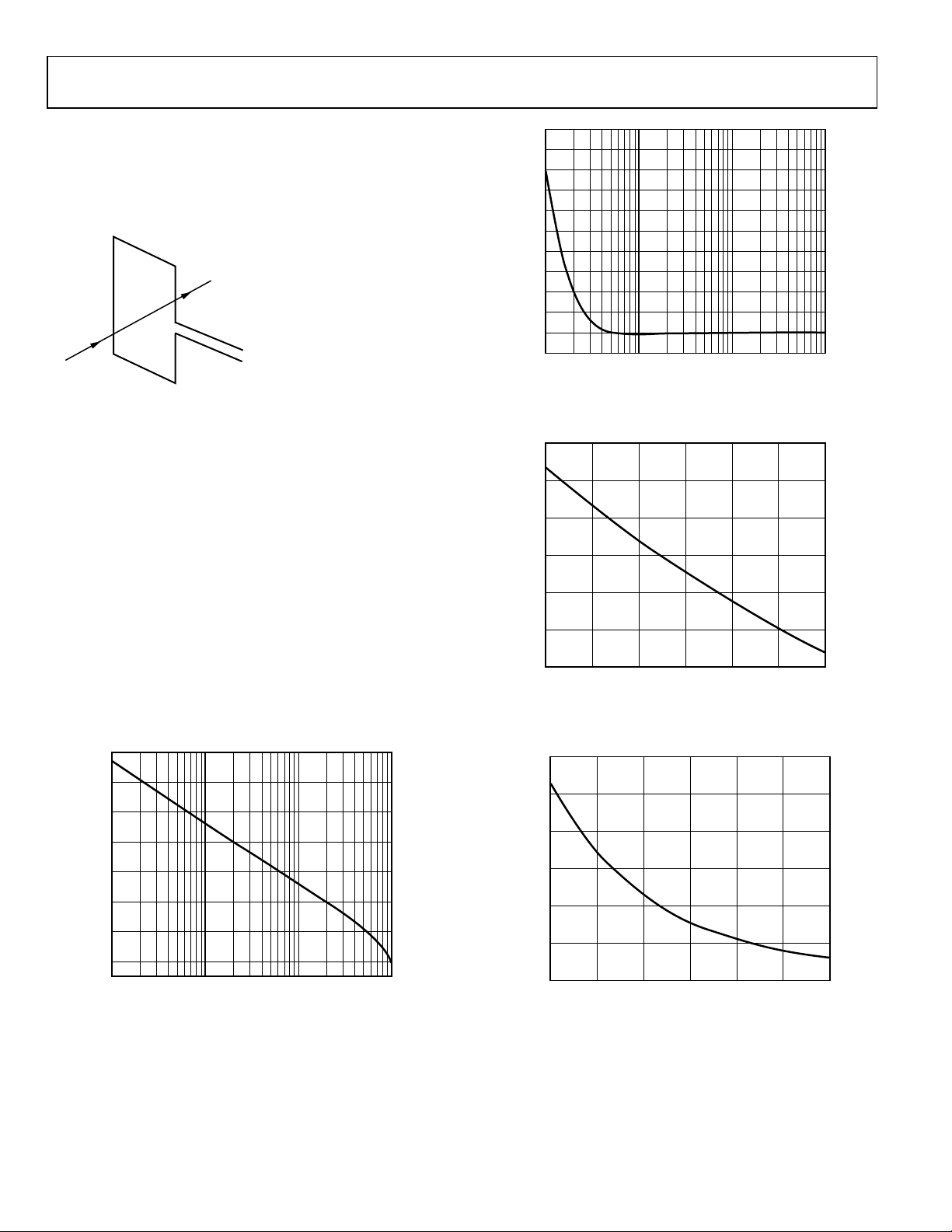

DI/DT CURRENT SENSOR AND DIGITAL INTEGRATOR

The di/dt sensor detects changes in the magnetic field caused by

the ac current. Figure 42 shows the principle of a di/dt current

sensor.

MAGNETIC FIELD CREATED BY CURRENT

(DIRECTLY PROPORTIONAL TO CURRENT)

+ EMF (ELECTROMOTIVE FORCE)

– INDUCED BY CHANGES IN

MAGNETIC FLUX DENSITY (di/dt)

Figure 42. Principle of a di/dt Current Sensor

The flux density of a magnetic field induced by a current is

directly proportional to the magnitude of the current. The

changes in the magnetic flux density passing through a conductor

loop generate an electromotive force (EMF) between the two

ends of the loop. The EMF is a voltage signal that is proportional to the di/dt of the current. The voltage output from the

di/dt current sensor is determined by the mutual inductance

between the current carrying conductor and the di/dt sensor.

The current signal needs to be recovered from the di/dt signal

before it can be used. An integrator is therefore necessary to

restore the signal to its original form. The ADE7758 has a builtin digital integrator to recover the current signal from the di/dt

sensor. The digital integrator on Channel 1 is disabled by default

when the ADE7758 is powered up. Setting the MSB of the

GAIN[7:0] register turns on the integrator. Figure 43 to Figure 46

show the magnitude and phase response of the digital

integrator.

20

10

0

–10

04443-042

80

81

82

83

84

85

86

87

PHASE (Degrees)

88

89

90

91

10 100 1k 10k

FREQUENCY (Hz)

Figure 44. Combined Phase Response of the

Digital Integrator and Phase Compensator

5

4

3

2

MAGNITUDE (dB)

1

0

–1

40 706560555045

FREQUENCY (Hz)

Figure 45. Combined Gain Response of the

Digital Integrator and Phase Compensator (40 Hz to 70 Hz)

89.80

89.85

89.90

04443-044

04443-045

–20

GAIN (dB)

–30

–40

–50

10 100 1k 10k

FREQUENCY (Hz)

Figure 43. Combined Gain Response of the

Digital Integrator and Phase Compensator

04443-043

Rev. E | Page 20 of 72

89.95

PHASE (Degrees)

90.00

90.05

90.10

40 706560555045

FREQUENCY (Hz)

Figure 46. Combined Phase Response of the

Digital Integrator and Phase Compensator (40 Hz to 70 Hz)

04443-046

Data Sheet ADE7758

Note that the integrator has a −20 dB/dec attenuation and

approximately −90° phase shi. When combined with a di/dt

sensor, the resulting magnitude and phase response should be a

flat gain over the frequency band of interest. However, the di/dt

sensor has a 20 dB/dec gain associated with it and generates

significant high frequency noise. A more effective antialiasing

filter is needed to avoid noise due to aliasing (see the Theory of

Operation section).

When the digital integrator is switched off, the ADE7758 can be

used directly with a conventional current sensor, such as a

current transformer (CT) or a low resistance current shunt.

PEAK CURRENT DETECTION

The ADE7758 can be programmed to record the peak of the

current waveform and produce an interrupt if the current

exceeds a preset limit.

Peak Current Detection Using the PEAK Register

The peak absolute value of the current waveform within a fixed

number of half-line cycles is stored in the IPEAK register.

Figure 47 illustrates the timing behavior of the peak current

detection.

L2

L1

CURRENT WAVEFORM

(PHASE SELECTED BY

PEAKSEL[2:0] IN

MMODE REGISTER)

NO. OF HALF

LINE CYCLES

SPECIFIED BY

LINECYC[15:0]

REGISTER

CONTENT OF

IPEAK[7:0]

Figure 47. Peak Current Detection Using the IPEAK Register

Note that the content of the IPEAK register is equivalent to

Bit 14 to Bit 21 of the current waveform sample. At full-scale

analog input, the current waveform sample is 0x2851EC. The

IPEAK at full-scale input is therefore expected to be 0xA1.

In addition, multiple phases can be activated for the peak

detection simultaneously by setting more than one of the

PEAKSEL[2:4] bits in the MMODE register to logic high. These

bits select the phase for both voltage and current peak

measurements. Note that if more than one bit is set, the VPEAK

and IPEAK registers can hold values from two different phases,

that is, the voltage and current peak are independently

processed (see the Peak Current Detection section).

00 L1 L2 L1

04443-047

Note that the number of half-line cycles is based on counting

the zero crossing of the voltage channel. The ZXSEL[2:0] bits in

the LCYCMODE register determine which voltage channels are

used for the zero-crossing detection. The same signal is also

used for line cycle energy accumulation mode if activated (see

the Line Cycle Accumulation Mode Register (0X17) section).

OVERCURRENT DETECTION INTERRUPT

Figure 48 illustrates the behavior of the overcurrent detection.

CURRENT PEAK WAVEFORM BEING MONITORED

(SELECTED BY PKIRQSEL[2:0] IN MMODE REGISTER)

IPINTLVL[7:0]

PKI RESET LOW

WHEN RSTATUS

REGISTER IS READ

PKI INTERRUPT FLAG

(BIT 15 OF STATUS

REGISTER)

READ RSTATUS

REGISTER

Figure 48. ADE7758 Overcurrent Detection

Note that the content of the IPINTLVL[7:0] register is

equivalent to Bit 14 to Bit 21 of the current waveform sample.

Therefore, setting this register to 0xA1 represents putting peak

detection at full-scale analog input. Figure 48 shows a current

exceeding a threshold. The overcurrent event is recorded by

setting the PKI flag (Bit 15) in the interrupt status register. If the

PKI enable bit is set to Logic 1 in the interrupt mask register, the

logic output goes active low (see the Interrupts section).

IRQ

Similar to peak level detection, multiple phases can be activated

for peak detection. If any of the active phases produce

waveform samples above the threshold, the PKI flag in the

interrupt status register is set. The phase of which overcurrent is

monitored is set by the PKIRQSEL[2:0] bits in the MMODE

register (see Table 19).

04443-048

Rev. E | Page 21 of 72

ADE7758 Data Sheet

CALIBRATIO N

GAIN[6:5]

+

PGA

–

VA

ANALOG INPUT

RANGE

0V

×1, ×2, ×4

0.5V

GAIN

ADC

0x2852

0x0

0xD7AE

VAP

VA

VN

Figure 49. ADC and Signal Processing in Voltage Channel

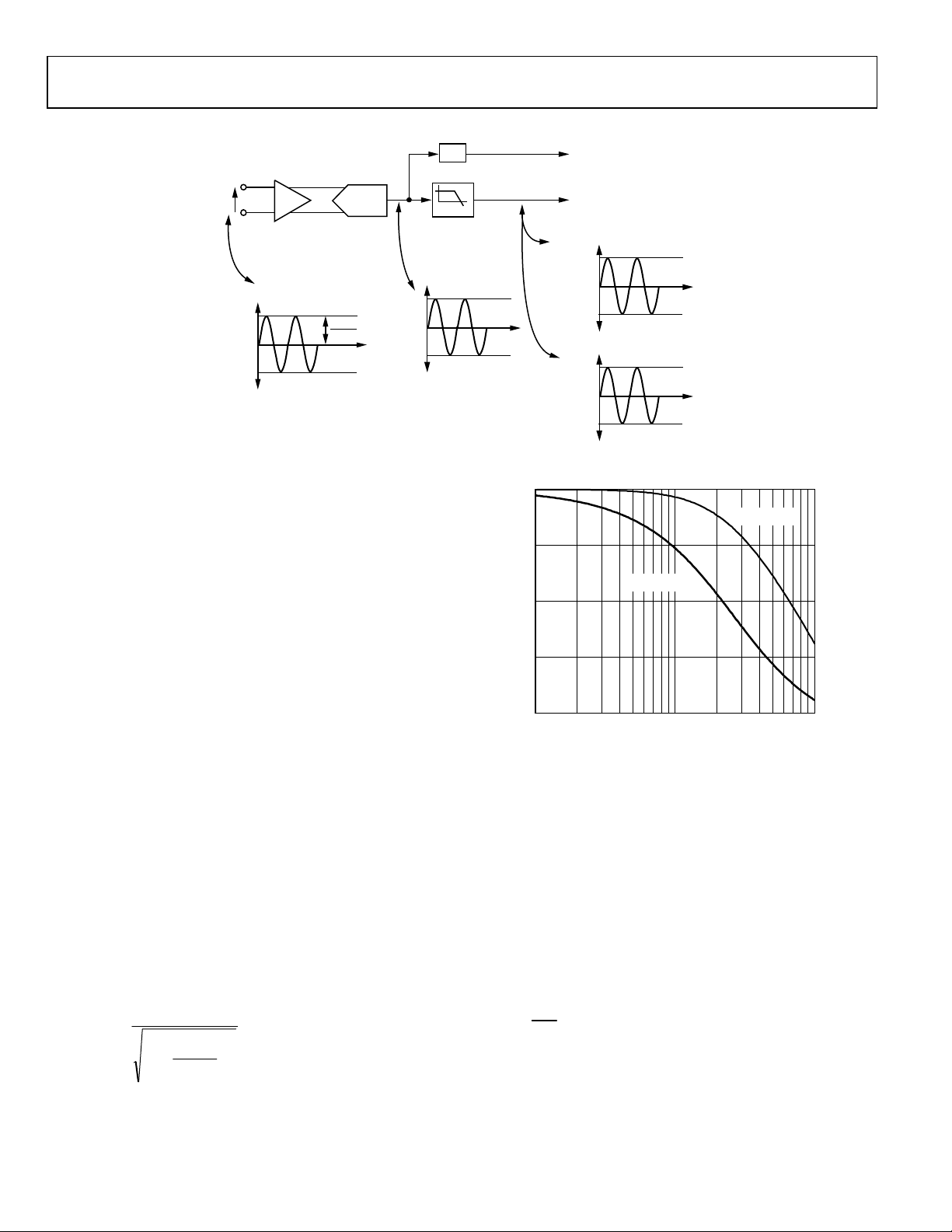

VOLTAGE CHANNEL ADC

Figure 49 shows the ADC and signal processing chain for the

input VA in the voltage channel. The VB and VC channels have

similar processing chains.

For active and reactive energy measurements, the output of the

ADC passes to the multipliers directly and is not filtered. This

solution avoids the much larger multibit multiplier and does not

affect the accuracy of the measurement. An HPF is not

implemented on the voltage channel to remove the dc offset

because the HPF on the current channel alone should be

sufficient to eliminate error due to ADC offsets in the power

calculation. However, ADC offset in the voltage channels

produces large errors in the voltage rms calculation and affects

the accuracy of the apparent energy calculation.

Voltage Channel Sampling

The waveform samples on the voltage channels can also be

routed to the WFORM register. However, before passing to the

WFORM register, the ADC outputs pass through a single-pole,

low-pass filter (LPF1) with a cutoff frequency at 260 Hz.

Figure 50 shows the magnitude and phase response of LPF1.

This filter attenuates the signal slightly. For example, if the line

frequency is 60 Hz, the signal at the output of LPF1 is

attenuated by 3.575%. The waveform samples are 16-bit, twos

complement data ranging between 0x2748 (+10,056d) and

0xD8B8 (−10,056d). The data is sign extended to 24-bit in the

WFORM register.

()

=fH

1

2

⎛

⎜

1

+

⎜

⎝

⎞

Hz60

⎟

⎟

Hz260

⎠

−==

(3)

dB225.0974.0

PHASE

Φ

PHCAL[6:0]

LPF1

f

= 260Hz

3dB

TO ACTIVE AND

REACTIVE ENERG Y

CALCULATIO N

TO VOLTAGE RMS

CALCULATIO N AND

WAVEFORM SAMPLING

LPF OUTPUT

50Hz

WORD RANGE

0x2797

0x0

0xD869

LPF OUTPUT

60Hz

WORD RANGE

0x2748

0x0

0xD8B8

0

–20

(60Hz; –13°)

–40

PHASE (Degrees)

–60

–80

10 100 1k

FREQUENCY (Hz)

04443-049

(60Hz; –0.2dB)

0

–10

–20

–30

–40

GAIN (dB)

04443-050

Figure 50. Magnitude and Phase Response of LPF1

Note that LPF1 does not affect the active and reactive energy

calculation because it is only used in the waveform sampling

signal path. However, waveform samples are used for the

voltage rms calculation and the subsequent apparent energy

accumulation.

The WAVSEL[2:0] bits in the WAVMODE register should be set

to 001 (binary) to start the voltage waveform sampling. The

PHSEL[1:0] bits control the phase from which the samples are

routed. In waveform sampling mode, one of four output sample

rates can be chosen by changing Bit 5 and Bit 6 of the WAVMODE

register (see Table 2 0). The available output sample rates are

26.0 kSPS, 13.5 kSPS, 6.5 kSPS, or 3.3 kSPS. By setting the WFSM

bit in the interrupt mask register to Logic 1, the interrupt request

output

bit waveform samples are transferred from the one byte

goes active low when a sample is available. The 24-

IRQ

ADE7758

(8 bits) at a time, with the most significant byte shifted out first.

The sign of the register is extended in the upper 8 bits. The

timing is the same as for the current channels, as seen in Figure 40.

Rev. E | Page 22 of 72

Data Sheet ADE7758

V

V

V

ZERO-CROSSING DETECTION

The ADE7758 has zero-crossing detection circuits for each of

the voltage channels (VAN, VBN, and VCN). Figure 51 shows

how the zero-cross signal is generated from the output of the

ADC of the voltage channel.

REFERENCE

ADC

24.8° @ 60Hz

f

–3dB

LPF1

= 260Hz

ZERO-

CROSSI NG

DETECTOR

ANALOG VOLTAGE

WAVE FOR M

(VAN, VBN, OR VCN)

LPF1

OUTPUT

IRQ

AN,

BN,

CN

1.0

0.908

GAIN[6:5]

×1, ×2, ×4

PGA

every time a zero crossing is detected on its associated input.

The default value of ZXTOUT is 0xFFFF. If the internal register

decrements to 0 before a zero crossing at the corresponding

input is detected, it indicates an absence of a zero crossing in

the time determined by the ZXTOUT[15:0]. The ZXTOx

detection bit of the corresponding phase in the interrupt status

register is then switched on (Bit 6 to Bit 8). An active low on the

output also appears if the ZXTOx mask bit for the

IRQ

corresponding phase in the interrupt mask register is set to

Logic 1. shows the mechanism of the zero-crossing

Figure 52

timeout detection when the Line Voltage A stays at a fixed dc

level for more than 384/CLKIN × ZXTOUT[15:0] seconds.

16-BIT INTERNAL

REGISTER VALUE

ZXTOUT[15:0]

VOLTAGE

CHANNEL A

READ RSTATUS

Figure 51. Zero-Crossing Detection on Voltage Channels

The zero-crossing interrupt is generated from the output of

LPF1. LPF1 has a single pole at 260 Hz (CLKIN = 10 MHz). As

a result, there is a phase lag between the analog input signal of

the voltage channel and the output of LPF1. The phase response

of this filter is shown in the Voltage Channel Sampling section.

The phase lag response of LPF1 results in a time delay of

approximately 1.1 ms (at 60 Hz) between the zero crossing on

the voltage inputs and the resulting zero-crossing signal. Note

that the zero-crossing signal is used for the line cycle

accumulation mode, zero-crossing interrupt, and line

period/frequency measurement.

When one phase crosses from negative to positive, the

corresponding flag in the interrupt status register (Bit 9 to

Bit 11) is set to Logic 1. An active low in the

output also

IRQ

appears if the corresponding ZX bit in the interrupt mask

register is set to Logic 1. Note that only zero crossing from

negative to positive generates an interrupt.

The flag in the interrupt status register is reset to 0 when the

interrupt status register with reset (RSTATUS) is read. Each

phase has its own interrupt flag and mask bit in the interrupt

register.

Zero-Crossing Timeout

Each zero-crossing detection has an associated internal timeout

register (not accessible to the user). This unsigned, 16-bit

register is decreased by 1 every 384/CLKIN seconds. The

registers are reset to a common user-programmed value, that is,

the zero-crossing timeout register (ZXTOUT[15:0], Address 0x1B),

04443-051

ZXTOA

DETECTION BIT

Figure 52. Zero-Crossing Timeout Detection

READ

RSTATUS

04443-052

PHASE COMPENSATION

When the HPF in the current channel is disabled, the phase

error between the current channel (IA, IB, or IC) and the

corresponding voltage channel (VA, VB, or VC) is negligible.

When the HPF is enabled, the current channels have phase

response (see Figure 53 through Figure 55). The phase response

is almost 0 from 45 Hz to 1 kHz. The frequency band is sufficient

for the requirements of typical energy measurement applications.

However, despite being internally phase compensated, the

ADE7758 must work with transducers that may have inherent

phase errors. For example, a current transformer (CT) with a

phase error of 0.1° to 0.3° is not uncommon. These phase errors

can vary from part to part, and they must be corrected to

perform accurate power calculations.

The errors associated with phase mismatch are particularly

noticeable at low power factors. The ADE7758 provides a

means of digitally calibrating these small phase errors. The

ADE7758 allows a small time delay or time advance to be

introduced into the signal processing chain to compensate for

the small phase errors.

The phase calibration registers (APHCAL, BPHCAL, and

CPHCAL) are twos complement, 7-bit sign-extended registers

that can vary the time advance in the voltage channel signal

path from +153.6 µs to −75.6 µs (CLKIN = 10 MHz),

Rev. E | Page 23 of 72

ADE7758 Data Sheet

respectively. Negative values written to the PHCAL registers

represent a time advance, and positive values represent a time

delay. One LSB is equivalent to 1.2 µs of time delay or 2.4 µs of

time advance with a CLKIN of 10 MHz. With a line frequency

of 60 Hz, this gives a phase resolution of 0.026° (360° × 1.2 µs ×

60 Hz) at the fundamental in the positive direction (delay) and

0.052° in the negative direction (advance). This corresponds to

a total correction range of −3.32° to +1.63° at 60 Hz.

Figure 56 illustrates how the phase compensation is used to

remove a 0.1° phase lead in IA of the current channel from the

external current transducer. To cancel the lead (0.1°) in the

current channel of Phase A, a phase lead must be introduced

into the corresponding voltage channel. The resolution of the

phase adjustment allows the introduction of a phase lead of

0.104°. The phase lead is achieved by introducing a time

advance into VA. A time advance of 4.8 µs is made by writing

−2 (0x7E) to the time delay block (APHCAL[6:0]), thus

reducing the amount of time delay by 4.8 µs or equivalently,

360° × 4.8 µs × 60 Hz = 0.104° at 60 Hz.

90

80

70

60

50

40

PHASE (Degrees)

30

20

10

0

0 100 200 300 400 500 600 700 800 1k900

FREQUENCY (Hz)

Figure 53. Phase Response of the HPF and Phase Compensation

(10 Hz to 1 kHz)

04443-053

0.20

0.15

0.10

0.05

PHASE (Degrees)

0

–0.05

–0.10

40 706560555045

FREQUENCY (Hz)

Figure 54. Phase Response of the HPF and Phase Compensation

(40 Hz to 70 Hz)

0.10

0.08

0.06

0.04

0.02

PHASE (Degrees)

0

–0.02

44 565452504846

FREQUENCY (Hz)

Figure 55. Phase Response of HPF and Phase Compensation

(44 Hz to 56 Hz)

04443-054

04443-055

Rev. E | Page 24 of 72

Data Sheet ADE7758

S

IAP

PGA1

IA

IAN

VAP

PGA2

VA

VN

VA

IA

ADC

ADC

0.1°

60Hz

HPF

RANGE OF PHASE

CALIBRATION

+1.36°, –2.76° @ 50Hz; 0.022°, 0. 043°

+1.63°, –3.31° @ 60Hz; 0.026°, 0. 052°

60

1111100

APHCAL[6:0]

–153.6µ s TO +75.6µs

Figure 56. Phase Calibration on Voltage Channels

PERIOD MEASUREMENT

The ADE7758 provides the period or frequency measurement

of the line voltage. The period is measured on the phase

specified by Bit 0 to Bit 1 of the MMODE register. The period

register is an unsigned 12-bit FREQ register and is updated

every four periods of the selected phase.

Bit 7 of the LCYCMODE selects whether the period register

displays the frequency or the period. Setting this bit causes the

register to display the period. The default setting is logic low,

which causes the register to display the frequency.

When set to measure the period, the resolution of this register is