Analog Devices AD7703 e Datasheet

LC2MOS

20-Bit A/D Converter

AD7703

FEATURES

Monolithic 16-Bit ADC

0.0015% Linearity Error

On-Chip Self-Calibration Circuitry

Programmable Low-Pass Filter

0.1 Hz to 10 Hz Corner Frequency

0 V to +2.5 V or ⴞ2.5 V Analog Input Range

4 kSPS Output Data Rate

Flexible Serial Interface

Ultralow Power

APPLICATIONS

Industrial Process Control

Weigh Scales

Portable Instrumentation

Remote Data Acquisition

GENERAL DESCRIPTION

The AD7703 is a 20-bit ADC that uses a S-D conversion technique. The analog input is continuously sampled by an analog

modulator whose mean output duty cycle is proportional to the

input signal. The modulator output is processed by an on-chip

digital filter with a six-pole Gaussian response, which updates the

output data register with 16-bit binary words at word rates up to

4kHz. The sampling rate, filter corner frequency, and output

word rate are set by a master clock input that may be supplied

externally, or by a crystal controlled on-chip clock oscillator.

The inherent linearity of the ADC is excellent and endpoint accuracy is ensured by self-calibration of zero and full scale, which

may be initiated at any time. The self-calibration scheme can

also be extended to null system offset and gain errors in the input

channel.

The output data is accessed through a flexible serial port, which

has an asynchronous mode compatible with UARTs and two

synchronous modes suitable for interfacing to shift registers or

the serial ports of industry-standard microcontrollers.

CMOS construction ensures low power dissipation, and a powerdown mode reduces the idle power consumption to only 10 µW.

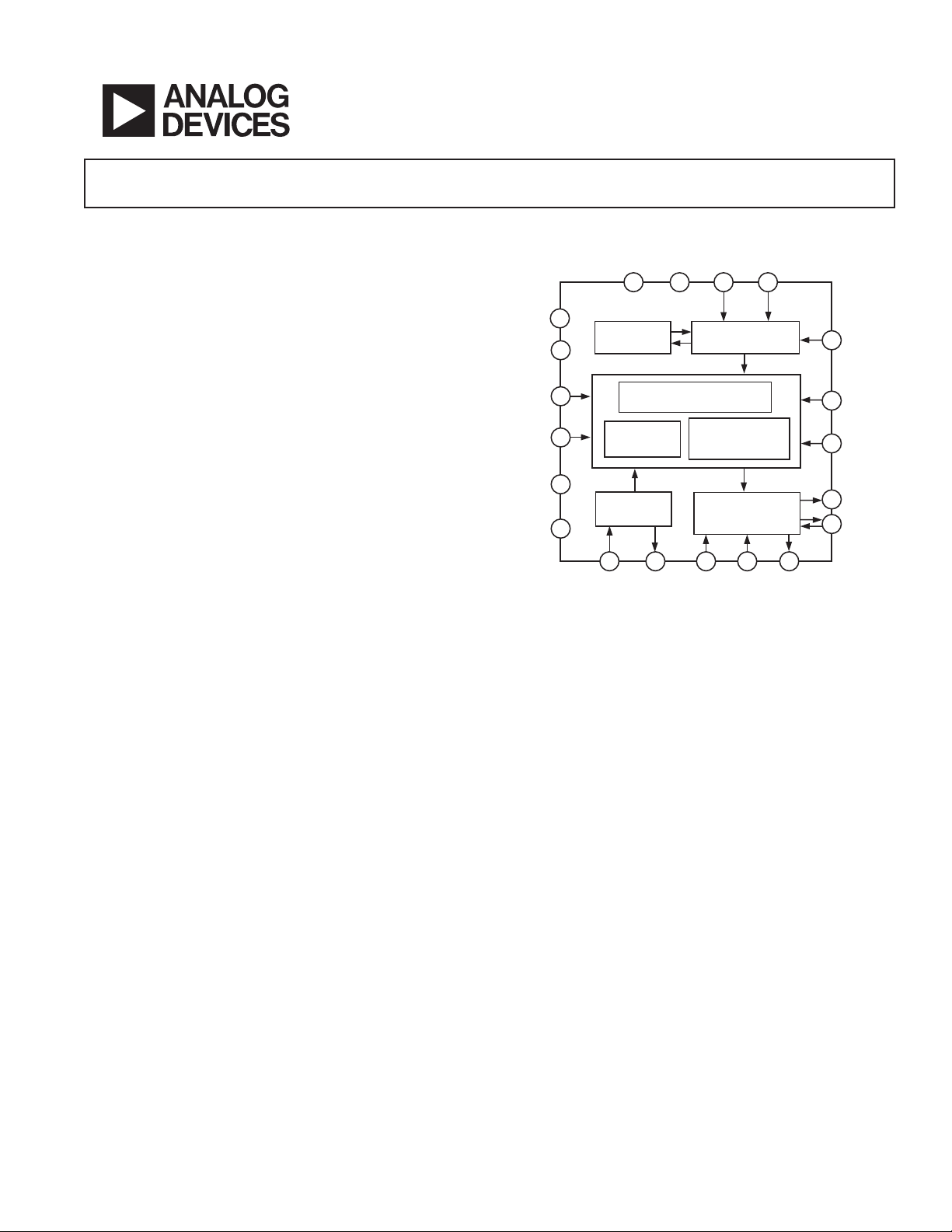

FUNCTIONAL BLOCK DIAGRAM

AV

DV

SC1 SC2

SS

4 17

CALIBRATION

MICROCONTROLLER

6-POLE GAUSSIAN

LOW-PASS

DIGITAL FILTER

SERIAL INTERFACE

LOGIC

MODE

CS DRDY

13

12

11

20

19

CAL

BP/UP

SLEEP

SDATA

SCLK

DV

AV

A

V

REF

AGND

DGND

SS

7 6

AD7703

15

DD

14

DD

IN

10

9

8

5

CALIBRATION

SRAM

20-BIT CHARGE BALANCE A/D

CONVERTER

ANALOG

MODULATOR

CLOCK

GENERATOR

2 18

3 161

CLKIN CLKOUT

PRODUCT HIGHLIGHTS

1. The AD7703 offers 20-bit resolution coupled with outstanding

0.0003% accuracy.

2. No missing codes ensures true, usable, 20-bit dynamic range,

removing the need for programmable gain and level-setting

circuitry.

3. The effects of temperature drift are eliminated by on-chip

self-calibration, which removes zero and gain error. External

circuits can also be included in the calibration loop to remove

system offsets and gain errors.

4. Flexible synchronous/asynchronous interface allows the

AD7703 to interface directly to the serial ports of industrystandard microcontrollers and DSP processors.

5. Low operating power consumption and an ultralow power

standby mode make the AD7703 ideal for loop-powered

remote sensing applications, or battery-powered portable

instruments.

REV. E

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

AD7703–SPECIFICATIONS

(TA = 25ⴗC; AVDD = DVDD = +5 V; AVSS = DVSS = –5 V; V

= +2.5 V; f

REF

CLKIN

BP/UP = +5 V; MODE = +5 V; AIN Source Resistance = 1 k⍀1 with 1 nF to AGND at AIN; unless otherwise noted.)

Parameter A/S Version

2

B Version

STATIC PERFORMANCE

Resolution 20 20 20 Bits

Integral Nonlinearity, T

25°C ±0.003 ±0.0015 ±0.0008 % FSR max

T

to T

MIN

Differential Nonlinearity, T

MAX

Positive Full-Scale Error

Full-Scale Drift

4

Unipolar Offset Error

Unipolar Offset Drift

Bipolar Zero Error

Bipolar Zero Drift

to T

MIN

to T

MIN

3

3

4

3

4

±0.0015 ±0.0007 ±0.0003 % FSR typ

MAX

±0.003 ±0.0015 ±0.0012 % FSR max

±0.5 ±0.5 ±0.5 LSB typ Guaranteed No Missing Codes

MAX

±4 ±4 ±4 LSB typ

±16 ±16 ±16 LSB max

±19/±37 ±19 ±19 LSB typ

±4 ±4 ±4 LSB typ

±16 ±16 ±16 LSB max

±26 ±26 ±26 LSB typ Temp Range: 0°C to +70°C

±67 +48/–400 ±67 ±67 LSB typ Specified Temp Range

±4 ±4 ±4 LSB typ

±16 ±16 ±16 LSB max

±13 ±13 ±13 LSB typ Temp Range: 0°C to +70°C

±34 +24/–200 ±34 ±34 LSB typ Specified Temp Range

Bipolar Negative Full-Scale Errors3±8 ±8 ±8 LSB typ

±32 ±32 ±32 LSB max

Bipolar Negative Full-Scale Drift4±10/±20 ±10 ±10 LSB typ

Noise (Referred to Output) 1.6 1.6 1.6 LSB rms typ

DYNAMIC PERFORMANCE

Sampling Frequency, f

Output Update Rate, f

Filter Corner Frequency, f

Settling Time to ±0.0007% FS 507904/f

S

OUT

–3 dB

f

/256 f

CLKIN

f

/1024 f

CLKIN

f

/409,600 f

CLKIN

CLKIN

CLKIN

CLKIN

CLKIN

507904/f

SYSTEM CALIBRATION

Positive Full-Scale Calibration Range V

Positive Full-Scale Overrange V

Negative Full-Scale Overrange –(V

Maximum Offset Calibration Ranges

Unipolar Input Range – (V

Bipolar Input Range –0.4 V

Input Span

7

+ 0.1 V

REF

+ 0.1 V

REF

REF

5, 6

REF

0.8 V

REF

2 V

REF

+ 0.1) –(V

+ 0.1) –(V

to +0.4 V

REF

REF

–0.4 V

0.8 V

+ 0.2 2 V

ANALOG INPUT

Unipolar Input Range 0 to 2.5 0 to 2.5 0 to 2.5 V

Bipolar Input Range ±2.5 ±2.5 ±2.5 V

Input Capacitance 20 20 20 pF typ

Input Bias Current

1

111nA typ

LOGIC INPUTS

All Inputs Except CLKIN

V

, Input Low Voltage 0.8 0.8 0.8 V max

INL

V

, Input High Voltage 2.0 2.0 2.0 V min

INH

CLKIN

V

, Input Low Voltage 0.8 0.8 0.8 V max

INL

V

, Input High Voltage 3.5 3.5 3.5 V min

INH

IIN, Input Current 10 10 10 µA max

LOGIC OUTPUTS

VOL, Output Low Voltage 0.4 0.4 0.4 V max I

VOH, Output High Voltage DV

Floating State Leakage Current ±10 ±10 ±10 µA max

– 1DV

DD

Floating State Output Capacitance 999pF typ

POWER REQUIREMENTS

Power Supply Voltages

Analog Positive Supply (AVDD) 4.5/5.5 4.5/5.5 4.5/5.5 V min/V max For Specified Performance

Digital Positive Supply (DVDD) 4.5/AV

Analog Negative Supply (AVSS) –4.5/–5.5 –4.5/–5.5 –4.5/–5.5 V min/V max

DD

4.5/AV

Digital Negative Supply (DVSS) –4.5/–5.5 –4.5/–5.5 –4.5/–5.5 V min/V max

Calibration Memory Retention

Power Supply Voltage 2.0 2.0 2.0 V min

2

/256 f

/1024 f

/409,600 f

CLKIN

+ 0.1 V

REF

+ 0.1 V

REF

+ 0.1) –(V

REF

+ 0.1) –(V

REF

to +0.4 V

REF

REF

+ 0.2 2 V

REF

– 1DV

DD

DD

REF

C Version

/256 Hz

CLKIN

/1024 Hz

CLKIN

/409,600 Hz

CLKIN

507904/f

+ 0.1 V max System calibration applies to

REF

+ 0.1 V max unipolar and bipolar ranges.

REF

+ 0.1) V max After calibration, if A

REF

+ 0.1) V max If AIN < 0 (unipolar) or –V

REF

–0.4 V

REF

0.8 V

REF

+ 0.2 V max

REF

– 1V min I

DD

4.5/AV

DD

2

CLKIN

to +0.4 V

Unit Test Conditions/Comments

sec For Full-Scale Input Step

the device will output all 1s.

V max (bipolar), the device will

REF

V min output all 0s.

= 1.6 mA

SINK

= 100 µA

SOURCE

V min/V max

= 4.096 MHz;

> V

IN

REF

REF

,

REV. E–2–

AD7703

Parameter A/S Version

POWER REQUIREMENTS

DC Power Supply Currents

Analog Positive Supply (AIDD) 2.7 2.7 2.7 mA max Typically 2 mA

Digital Positive Supply (DIDD)2 22mA max Typically 1 mA

Analog Negative Supply (AISS) 2.7 2.7 2.7 mA max Typically 2 mA

Digital Negative Supply (DISS) 0.1 0.1 0.1 mA max Typically 0.03 mA

Power Supply Rejection

Positive Supplies 70 70 70 dB typ

Negative Supplies 75 75 75 dB typ

Power Dissipation

Normal Operation 37 37 37 mW max SLEEP = Logic 1,

Standby Operations

A, B, C 20 20 20 µW max Typically 10 µW

S404040µW max

NOTES

1

The AIN pin presents a very high impedance dynamic load that varies with clock frequency. A ceramic 1 nF capacitor from the AIN pin to AGND is necessary.

Source resistance should be 750 or less.

2

Temperature ranges are as follows: A, B, C Versions: –40°C to +85°C; S Version: –55°C to +125°C.

3

Applies after calibration at the temperature of interest. Full-scale error applies for both unipolar and bipolar input ranges.

4

Total drift over the specified temperature range after calibration at power-up at 25°C. This is guaranteed by design and/or characterization. Recalibration at any

temperature will remove these errors.

5

In Unipolar mode, the offset can have a negative value (–V

6

The specifications for input overrange and for input span apply additional constraints on the offset calibration range.

7

For Unipolar mode, input span is the difference between full scale and zero scale. For Bipolar mode, input span is the difference between positive and negative full-scale

points. When using less than the maximum input span, the span range may be placed anywhere within the range of ± (V

8

All digital outputs unloaded. All digital inputs at 5 V CMOS levels.

9

Applies in 0.1 Hz to 10 Hz bandwidth. PSRR at 60 Hz will exceed 120 dB due to the digital filter.

10

CLKIN is stopped. All digital inputs are grounded.

Specifications subject to change without notice.

8

9

10

2

B Version

) such that the Unipolar mode can mimic Bipolar mode operation.

REF

2

C Version

2

Unit Test Conditions/Comments

Typically 25 mW

SLEEP = Logic 0,

+ 0.1).

REF

ABSOLUTE MAXIMUM RATINGS

(TA = 25°C, unless otherwise noted.)

1

DVDD to AGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

to AVDD . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

DV

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –6 V

DV

SS

AV

to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +6 V

DD

to AGND . . . . . . . . . . . . . . . . . . . . . . . . +0.3 V to –6 V

AV

SS

AGND to DGND . . . . . . . . . . . . . . . . . . . . . –0.3 V to +0.3 V

Digital Input Voltage to DGND . . . . –0.3 V to DV

Analog Input Voltage to AGND . . . AV

Input Current to Any Pin Except Supplies

– 0.3 V to AVDD + 0.3 V

SS

2

. . . . . . . . ± 10 mA

+ 0.3 V

DD

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause

permanent damage to the device. This is a stress rating only; functional operation

of the device at these or any other conditions above those listed in the

operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

2

Transient currents of up to 100 mA will not cause SCR latch-up.

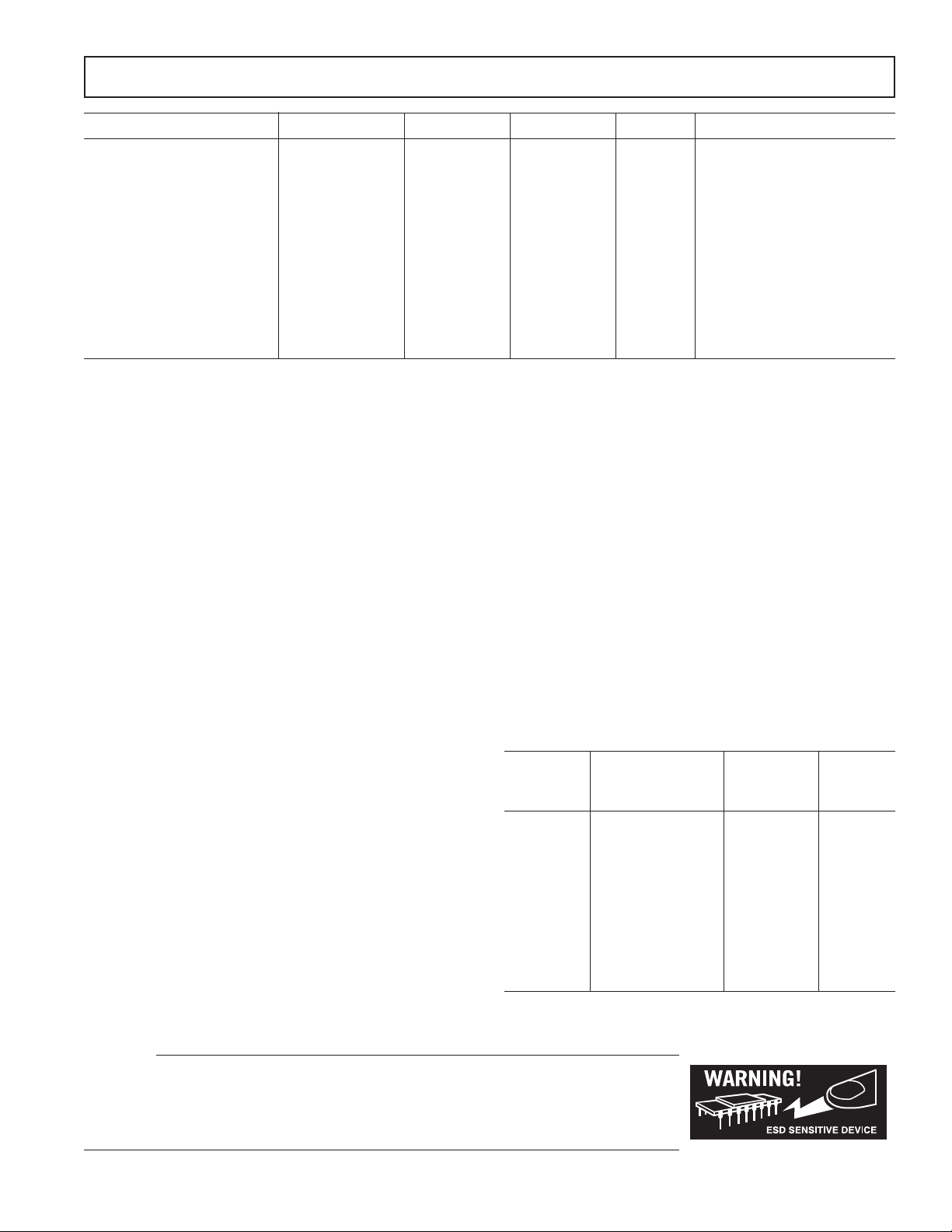

ORDERING GUIDE

Temperature Error Package

Model Range (% FSR) Options*

Operating Temperature Range

Industrial (A, B, C Versions) . . . . . . . . . . . –40°C to +85°C

Extended (S Version) . . . . . . . . . . . . . . . . –55°C to +125°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . . . 300°C

Power Dissipation (DIP Package) to 75°C . . . . . . . . . 450 mW

Derates above 75°C by . . . . . . . . . . . . . . . . . . . . . 10 mW/°C

Power Dissipation (SOIC Package) to 75°C . . . . . . . 250 mW

Derates above 75°C by . . . . . . . . . . . . . . . . . . . . . . 15 mW/°C

AD7703AN –40°C to +85°C 0.003 N-20

AD7703BN –40°C to +85°C 0.0015 N-20

AD7703CN –40°C to +85°C 0.0012 N-20

AD7703AR –40°C to +85°C 0.003 R-20

AD7703BR –40°C to +85°C 0.0015 R-20

AD7703CR –40°C to +85°C 0.0012 R-20

AD7703AQ –40°C to +85°C 0.003 Q-20

AD7703BQ –40°C to +85°C 0.0015 Q-20

AD7703CQ –40°C to +85°C 0.0012 Q-20

AD7703SQ –55°C to +125°C 0.003 Q-20

*N = Plastic DIP; R = SOIC; Q = CERDIP.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD7703 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

Linearity

REV. E

–3–

AD7703

TIMING CHARACTERISTICS

(AVDD = DVDD = +5 V ⴞ 10%; AVSS = DVSS = –5 V ⴞ 10%; AGND = DGND = O V;

1, 2

f

= 4.096 MHz; Input Levels: Logic O = O V, Logic 1 = DVDD; unless otherwise noted.)

CLKIN

Limit at T

MIN

, T

MAX

Limit at T

MIN

, T

MAX

Parameter (A, B Versions) (S, T Versions) Unit Conditions/Comments

3, 4

f

CLKIN

200 200 kHz min Master Clock Frequency: Internal Gate Oscillator

55MHz max Typically 4.096 MHz

200 200 kHz min Master Clock Frequency: Externally Supplied

5

t

r

5

t

f

t

1

t

2

6

t

3

SSC MODE

7

t

4

t

5

t

6

7

t

8

8

t

9

8, 9

t

10

55MHz max

50 50 ns max Digital Output Rise Time. Typically 20 ns.

50 50 ns max Digital Output Fall Time. Typically 20 ns.

00ns min SC1, SC2 to CAL High Setup Time

50 50 ns min SC1, SC2 Hold Time after CAL Goes High

1000 1000 ns min SLEEP High to CLKIN High Setup Time

3/f

CLKIN

3/f

CLKIN

ns max Data Access Time (CS Low to Data Valid)

100 100 ns max SCLK Falling Edge to Data Valid Delay (25 ns typ)

250 250 ns min MSB Data Setup Time. Typically 380 ns.

300 300 ns max SCLK High Pulsewidth. Typically 240 ns.

790 790 ns max SCLK Low Pulsewidth. Typically 730 ns.

l/f

+ 200 l/f

CLKIN

4/f

+ 200 4/f

CLKIN

+ 200 ns max SCLK Rising Edge to Hi-Z Delay (l/f

CLKIN

+ 200 ns max CS High to Hi-Z Delay

CLKIN

+ 100 ns typ)

CLKIN

SEC MODE

f

SCLK

t

11

t

12

7, 10

t

13

11

t

14

8

t

15

8

t

16

NOTES

1

Sample tested at 25°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

2

See Figures 1 to 6.

3

CLKIN duty cycle range is 20% to 80%. CLKIN must be supplied whenever the AD7703 is not in SLEEP mode. If no clock is present in this case, the device

can draw higher current than specified and possibly become uncalibrated.

4

The AD7703 is production tested with f

5

Specified using 10% and 90% points on waveform of interest.

6

In order to synchronize several AD7703s together using the SLEEP pin, this specification must be met.

7

t4 and t13 are measured with the load circuit of Figure 1 and defined as the time required for an output to cross 0.8 V or 2.4 V.

8

t9, t10, t15, and t16 are derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number

is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the time quoted in the Timing Characteristics is

the true bus relinquish time of the part and as such is independent of external bus loading capacitance.

9

If CS is returned high before all 20 bits are output, the SDATA and SCLK outputs will complete the current data bit and then go to high impedance.

10

If CS is activated asynchronously to DRDY, CS will not be recognized if it occurs when DRDY is high for four clock cycles. The propagation delay time may be

as great as four CLKIN cycles plus 160 ns. To guarantee proper clocking of SDATA when using asynchronous CS, the SCLK input should not be taken high

sooner than four CLKIN cycles plus 160 ns after CS goes low.

11

SDATA is clocked out on the falling edge of the SCLK input.

Specifications subject to change without notice.

55MHz max Serial Clock Input Frequency

35 35 ns min SCLK Input High Pulsewidth

160 160 ns min SCLK Low Pulsewidth

160 160 ns max Data Access Time (CS Low to Data Valid). Typically 80 ns.

150 150 ns max SCLK Falling Edge to Data Valid Delay. Typically 75 ns.

250 250 ns max CS High to Hi-Z Delay

200 200 ns max SCLK Falling Edge to Hi-Z Delay. Typically 100 ns.

at 4.096 MHz. It is guaranteed by characterization to operate at 200 kHz.

CLKIN

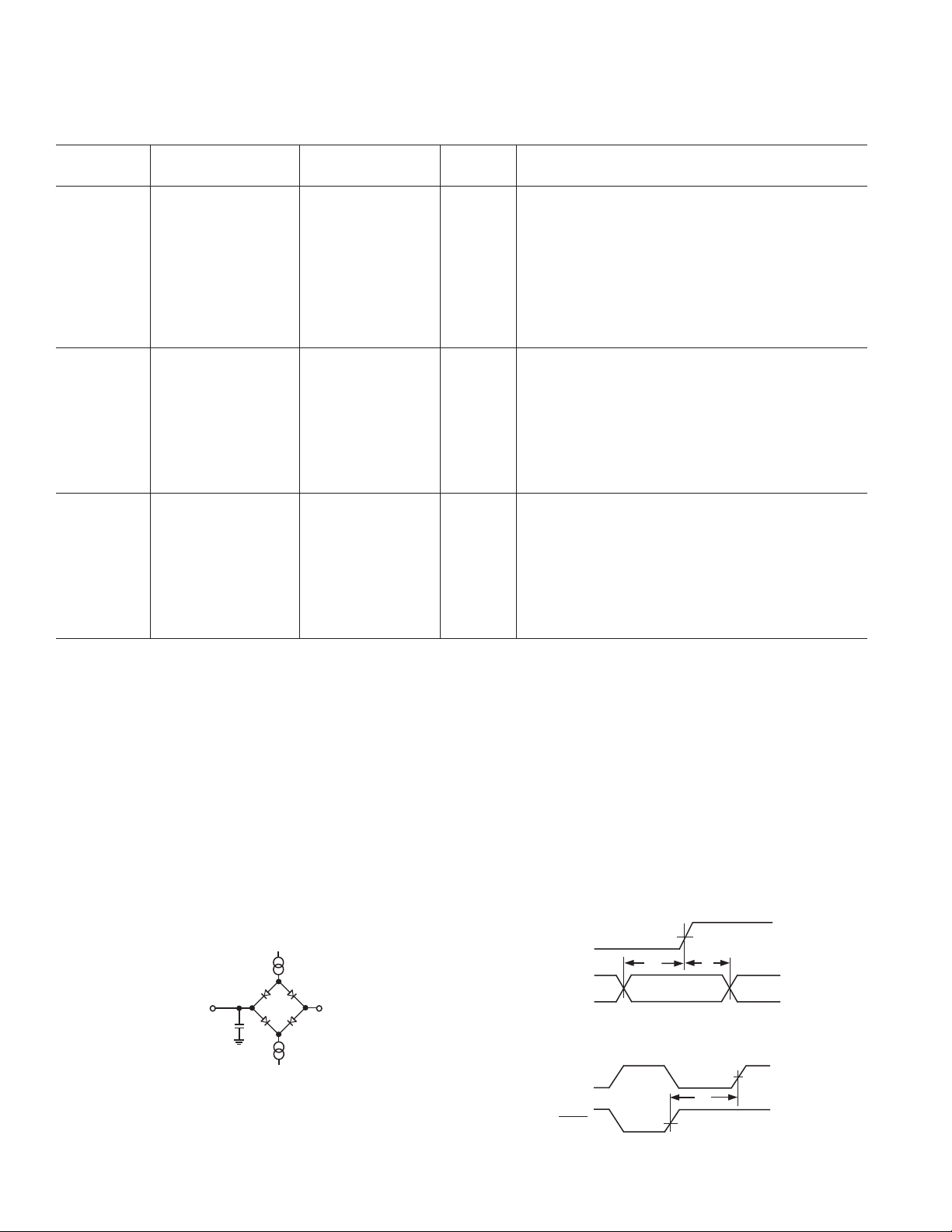

I

OL

1.6mA

OUTPUT

PIN

TO

100pF

C

L

I

OH

200A

+

2.1V

Figure 1. Load Circuit for Access Time

and Bus Relinquish Time

CAL

t

SC1, SC2

t

1

SC1, SC2 VALID

2

Figure 2. Calibration Control Timing

CLKIN

t

3

SLEEP

Figure 3. Sleep Mode Timing

REV. E–4–

AD7703

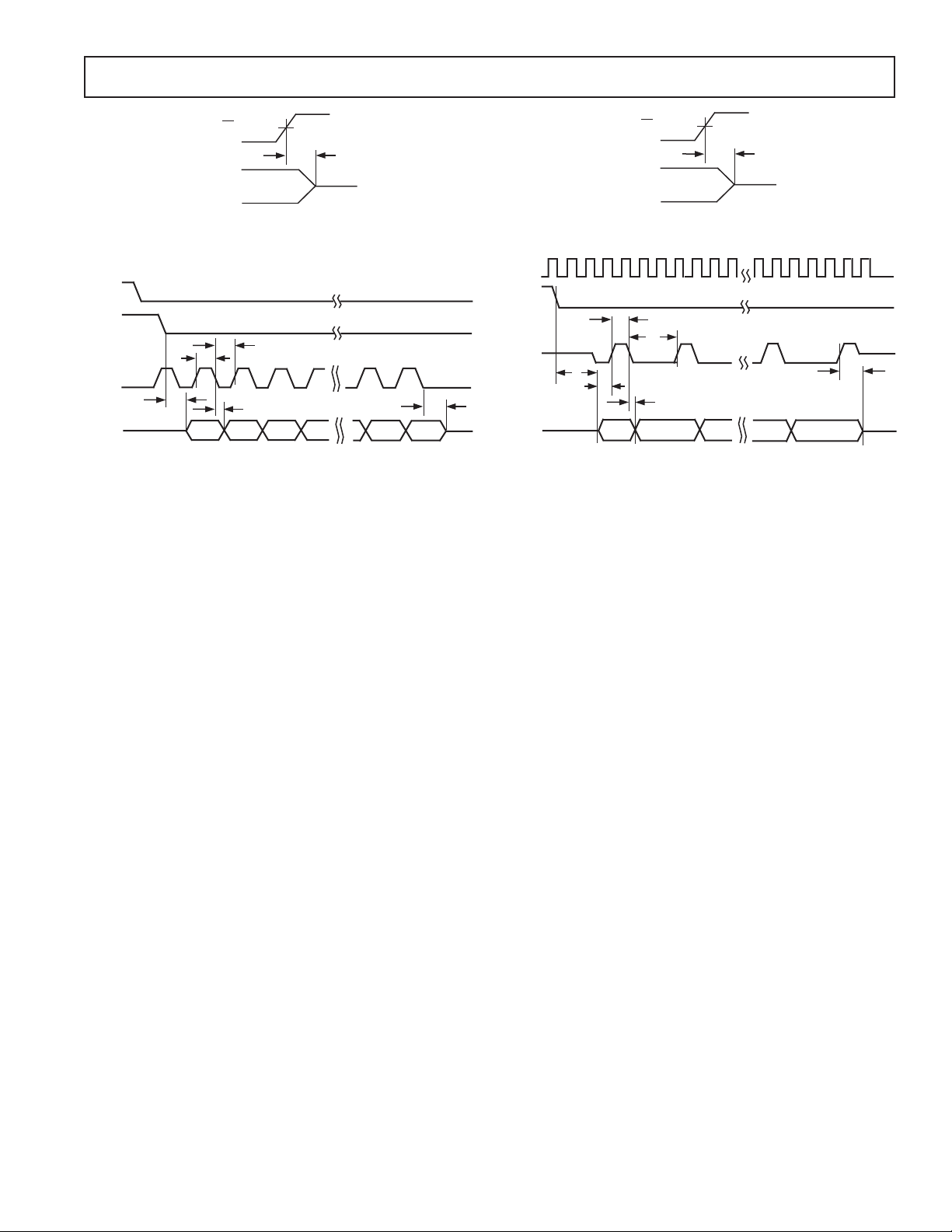

CS

t

10

SDATA

DATA

VA LI D

HI-Z

Figure 4. SSC Mode Data Hold Time

DRDY

CS

t

12

t

SCLK

SDATA

HI-Z

11

t

13

DB19

t

DB18

14

DB1

DB0

t

16

HI-Z

Figure 5a. SEC Mode Timing Diagram

DEFINITION OF TERMS

Linearity Error

This is the maximum deviation of any code from a straight line

passing through the endpoints of the transfer function. The

endpoints of the transfer function are zero-scale (not to be

confused with bipolar zero), a point 0.5 LSB below the first code

transition (000 . . . 000 to 000 . . . 001) and full-scale, a point

1.5 LSB above the last code transition (111 . . . 110 to 111 . . .

111). The error is expressed as a percentage of full scale.

Differential Linearity Error

This is the difference between any code’s actual width and the

ideal (1 LSB) width. Differential linearity error is expressed in

LSB. A differential linearity specification of ±1 LSB or less

guarantees monotonicity.

Positive Full-Scale Error

Positive full-scale error is the deviation of the last code transition

(111 . . . 110 to 111 . . . 111) from the ideal (V

± 3/2 LSB).

REF

It applies to both positive and negative analog input ranges and

is expressed in microvolts.

Unipolar Offset Error

Unipolar offset error is the deviation of the first code transition

from the ideal (AGND + 0.5 LSB) when operating in the

Unipolar mode.

Bipolar Zero Error

This is the deviation of the midscale transition (0111 . . . 111 to

1000 . . . 000) from the ideal (AGND – 0.5 LSB) when operating

in the Bipolar mode. It is expressed in microvolts.

Bipolar Negative Full-Scale Error

This is the deviation of the first code transition from the ideal

(–V

+ 0.5 LSB) when operating in the Bipolar mode.

REF

CS

t

15

SDATA

DATA

VA LI D

HI-Z

Figure 5b. SEC Mode Data Hold Time

CLKIN

CS

t

7

t

SCLK

SDATA

HI-Z

HI-Z

8

t

4

t

8

DB19

t

5

DB18

DB1 DB0

HI-Z

t

9

HI-Z

Figure 6. SSC Mode Timing Diagram

Positive Full-Scale Overrange

Positive full-scale overrange is the amount of overhead available

to handle input voltages greater than +V

(for example, noise

REF

peaks or excess voltages due to system gain errors in system

calibration routines) without introducing errors due to overloading

the analog modulator or overflowing the digital filter.

Negative Full-Scale Overrange

This is the amount of overhead available to handle voltages below

without overloading the analog modulator or overflowing

–V

REF

the digital filter. Note that the analog input will accept negative

voltage peaks even in the Unipolar mode.

Offset Calibration Range

In the system calibration modes (SC2 low), the AD7703 calibrates

its offset with respect to the A

pin. The offset calibration range

IN

specification defines the range of voltages, expressed as a

percentage of V

, that the AD7703 can accept and still accurately

REF

calibrate offset.

Full-Scale Calibration Range

This is the range of voltages that the AD7703 can accept in the

system calibration mode and still correctly calibrate full scale.

Input Span

In system calibration schemes, two voltages applied in sequence

to the AD7703’s analog input define the analog input range. The

input span specification defines the minimum and maximum

input voltages from zero to full scale that the AD7703 can accept

and still accurately calibrate gain. The input span is expressed

as a percentage of V

REF.

REV. E

–5–

Loading...

Loading...