Analog Devices AD767 Datasheet

Microprocessor-Compatible

a

FEATURES

Complete 12-Bit D/A Function

On-Chip Output Amplifier

High Stability Buried Zener Reference

Fast 40 ns Write Pulse

0.3" Skinny DIP and PLCC Packages

Single Chip Construction

Monotonicity Guaranteed Over Temperature

Settling Time: 3 ms max to 1/2 LSB

Guaranteed for Operation with 612 V or 615 V Supplies

TTL/5 V CMOS Compatible Logic Inputs

MIL-STD-883 Compliant Versions Available

PRODUCT DESCRIPTION

The AD767 is a complete voltage output 12-bit digital-toanalog converter including a high stability buried Zener

reference and input latch on a single chip. The converter uses

12 precision high-speed bipolar current steering switches and a

laser-trimmed thin-film resistor network to provide high accuracy.

Microprocessor compatibility is achieved by the on-chip latch.

The design of the input latch allows direct interface to 12-bit

buses. The latch responds to strobe pulses as short as 40 ns,

allowing use with the fastest available microprocessors.

The functional completeness and high performance of the

AD767 result from a combination of advanced switch design,

high-speed bipolar manufacturing process, and the proven laser

wafer-trimming (LWT) technology.

The subsurface (buried) Zener diode on the chip provides a

low-noise voltage reference which has long-term stability and

temperature drift characteristics comparable to the best discrete

reference diodes. The laser trimming process which provides the

excellent linearity is also used to trim the absolute value of the

reference as well as its temperature coefficient. The AD767 is

thus well suited for wide temperature range performance with

±1/2 LSB maximum linearity error and guaranteed monotonicity

over the full temperature range. Typical full-scale gain T.C. is

5 ppm/°C.

12-Bit D/A Converter

AD767*

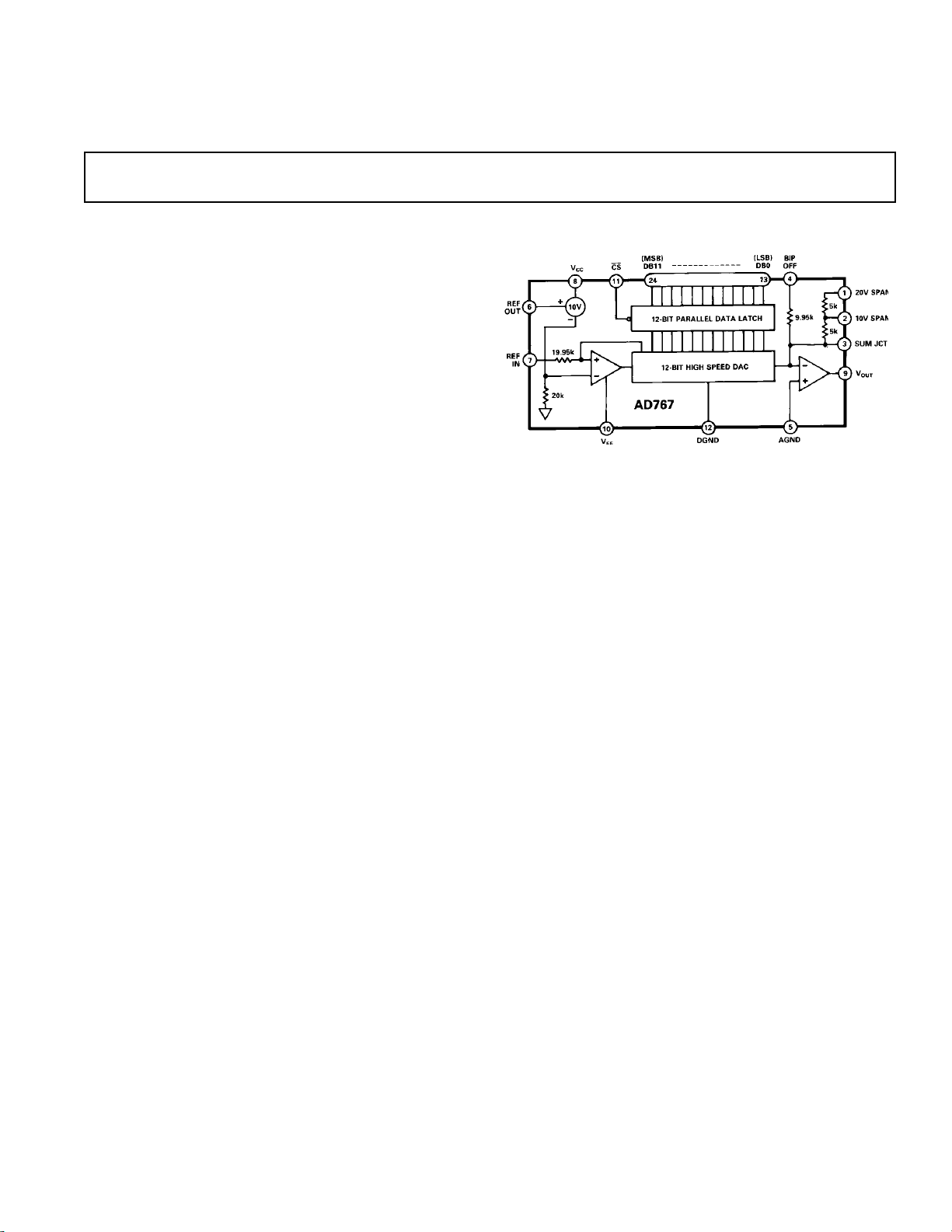

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1. The AD767 is a complete voltage output DAC with voltage

reference and digital latches on a single IC chip.

2. The input latch responds to write pulse widths as short as

40 ns assuring direct interface with the industry’s fastest

microprocessors.

3. The internal buried Zener reference is laser-trimmed to

10.00 volts with a ±1% maximum error. The reference

voltage is also available for external application.

4. The gain setting and bipolar offset resistors are matched to

the internal ladder network to guarantee a low gain temperature

coefficient and are laser trimmed for minimum full-scale and

bipolar offset errors.

5. The precision high-speed current steering switches and

on-board high-speed output amplifier settle within 1/2 LSB

for a 10 V full-scale transition in 3.0 µs when properly

compensated.

6. The AD767 is available in versions compliant with

MIL-STD-883. Refer to the Analog Devices Military

Products Databook or current AD767/883B data sheet for

detailed specifications.

*Protected by Patent Numbers 3,803,590; 3,890,611; 3,932,863; 3,978,473;

4,020,486; and others pending.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD767–SPECIFICATIONS

Model AD767J/A/S

(TA = +258C, 615 volt power supplies, Unipolar Mode, unless otherwise noted.)

1

AD767K/B AD767A2 Chips

Min Typ Max Min Typ Max Min Typ Max Units

DIGITAL INPUTS

Resolution 12 12 12 Bits

Logic Levels (TTL Compatible, T

MIN–TMAX

3

)

VIH (Logic “1”) +2.0 +5.5 +2.0 +5.5 +2.0 +5.5 V

VIL (Logic “0”) J, K, A, B 0 +0.8 0 +0.8 0 +0.8 V

VIL (Logic “0”) S 0 +0.7 V

IIH (VIH = 5.5 V) 3 10 3 10 3 10 µA

IIL (VIL = 0.8 V) 1 5 1 5 1 5 µA

TRANSFER CHARACTERISTICS

ACCURACY

Linearity Error @ +25°C ±1/2 61 ±1/8 61/2 ±1/2 61 LSB

TA = T

MIN

to T

MAX

±1/2 61 ±1/4 61/2 ±1/2 61 LSB

Differential Linearity Error @ +25°C ±1/2 61 ±1/4 61 ±1/2 61 LSB

TA = T

Gain Error

Unipolar Offset Error

Bipolar Zero Error

MIN

4

to T

MAX

4

Monotonicity Guaranteed Monotonicity Guaranteed Monotonicity Guaranteed LSB

4

±0.1 60.2 ±0.1 60.2 ± 0.1 60.2 % of FSR

±1 62 ±1 62 ±1 62 LSB

5

±0.05 60.1 ±0.05 60.1 ±0.05 60.1 % of FSR

DRIFT

Gain TA = 25°C to T

Unipolar Offset TA = 25°C to T

Bipolar Zero TA = 25°C to T

MIN

or T

MAX

MIN

MIN

or T

or T

MAX

MAX

±5 ±30 ±5 ±15 ±5 ±30 ppm of FSR/°C

±1 ±3 ±1 ±3 ±1 ±3 ppm of FSR/°C

±5 ±10 ±10 ±5 ±10 ppm of FSR/°C

CONVERSION SPEED

Settling Time to ±0.01% of FSR for

FSR change (2 kΩ||500 pF load)

with 10 kΩ Feedback 3 4 3 4 3 4 µs

with 5 kΩ Feedback 2 3 2 3 2 3 µs

For LSB Change 1 1 1 µs

Slew Rate 10 10 10 V/µs

ANALOG OUTPUT

Ranges

6

± 2.5, ±5, ±10, ±2.5, ± 5, ±10, ±2.5, ±5, ±10, V

+5, +10 +5, +10 +5, +10

Output Current ± 5 ± 5 ±5mA

Output Impedance (dc) 0.05 0.05 0.05 Ω

Short-Circuit Current 40 40 40 mA

REFERENCE OUTPUT 9.90 10.00 10.10 9.90 10.00 10.10 9.90 10.00 10.10 V

External Current 0.1 1.0 0.1 1.0 0.1 1.0 mA

POWER SUPPLY SENSITIVITY

VCC = +11.4 to +16.5 V dc 5 10 5 10 5 10 ppm of FS/%

V

= –11.4 to –16.5 V dc 5 10 5 10 5 10 ppm of FS/%

EE

POWER SUPPLY REQUIREMENTS

Rated Voltages ±12, ±15 ±12, ± 15 ±12, ± 15 V

6

Range

611.4 616.5 611.4 616.5 611.4 616.5 V

Supply Current

+11.4 to +16.5 V dc 9 13 9 13 9 13 mA

–11.4 to –16.5 V dc 18 23 18 23 18 23 mA

Total Power Consumption 400 600 400 600 400 600 mW

TEMPERATURE RANGE

J/K 0 +70 0 +70 °C

A/B –25 +85 –25 +85 –25 +85 °C

S –55 +125 –55 +125 °C

Operating –55 +125 –55 +125 °C

Storage (All Grades) –65 +125 –65 +125 –65 +125 °C

NOTES

1

AD767 “S” specifications shown for information only. Consult Analog Devices Military Databook or contact factory for a controlled specification sheet.

2

AD767A Chips specifications are tested at +25°C and, when in boldface, at +85°C. They are typical at –25°C.

3

The digital input specifications are 100% tested at +25°C, and guaranteed but not tested over the full temperature range.

4

Adjustable to zero.

5

FSR means “Full-Scale Range” and is 20 V for ±10 V range and 10 V for the ±5 V range.

6

A minimum power supply of ±12.5 V is required for a ± 10 V full-scale output and ±11.4 V is required for all other voltage ranges.

Specifications subject to change without notice.

Specifications shown in boldface are tested on all production units at final electrical test (except per Notes 1 and 2). Results from those tests are used to calculate

outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

–2–

REV. A

AD767

ABSOLUTE MAXIMUM RATINGS*

VCC to Power Ground . . . . . . . . . . . . . . . . . . . . .0 V to +18 V

V

to Power Ground . . . . . . . . . . . . . . . . . . . . . 0 V to –18 V

EE

Digital Inputs (Pins 11, 13–24)

to Power Ground . . . . . . . . . . . . . . . . . . . . –1.0 V to +7.0 V

Ref In to Reference Ground . . . . . . . . . . . . . . . . . . . . . . ±12 V

Bipolar Offset to Reference Ground . . . . . . . . . . . . . . . . ±12 V

10 V Span R to Reference Ground . . . . . . . . . . . . . . . . . ±12 V

20 V Span R to Reference Ground . . . . . . . . . . . . . . . . . ±24 V

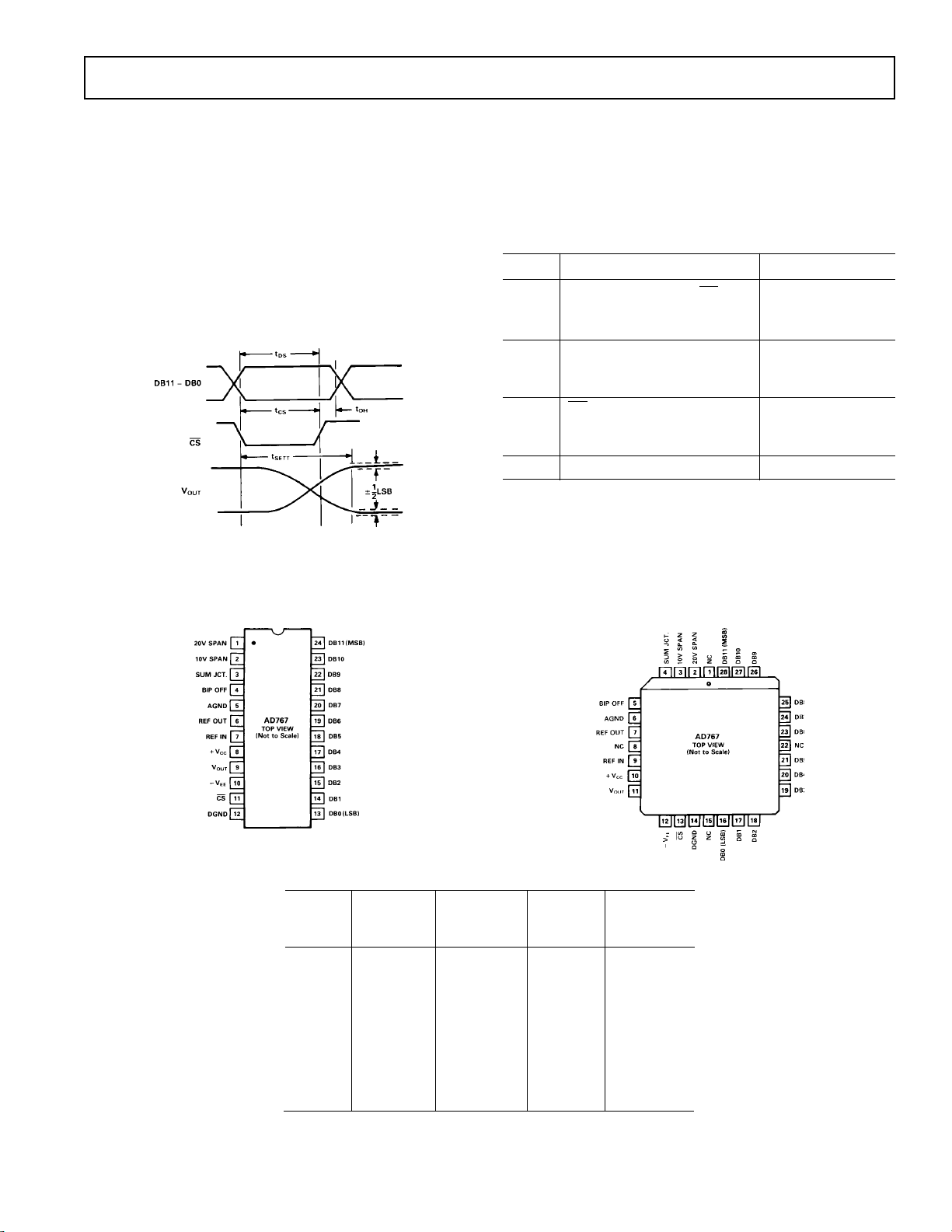

TIMING SPECIFICATIONS

(All Models, T

V

= –12 V or –15 V)

EE

= 25°C, V

A

= +12 V or +15 V,

CC

PIN CONFIGURATION

Ref Out, V

(Pins 6, 9) . . . Indefinite short to power ground

OUT

Momentary Short to V

CC

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . .1000 mW

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in

the operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

Symbol Parameter Min Typ Max

t

DS

Data Valid to End of CS 40 – – ns

(–25°C to +85°C) 60 – – ns

(–55°C to +125°C) 90 – – ns

t

DH

Data Hold Tiıne 10 – – ns

(–25°C to +85°C) 10 – – ns

(–55°C to +125°C) 20 – – ns

t

CS

CS Pulse Width 40 – – ns

(–25°C to +85°C) 60 – – ns

(–55°C to +125°C) 90 – – ns

t

SETT

*t

SETT

t

SETT

Output Voltage Settling Time* – 2 4 µs

is measured referenced to the leading edge of tCS. If tCS > tDS, then

is measured referenced to the beginning of Data Valid.

DIP

ORDERING GUIDE

Linearity Gain T.C.

Temperature Error Max Max

MIN–TMAX

ppm/8C

Model

1

Package Range 8CT

AD767JN Plastic DIP 0 to +70 ±1 LSB 30

AD767JP PLCC 0 to +70 ±1 LSB 30

AD767KN Plastic DIP 0 to +70 ±1/2 LSB 15

AD767KP PLCC 0 to +70 ±1/2 LSB 15

AD767AD Ceramic DIP –25 to +85 ±1 LSB 30

AD767BD Ceramic DIP –25 to +85 ±1/2 LSB 15

AD767SD/

883B Ceramic DIP –55 to +125 Note 2 Note 2

AD767A

Chips N/A –25 to +85 ±1 LSB 30

NOTES

1

D = Ceramic DIP; N = Plastic DIP; P = Plastic Leaded Chip Carrier.

2

For details on grade and package offerings screened in accordance with MIL-STD-883, refer to

the Analog Devices Military Products Databook or current AD767/883B data sheet.

PLCC

REV. A

–3–

Loading...

Loading...