a

16-Bit, 570 kSPS CMOS ADC

FEATURES

Throughput:

570 kSPS (Warp Mode)

500 kSPS (Normal Mode)

INL: ⴞ2.5 LSB Max (ⴞ0.0038% of Full-Scale)

16 Bits Resolution with No Missing Codes

S/(N+D): 90 dB Typ @ 45 kHz

THD: –100 dB Typ @ 45 kHz

Analog Input Voltage Range: 0 V to 2.5 V

Both AC and DC Specifications

No Pipeline Delay

Parallel and Serial 5 V/3 V Interface

TM

/QSPITM/MICROWIRETM/DSP Compatible

SPI

Single 5 V Supply Operation

Power Dissipation

115 mW Maximum,

21 W @ 100 SPS

Power-Down Mode: 7 W Max

Package: 48-Lead Quad Flat Pack (LQFP)

Pin-to-Pin Compatible Upgrade of the AD7660

APPLICATIONS

Data Acquisition

Instrumentation

Digital Signal Processing

Spectrum Analysis

Medical Instruments

Battery-Powered Systems

Process Control

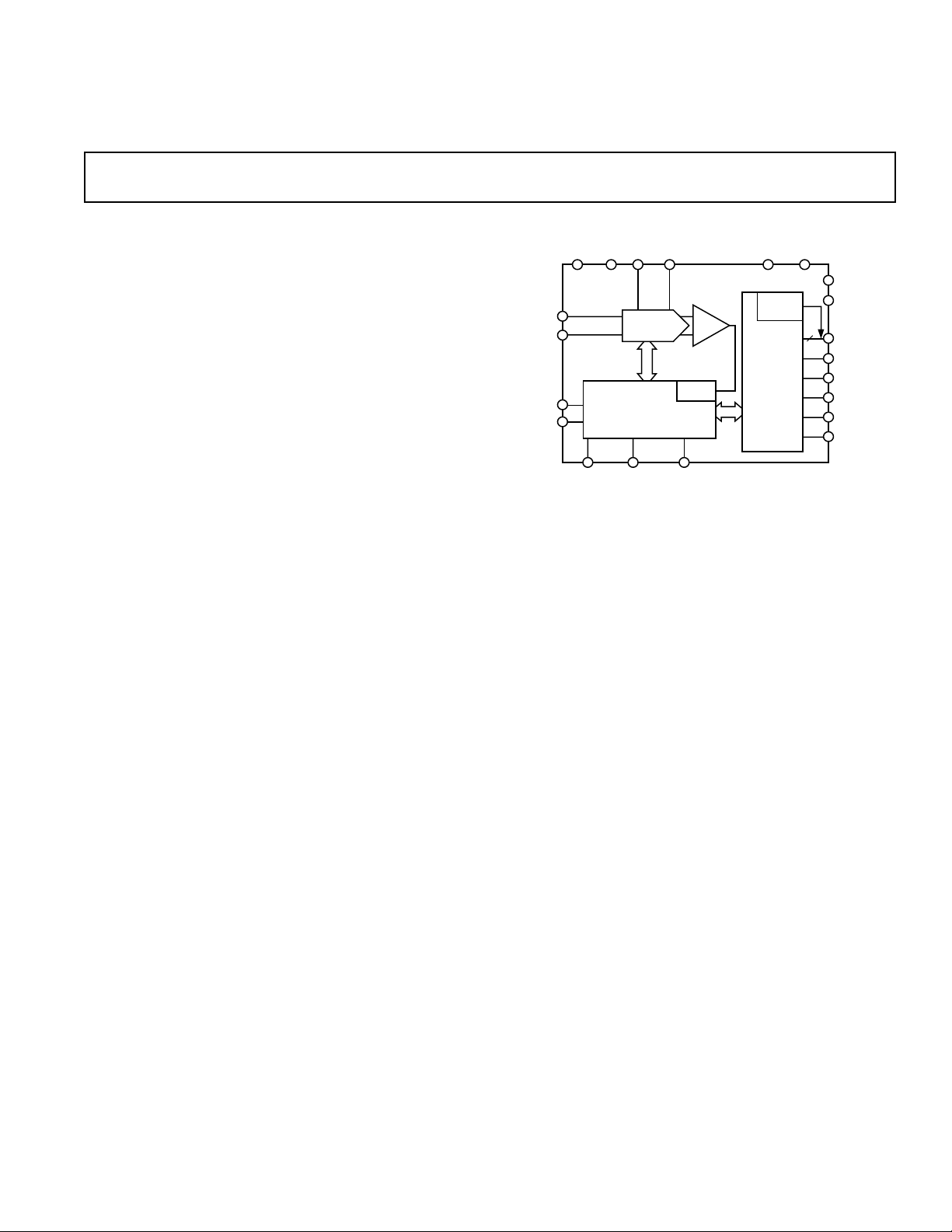

FUNCTIONAL BLOCK DIAGRAM

AVDD AGND REF REFGND

IN

INGND

PD

RESET

CALIBRATION CIRCUITRY

AD7664

SWITCHED

CAP DAC

CLOCK

CONTROL LOGIC AND

CNVSTWARP IMPULSE

AD7664

DGNDDVDD

SERIAL

PORT

16

PARALLEL

INTERFACE

*

OVDD

OGND

DATA[15:0]

BUSY

RD

CS

SER/PAR

OB/2C

GENERAL DESCRIPTION

The AD7664 is a 16-bit, 570 kSPS, charge redistribution SAR,

analog-to-digital converter that operates from a single 5 V power

supply. The part contains a high-speed 16-bit sampling ADC,

an internal conversion clock, error correction circuits, and both

serial and parallel system interface ports.

The AD7664 is hardware factory calibrated and is comprehensively

tested to ensure such ac parameters as signal-to-noise ratio (SNR)

and total harmonic distortion (THD), in addition to the more

traditional dc parameters of gain, offset, and linearity.

It features a very high sampling rate mode (Warp) and, for asynchronous conversion rate applications, a fast mode (Normal)

and, for low power applications, a reduced power mode (Impulse)

where the power is scaled with the throughput.

It is fabricated using Analog Devices’ high-performance, 0.6 micron

CMOS process, with correspondingly low cost and is available in a

48-lead LQFP with operation specified from –40°C to +85°C.

*Patent pending.

SPI and QSPI are trademarks of Motorola Inc.

MICROWIRE ia a trademark of National Semiconductor Corporation

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

PRODUCT HIGHLIGHTS

1. Fast Throughput

The AD7664 is a 570 kSPS, charge redistribution, 16-bit

SAR ADC with internal error correction circuitry.

2. Superior INL

The AD7664 has a maximum integral nonlinearity of 2.5 LSBs

with no missing 16-bit code.

3. Single-Supply Operation

The AD7664 operates from a single 5 V supply and dissipates

only a maximum of 115 mW. In impulse mode, its power

dissipation decreases with the throughput to, for instance, only

21 µW at a 100 SPS throughput. It consumes 7 µW maximum

when in power-down.

4. Serial or Parallel Interface

Versatile parallel or 2-wire serial interface arrangement

compatible with both 3 V or 5 V logic.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

AD7664

–SPECIFICATIONS

(–40ⴗC to +85ⴗC, AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V, unless otherwise noted.)

Parameter Conditions Min Typ Max Unit

RESOLUTION 16 Bits

ANALOG INPUT

Voltage Range V

Operating Input Voltage V

Analog Input CMRR fIN = 10 kHz 62 dB

IN

IN

V

INGND

– V

INGND

0V

–0.1 +3 V

REF

V

–0.1 +0.5 V

Input Current 570 kSPS Throughput 7 µA

Input Impedance See Analog Input Section

THROUGHPUT SPEED

Complete Cycle In Warp Mode 1.75 µs

Throughput Rate In Warp Mode 1 570 kSPS

Time Between Conversions In Warp Mode 1 ms

Complete Cycle In Normal Mode 2 µs

Throughput Rate In Normal Mode 0 500 kSPS

Complete Cycle In Impulse Mode 2.25 µs

Throughput Rate In Impulse Mode 0 444 kSPS

DC ACCURACY

Integral Linearity Error –2.5 +2.5 LSB

1

Differential Linearity Error –1 +1.5 LSB

No Missing Codes 16 Bits

Transition Noise 0.7 LSB

Full-Scale Error

Unipolar Zero Error

2

2

REF = 2.5 V ±0.08 % of FSR

±5 ±15 LSB

Power Supply Sensitivity AVDD = 5 V ± 5% ±3 LSB

AC ACCURACY

Signal-to-Noise f

Spurious Free Dynamic Range fIN = 45 kHz 100 dB

= 100 kHz 90 dB

IN

fIN = 100 kHz 100 dB

Total Harmonic Distortion fIN = 45 kHz –100 dB

fIN = 100 kHz –100 dB

Signal-to-(Noise+Distortion) fIN = 45 kHz 90 dB

fIN = 100 kHz 89 dB

–3 dB Input Bandwidth 18 MHz

–60 dB Input, f

= 100 kHz 30 dB

IN

SAMPLING DYNAMICS

Aperture Delay 2ns

Aperture Jitter 5 ps rms

Transient Response Full-Scale Step 250 ns

REFERENCE

External Reference Voltage Range 2.3 2.5 AVDD – 1.85 V

External Reference Current Drain 570 kSPS Throughput 115 µA

DIGITAL INPUTS

Logic Levels

V

IL

V

IH

I

IL

I

IH

–0.3 +0.8 V

2.0 OVDD + 0.3 V

–1 +1 µA

–1 +1 µA

DIGITAL OUTPUTS

Data Format Parallel or Serial 16-Bits

Pipeline Delay Conversion Results Available

Immediately after

Completed Conversion

V

OL

V

OH

I

= 1.6 mA 0.4 V

SINK

I

= –500 µA OVDD – 0.6 V

SOURCE

POWER SUPPLIES

Specified Performance

AVDD 4.75 5 5.25 V

DVDD 4.75 5 5.25 V

OVDD 2.7 5.25 V

Operating Current

AVDD 15.5 mA

5

DVDD

5

OVDD

Power Dissipation

4

500 kSPS Throughput

3.8 mA

5

500 kSPS Throughput

100 SPS Throughput

In Power-Down Mode

4

6

7

100 µA

115 mW

21 µW

7 µW

–2–

REV. C

AD7664

Parameter Conditions Min Typ Max Unit

TEMPERATURE RANGE

Specified Performance T

NOTES

1

LSB means Least Significant Bit. With the 0 V to 2.5 V input range, one LSB is 38.15 µV.

2

See Definition of Specifications section. These specifications do not include the error contribution from the external reference.

3

All specifications in dB are referred to a full-scale input FS. Tested with an input signal at 0.5 dB below full-scale unless otherwise specified.

4

In normal mode.

5

Tested in parallel reading mode.

6

In impulse mode.

7

With all digital inputs forced to OVDD or OGND respect

8

Contact factory for extended temperature range.

Specifications subject to change without notice.

8

MIN

to T

MAX

–40 +85

°C

ively.

TIMING SPECIFICATIONS

(–40ⴗC to +85ⴗC, AVDD = DVDD = 5 V, OVDD = 2.7 V to 5.25 V, unless otherwise noted.)

Symbol Min Typ Max Unit

REFER TO FIGURES 11 AND 12

Convert Pulsewidth t

Time Between Conversions t

(Warp Mode/Normal Mode/Impulse Mode)

CNVST LOW to BUSY HIGH Delay t

BUSY HIGH All Modes Except in t

Master Serial Read After Convert Mode

1

2

3

4

5ns

1.75/2/2.25 Note 1 µs

25 ns

1.5/1.75/2 µs

(Warp Mode/Normal Mode/Impulse Mode)

Aperture Delay t

End of Conversion to BUSY LOW Delay t

Conversion Time t

(Warp Mode/Normal Mode/Impulse Mode)

Acquisition Time t

RESET Pulsewidth t

5

6

7

8

9

10 ns

250 ns

10 ns

2ns

1.5/1.75/2 µs

REFER TO FIGURES 13, 14, AND 15 (Parallel Interface Modes)

CNVST LOW to DATA Valid Delay t

(Warp Mode/Normal Mode/Impulse Mode)

DATA Valid to BUSY LOW Delay t

Bus Access Request to DATA Valid t

Bus Relinquish Time t

REFER TO FIGURES 16 AND 17 (Master Serial Interface Modes)

CS LOW to SYNC Valid Delay t

CS LOW to Internal SCLK Valid Delay

2

CS LOW to SDOUT Delay t

CNVST LOW to SYNC Delay t

(Warp Mode/Normal Mode/Impulse Mode)

SYNC Asserted to SCLK First Edge Delay t

Internal SCLK Period t

Internal SCLK HIGH (INVSCLK Low)

Internal SCLK LOW (INVSCLK Low)

3

3

SDOUT Valid Setup Time t

SDOUT Valid Hold Time t

SCLK Last Edge to SYNC Delay t

CS HIGH to SYNC HI-Z t

CS HIGH to Internal SCLK HI-Z t

CS HIGH to SDOUT HI-Z t

BUSY HIGH in Master Serial Read after Convert t

(Warp Mode/Normal Mode/Impulse Mode)

CNVST LOW to SYNC Asserted Delay t

(Warp Mode/Normal Mode/Impulse Mode)

SYNC Deasserted to BUSY LOW Delay t

REFER TO FIGURES 18 AND 20 (Slave Serial Interface Modes)

External SCLK Setup Time t

External SCLK Active Edge to SDOUT Delay t

SDIN Setup Time t

SDIN Hold Time t

External SCLK Period t

External SCLK HIGH t

External SCLK LOW t

NOTES

1

In warp mode only, the maximum time between conversions is 1 ms; otherwise, there is no required maximum time.

2

In serial interface modes, the SYNC, SCLK, and SDOUT timings are defined with a maximum load CL of 10 pF; otherwise, the load is 60 pF maximum.

3

If the polarity of SCLK is inverted, the timing references of SCLK are also inverted.

Specifications subject to change without notice.

REV. C

10

11

12

13

2

14

t

15

16

17

18

19

t

20

t

21

22

23

24

25

26

27

28

29

30

2

31

32

33

34

35

36

37

45 ns

515ns

25/275/525 ns

4ns

40 75 ns

30 ns

9.5 ns

4.5 ns

3ns

3

1/1.25/1.5 µs

50 ns

5ns

316ns

5ns

5ns

25 ns

10 ns

10 ns

–3–

1.5/1.75/2 µs

40 ns

10 ns

10 ns

10 ns

10 ns

10 ns

10 ns

2.75/3/3.25 µs

AD7664

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

IN2, REF, INGND, REFGND to AGND

. . . . . . . . . . . . . . . . . . . . . . .AVDD + 0.3 V to AGND – 0.3 V

Ground Voltage Differences

AGND, DGND, OGND . . . . . . . . . . . . . . . . . . . . . . ± 0.3 V

Supply Voltages

AVDD, DVDD, OVDD . . . . . . . . . . . . . . . . . . . . . . . . . 7 V

AVDD to DVDD, AVDD to OVDD . . . . . . . . . . . . . . ±7 V

DVDD to OVDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 7 V

Digital Inputs

Except the Data Bus D(7:4) . . . . . –0.3 V to DVDD + 3.0 V

Data Bus D(7:4) . . . . . . . . . . . . . –0.3 V to OVDD + 3.0 V

Internal Power Dissipation

3

. . . . . . . . . . . . . . . . . . . . 700 mW

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range

(Soldering 10 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . 300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

See Analog Input section.

3

Specification is for the device in free air:

48-Lead LQFP; θ

= 91°C/W, θ

JA

= 30°C/W

JC

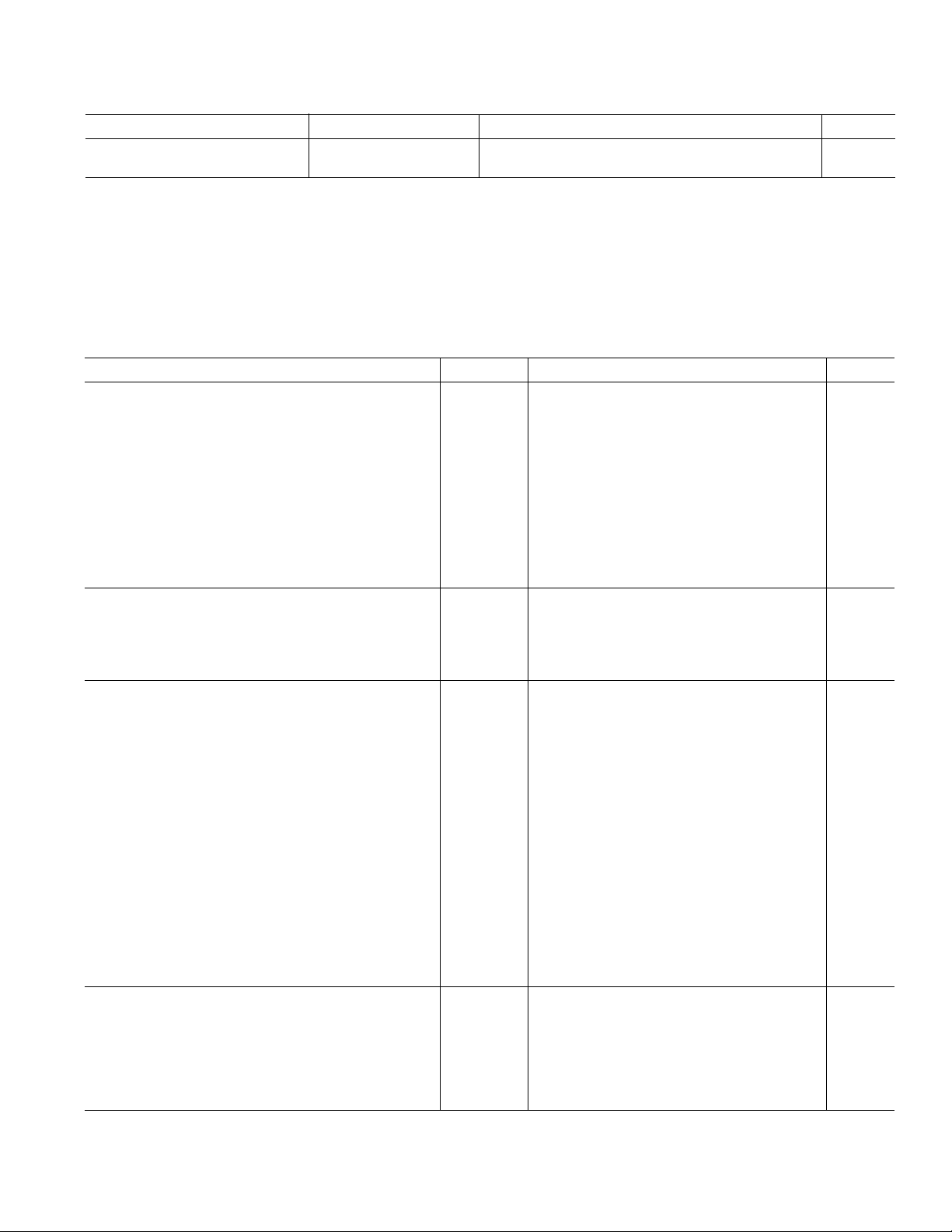

I

1.6mA

TO OUTPUT

PIN

C

L

60pF*

500A

*

IN SERIAL INTERFACE MODES, THE SYNC, SCLK, AND

SDOUT TIMINGS ARE DEFINED WITH A MAXIMUM LOAD

OF 10pF; OTHERWISE, THE LOAD IS 60pF MAXIMUM.

C

L

OL

1.4V

I

OH

Figure 1. Load Circuit for Digital Interface Timing,

SDOUT, SYNC, SCLK Outputs, C

0.8V

t

DELAY

2V

0.8V

= 10 pF

L

2V

t

DELAY

2V

0.8V

Figure 2. Voltage Reference Levels for Timing

ORDERING GUIDE

Temperature

Model INL Maximum No Missing Codes Range Package Description Package Option

AD7664AST

AD7664ASTRL

EVAL-AD7664CB

1

EVAL-CONTROL BRD2

NOTES

1

This board can be used as a standalone evaluation board or in conjunction with the EVAL-CONTROL BRD2 for evaluation/demonstration purposes.

2

This board allows a PC to control and communicate with all Analog Devices evaluation boards ending in the CB designators.

±2.5 LSB 16 Bits

±2.5 LSB 16 Bits

2

–40°C to +85°C Quad Flatpack (LQFP) ST-48

–40°C to +85°C Quad Flatpack (LQFP) ST-48

Evaluation Board

Controller Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD7664 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

–4–

REV. C

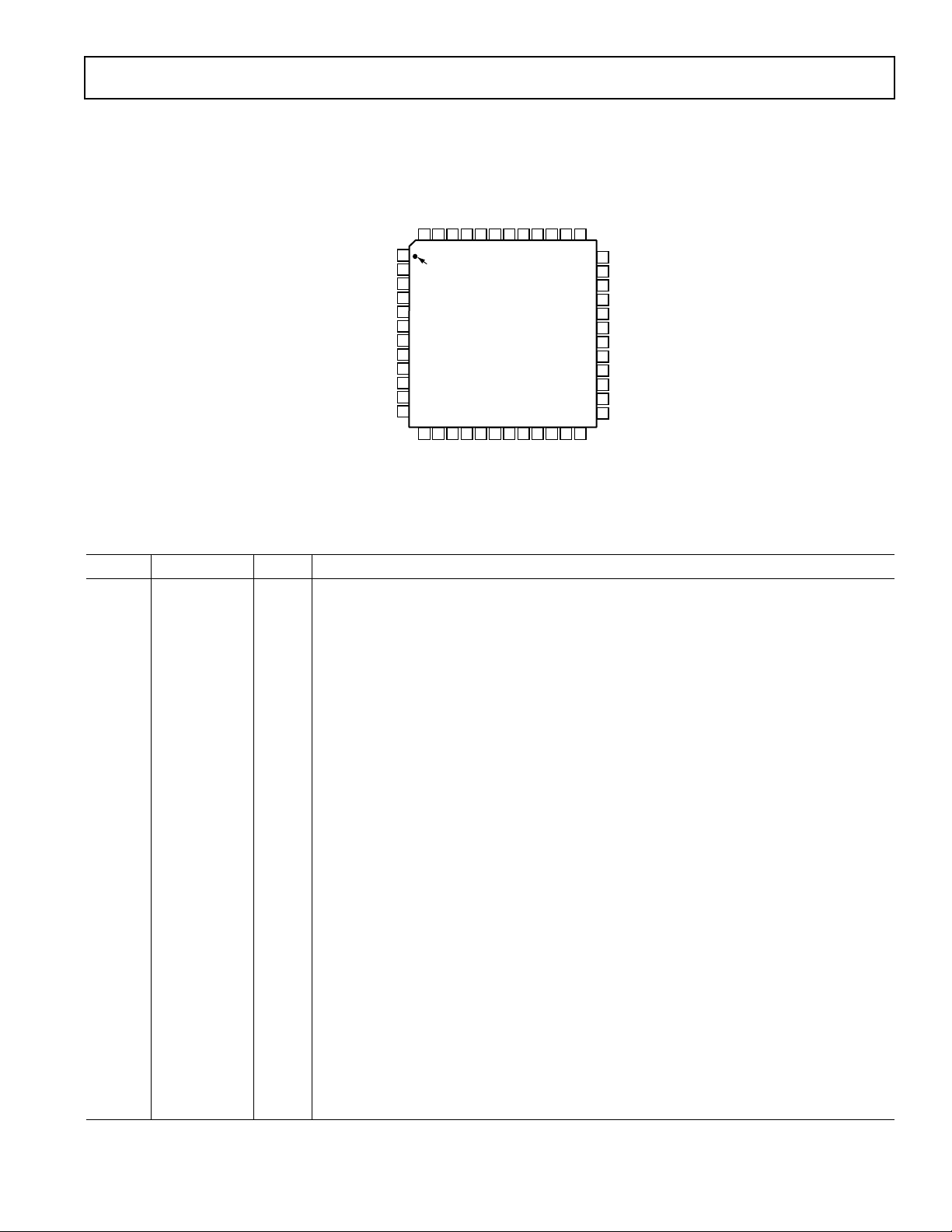

PIN CONFIGURATION

48-Lead LQFP

(ST-48)

AD7664

AGND

AVDD

NC

DGND

OB/2C

WARP

IMPULSE

SER/PAR

D0

D1

D2

D3

NC = NO CONNECT

NCNCNCNCNCINNCNCNC

48

47 46 45 44 39 38 3743 42 41 40

1

PIN 1

IDENTIFIER

2

3

4

5

6

7

8

9

10

11

12

13 14

D4/EXT/INT

AD7664

TOP VIEW

(Not to Scale)

15 16 17 18 19 20 21 22 23 24

OGND

D6/INVSCLK

D5/INVSYNC

D7/RDC/SDIN

OVDD

DVDD

DGND

D8/SDOUT

INGND

REFGND

D9/SCLK

D10/SYNC

REF

36

AGND

35

CNVST

34

PD

33

RESET

32

CS

31

RD

30

DGND

29

BUSY

28

D15

27

D14

26

D13

25

D12

D11/RDERROR

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Type Description

1 AGND P Analog Power Ground Pin

2 AVDD P Input Analog Power Pins. Nominally 5 V.

3, 40–42, NC No Connect

44–48

4 DGND DI Must be tied to the ground where DVDD is referred.

5 OB/2C DI Straight Binary/Binary Two’s Complement. When OB/2C is HIGH, the digital output is

straight binary; when LOW, the MSB is inverted resulting in a two’s complement output from

its internal shift register.

6 WARP DI Mode Selection. When HIGH and IMPULSE LOW, this input selects the fastest mode, the

maximum throughput is achievable, and a minimum conversion rate must be applied in order

to guarantee full specified accuracy. When LOW, full accuracy is maintained independent of

the minimum conversion rate.

7 IMPULSE DI Mode Selection. When HIGH and WARP LOW, this input selects a reduced power mode. In

this mode, the power dissipation is approximately proportional to the sampling rate.

8 SER/PAR DI Serial/Parallel Selection Input. When LOW, the parallel port is selected; when HIGH, the

serial interface mode is selected and some bits of the DATA bus are used as a serial port.

9–12 DATA[0:3] DO Bit 0 to Bit 3 of the Parallel Port Data Output Bus. These pins are always outputs, regardless

of the state of SER/PAR.

13 DATA[4] DI/O When SER/PAR is LOW, this output is used as Bit 4 of the Parallel Port Data Output Bus.

or EXT/INT When SER/PAR is HIGH, this input, part of the serial port, is used as a digital select input for

choosing the internal or an external data clock. With EXT/INT tied LOW, the internal clock

is selected on SCLK output. With EXT/INT set to a logic HIGH, output data is synchronized

to an external clock signal connected to the SCLK input.

14 DATA[5] DI/O When SER/PAR is LOW, this output is used as Bit 5 of the Parallel Port Data Output Bus.

or INVSYNC When SER/PAR is HIGH, this input, part of the serial port, is used to select the active state of

the SYNC signal. It is active in both master and slave mode. When LOW, SYNC is active

HIGH. When HIGH, SYNC is active LOW.

15 DATA[6] DI/O When SER/PAR is LOW, this output is used as Bit 6 of the Parallel Port Data Output Bus.

or INVSCLK

When SER/PAR is HIGH, this input, part of the serial port, is used to invert the SCLK signal.

It is active in both master and slave mode.

REV. C

–5–

AD7664

Pin No. Mnemonic Type Description

16 DATA[7] DI/O When SER/PAR is LOW, this output is used as Bit 7 of the Parallel Port Data Output Bus.

or RDC/SDIN When SER/PAR is HIGH, this input, part of the serial port, is used as either an external data

input or a read mode selection input depending on the state of EXT/INT.

When EXT/INT is HIGH, RDC/SDIN could be used as a data input to daisy chain the conversion

results from two or more ADCs onto a single SDOUT line. The digital data level on SDIN is

output on DATA with a delay of 16 SCLK periods after the initiation of the read sequence.

When EXT/INT is LOW, RDC/SDIN is used to select the read mode. When RDC/SDIN is

HIGH, the data is output on SDOUT during conversion. When RDC/SDIN is LOW, the

data can be output on SDOUT only when the conversion is complete.

17 OGND P Input/Output Interface Digital Power Ground

18 OVDD P Input/Output Interface Digital Power. Nominally at the same supply than the supply of the

host interface (5 V or 3 V).

19 DVDD P Digital Power. Nominally at 5 V.

20 DGND P Digital Power Ground

21 DATA[8] DO When SER/PAR is LOW, this output is used as Bit 8 of the Parallel Port Data Output Bus.

or SDOUT When SER/PAR is HIGH, this output, part of the serial port, is used as a serial data output

synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7664

provides the conversion result, MSB first, from its internal shift register. The DATA format is

determined by the logic level of OB/2C. In serial mode, when EXT/INT is LOW, SDOUT is

valid on both edges of SCLK.

In serial mode, when EXT/INT is HIGH:

If INVSCLK is LOW, SDOUT is updated on SCLK rising edge and valid on the next

falling edge.

If INVSCLK is HIGH, SDOUT is updated on SCLK falling edge and valid on the next rising edge.

22 DATA[9] DI/O When SER/PAR is LOW, this output is used as the Bit 9 of the Parallel Port Data

or SCLK Output Bus.

When SER/PAR is HIGH, this pin, part of the serial port, is used as a serial data clock input

or output, dependent upon the logic state of the EXT/INT pin. The active edge where the

data SDOUT is updated depends upon the logic state of the INVSCLK pin.

23 DATA[10] DO When SER/PAR is LOW, this output is used as the Bit 10 of the Parallel Port Data Output Bus.

or SYNC When SER/PAR is HIGH, this output, part of the serial port, is used as a digital output frame

synchronization for use with the internal data clock (EXT/INT = Logic LOW). When a read

sequence is initiated and INVSYNC is LOW, SYNC is driven HIGH and remains HIGH

while SDOUT output is valid. When a read sequence is initiated and INVSYNC is High,

SYNC is driven LOW and remains LOW while SDOUT output is valid.

24 DATA[11] DO When SER/PAR is LOW, this output is used as the Bit 11 of the Parallel Port Data Output Bus.

or RDERROR When SER/PAR is HIGH and EXT/INT is HIGH, this output, part of the serial port, is

used as a incomplete read error flag. In slave mode, when a data read is started and not

complete when the following conversion is complete, the current data is lost and RDERROR

is pulsed high.

25–28 DATA[12:15] DO Bit 12 to Bit 15 of the Parallel Port Data output bus. These pins are always outputs regard

less of the state of SER/PAR.

29 BUSY DO Busy Output. Transitions HIGH when a conversion is started, and remains HIGH until the

conversion is complete and the data is latched into the on-chip shift register. The falling edge

of BUSY could be used as a data ready clock signal.

30 DGND P Must Be Tied to Digital Ground

31 RD DI

32 CS DI Chip Select. When CS and RD are both LOW, the interface parallel or serial output bus is

33 RESET DI Reset Input. When set to a logic HIGH, reset the AD7664. Current conversion if any is aborted.

34 PD DI Power-Down Input. When set to a logic HIGH, power consumption is reduced and conversions

Read Data. When CS and RD are both LOW, the interface parallel or serial output bus is enabled.

enabled. CS is also used to gate the external clock.

If not used, this pin could be tied to DGND.

are inhibited after the current one is completed.

–6–

REV. C

Loading...

Loading...