Analog Devices AD7628TQ, AD7628TE, AD7628KR, AD7628KP, AD7628KN Datasheet

...

CMOS Dual 8-Bit

a

FEATURES

On-Chip Latches for Both DACs

+12 V to +15 V Operation

DACs Matched to 1%

Four Quadrant Multiplication

TTL/CMOS Compatible from +12 V to +15 V

Latch Free (Protection Schottkys not Required)

APPLICATIONS

Disk Drives

Programmable Filters

X-Y Graphics

Gain/Attenuation

GENERAL DESCRIPTION

The AD7628 is a monolithic dual 8-bit digital/analog converter

featuring excellent DAC-to-DAC matching. It is available in

small 0.3" wide 20-pin DIPs and in 20-terminal surface mount

packages.

Separate on-chip latches are provided for each DAC to allow

easy microprocessor interface.

Data is transferred into either of the two DAC data latches via a

common 8-bit TTL/CMOS compatible input port. Control input

DAC A/DAC B determines which DAC is to be loaded.

The AD7628’s load cycle is similar to the write cycle of a random access memory, and the device is bus compatible with most

8-bit microprocessors, including 6502, 6809, 8085, Z80.

The device operates from a +12 V to +15 V power supply and is

TTL-compatible over this range. Power dissipation is a low

20 mW.

Both DACs offer excellent four quadrant multiplication characteristics with a separate reference input and feedback resistor for

each DAC.

Buffered Multiplying DAC

AD7628

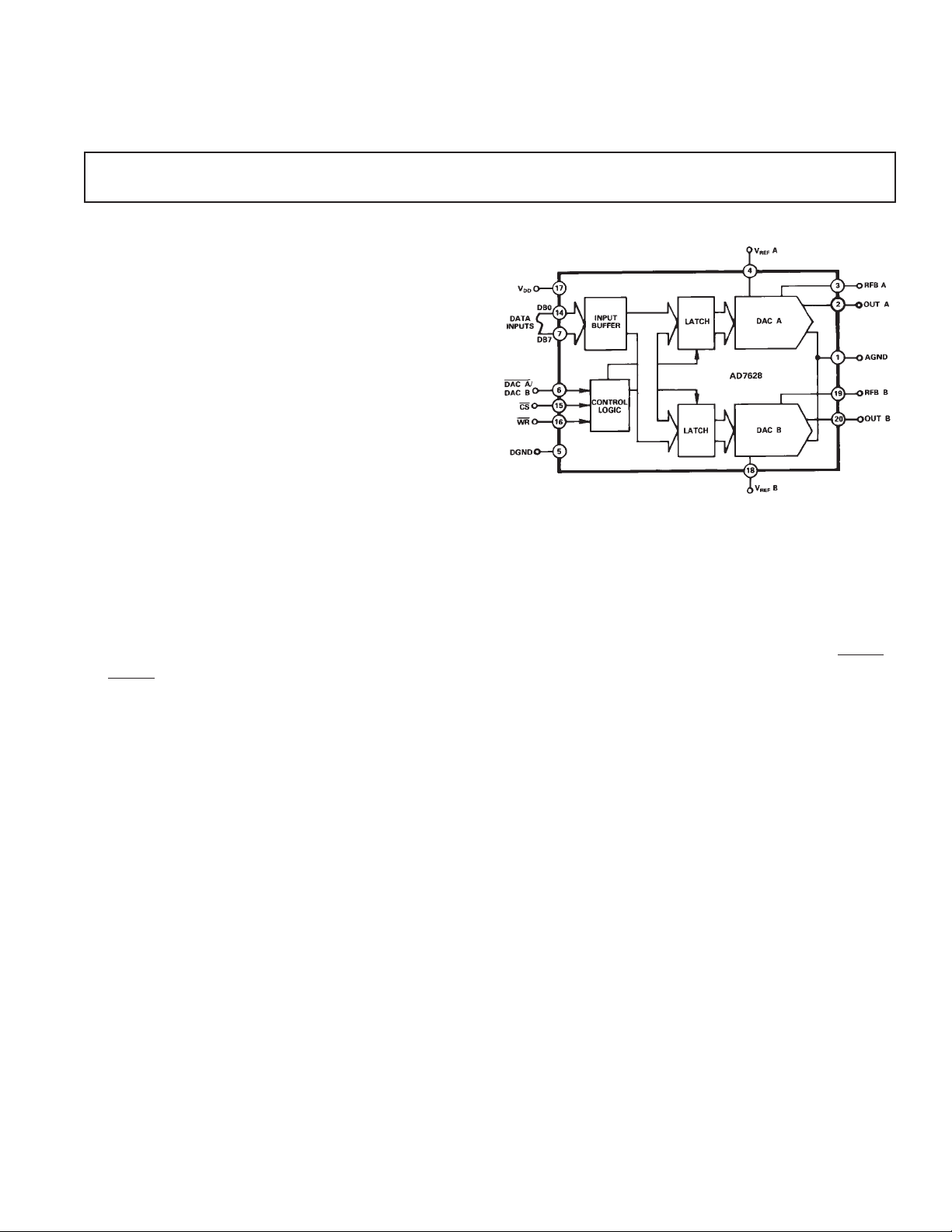

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1. DAC to DAC matching: since both of the AD7628 DACs

are fabricated at the same time on the same chip, precise

matching and tracking between DAC A and DAC B is inherent. The AD7628’s matched CMOS DACs make a whole

new range of applications circuits possible, particularly in the

audio, graphics and process control areas.

2. Small package size: combining the inputs to the on-chip

DAC latches into a common data bus and adding a

DAC B select line has allowed the AD7628 to be packaged in

a small 20-pin 0.3" wide DIP, 20-pin SOIC, 20-terminal

PLCC and 20-terminal LCC.

3. TTL-Compatibility: All digital inputs are TTL-compatible

over a +12 V to +15 V power supply range.

DAC A/

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1996

AD7628–SPECIFICA TIONS

(V

= +10.8 V to +15.75 V, V

DD

otherwise noted)

REF

A = V

B = +10 V; OUT A = OUT B = 0 V unless

REF

Parameter TA = +258C1to +858C to +1258C

STATIC PERFORMANCE

2

TA = –408CT

= –558C

A

1

Units Test Conditions/Comments

Resolution 8 8 8 Bits

Relative Accuracy ± 1/2 ± 1/2 ± 1/2 LSB max This is an Endpoint Linearity Specification

Differential Nonlinearity ± 1 ± 1 ± l LSB max All Grades Guaranteed Monotonic Over

Full Operating Temperature Range

Gain Error ±2 ±3 ±3 LSB max Measured Using Internal RFB A and RFB B.

Both DAC Latches Loaded with 11111111.

Gain Error is Adjustable Using Circuits

Gain Temperature Coefficient

3

of Figures 4 and 5.

∆Gain/∆Temperature ± 0.0035 ± 0.0035 %/°C max

Output Leakage Current

OUT A (Pin 2) ±50 ±200 ±200 nA max DAC Latches Loaded with 00000000

OUT B (Pin 20) ±50 ±200 ±200 nA max

Input Resistance (V

V

A/V

REF

B Input Resistance

REF

Match ±1 ±1 ±1 % max

DIGITAL INPUTS

Input High Voltage (VIH) 2.4 2.4 2.4 V min

Input Low Voltage (VIL) 0.8 0.8 0.8 V max

Input Current (IIN) ±1 ±10 ±10 µA max VIN = 0 or V

Input Capacitance

DB0–DB7 10 10 10 pF max

A, V

REF

4

B)88 8kΩ min Input Resistance TC = –300 ppm/°C, Typical

REF

15 15 15 kΩ max Input Resistance is 11 kΩ

DD

WR, CS, DACA/DACB 15 15 15 pF max

SWITCHING CHARACTERISTICS

3

See Timing Diagram

Chip Select to Write Set Up Time (tCS) 160 160 210 ns min

Chip Select to Write Hold Time (tCH) 10 10 10 ns min

DAC Select to Write Set Up Time (tAS) 160 160 210 ns min

DAC Select to Write Hold Time (tAH) 10 10 10 ns min

Data Valid to Write Set Up Time (tDS) 160 160 210 ns min

Data Valid to Write Hold Time (tDH) 10 10 10 ns min

Write Pulse Width (tWR) 150 170 210 ns min

POWER SUPPLY See Figure 3

IDD, K Grade 2 2 mA All Digital Inputs VIL or V

B, T Grades 2 2.5 2.5 mA All Digital Inputs VIL or V

All Grades 100 500 500 µA All Digital Inputs 0 V or V

IH

IH

DD

Specifications subject to change without notice.

AC PERFORMANCE CHARACTERISTICS

These characteristics are included for Design Guidance only and are not

subject to test. VDD = +10.8 V to +15.75 V. (Measured Using Recommended PC Board Layout (Figure 7) and AD644 as Output Amplifiers)

TA = –408CT

Parameter TA = +258C1to +858C

DC SUPPLY REJECTION

(∆GAIN/∆VDD) 0.01 0.02 0.02 % per % max ∆V

1

CURRENT SETTLING TIME 350 400 400 ns max To 1/2 LSB OutA/OutB Load = 100 Ω.

DIGITAL-TO-ANALOG GLITCH

IMPULSE 330 nV sec typ For Code Transition 00000000 to 11111111

OUTPUT CAPACITANCE

C

A 25 25 25 pF max DAC Latches Loaded with 00000000

OUT

C

B 25 25 25 pF max

OUT

C

A 60 60 60 pF max DAC Latches Loaded with 11111111

OUT

C

B 60 60 60 pF max

OUT

AC FEEDTHROUGH

V

A to OUT A –70 –65 –65 dB max V

REF

V

B to OUT B –70 –65 –65 dB max @ 10 kHz

REF

CHANNEL-TO-CHANNEL ISOLATION Both DAC Latches Loaded with 11111111.

V

A to OUT B –80 dB typ V

REF

V

B to OUTA –80 dB typ V

REF

DIGITAL CROSSTALK 60 nV sec typ Measured for Code Transition 00000000

HARMONIC DISTORTION –85 dB typ VIN = 6 V rms @ 1 kHz

NOTES

1

Temperature Ranges are K Version; –40°C to +85°C; B Version; –40 °C to +85 °C; T Version; –55 °C to +125 °C.

2

Specification applies to both DACs in AD7628.

3

Guaranteed by design but not production tested.

4

Logic inputs are MOS Gates. Typical input current (+25°C) is less than 1 nA.

Specifications subject to change without notice.

= –558C

A

to +1258πC1Units Test Conditions/Comments

= ±5%

DD

WR = CS = 0 V.

DB0–DB7 = 0 V to VDD or VDD to 0 V

A, V

REF

REF

V

REF

REF

V

REF

B = 20 V p-p Sine Wave

REF

A = 20 V p-p Sine Wave @ 10 kHz

B = 0 V See Figure 6.

B = 20 V p-p Sine Wave @ 10 kHz

A = 0 V See Figure 6.

to 11111111

–2–

REV. A

AD7628

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

(TA = +25°C unless otherwise noted)

VDD to AGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V, +17 V

V

to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V, +17 V

DD

AGND to DGND . . . . . . . . . . . . . . . . . . . . . . . . V

DGND to AGND . . . . . . . . . . . . . . . . . . . . . . . . V

Digital Input Voltage to DGND . . . . . . –0.3 V, V

V

, V

to AGND . . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V

PIN20

B to AGND . . . . . . . . . . . . . . . . . . . . . . .±25 V

REF

B to AGND . . . . . . . . . . . . . . . . . . . . . . . ±25 V

RFB

V

V

PIN2

REF

RFB

A, V

A, V

+ 0.3 V

DD

+ 0.3 V

DD

+ 0.3 V

DD

Power Dissipation (Any Package) to +75°C . . . . . . . . 450 mW

Derates above +75°C by . . . . . . . . . . . . . . . . . . . 6 mW/°C

Operating Temperature Range

Commercial (K) Grades . . . . . . . . . . . . . . . –40°C to +85°C

Industrial (B) Grades . . . . . . . . . . . . . . . . . –40°C to +85°C

Extended (T) Grades . . . . . . . . . . . . . . . . –55°C to +125°C

Storage Temperature . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . +300°C

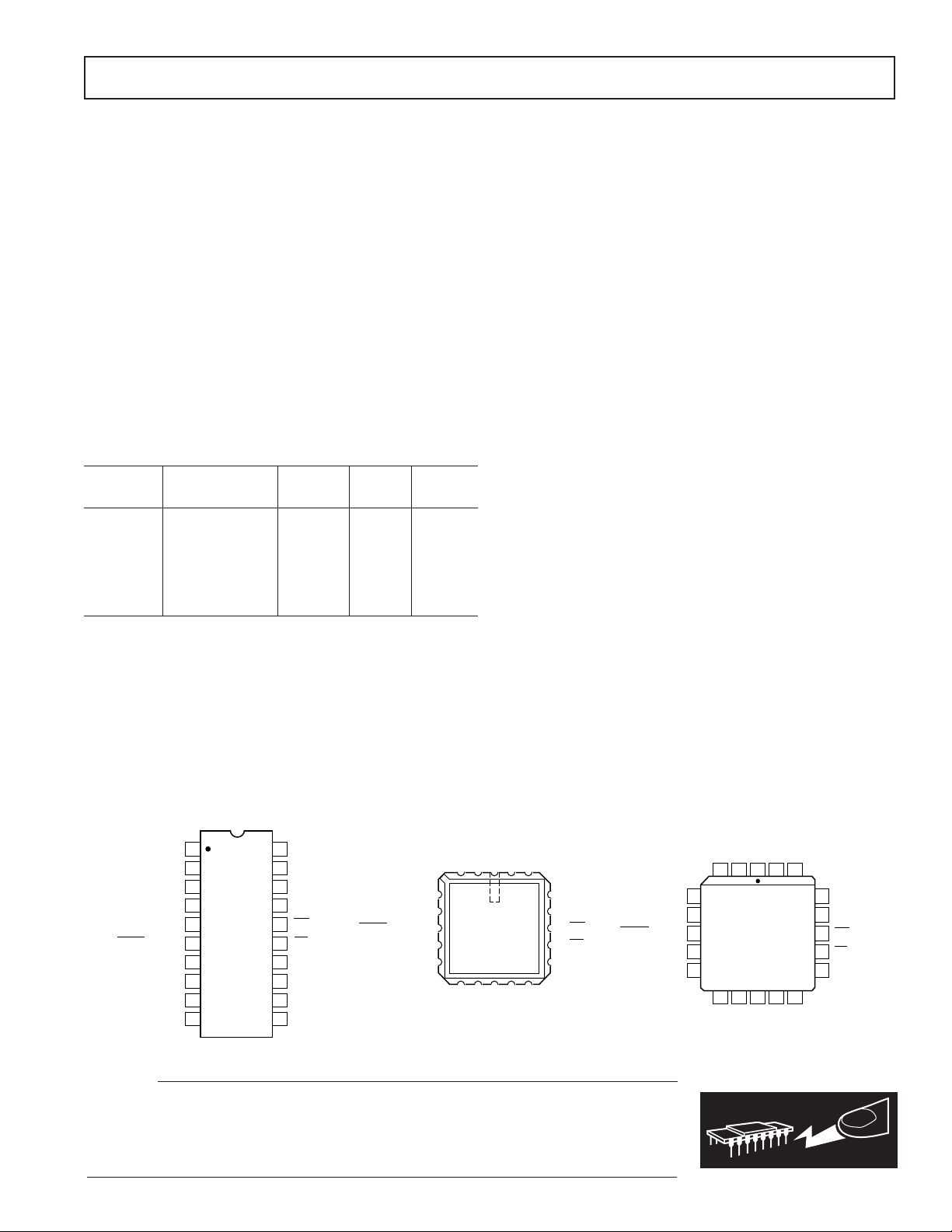

ORDERING GUIDE

Temperature Relative Gain Package

1

Model

Range Accuracy Error Option

AD7628KN –40°C to +85°C ±1/2 LSB ±2 LSB N-20

AD7628KP –40°C to +85°C ±1/2 LSB ±2 LSB P-20A

AD7628KR –40°C to +85°C ±1/2 LSB ±2 LSB R-20

AD7628BQ –40°C to +85°C ±1/2 LSB ±2 LSB Q-20

AD7628TQ –55°C to +125° C ±1/2 LSB ±2 LSB Q-20

AD7628TE –55°C to +125°C ±1/2 LSB ±2 LSB E-20A

NOTES

1

To order MIL-STD-883, Class B process parts, add /883B to part number.

Contact your local sales office for military data sheet.

2

E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip

Carrier; Q = Cerdip; R = SOIC.

TERMINOLOGY

Relative Accuracy:

Relative accuracy or endpoint nonlinearity is a measure of the

maximum deviation from a straight line passing through the

endpoints of the DAC transfer function. It is measured after adjusting for zero and full-scale, and is normally expressed in

LSBs or as a percentage of full-scale reading.

Differential Nonlinearity:

Differential nonlinearity is the difference between the measured

change and the ideal 1 LSB change between any two adjacent

codes. A specified differential nonlinearity of ± 1 LSB max over

the operating temperature range ensures monotonicity.

Gain Error:

Gain error is a measure of the output error between an ideal

DAC and the actual device output. It is measured with all 1s in

the DAC latches after offset error has been adjusted out. Gain

error of both DACs is adjustable to zero with external resistance.

Output Capacitance:

Capacitance from OUT A or OUT B to AGND.

Digital-to-Analog Glitch Impulse:

2

The amount of charge injected from the digital inputs to the

analog output when the inputs change state. This is normally

specified as the area of the glitch in either pA-secs or nV-secs,

depending upon whether the glitch is measured as a current or

voltage signal. Glitch impulse is measured with V

REF

A, V

= AGND.

Channel-to-Channel Isolation:

The proportion of input signal from one DAC’s reference input

that appears at the output of the other DAC, expressed as a

ratio in dB.

Digital Crosstalk:

The glitch energy transferred to the output of one converter due

to a change in digital input code to the other converter. Specified in nV secs.

REF

B

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7628 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. A

DIP, SOIC

1

AGND

2

OUT A

3

RFB A

4

A

V

REF

DGND

DAC A/DAC B

(MSB) DB7

DB6 DB1

DB5

DB4

AD7628

5

6

(Not to Scale)

7

813

912

10 11

TOP VIEW

20

19

18

17

16

15

14

OUT B

RFB B

V

B

REF

V

DD

WR

CS

DB0 (LSB)

DB2

DB3

V

REF

DGND

DAC A /DAC B

DB7 (MSB)

DB6

PIN CONFIGURATIONS

LCCC

A

4

5

6

7

8

OUT A

RFB A

AD7628

TOP VIEW

(Not to Scale)

DB5

DB4

AGND

12 1391110

DB3

OUT B

1931220

DB2

RFB B

DB1

18

V

17

V

16

WR

CS

15

14

DB0 (LSB)

REF

DD

–3–

B

V

REF

DGND

DAC A/DAC B

DB7 (MSB)

DB6

PLCC

OUT A

OUT B

AGND

DB3

RFB B

19312 20

V

B

18

REF

V

17

DD

WR

16

CS

15

DB0 (LSB)

14

12 1391110

DB1

DB2

RFB A

A

4

5

AD7628

6

TOP VIEW

(Not to Scale)

7

8

DB5

DB4

Loading...

Loading...