ANALOG DEVICES ad7625 Service Manual

16-Bit, 6 MSPS, PulSAR

V

FEATURES

Throughput: 6 MSPS

SNR: 93 dB

INL: ±0.45 LSB typical, ±1 LSB maximum

DNL: ±0.3 LSB typical, ±0.5 LSB maximum

Power dissipation: 135 mW

32-lead LFCSP (5 mm × 5 mm)

SAR architecture

No latency/no pipeline delay

16-bit resolution with no missing codes

Zero error: ±1.5 LSB

Differential input voltage: ±4.096 V

Serial LVDS interface

Self-clocked mode

Echoed-clock mode

Can use LVDS or CMOS for conversion control (CNV signal)

Reference options

Internal: 4.096 V

External (1.2 V) buffered to 4.096 V

External: 4.096 V

APPLICATIONS

High dynamic range telecommunications

Receivers

Digital imaging systems

High speed data acquisition

Spectrum analysis

Test equipment

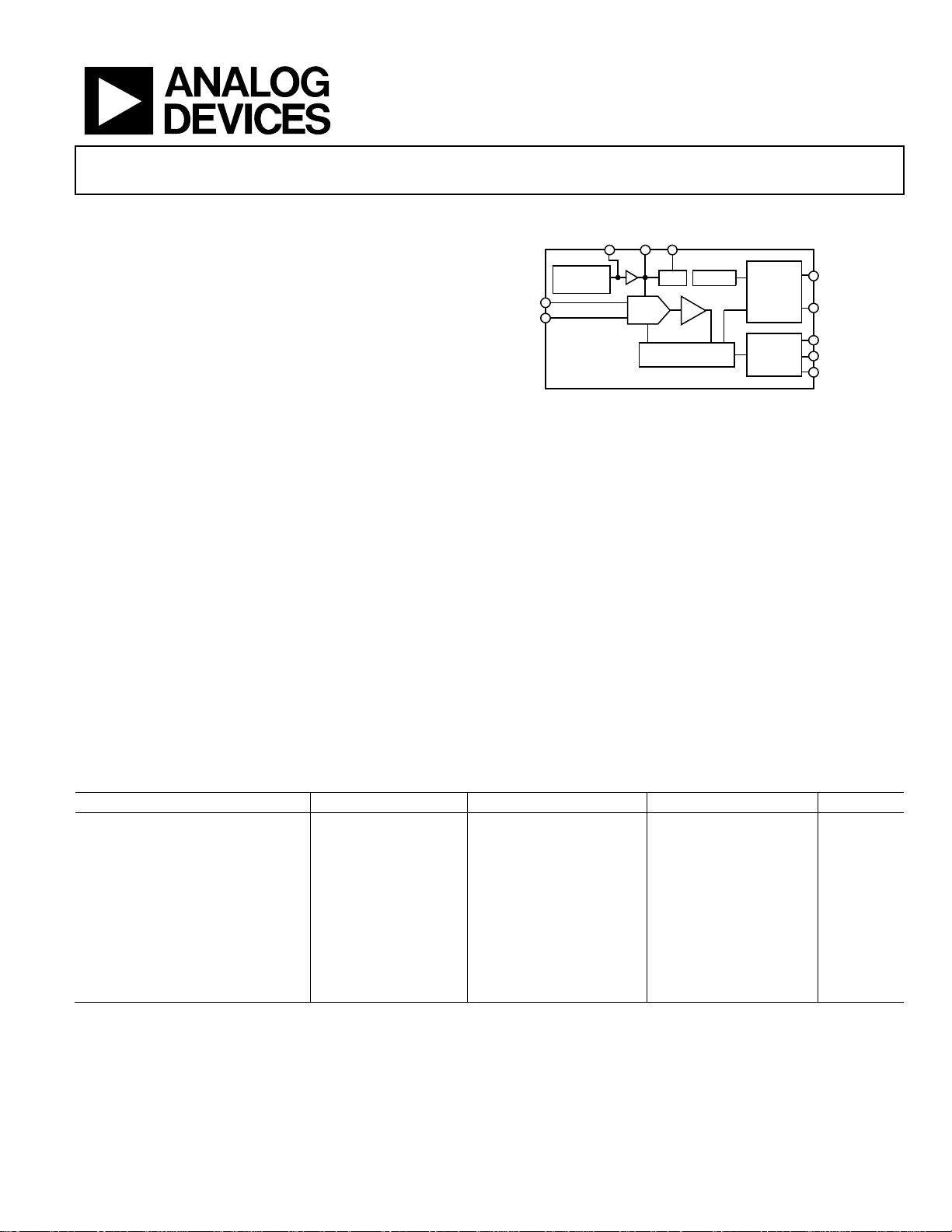

Differential ADC

AD7625

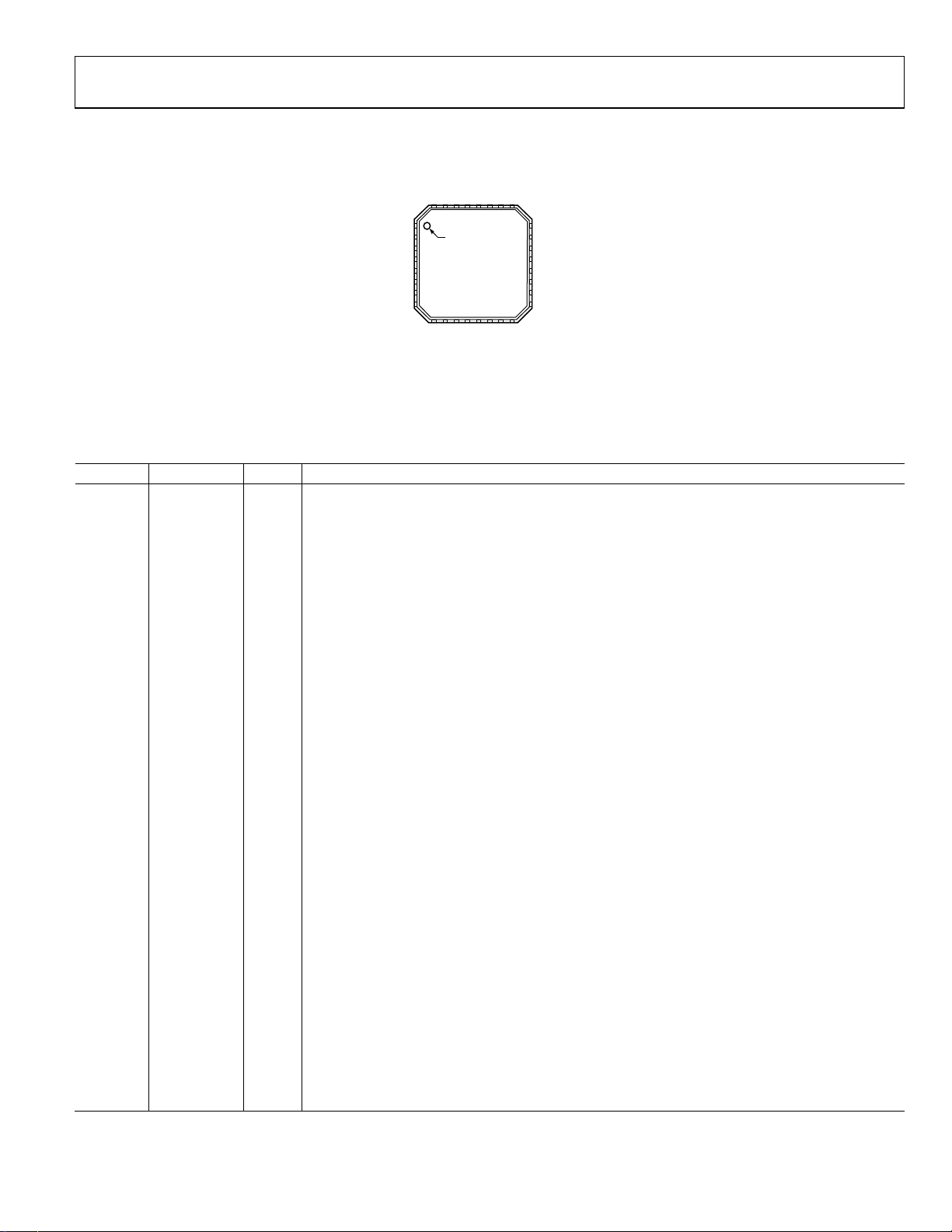

FUNCTIONAL BLOCK DIAGRAM

CAP

DAC

CM

÷2

SAR

CLOCK

Figure 1.

LOGIC

SERIAL

LVDS

VIO

CNV+, CNV–

D+, D–

DCO+, DCO–

CLK+, CLK–

REFIN REF

1.2V

BAND GAP

IN+

IN–

AD7625

GENERAL DESCRIPTION

The AD7625 is a 16-bit, 6 MSPS, charge redistribution successive

approximation register (SAR) based architecture analog-to-digital

converter (ADC). SAR architecture allows unmatched performance both in noise (93 dB SNR) and in linearity (1 LSB). The

AD7625 contains a high speed, 16-bit sampling ADC, an internal

conversion clock, and an internal buffered reference. On the

CNV± rising edge, it samples the voltage difference between the

IN+ and IN− pins. The voltages on these pins swing in opposite

phase between 0 V and REF. The 4.096 V reference voltage, REF,

can be generated internally or applied externally.

All converted results are available on a single LVDS self-clocked

or echoed-clock serial interface, reducing external hardware

connections.

The AD7625 is housed in a 32-lead, 5 mm × 5 mm LFCSP with

operation specified from −40°C to +85°C.

7652-001

Table 1. Fast PulSAR® ADC Selection

Input Type Resolution (Bits) 1 MSPS to <2 MSPS 2 MSPS to 3 MSPS 6 MSPS

Differential (Ground Sense) 16 AD7653

16 AD7667

16 AD7980

16 AD7983

True Bipolar 16 AD7671

Differential (Antiphase) 16 AD7677 AD7621 AD7625

16 AD7623 AD7622

18 AD7643 AD7641

18 AD7982

18 AD7984

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009 Analog Devices, Inc. All rights reserved.

AD7625

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Timing Specifications .................................................................. 5

Absolute Maximum Ratings ............................................................ 6

Thermal Resistance ...................................................................... 6

ESD Caution .................................................................................. 6

Pin Configuration and Function Descriptions ............................. 7

Typical Performance Characteristics ............................................. 9

Terminology .................................................................................... 12

Theory of Operation ...................................................................... 13

Circuit Information .................................................................... 13

Converter Information .............................................................. 13

Transfer Functions ..................................................................... 14

Analog Inputs ............................................................................. 14

Typical Connection Diagram ................................................... 15

Driving the AD7625 ................................................................... 16

Voltage Reference Options ........................................................ 17

Power Supply ............................................................................... 18

Digital Interface .......................................................................... 19

Applications Information .............................................................. 21

Layout, Decoupling, and Grounding ....................................... 21

Outline Dimensions ....................................................................... 22

Ordering Guide .......................................................................... 22

REVISION HISTORY

1/09—Revision 0: Initial Version

Rev. 0 | Page 2 of 24

AD7625

SPECIFICATIONS

VDD1 = 5 V; VDD2 = 2.5 V; VIO = 2.5 V; REF = 4.096 V; all specifications T

Table 2.

Parameter Test Conditions/Comments Min Typ Max Unit

RESOLUTION 16 Bits

ANALOG INPUT

Voltage Range V

Operating Input Voltage V

− V

IN+

IN+

−V

IN−

, V

to GND −0.1 V

IN−

Common-Mode Input Range V

Common-Mode Rejection Ratio fIN = 1 MHz 60 dB

Input Current Midscale input 77 µA

THROUGHPUT

Complete Cycle 166 ns

Throughput Rate 0.1 6 MSPS

DC ACCURACY

Integral Linearity Error −1 ±0.45 +1 LSB

No Missing Codes 16 Bits

Differential Linearity Error −0.5 ±0.3 +0.5 LSB

Transition Noise 0.6 LSB

Zero Error T

MIN

to T

−4 ±1.5 +4 LSB

MAX

Zero Error Drift 0.5 ppm/°C

Gain Error T

MIN

to T

8 20 LSB

MAX

Gain Error Drift 0.4 ppm/°C

Power Supply Sensitivity

1

VDD1 = 5 V ± 5% 0.4 LSB

VDD2 = 2.5 V ± 5% 0.2 LSB

AC ACCURACY

External Reference fIN = 20 kHz

Dynamic Range 92.5 93.2 dB

Signal-to-Noise Ratio 92 93 dB

Spurious-Free Dynamic Range 106 dB

Total Harmonic Distortion −105.5 dB

Signal-to-(Noise + Distortion) 91.5 92 dB

Internal Reference fIN = 20 kHz

Dynamic Range 92.5 93.2 dB

Signal-to-Noise Ratio 91.5 92.9 dB

Spurious-Free Dynamic Range 106 dB

Total Harmonic Distortion −105.5 dB

Signal-to-(Noise + Distortion) 91 92.5 dB

−3 dB Input Bandwidth 100 MHz

Aperture Jitter 0.25 ps rms

INTERNAL REFERENCE

Output Voltage REFIN @ 25°C 1.2 V

Temperature Drift −40°C to +85°C ±15 ppm/°C

REFERENCE BUFFER

REFIN Input Voltage Range 1.2 V

REF Output Voltage Range 4.076 4.096 4.116 V

Line Regulation VDD1 ± 5%, VDD2 ± 5% 5 mV

EXTERNAL REFERENCE

Voltage Range REF 4.096 V

VCM PIN @ 25°C

Output Voltage REF/2 V

Output Impedance 4 5 6 kΩ

MIN

to T

REF

REF

, unless otherwise noted.

MAX

+V

/2 − 0.05 V

/2 V

REF

V

REF

+ 0.1 V

REF

/2 + 0.05 V

REF

Rev. 0 | Page 3 of 24

AD7625

Parameter Test Conditions/Comments Min Typ Max Unit

LVDS I/O (ANSI-644)

Data Format Serial LVDS twos complement

Differential Output Voltage, VOD R

Common-Mode Output Voltage, V

OCM

Differential Input Voltage, VID 100 650 mV

Common-Mode Input Voltage, V

ICM

POWER SUPPLIES

Specified Performance

VDD1 4.75 5 5.25 V

VDD2 2.37 2.5 2.63 V

VIO 2.37 2.5 2.63 V

Operating Currents

Static—Not Converting

VDD1 4.5 7.8 mA

VDD2 17 22.7 mA

VIO

With Internal Reference 6 MSPS throughput

VDD1 11 15.4 mA

VDD2 21.5 28.3 mA

VIO

Without Internal Reference 6 MSPS throughput

VDD1 9 12.1 mA

VDD2 21 26 mA

VIO

Power Dissipation

3

Static—Not Converting 95 130 mW

With Internal Reference 6 MSPS throughput 145 190 mW

Without Internal Reference 6 MSPS throughput 135 165 mW

Energy per Conversion 6 MSPS throughput 22 nJ/sample

TEMPERATURE RANGE

Specified Performance T

1

Using an external reference.

2

The ANSI-644 LVDS specification has a minimum output common mode (V

3

Power dissipation is for the AD7625 device only. In self-clocked interface mode, 9 mW is dissipated in the 100 Ω terminator. In echoed-clock interface mode, 18 mW is

dissipated in two 100 Ω terminators.

= 100 Ω 200 350 454 mV

L

2

R

= 100 Ω 850 1250 1375 mV

L

800 1575 mV

Self-clocked mode and echoed-

11 13 mA

clock mode

Self-clocked mode and echoed-

13.5 16 mA

clock mode

Self-clocked mode and echoed-

13.5 16 mA

clock mode

to T

MIN

−40 +85 °C

MAX

) of 1125 mV.

OCM

Rev. 0 | Page 4 of 24

AD7625

TIMING SPECIFICATIONS

VDD1 = 5 V; VDD2 = 2.5 V; VIO = 2.37 V to 2.63 V; REF = 4.096 V; all specifications T

Table 3.

Parameter Symbol Min Typ Max Unit

Time Between Conversions

Acquisition Time t

CNV± High Time t

CNV± to D± (MSB) Delay t

CNV± to Last CLK± (LSB) Delay t

CLK± Period

2

t

CLK± Frequency f

CLK± to DCO± Delay (Echoed-Clock Mode) t

DCO± to D± Delay (Echoed-Clock Mode) t

CLK± to D± Delay t

1

The maximum time between conversions is 10,000 ns. If CNV± is left idle for a time greater than the maximum value of t

2

For the minimum CLK period, the window available to read data is t

mode, n = 16; in self-clocked interface mode, n = 18.

1

t

CYC

ACQ

CNVH

MSB

CLKL

CLK

CLK

DCO

D

CLKD

CYC

− t

166 10,000 ns

40 ns

10 40 ns

145 ns

110 ns

(t

− t

CYC

MSB

250 300 MHz

0 4 7 ns

0 1 ns

0 4 7 ns

+ t

. Divide this time by the number of bits (n) that are read. In echoed-clock interface

MSB

CLK

to T

MIN

+ t

)/n 4 3.33 ns

CLK

, unless otherwise noted.

MAX

, the subsequent conversion result is invalid.

CYC

Rev. 0 | Page 5 of 24

AD7625

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Analog Inputs/Outputs

IN+, IN− to GND1

−0.3 V to REF + 0.3 V or

±130 mA

REF2 to GND −0.3 V to +6 V

VCM, CAP2 to GND −0.3 V to +6 V

CAP1, REFIN to GND −0.3 V to +2.7 V

Supply Voltage

VDD1 −0.3 V to +6 V

VDD2, VIO −0.3 V to +3 V

Digital Inputs to GND −0.3 V to VIO + 0.3 V

Digital Outputs to GND −0.3 V to VIO + 0.3 V

Input Current to Any Pin Except

Supplies

3

Operating Temperature Range

±10 mA

−40°C to +85°C

(Commercial)

Storage Temperature Range −65°C to +150°C

Junction Temperature 150°C

ESD 1 kV

1

See the Analog Inputs section.

2

Keep CNV+/CNV− low for any external REF voltage > 4.3 V applied

to the REF pin.

3

Transient currents of up to 100 mA do not cause SCR latch-up.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 5. Thermal Resistance

Package Type θJA θ

Unit

JC

32-Lead LFCSP_VQ 40 4 °C/W

ESD CAUTION

Rev. 0 | Page 6 of 24

AD7625

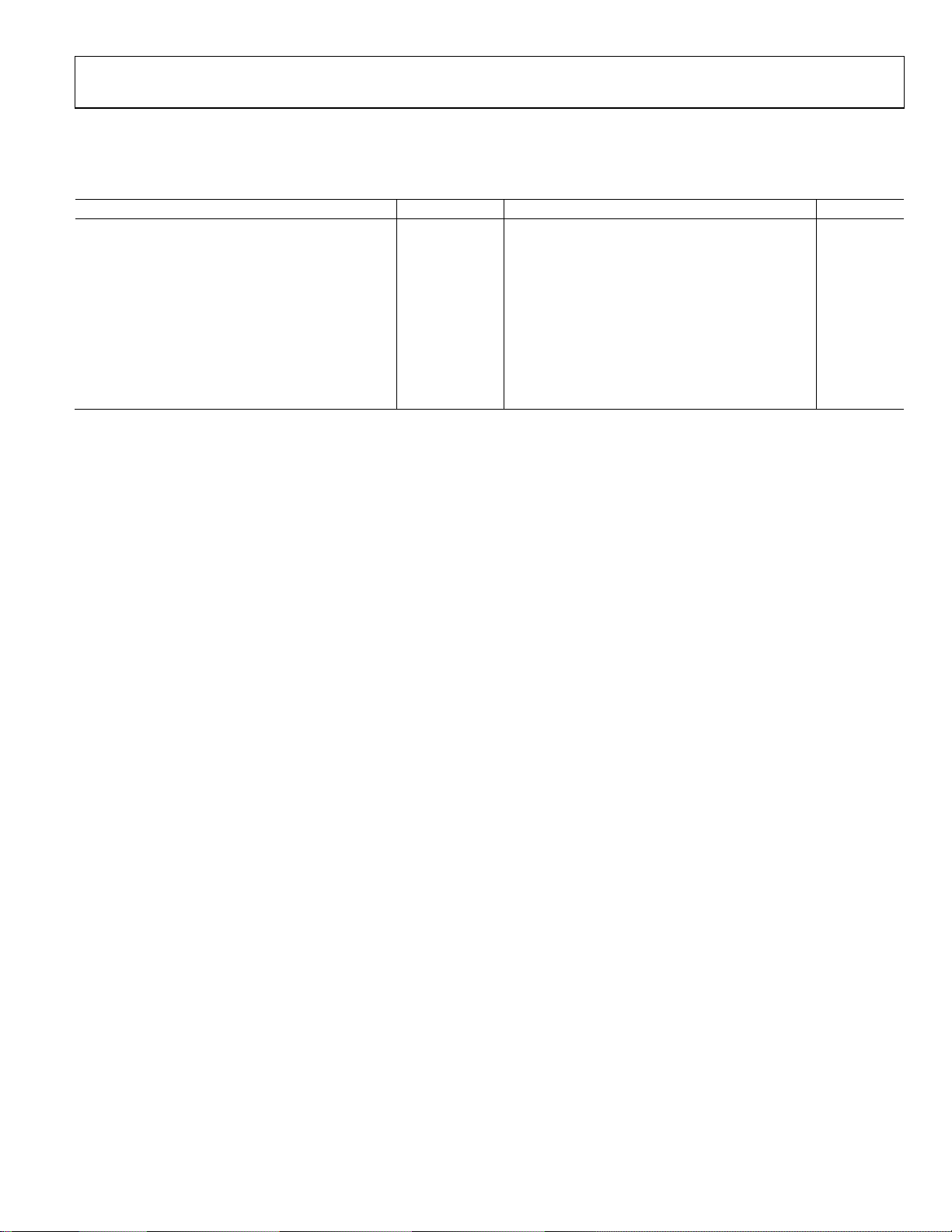

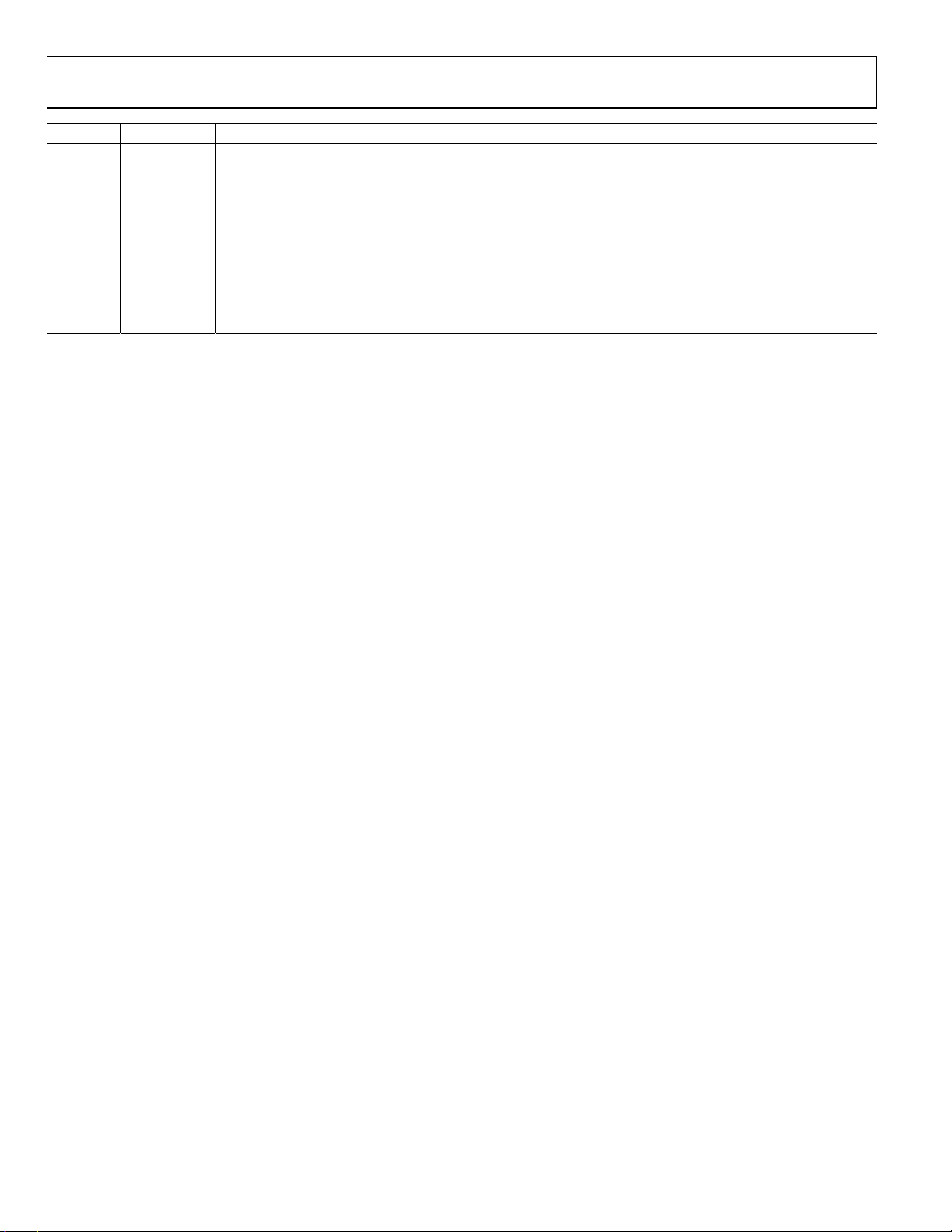

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

P2

F

REF

GND

RE

REF

CA

GND

CAP2

CAP2

29

28

27

26

31

30

32

25

VDD1

1

2

3

4

5

6

7

8

PIN 1

INDICATOR

AD7625

TOP VIEW

(Not to Scale)

9

11

10

12

D–

D+

VIO

CNV+

13

14

15

GND

DCO–

DCO+

VDD2

CAP1

REFIN

EN0

EN1

VDD2

CNV–

NOTES

1. CONNECT T HE EXPOSED P AD TO THE G ROUND

PLANE OF T HE PCB USING MULTIPLE VIAS.

GND

24

IN+

23

IN–

22

VCM

21

VDD1

20

VDD1

19

VDD2

18

CLK+

17

16

CLK–

07652-002

Figure 2.

Table 6. Pin Function Descriptions

Pin No. Mnemonic Type

1

Description

1 VDD1 P Analog 5 V Supply. Decouple the 5 V supply with a 100 nF capacitor.

2 VDD2 P

Analog 2.5 V Supply. Decouple this pin with a 100 nF capacitor. The 2.5 V supply source should

supply this pin first and then be traced to the other VDD2 pins (Pin 7 and Pin 18).

3 CAP1 AO Connect this pin to a 10 nF capacitor.

4 REFIN AI/O

Prebuffer Reference Voltage. When using the internal reference, this pin outputs the band gap voltage

and is nominally at 1.2 V. It can be overdriven with an external reference voltage such as the ADR280.

In either internal or external reference mode, a 10 F capacitor is required. If using an external 4.096 V

reference (connected to REF), this pin is a no connect and does not require any capacitor.

5, 6 EN0, EN1 DI Enable Pins. The logic levels of these pins set the operation of the device as follows:

EN1 = 0, EN0 = 0: Illegal state.

EN1 = 0, EN0 = 1: Enable internal buffer, disable internal reference. An external 1.2 V reference

connected to the REFIN pin is required.

EN1 = 1, EN0 = 0: Disable internal reference and reference buffer. An external 4.096 V reference

connected to the REF pin is required.

EN1 = 1, EN0 = 1: Enable internal reference and reference buffer.

7 VDD2 P Digital 2.5 V Supply. Decouple this pin with a 100 nF capacitor.

8, 9 CNV−, CNV+ DI

Convert Input. These pins act as the conversion control pin. On the rising edge of these pins, the

analog inputs are sampled and a conversion cycle is initiated. CNV+ works as a CMOS input when

CNV− is grounded; otherwise, CNV+ and CNV− are differential LVDS inputs.

10, 11 D−, D+ DO LVDS Data Outputs. The conversion data is output serially on these pins.

12 VIO P Input/Output Interface Supply. Use a 2.5 V supply and decouple this pin with a 100 nF capacitor.

13 GND P Ground. Return path for the 100 nF capacitor connected to Pin 12.

14, 15 DCO−, DCO+ DO

LVDS Buffered Clock Outputs. When DCO+ is grounded, the self-clocked interface mode is selected.

In this mode, the 16-bit results on D± are preceded by a 2-bit header (10) to allow synchronization of

the data by the digital host with simple logic. When DCO+ is not grounded, the echoed-clock inter-

face mode is selected. In this mode, DCO± is a copy of CLK±. The data bits are output on the falling

edge of DCO+ and can be latched in the digital host on the next rising edge of DCO+.

16, 17 CLK−, CLK+ DI LVDS Clock Inputs. This clock shifts out the conversion results on the falling edge of CLK+.

18 VDD2 P Analog 2.5 V Supply. Decouple this pin with a 100 nF capacitor.

19, 20 VDD1 P

Analog 5 V Supply. Isolate these pins from Pin 1 with a ferrite bead and decouple them with a 100 nF

capacitor.

21 VCM AO

Common-Mode Output. When using any reference scheme, this pin produces one-half the voltage

present on the REF pin, which can be useful for driving the common mode of the input amplifiers.

22 IN− AI Differential Negative Analog Input. Referenced to and must be driven 180° out of phase with IN+.

23 IN+ AI Differential Positive Analog Input. Referenced to and must be driven 180° out of phase with IN−.

24 GND P Ground.

Rev. 0 | Page 7 of 24

AD7625

Pin No. Mnemonic Type

25, 26, 28 CAP2 AO

1

Description

Connect all three CAP2 pins together and decouple them with the shortest trace possible to a single

10 F, low ESR, low ESL capacitor. The other side of the capacitor must be placed close to Pin 27 (GND).

27 GND P Ground. Return path for the 10 F capacitor connected to Pin 25, Pin 26, and Pin 28.

29, 30, 32 REF AI/O

Buffered Reference Voltage. When using the internal reference or the 1.2 V external reference (REFIN

input), the 4.096 V system reference is produced at this pin. When using an external reference, such

as the ADR434 or the ADR444, the internal reference buffer must be disabled. In either case, connect

all three REF pins together and decouple them with the shortest trace possible to a single 10 F, low

ESR, low ESL capacitor. The other side of the capacitor must be placed close to Pin 31 (GND).

31 GND P Ground. Return path for the 10 F capacitor connected to Pin 29, Pin 30, and Pin 32.

EP Exposed Pad

The exposed pad is located on the underside of the package. Connect the exposed pad to the

ground plane of the PCB using multiple vias. See the Exposed Paddle section for more information.

1

AI = analog input; AI/O = bidirectional analog; AO = analog output; DI = digital input; DO = digital output; P = power.

Rev. 0 | Page 8 of 24

Loading...

Loading...