16-Bit, 6MSPS PulSAR

V

www.BDTIC.com/ADI

Preliminary Technical Data

FEATURES

Throughput: 6 MSPS

SAR architecture

16-bit resolution with no missing codes

SNR: 92 dB Typ, 90dB Min @ 1MHz

INL: ±1 LSB Typ, ±2 LSB Max

DNL: ±0.3 LSB Typ, ±1 LSB Max

Differential input range: ± 4.096V

No latency/no pipeline delay (SAR architecture)

Serial LVDS interface:

Self-clocked mode

Echoed-clock mode

Reference:

Internal 4.096 V

External (1.2V) buffered to 4.096 V

External 4.096 V

Power dissipation 150 mW

32-Lead LFCSP package (5 mm x 5 mm)

APPLICATIONS

High dynamic range telecommunications

Receivers

Digital imaging systems

High-speed data acquisition

Spectrum analysis

Test equipment

Table 1. Fast PulSAR ADC Selection

≥1 MSPS

Res

Input Type

Differential

(ground

sense)

True Bipolar 16 AD7671

Differential

(anti-phase)

Differential

(anti-phase)

(Bit

s)

16 AD7653

16 AD7677

18 AD7643

to

< 2MSPS

AD7667

AD7980

AD7983

AD7623

AD7982

AD7984

≥ 2 MSPS

to

≤ 3 MSPS

AD7985

AD7621

AD7622

AD7641

AD7986

6 MSPS

AD7625 AD7626

10

MSPS

Differential ADC

AD7625

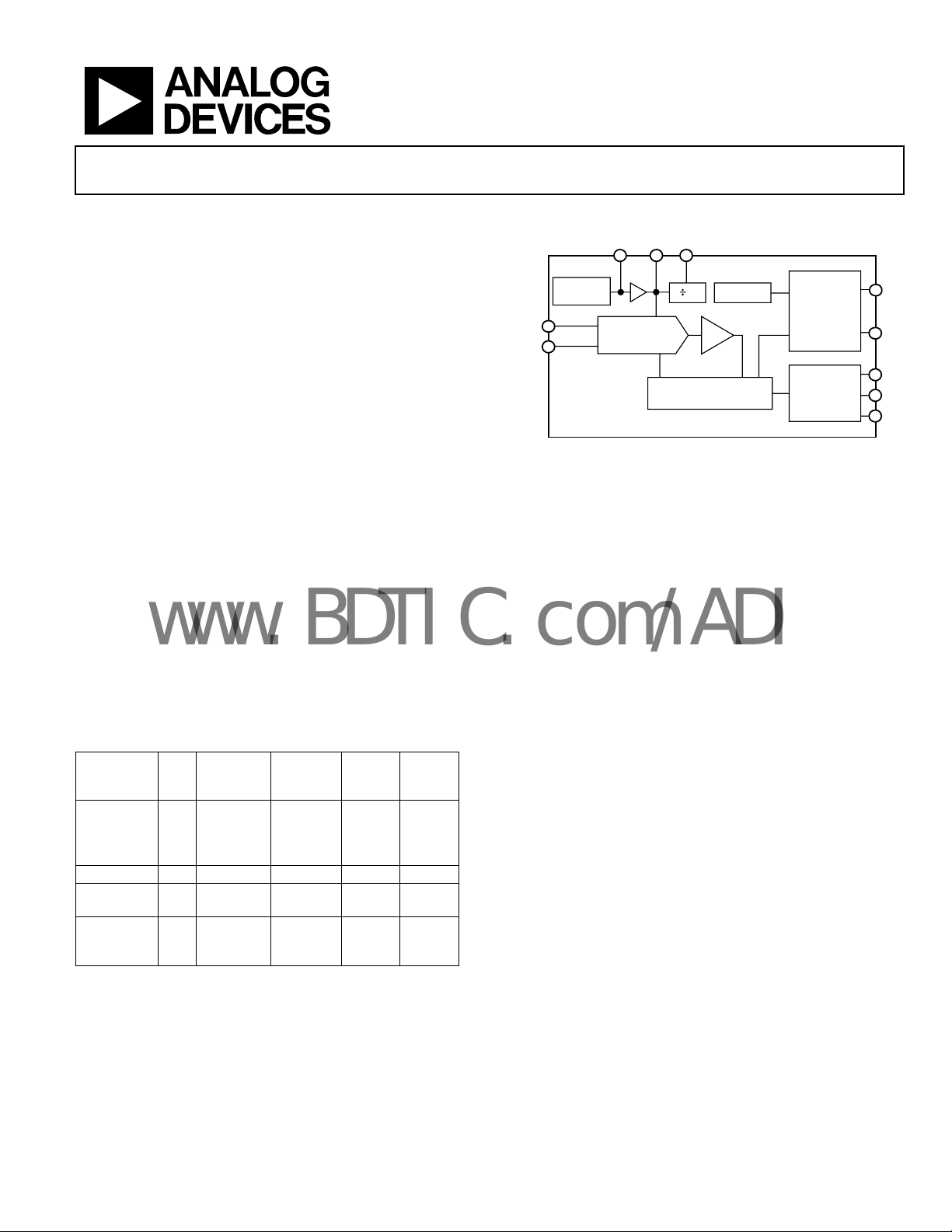

FUNCTIONAL BLOCK DIAGRAM

REFIN REF

1.2V

BANDGAP

IN+

IN-

CAP DAC

AD7626

GENERAL DESCRIPTION

The AD7625 is a 16-bit, 6MSPS, charge redistribution successive

approximation register (SAR) architecture, analog-to-digital

converter (ADC). SAR architecture allows unmatched

performance both in noise – 92dB SNR - and in linearity –

1LSB. The AD7625 contains a high speed 16-bit sampling ADC,

an internal conversion clock, and an internal buffered reference.

On the CNV edge, it samples the voltage difference between

IN+ and IN− pins. The voltages on these pins swing in opposite

phase between 0 V and REF. The 4.096V reference voltage, REF,

can be generated internally or applied externally.

All converted results are available on a single LVDS self-clocked

or echoed-clock serial interface reducing external hardware

connections.

The AD7625 is housed in a 32-lead LFCSP (5mm by 5mm) with

operation specified from −40°C to +85°C.

CM

2

SAR

Figure 1.

CLOCK

LOGIC

SERIAL

LVDS

VIO

CNV

D

DCO

CLK

Rev. PrB

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

AD7625 Preliminary Technical Data

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Specifications..................................................................................... 3

Timing Specifications .................................................................. 4

Absolute Maximum Ratings............................................................ 5

Thermal Resistance.......................................................................5

ESD Caution...................................................................................5

Pin Configuration and Function Descriptions..............................6

Terminology.......................................................................................8

Theory of Operation .........................................................................9

Outline Dimensions....................................................................... 11

Rev. PrB | Page 2 of 11

Preliminary Technical Data AD7625

www.BDTIC.com/ADI

SPECIFICATIONS

VDD1 = 5 V; VDD2 = 2.5 V; VIO = 2.5 V; V

Table 2.

Parameter Conditions Min Typ Max Unit

RESOLUTION 16 Bits

ANALOG INPUT

Voltage Range V

Operating Input Voltage V

Common Mode Input Range V

Analog Input CMRR fIN = 1 MHz 60 dB

Input Current 6 MSPS throughput 350 μA

THROUGHPUT SPEED

Complete Cycle 166 ns

Throughput Rate 0.001 6 MSPS

DC ACCURACY

Integral Linearity Error -2 ±1 +2 LSB

No Missing Codes 16 Bits

Differential Linearity Error -1 ±0.3 +1 LSB

Transition Noise 0.6 LSB

Zero Error, T

MIN

to T

±100 μV

MAX

Zero Error Drift 1 ppm/°C

Gain Error, T

MIN

to T

50 ppm of FS

MAX

Gain Error Drift 1 ppm/°C

Power Supply Sensitivity VDD1 = 5 V ± 5% TBD LSB

VDD2 = 2.5 V ± 5% TBD LSB

AC ACCURACY

Dynamic Range 90 92 dB

Signal-to-Noise fIN = 250 kHz 90 92 dB

Spurious-Free Dynamic Range fIN = 250 kHz 110 dB

f

Total Harmonic Distortion fIN = 250 kHz -110 dB

f

Signal-to-(Noise + Distortion) fIN = 250 kHz 92 dB

−3 dB Input Bandwidth 100 MHz

Aperture Delay ns

Aperture jitter 5 ps rms

Transient Response Full-Scale Step 50 ns

INTERNAL REFERENCE

Output Voltage REFIN @ 25°C 1.2 V

Temperature Drift −40°C to +85°C ±7 ppm/°C

REFERENCE BUFFER

REFIN Input Voltage Range 1.2 V

REF Output Voltage range 4.096 V

EXTERNAL REFERENCE

Voltage Range REF 4.096 V

VCM @ 25°C

Output Voltage V

Output Impedance 4 5 6 kΩ

= 4.096 V; all specifications T

REF

− V

IN+

IN+

IN

IN

−V

IN−

, V

to AGND −0.1 +V

IN−

= TBD 90 dB

= TBD -90 dB

MIN

to T

, unless otherwise noted.

MAX

+V

REF

/2 – 0.1 V

REF

REF

REF

V

REF

+ 0.1 V

REF

/2 V

/2 + 0.1 V

REF

/2 V

REF

/2

Rev. PrB | Page 3 of 11

AD7625 Preliminary Technical Data

www.BDTIC.com/ADI

Parameter Conditions Min Typ Max Unit

LVDS I/O, (ANSI-644)

Data Format Serial LVDS Two’s complement

VOD Differential Output Voltage,

=100 Ω

R

L

V

OCM

Common mode Output Voltage,

=100Ω

R

L

247 350 454 mV

1125 1250 1375 mV

VID Differential Input Voltage 100 650 mV

V

Common mode Input Voltage 800 1575 mV

ICM

POWER SUPPLIES

Specified Performance

VDD1 4.75V 5 5.25V V

VDD2 2.37 2.5 2.63 V

VIO 2.3 2.5 2.7 V

Operating Currents

VDD1 10 mA

VDD2 25 mA

VIO Self-clocked mode 14 mA

VIO Echoed-clock mode 18 mA

Power Dissipation1

With Internal Reference 6 MSPS throughput 140 mW

Without Internal Reference 6 MSPS throughput 120 mW

Energy per conversion 6 MSPS throughput 10 nJ/sample

TEMPERATURE RANGE

Specified Performance T

1

Power dissipation is for the AD7626 only. In self-clocked interface, 9mW is dissipated in the 100 ohm terminator. In echoed-clock interface, 18mW is dissipated in (2)

100 ohm terminators.

MIN

to T

−40 +85 °C

MAX

TIMING SPECIFICATIONS

VDD1 = 5 V; VDD2 = 2.5 V; VIO = 2.3V to 2.7 V; V

Table 3.

Parameter Symbol Min Typ Max Unit

Time between conversion t

Acquisition time t

CNV high time t

CNV to D (MSB) delay t

CNV to last CLK (LSB) delay t

CLK period t

CLK frequency f

CLK to DCO delay (echoed-clock mode) t

DCO to D delay (echoed-clock mode) tD -1 0 1 ns

CLK to D delay t

= 4.096 V; all specifications T

REF

100 ns

CYC

40 10000 ns

ACQ

10 40 ns

CNVH

166 ns

MSB

120 ns

CLKL

TBD 4 ns

CLK

250 400 MHz

CLK

0 4 7 ns

DCO

0 4 7 ns

CLKD

MIN

to T

, unless otherwise noted.

MAX

Rev. PrB | Page 4 of 11

Loading...

Loading...