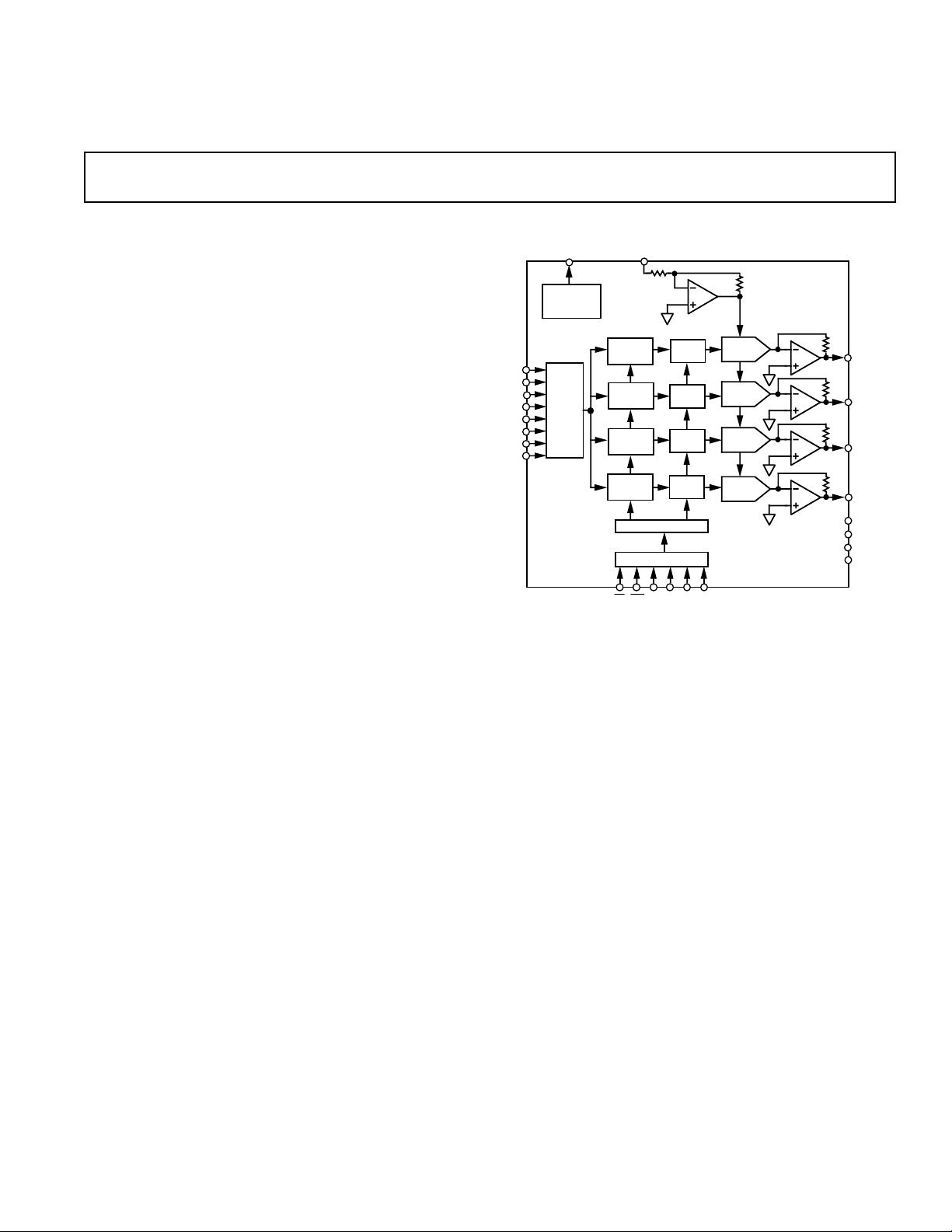

VOLTAGE

REFERENCE

TTL

INPUTS

8-BIT

BUS

INPUT

LATCHES

DAC

LATCHES

+5V

D7

D6

D5

D4

D3

D2

D1

D0

CONTROL LOGIC

TTL INPUTS

A3 A2 A1 A0

2.22k

+12V

10k

V

REFOUT

V

REFIN

CS WR

V

OUT3

V

OUT2

V

OUT1

V

OUT0

V

DD

V

SS

AGND

DGND

8 + 4-BIT

LATCHES

8 + 4-BIT

LATCHES

8 + 4-BIT

LATCHES

8 + 4-BIT

LATCHES

12-BIT

LATCH

–12V

12-BIT

DAC

12-BIT

DAC

12-BIT

DAC

12-BIT

DAC

12-BIT

LATCH

12-BIT

LATCH

12-BIT

LATCH

10k

10k

10k

AD75004

Quad 12-Bit

a

FEATURES

4 Complete 12-Bit D/A Functions

Double-Buffered Latches

Simultaneous Update of All DACs Possible

65 V Output Range

High Stability Bandgap Reference

Monolithic BiMOS Construction

Guaranteed Monotonic over Temperature

3/4 LSB Linearity Guaranteed over Temperature

4 ms max Settling Time to 0.01%

Operates with 612 V Supplies

Low Power: 720 mW max Including Reference

TTL/5 V CMOS Compatible Logic Inputs

8-Bit Microprocessor Interface

24-Pin PDIP or 28-Lead PLCC Package

PRODUCT DESCRIPTION

The AD75004 contains four complete, voltage output, 12-bit

digital-to-analog converters, a high stability bandgap reference,

and double-buffered input latches on a single chip. The converters use 12 precision high speed bipolar current steering switches

and laser-trimmed thin-film resistor networks to provide fast

settling time and high accuracy.

Microprocessor compatibility is achieved by the on-chip

double-buffered latches. The design of the input latches allows

direct interface to 8-bit buses. The 12 bits of data from the first

rank of latches can then be transferred to the second rank,

avoiding generation of spurious analog output values. The latch

responds to strobe pulses as short as 50 ns, allowing use with

fast microprocessors.

The functional completeness and high performance of the

AD75004 results from a combination of advanced switch design, the BiMOS II fabrication process, and proven laser trimming technology. BiMOS II is an epitaxial BiCMOS process

optimized for analog and converter functions. The AD75004 is

trimmed at the wafer level and is specified to ± 1/2 LSB maximum linearity error at 25°C and ±3/4 LSB over the full operating temperature range. The on-chip output amplifiers provide

an output range of ±5 V, with 1 LSB equal to 2.44 mV.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

D/A Converter

AD75004

FUNCTIONAL BLOCK DIAGRAM

The bandgap reference on the chip has low noise, long term

stability and temperature drift characteristics comparable to

discrete reference diodes. The absolute value of the reference is

laser trimmed to +5.00 V with 0.6% maximum error. Its temperature coefficient is also laser trimmed.

Typical full-scale gain TC is 15 ppm/°C. With guaranteed

monotonicity over the full temperature range, the AD75004 is

well suited for wide temperature range performance.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

AD75004–SPECIFICA TIONS

(TA = +258C, 612.0 V power supplies unless otherwise noted)

Parameter Symbol Min Typ Max Units

DIGITAL INPUTS (D0–D7, A0–A3, CS, WR)

Logic Levels (TTL Compatible)

Input Voltage, Logic “1” V

Input Voltage, Logic “0” V

Input Current, V

Input Current, V

= 5.5 V I

IH

= 0.8 V I

IL

Input Capacitance C

IH

IL

IH

IL

IN

2.0 5.5 V

0 0.8 V

10 µA

10 µA

10 pF

ACCURACY

Resolution 12 Bits

Integral Linearity Error ±1/4 61/2 LSB

Integral Linearity Error, T

MIN

to T

MAX

±1/2 ±3/4 LSB

Differential Linearity Error ±1/2 63/4 LSB

Differential Linearity Error, T

Gain (Full-Scale) Error

Gain Error Drift, T

Bipolar Zero Error

1

to T

MIN

1

Bipolar Zero Error Drift, T

MAX

MIN

MIN

1

to T

to T

MAX

MAX

1

Guaranteed Monotonic

±2 610 LSB

±15 ±30 ppm/°C

±1 62 LSB

±3 ±7 ppm/°C

CHANNEL-TO-CHANNEL MISMATCH

Integral Linearity Error ±1/2 61 LSB

Gain Error

Bipolar Zero Error

1

1

±1 64 LSB

±1 62 LSB

DYNAMIC PERFORMANCE

Settling Time to ±0.01% of FSR

for FSR Change, 2 kΩ || 500 pF Load 2 4 µs

Slew Rate, 2 kΩ || 500 pF Load 5 V/µs

Digital Input Crosstalk (Static)

2

–50 dB

ANALOG OUTPUTS

Full-Scale Range (FSR) V

Output Current I

OUT

OUT

±5mA

±5V

Short Circuit Limit Current 640 mA

VOLTAGE REFERENCE

Reference Output Voltage V

Temperature Coefficient ±15 ± 25 ppm/°C

Reference Output Currents

3

Reference Input Voltage V

Reference Input Current @ 5.0 V I

POWER SUPPLY GAIN SENSITIVITY

∆Gain/∆V

, VDD = +10.8 to +13.2 V dc

DD

∆Gain/∆VSS, VSS = –10.8 to –13.2 V dc

1

1

REFOUT

REFIN

REFIN

4.97 5.00 5.03 V

3.0 5.0 mA

4.5 5.0 5.5 V

3.0 mA

±15 625 ppm of FSR/%

±15 625 ppm of FSR/%

POWER SUPPLY REQUIREMENTS

Voltage Range V

Supply Currents IDD, I

DD

, V

SS

SS

610.8 ±12 613.2 V

±25 630 mA

TEMPERATURE RANGE

Specification T

MIN

, T

MAX

0 +70 °C

Storage –65 +150 °C

NOTES

1

Gain and bipolar zero errors are measured using internal voltage reference and include its errors.

2

Digital crosstalk is defined as the change in any one output’s steady state value as a result of any other output being driven from V

2 kΩ || 500 pF load by means of varying the digital input code.

3

The internal voltage reference is intended to drive on-chip only; buffer it if using it externally.

4

All minimum and maximum specifications are guaranteed, and specifications shown in boldface are tested on all production units at final electrical test. Results from

those tests are used to calculate outgoing quality levels.

Specifications subject to change without notice.

OUTMIN

to V

OUTMAX

into a

–2–

REV. A

Loading...

Loading...