V

V

Isolated Sigma-Delta Modulator

FEATURES

20 MHz maximum external clock rate

Second-order modulator

16 bits no missing codes

±2 LSB INL typical at 16 bits

3.5 μV/°C maximum offset drift

On-board digital isolator

On-board reference

Low power operation: 20 mA maximum at 5.25 V

−40°C to +105°C operating range

16-lead SOIC package

Safety and regulatory approvals

UL recognition

5000 V rms for 1 minute per UL 1577

CSA Component Acceptance Notice #5A

VDE Certificate of Conformity

DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

V

= 891 V peak

IORM

APPLICATIONS

AC motor controls

Data acquisition systems

A/D + opto-isolator replacements

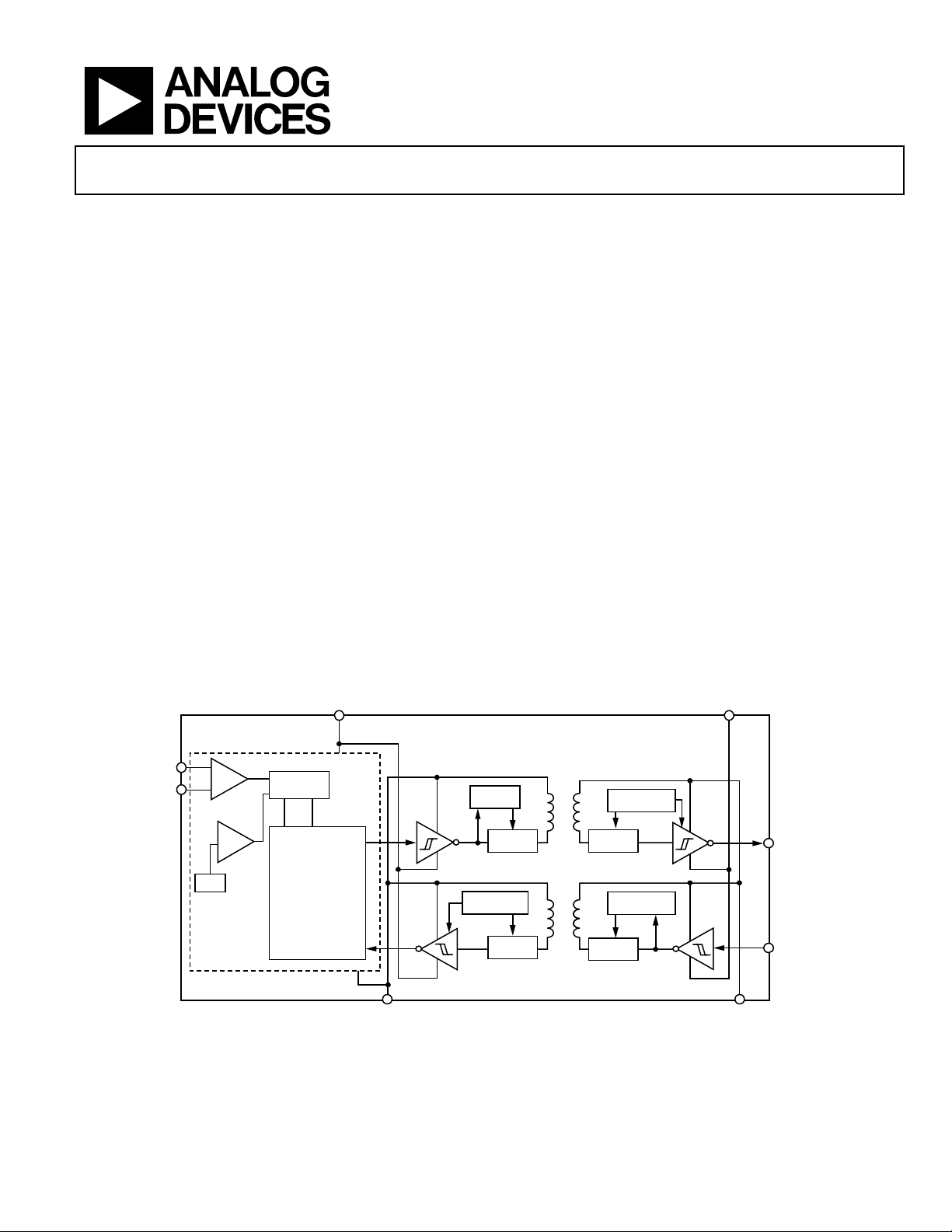

FUNCTIONAL BLOCK DIAGRAM

DD1

AD7401

GENERAL DESCRIPTION

The AD74011 is a second-order, sigma-delta (Σ-Δ) modulator

that converts an analog input signal into a high speed, 1-bit data

stream with on-chip digital isolation based on Analog Devices,

Inc. iCoupler® technology. The AD7401 operates from a 5 V

power supply and accepts a differential input signal of ±200 mV

(±320 mV full scale). The analog input is continuously sampled

by the analog modulator, eliminating the need for external

sample-and-hold circuitry. The input information is contained

in the output stream as a density of ones with a data rate up to

20 MHz. The original information can be reconstructed with an

appropriate digital filter. The serial I/O can use a 5 V or a 3 V

supply (V

The serial interface is digitally isolated. High speed CMOS,

combined with monolithic air core transformer technology,

means the on-chip isolation provides outstanding performance

characteristics, superior to alternatives such as optocoupler

devices. The part contains an on-chip reference. The AD7401

is offered in a 16-lead SOIC and has an operating temperature

range of −40°C to +105°C.

An internal clock version, AD7400, is also available.

1

Protected by U.S. Patents 5,952,849; 6,873,065; and 7,075,329.

DD2

).

DD2

VIN+

VIN–

REF

H

/

T

U

B

F

Σ-∆ ADC

CONTROL LOGIC

GND

1

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

UPDATE

ENCODE DECODE

WATCHDOG

DECODE

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006–2011 Analog Devices, Inc. All rights reserved.

WATCHDOG

ENCODE

AD7401

UPDATE

GND

MDAT

MCLKIN

2

05851-001

AD7401

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Timing Specifications .................................................................. 4

Insulation and Safety-Related Specifications............................ 5

Regulatory Information............................................................... 5

DIN V VDE V 0884-10 (VDE V 0884-10) Insulation

Characteristics .............................................................................. 6

Absolute Maximum Ratings............................................................ 7

ESD Caution.................................................................................. 7

Pin Configuration and Function Descriptions............................. 8

REVISION HISTORY

7/11—Rev. C to Rev. D

Changes to Minimum External Air Gap (Clearance) Parameter,

Table 3 and Minimum External Tracking (Creepage) Parameter,

Table 3 ................................................................................................ 5

Changes to Figure 5; Pin 1 Description, Table 8; and Pin 7

Description, Table 8.......................................................................... 8

1/11—Rev. B to Rev. C

Changes to Features Section............................................................ 1

Changes to Input-to-Output Momentary Withstand Voltage

Parameter, Table 3, UL Column, Table 4, and Note 1, Table 4 .......... 5

Changes to Ordering Guide...................................................................18

Typical Performance Characteristics..............................................9

Terminology.................................................................................... 12

Theory of Operation ...................................................................... 13

Circuit Information.................................................................... 13

Analog Input............................................................................... 13

Differential Inputs...................................................................... 14

Digital Filter ................................................................................ 15

Applications Information.............................................................. 17

Grounding and Layout.............................................................. 17

Evaluating the AD7401 Performance...................................... 17

Insulation Lifetime..................................................................... 17

Outline Dimensions....................................................................... 18

Ordering Guide .......................................................................... 18

9/07—Rev. A to Rev. B

Updated VDE Certification Throughout ......................................1

Changes to Table 6.............................................................................7

12/06—Rev. 0 to Rev. A

Changes to Features and General Description ..............................1

Changes to Table 1.............................................................................3

Changes to Table 2.............................................................................4

Changes to Table 6.............................................................................7

Changes to Table 8.............................................................................8

Changes to Circuit Information Section ..................................... 13

Changes to Figure 27...................................................................... 15

1/06—Revision 0: Initial Version

Rev. D | Page 2 of 20

AD7401

SPECIFICATIONS

V

= 4.5 V to 5.25 V, V

DD1

f

= 16 MHz maximum, tested with Sinc3 filter, 256 decimation rate, as defined by Verilog code, unless otherwise noted.

MCLK

= 3 V to 5.5 V, VIN+ = −200 mV to +200 mV, and VIN− = 0 V (single-ended); TA = T

DD2

MIN

to T

MAX

,

Table 1.

Parameter Y Version

STATIC PERFORMANCE

Resolution

Integral Nonlinearity

3

16 Bits min Filter output truncated to 16 bits

±15 LSB max −40°C to +85°C; ±2 LSB typical; f

1, 2

Unit Test Conditions/Comments

= 20 MHz maximum4

MCLK

±25 LSB max >85°C to 105°C

±55 LSB max f

Differential Nonlinearity

Offset Error

3

3

±0.9 LSB max

±0.6 mV max f

= 20 MHz maximum4; VIN+ = −250 mV to +250 mV

MCLK

Guaranteed no missed codes to 16 bits;

f

= 20 MHz maximum4; VIN+ = −250 mV to +250 mV

MCLK

= 20 MHz maximum4; VIN+ = −250 mV to +250 mV

MCLK

±50 μV typ TA = 25°C

Offset Drift vs. Temperature

3.5 μV/°C max −40°C to +105°C

1 μV/°C typ

Offset Drift vs. V

DD1

120 μV/V typ

Gain Error3 ±1.6 mV max −40°C to +85°C

±2 mV max >85°C to 105°C

±1 mV typ f

= 20 MHz maximum4; VIN+ = −250 mV to +250 mV

MCLK

Gain Error Drift vs. Temperature 23 μV/°C typ −40°C to +105°C

Gain Error Drift vs. V

110 μV/V typ

DD1

ANALOG INPUT

Input Voltage Range

±200 mV min/mV max For specified performance; full range ±320 mV

Dynamic Input Current ±9 μA max VIN+ = 400 mV, VIN− = 0 V

DC Leakage Current ±0.5 μA max

Input Capacitance 10 pF typ

DYNAMIC SPECIFICATIONS VIN+ = 5 kHz, 400 mV p-p sine

Signal-to-(Noise + Distortion) Ratio (SINAD)3 70 dB min −40°C to +85°C; f

68 dB min −40°C to +85°C; f

= 9 MHz to 20 MHz4

MCLK

= 5 MHz to <9 MHz

MCLK

65 dB min >85°C to 105°C

65 dB min f

= 20 MHz maximum4; VIN+ = −250 mV to +250 mV

MCLK

81 dB typ

Signal-to-Noise Ratio (SNR) 80 dB min −40°C to +105°C; 82 dB typ

80 dB min f

Total Harmonic Distortion (THD)3 −92 dB typ f

= 20 MHz maximum4; VIN+ = −250 mV to +250 mV

MCLK

= 20 MHz maximum4; VIN+ = −250 mV to +250 mV

MCLK

Peak Harmonic or Spurious Noise (SFDR)3 −92 dB typ

Effective Number of Bits (ENOB)3 11.5 Bits

Isolation Transient Immunity3 25 kV/μs min

LOGIC INPUTS

Input High Voltage, VIH 0.8 × V

Input Low Voltage, VIL 0.2 × V

30 kV/μs typ

V min

DD2

V max

DD2

Input Current, IIN ±0.5 μA max

Input Capacitance, C

5

10 pF max

IN

Rev. D | Page 3 of 20

AD7401

T

Parameter Y Version

1, 2

Unit Test Conditions/Comments

LOGIC OUTPUTS

Output High Voltage, VOH V

− 0.1 V min IO = −200 μA

DD2

Output Low Voltage, VOL 0.4 V max IO = +200 μA

POWER REQUIREMENTS

V

4.5/5.25 V min/V max

DD1

V

3/5.5 V min/V max

DD2

6

I

12 mA max V

DD1

7

I

DD2

8 mA max V

4 mA max V

1

Temperature range is −40°C to +85°C.

2

All voltages are relative to their respective ground.

3

See the section. Terminology

4

For f

> 16 MHz to 20 MHz, mark space ratio is 48/52 to 52/48, V

MCLK

5

Sample tested during initial release to ensure compliance.

6

See . Figure 15

7

See . Figure 17

= V

= 5 V ± 5%, and TA = −40°C to +85°C.

DD1

DD2

= 5.25 V

DD1

= 5.5 V

DD2

= 3.3 V

DD2

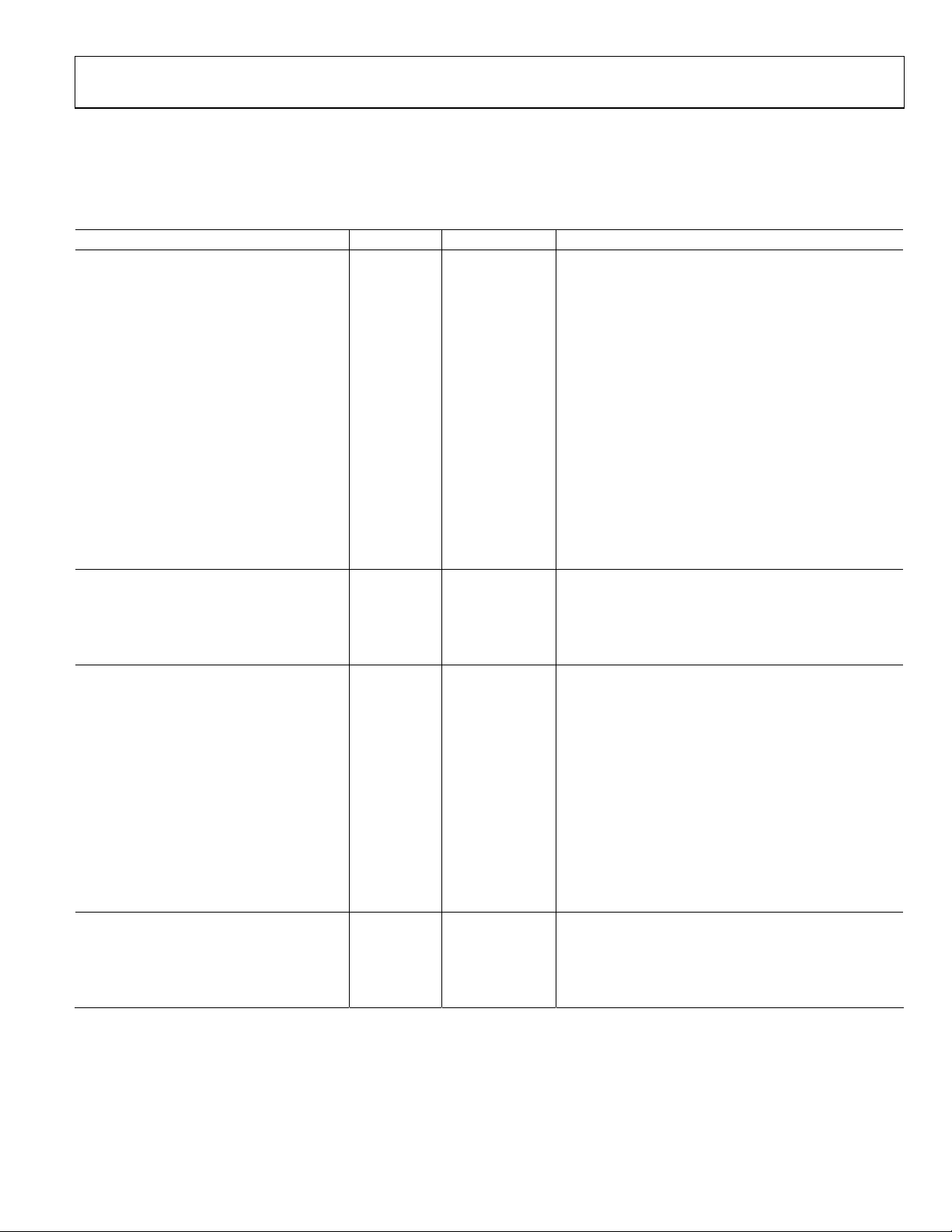

TIMING SPECIFICATIONS

V

= 4.5 V to 5.25 V, V

DD1

Table 2.

Parameter Limit at T

2, 3

f

20 MHz max Master clock input frequency

MCLKIN

5 MHz min Master clock input frequency

4

t

1

4

t

2

t3 0.4 × t

t

4

1

Sample tested during initial release to ensure compliance

2

Mark space ratio for clock input is 40/60 to 60/40 for f

3

V

= V

= 5 V ± 5% for f

DD1

DD2

4

Measured with the load circuit of and defined as the time required for the output to cross 0.8 V or 2.0 V. Figure 2

= 3 V to 5.5 V, TA = T

DD2

, T

MIN

MAX

to T

MAX

, unless otherwise noted.1

MIN

Unit Description

25 ns max Data access time after MCLK rising edge

15 ns min Data hold time after MCLK rising edge

ns min Master clock low time

MCLKIN

0.4 × t

ns min Master clock high time

MCLKIN

> 16 MHz to 20 MHz.

MCLKIN

to 16 MHz and 48/52 to 52/48 for f

MCLKIN

> 16 MHz to 20 MHz.

MCLKIN

O OUTPUT

PIN

25pF

C

200µA I

L

200µA I

OL

1.6V

OH

05851-002

Figure 2. Load Circuit for Digital Output Timing Specifications

t

4

MCLKIN

MDAT

t

1

Figure 3. Data Timing

Rev. D | Page 4 of 20

t

2

t

3

05851-003

AD7401

INSULATION AND SAFETY-RELATED SPECIFICATIONS

Table 3.

Parameter Symbol Value Unit Conditions

Input-to-Output Momentary Withstand Voltage V

Minimum External Air Gap (Clearance) L(I01) 8.1 min mm

Minimum External Tracking (Creepage) L(I02) 7.46 min mm

Minimum Internal Gap (Internal Clearance) 0.017 min mm Insulation distance through insulation

Tracking Resistance (Comparative Tracking Index) CTI >175 V DIN IEC 112/VDE 0303 Part 1

Isolation Group IIIa Material Group (DIN VDE 0110, 1/89, Table I)

REGULATORY INFORMATION

Table 4.

UL1 CSA VDE2

Recognized under 1577

Component Recognition Program

5000 V rms Isolation Voltage

File E214100 File 205078 File 2471900-4880-0001

1

In accordance with UL 1577, each AD7401 is proof tested by applying an insulation test voltage ≥ 6000 V rms for 1 second (current leakage detection limit = 15 μA).

2

In accordance with DIN V VDE V 0884-10, each AD7401 is proof tested by applying an insulation test voltage ≥ 1671 V peak for 1 second (partial discharge detection

limit = 5 pC).

Approved under CSA Component

1

Acceptance Notice #5A

Reinforced insulation per CSA

60950-1-03 and IEC 60950-1, 630 V

rms maximum working voltage

5000 min V rms 1-minute duration

ISO

Measured from input terminals to output

terminals, shortest distance through air

Measured from input terminals to output

terminals, shortest distance path along body

Certified according to DIN V VDE V 0884-10 (VDE V 0884-

10):2006-122

Reinforced insulation per DIN V VDE V 0884-10 (VDE V 0884-

10):2006-12, 891V peak

Rev. D | Page 5 of 20

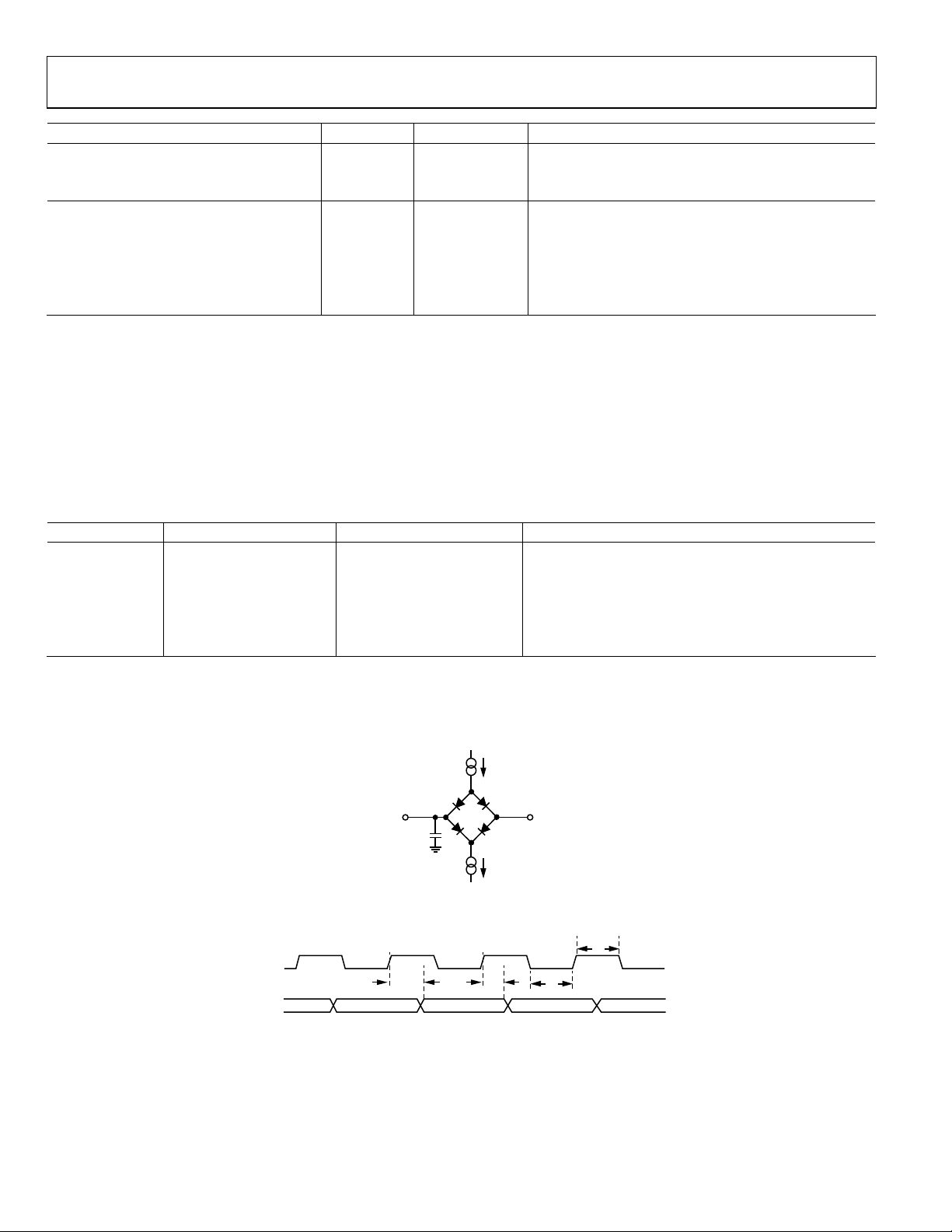

AD7401

DIN V VDE V 0884-10 (VDE V 0884-10) INSULATION CHARACTERISTICS

This isolator is suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by

means of protective circuits.

Table 5.

Description Symbol Characteristic Unit

INSTALLATION CLASSIFICATION PER DIN VDE 0110

For Rated Mains Voltage ≤ 300 V rms I–IV

For Rated Mains Voltage ≤ 450 V rms I–II

For Rated Mains Voltage ≤ 600 V rms I–II

CLIMATIC CLASSIFICATION 40/105/21

POLLUTION DEGREE (DIN VDE 0110, TABLE I) 2

MAXIMUM WORKING INSULATION VOLTAGE V

INPUT-TO-OUTPUT TEST VOLTAGE, METHOD B1

V

× 1.875 = VPR, 100% Production Test, tm = 1 sec, Partial Discharge < 5 pC VPR 1671 V peak

IORM

INPUT-TO-OUTPUT TEST VOLTAGE, METHOD A VPR

After Environmental Test Subgroup 1 1426 V peak

V

× 1.6 = VPR, tm = 60 sec, Partial Discharge < 5 pC

IORM

After Input and/or Safety Test Subgroup 2/3 1069 V peak

V

× 1.2 = VPR, tm = 60 sec, Partial Discharge < 5 pC

IORM

HIGHEST ALLOWABLE OVERVOLTAGE (TRANSIENT OVERVOLTAGE, tTR = 10 sec) VTR 6000 V peak

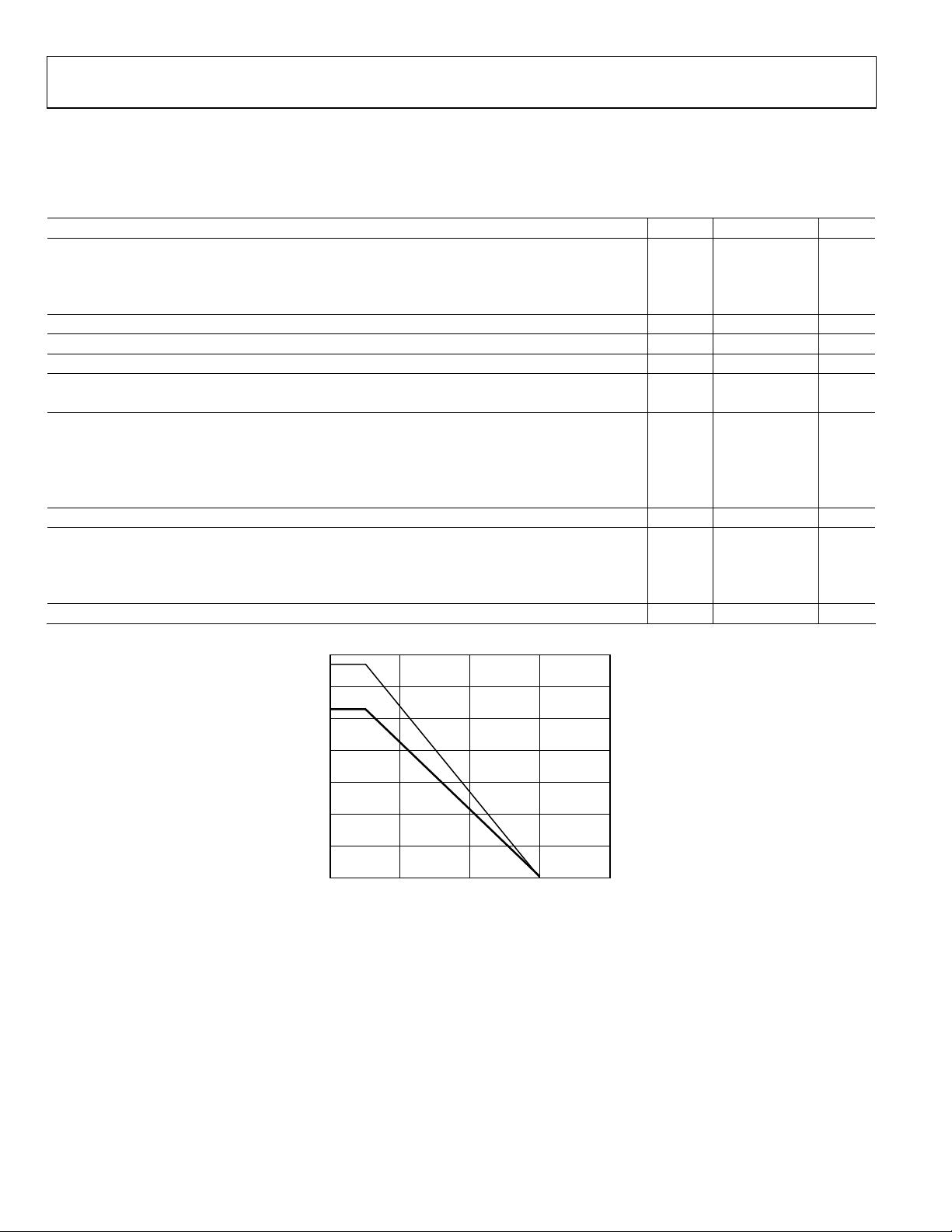

SAFETY-LIMITING VALUES (MAXIMUM VALUE ALLOWED IN THE EVENT OF A FAILURE, ALSO SEE Figure 4)

Case Temperature TS 150 °C

Side 1 Current IS1 265 mA

Side 2 Current IS2 335 mA

INSULATION RESISTANCE AT TS, VIO = 500 V RS >109 Ω

350

891 V peak

IORM

300

250

200

150

100

SAFETY-LIMI TING CURRENT (mA)

50

0

0

Figure 4. Thermal Derating Curve, Dependence of Safety-Limiting Values

with Case Temperature per DIN V VDE V 0884-10

SIDE #2

SIDE #1

50 100 150 200

CASE TEMPE RATURE (°C)

5851-004

Rev. D | Page 6 of 20

Loading...

Loading...