Dual Precision, Low Cost,

A

G

FEATURES

Supports defense and aerospace applications (AQEC

standard)

Military temperature range (−55°C to +125°C)

Controlled manufacturing baseline

One assembly/test site

One fabrication site

Enhanced product change notification

Qualification data available on request

Enhanced replacement for LF412 and TL082

AC performance

Settles to ±0.01% in 1.0 μs

16 V/μs minimum slew rate

3 MHz minimum unity-gain bandwidth

DC performance

150 V/mV minimum open-loop gain

Available in a SOIC_N package

GENERAL DESCRIPTION

The AD712-EP is a high speed, precision, monolithic

operational amplifier offering high performance over the

military temperature range of −55°C to +125°C. Its low offset

voltage and offset voltage drift are the results of advanced laser

wafer trimming technology. These performance benefits allow

the user to easily upgrade existing designs that use older

precision BiFET or bipolar op amps.

The superior ac and dc performance of this op amp makes it

suitable for active filter applications. With a slew rate of 16 V/μs

and a settling time of 1 μs to ±0.01%, the AD712-EP is ideal as a

buffer for 12-bit digital-to-analog converters (DACs) and 12-bit

analog-to-digital converters (ADCs) and as a high speed

integrator.

High Speed BiFET Op Amp

AD712-EP

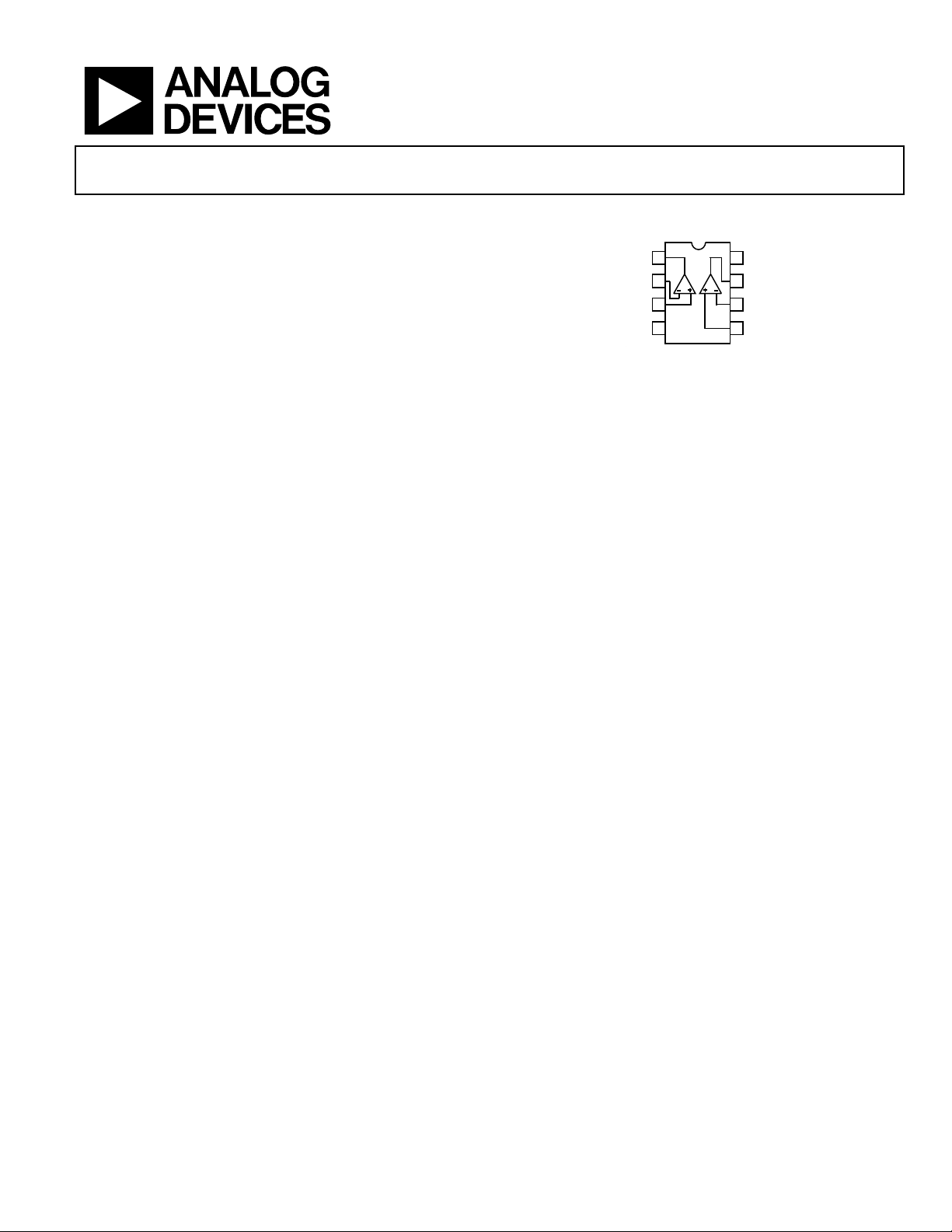

CONNECTION DIAGRAM

MPLIFIER NO. 1

OUTPUT

INVERTING

NONINVERTIN

1

2

INPUT

3

INPUT

V–

4

AD712-EP

Figure 1. 8-Lead SOIC_N (R-Suffix)

The combination of excellent noise performance and low input

current also make the AD712-EP useful for photodiode preamps.

Common-mode rejection of 88 dB and open-loop gain of

400 V/mV ensure 12-bit performance even in high speed unitygain buffer circuits.

The AD712-EP is available in an 8-lead SOIC_N package.

Additional applications information is available in the AD712

data sheet.

AMPLIFIER NO. 2

8

V+

OUTPUT

7

INVERTING

6

INPUT

NONINVERTING

5

INPUT

09285-001

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

AD712-EP

TABLE OF CONTENTS

Features .............................................................................................. 1

Connection Diagram ....................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

REVISION HISTORY

8/10—Revision 0: Initial Version

Absolute Maximum Ratings ............................................................5

ESD Caution...................................................................................5

Typical Performance Characteristics ..............................................6

Outline Dimensions ....................................................................... 10

Ordering Guide .......................................................................... 10

Rev. 0 | Page 2 of 12

AD712-EP

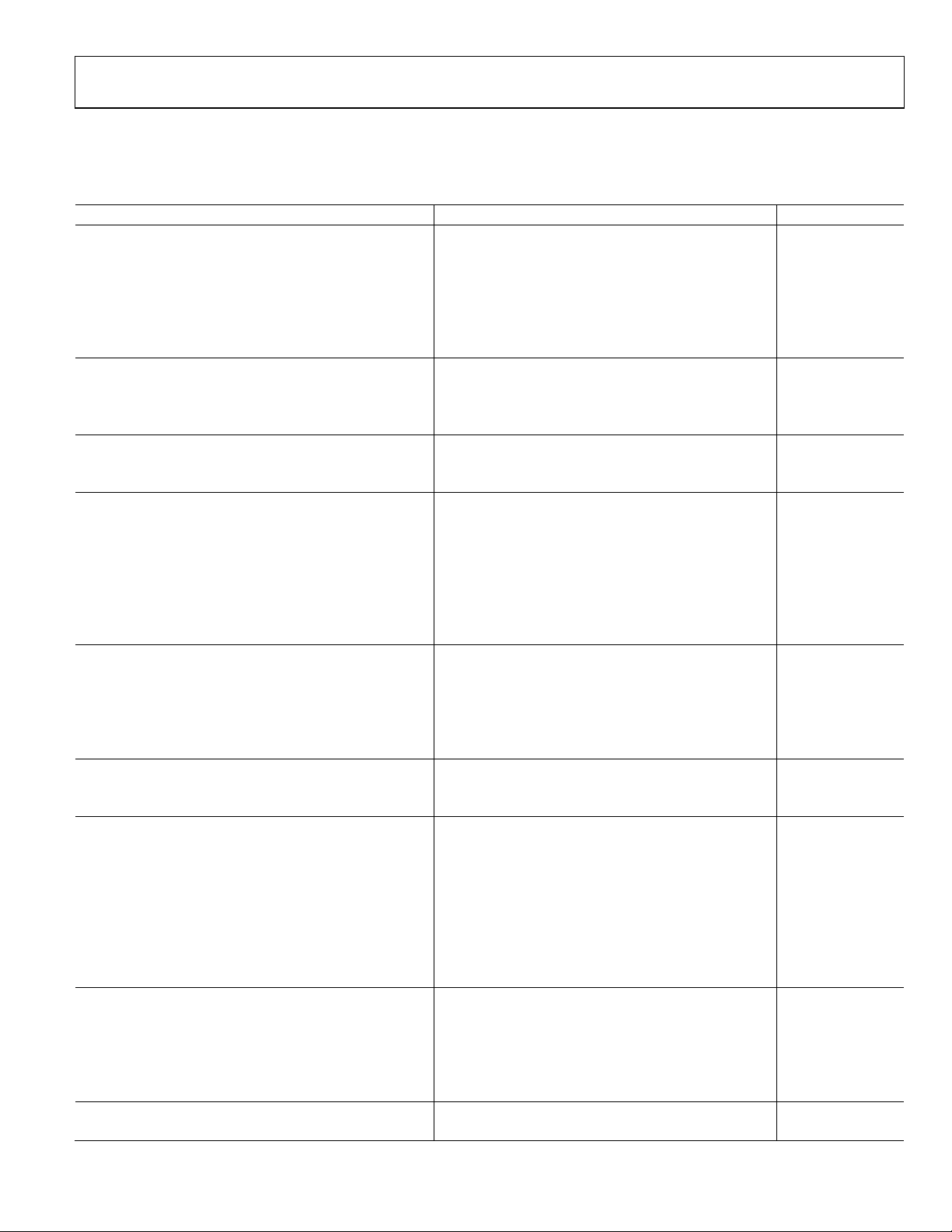

SPECIFICATIONS

VS = ±15 V @ TA = 25°C, unless otherwise noted.

Table 1.

Parameter Min Typ Max Unit

INPUT OFFSET VOLTAGE1

Initial Offset 0.3 3 mV

T

to T

MIN

vs. Temperature 7 20 V/°C

vs. Supply 76 95 dB

T

Long-Term Offset Stability 15 µV/month

INPUT BIAS CURRENT2

VCM = 0 V 25 75 pA

VCM = 0 V @ T

VCM = ±10 V 100 pA

INPUT OFFSET CURRENT

VCM = 0 V 10 25 pA

VCM = 0 V @ T

MATCHING CHARACTERISTICS

Input Offset Voltage 3 mV

T

MIN

Input Offset Voltage Drift 20 µV/°C

Input Bias Current 25 pA

Crosstalk

At f = 1 kHz 120 dB

At f = 100 kHz 90 dB

FREQUENCY RESPONSE

Small Signal Bandwidth 3.0 4.0 MHz

Full Power Response 200 kHz

Slew Rate 16 20 V/µs

Settling Time to 0.01% 1.0 1.2 µs

Total Harmonic Distortion 0.0003 %

INPUT IMPEDANCE

Differential 3 × 1012||5.5 Ω||pF

Common Mode 3 × 1012||5.5 Ω||pF

INPUT VOLTAGE RANGE

Differential3 ±20 V

Common-Mode Voltage4 +14.5, −11.5 V

T

MIN

Common-Mode Rejection Ratio

VCM = ±10 V 76 88 dB

T

VCM = ±11 V 70 84 dB

T

INPUT VOLTAGE NOISE

0.1 Hz to 10 Hz 2 µV p-p

f = 10 Hz 45 nV/√Hz

f = 100 Hz 22 nV/√Hz

f = 1 kHz 18 nV/√Hz

f = 10 kHz 16 nV/√Hz

INPUT CURRENT NOISE

f = 1 kHz 0.01 pA/√Hz

4 mV

MAX

to T

MIN

to T

to T

MIN

MIN

76 dB

MAX

26 77 nA

MAX

11 26 nA

MAX

4 mV

MAX

−VS + 4 +VS − 2 V

MAX

to T

76 84 dB

MAX

to T

70 80 dB

MAX

Rev. 0 | Page 3 of 12

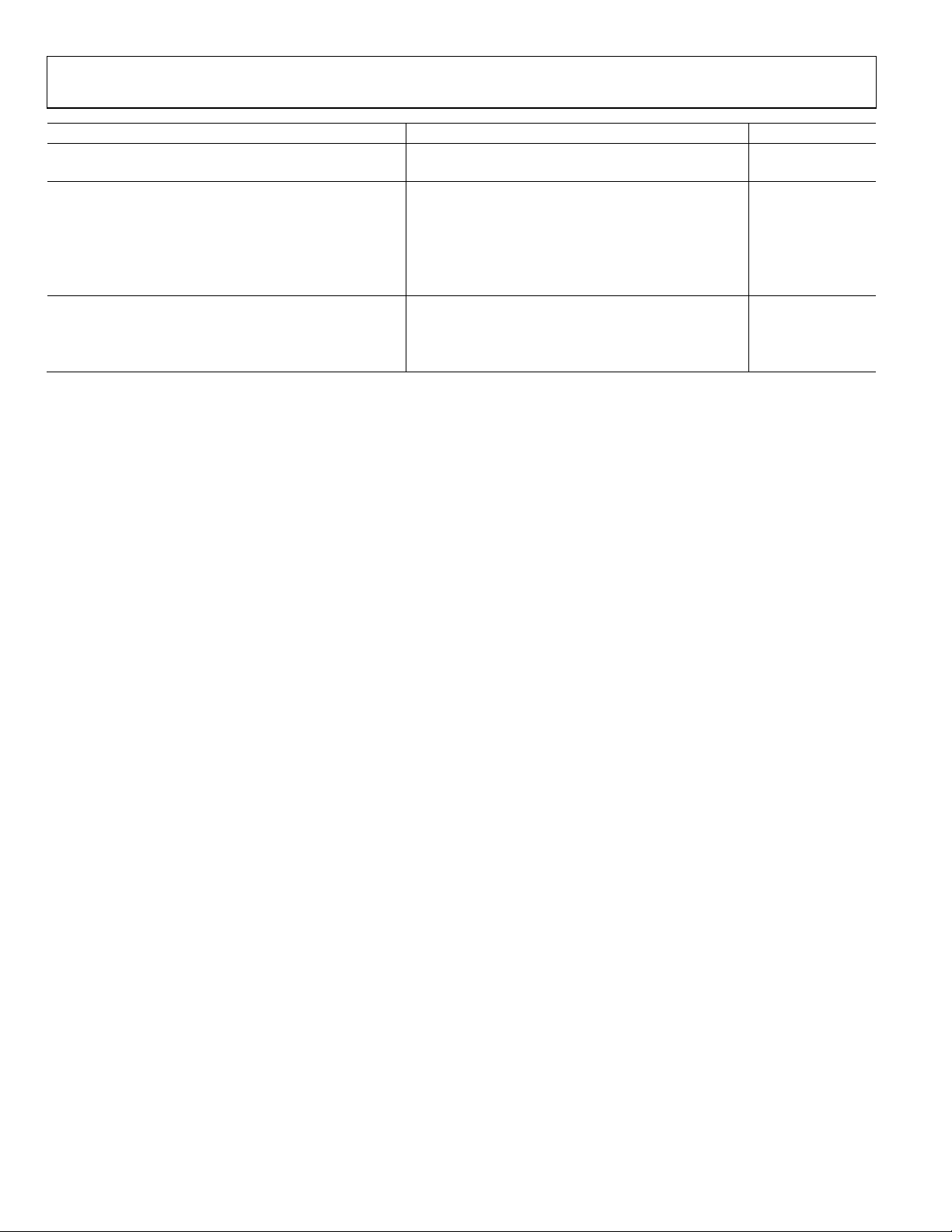

AD712-EP

Parameter Min Typ Max Unit

OPEN-LOOP GAIN 150 V/mV

T

to T

MIN

OUTPUT CHARACTERISTICS

Output Voltage Swing High 13.9 13.0 V

T

Output Voltage Swing Low −12.5 −13.1 V

T

Current 25 mA

POWER SUPPLY

Rated Performance ±15 V

Operating Range ±4.5 ±18 V

Quiescent Current 5.0 6.8 mA

1

Input offset voltage specifications are guaranteed after 5 minutes of operation at TA = 25°C.

2

Bias current specifications are guaranteed maximum at either input after 5 minutes of operation at TA = 25°C. For higher temperatures, the current doubles every 10°C.

3

Defined as voltage between inputs, such that neither exceeds ±10 V from ground.

4

Typically exceeding −14.1 V negative common-mode voltage on either input results in an output phase reversal.

100 V/mV

MAX

to T

MIN

MIN

12.0 V

MAX

to T

−12.0 V

MAX

Rev. 0 | Page 4 of 12

AD712-EP

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage ±18 V

Internal Power Dissipation1

Input Voltage2 ±18 V

Output Short-Circuit Duration Indefinite

Differential Input Voltage +VS and −VS

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −55°C to +125°C

Lead Temperature Range (Soldering 60 sec) 300°C

1

Thermal characteristics: 8-lead SOIC_N, θJA = 100°C.

2

For supply voltages less than ±18 V, the absolute maximum voltage is equal

to the supply voltage.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 5 of 12

AD712-EP

V

TYPICAL PERFORMANCE CHARACTERISTICS

20

6

15

10

= 2kΩ

R

L

25°C

5

INPUT VOLTAGE SWING (V)

0

0510

SUPPLY VOLTAGE ± V

Figure 2. Input Voltage Swing vs. Supply Voltage

20

15

10

5

OUTPUT VOLTAGE SWING (V)

0

05

SUPPLY VOLTAGE ± V

+V

OUT

RL= 2kΩ

25°C

10 15 20

Figure 3. Output Voltage Swing vs. Supply Voltage

15 20

–V

OUT

5

4

3

QUIESCENT CURRENT (mA)

2

09285-002

0 5 10 15 20

SUPPLY VOLTAGE ± V

09285-005

Figure 5. Quiescent Current vs. Supply Voltage

6

10

7

10

8

= 0) (Amps)

10

CM

9

10

10

10

11

10

INPUT BIAS CURRENT (

12

10

–40 –20

09285-003

–60

0 20 40 60 80 100 120 140

TEMPERATURE ( °C)

09285-006

Figure 6. Input Bias Current vs. Temperature

OUTPUT IM PE DANCE (Ω)

0.01

100

1.0

0.1

10

1k

10k 100k 1M 10M

FREQUENCY (Hz)

09285-007

Figure 7. Output Impedance vs. Frequency

30

25

20

±15V SUPPLIES

15

10

OUTPUT VO LTAGE SW ING (V p-p)

5

0

10 100 1k 10k

LOAD RESISTANCE (Ω)

09285-004

Figure 4. Output Voltage Swing vs. Load Resistance

Rev. 0 | Page 6 of 12

AD712-EP

100

100

100

MAX T GRADE LIMIT

75

V

= 15V

S

50

25

INPUT BIAS CURRENT ( pA)

0

–10

–5 0 5 10

COMMON-MODE VOLTAGE (V)

25°C

Figure 8. Input Bias Current vs. Common-Mode Voltage

26

24

22

20

18

16

14

SHORT-CIRCUI T CURRENT LIMIT (mA)

12

– OUTPUT CURRENT

+ OUTPUT CURRENT

80

60

40

20

OPEN-LOOP GAIN (d B)

0

–20

10 100 1k 10k 100k 1M 10M

09285-008

GAIN

PHASE

2kΩ

100pF

LOAD

FREQUENCY (Hz)

80

60

40

20

PHASE MARGIN (Degrees)

0

–20

09285-011

Figure 11. Open-Loop Gain and Phase Margin vs. Frequency

125

120

115

= 2kΩ

R

L

110

105

OPEN-LOOP GAIN (dB)

100

25°C

10

–60

–40 –20 0 20 40 60 80 100 120 140

AMBIENT TEM P ERATURE (°C)

Figure 9. Short-Circuit Current Limit vs. Temperature

5.0

4.5

4.0

3.5

UNITY-GAIN BANDWIDTH (MHz)

3.0

–40 –20 0 20 40 60 80 100 120 140

–60

TEMPERATURE ( °C)

Figure 10. Unity-Gain Bandwidth vs. Temperature

95

0 5 10 15 20

09285-009

SUPPLY VOLTAGE ± V

09285-012

Figure 12. Open-Loop Gain vs. Supply Voltage

110

100

80

60

40

POWER SUPP LY REJECTION (dB)

20

VS = ±15V SUPPLIES

WITH 1V p-p SINEWAVE 25°C

0

10 100 1k 10k 100k 1M

09285-010

SUPPLY MO DUL ATION FREQUENCY (Hz)

+ SUPPLY

– SUPPLY

09285-013

Figure 13. Power Supply Rejection vs. Frequency

Rev. 0 | Page 7 of 12

AD712-EP

–

√

100

CMR (dB)

VS = ±15V

= 1V p-p

V

CM

80

60

40

25°C

THD (dB)

–80

–90

–100

–110

70

3V rms

R

= 2kΩ

L

C

= 100pF

L

20

0

10 100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 14. Common-Mode Rejection (CMR) vs. Frequency

30

25

20

15

10

OUTPUT VOLTAGE SWING (V p-p)

5

0

100k 1M 10M

FREQUENCY (Hz)

RL= 2kΩ

25°C

V

= ±15V

S

Figure 15. Large Signal Frequency Response

10

8

6

4

OUTPUT SWING FROM 0V TO ±VOLTS

–10

2

0

–2

–4

–6

–8

0.5

0.6 0.7

0.01%0.1%1%

0.1%1%ERROR

0.01%

SETTLING TIME (µs)

0.8 0.9 1.0

Figure 16. Output Swing and Error vs. Settling Time

–120

–130

100 1k 10k 100k

09285-014

FREQUENCY (Hz)

09285-017

Figure 17. Total Harmonic Distortion (THD) vs. Frequency

1k

Hz)

100

10

INPUT NOISE VOLTAGE (nV/

1

09285-015

10 100 1k 10k 100k1

FREQUENCY (Hz)

09285-018

Figure 18. Input Noise Voltage Spectral Density

25

20

15

10

SLEW RATE (V/µ s)

5

0

09285-016

0 100

200 300 400 500 600 700 800 900

INPUT ERROR SIGNAL (mV)

(AT SUMMING J UNCTION)

09285-019

Figure 19. Slew Rate vs. Input Error Signal

Rev. 0 | Page 8 of 12

AD712-EP

25

20

SLEW RATE (V/µs)

15

–60 –40 –20

0 20 40 60 80 100 120 140

TEMPERATURE (°C)

Figure 20. Slew Rate vs. Temperature

09285-020

Rev. 0 | Page 9 of 12

AD712-EP

OUTLINE DIMENSIONS

5.00(0.1968)

4.80(0.1890)

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES)ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLYAND ARE NOT APPROPRIATE FOR USE IN DESIGN.

85

1

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-AA

BSC

6.20 (0.2441)

5.80 (0.2284)

4

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

8°

0°

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

1.27 (0.0500)

0.40 (0.0157)

45°

012407-A

Figure 21. 8-Lead Standard Small Outline Package [SOIC_N]

Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

ORDERING GUIDE

Model1 Temperature Range Package Description Package Option

AD712TRZ-EP −55°C to +125°C 8-Lead SOIC_N R-8

AD712TRZ-EP-R7 −55°C to +125°C 8-Lead SOIC_N R-8

1

Z = RoHS Compliant Part.

Rev. 0 | Page 10 of 12

AD712-EP

NOTES

Rev. 0 | Page 11 of 12

AD712-EP

NOTES

©2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D09285-0-8/10(0)

Rev. 0 | Page 12 of 12

Loading...

Loading...