Low Noise, 90 MHz

FEATURES

Linear-in-dB gain control

Pin programmable gain ranges

−11 dB to +31 dB with 90 MHz bandwidth

9 dB to 51 dB with 9 MHz bandwidth

Any intermediate range, for example −1 dB to +41 dB

with 30 MHz bandwidth

Bandwidth independent of variable gain

1.3 nV/√Hz input noise spectral density

±0.5 dB typical gain accuracy

APPLICATIONS

RF/IF AGC amplifier

Video gain control

A/D range extension

Signal measurement

GENERAL DESCRIPTION

The AD603 is a low noise, voltage-controlled amplifier for use

in RF and IF AGC systems. It provides accurate, pin selectable

gains of −11 dB to +31 dB with a bandwidth of 90 MHz or 9 dB

to 51 dB with a bandwidth of 9 MHz. Any intermediate gain

range may be arranged using one external resistor. The input

referred noise spectral density is only 1.3 nV/√Hz and power

consumption is 125 mW at the recommended ±5 V supplies.

The decibel gain is linear in dB, accurately calibrated, and stable

over temperature and supply. The gain is controlled at a high

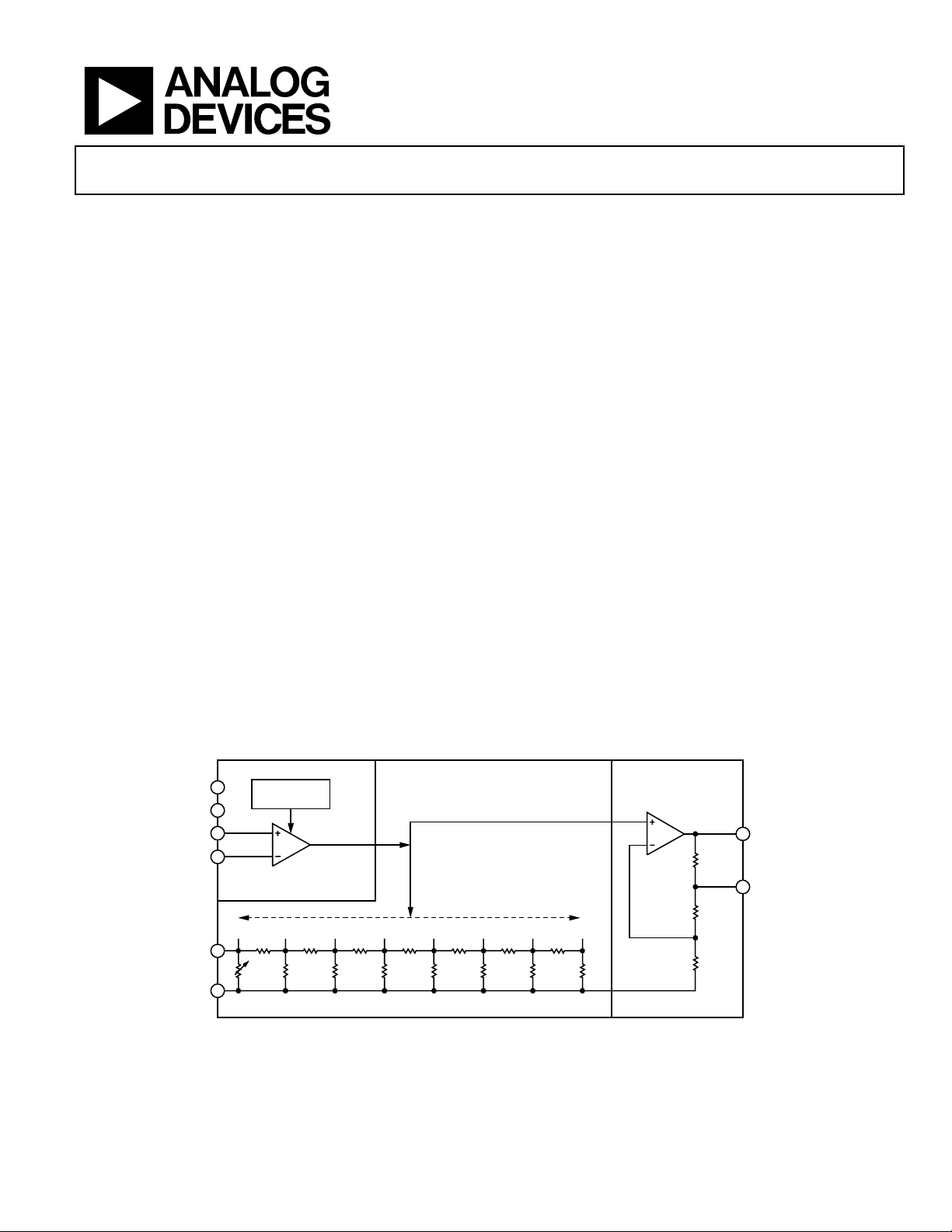

FUNCTIONAL BLOCK DIAGRAM

Variable Gain Amplifier

AD603

impedance (50 MΩ), low bias (200 nA) differential input; the

scaling is 25 mV/dB, requiring a gain control voltage of only 1 V

to span the central 40 dB of the gain range. An overrange and

underrange of 1 dB is provided whatever the selected range. The

gain control response time is less than 1 µs for a 40 dB change.

The differential gain control interface allows the use of either

differential or single-ended positive or negative control voltages.

Several of these amplifiers may be cascaded and their gain

control gains offset to optimize the system S/N ratio.

The AD603 can drive a load impedance as low as 100 Ω with

low distortion. For a 500 Ω load in shunt with 5 pF, the total

harmonic distortion for a ±1 V sinusoidal output at 10 MHz is

typically −60 dBc. The peak specified output is ±2.5 V

minimum into a 500 Ω load.

The AD603 uses a patented proprietary circuit topology—the

X-AMP®. The X-AMP comprises a variable attenuator of 0 dB

to −42.14 dB followed by a fixed-gain amplifier. Because of the

attenuator, the amplifier never has to cope with large inputs and

can use negative feedback to define its (fixed) gain and dynamic

performance. The attenuator has an input resistance of 100 Ω,

laser trimmed to ±3%, and comprises a seven-stage R-2R ladder

network, resulting in an attenuation between tap points of

6.021 dB. A proprietary interpolation technique provides a

continuous gain control function which is linear in dB.

The AD603 is specified for operation from −40°C to +85°C.

8

VPOS

6

VNEG

1

GPOS

2

GNEG

3

VINP

4

COMM

Rev. G

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

SCALING

REFERENCE

V

G

GAIN-

CONTROL

INTERFACE

0dB –6.02dB –12.04dB –18.06dB –24.08dB –30.1dB –36.12dB –42.14dB

RR R R R R R

2R 2R 2R 2R 2R 2R R

R-2R LADDER NETWORK

PRECISION PASSIVE

INPUT ATTENUATOR

AD603

Figure 1.

FIXED-GAIN

AMPLIFIER

7

V

OUT

1

6.44kΩ

5

FDBK

1

694Ω

1

20Ω

1

NOMINAL VALUES.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

www.analog.com

00539-001

AD603

TABLE OF CONTENTS

Specifications..................................................................................... 3

Using the AD603 in Cascade ........................................................ 14

Absolute Maximum Ratings............................................................ 4

ESD Caution.................................................................................. 4

Pin Configuration and Function Descriptions............................. 5

Typical Performance Characteristics .............................................6

Theory of Operation ......................................................................11

Noise Performance .....................................................................11

The Gain Control Interface....................................................... 12

Programming the Fixed-Gain Amplifier

Using Pin Strapping

................................................................... 12

REVISION HISTORY

3/05—Rev. F to Rev. G

Updated Format.................................................................. Universal

Change to Features............................................................................1

Changes to General Description .....................................................1

Change to Figure 1 ............................................................................1

Changes to Specifications.................................................................3

New Figure 4 and Renumbering Subsequent Figures...................6

Change to Figure 10 ..........................................................................7

Change to Figure 23 ..........................................................................9

Change to Figure 29 ........................................................................12

Updated Outline Dimensions........................................................20

Sequential Mode (Optimal S/N Ratio).................................... 14

Parallel Mode (Simplest Gain Control Interface) .................. 16

Low Gain Ripple Mode (Minimum Gain Error) ................... 16

Applications..................................................................................... 18

A Low Noise AGC Amplifier.................................................... 18

Caution ........................................................................................19

Outline Dimensions....................................................................... 20

Ordering Guide .......................................................................... 20

4/04—Rev. E to Rev. F

Changes to Specifications.................................................................2

Changes to Ordering Guide.............................................................3

8/03—Rev. D to Rev E

Updated Format.................................................................. Universal

Changes to Specifications.................................................................2

Changes to TPCs 2, 3, 4.....................................................................4

Changes to Sequential Mode (Optimal S/N Ratio) section.........9

Change to Figure 8 ..........................................................................10

Updated Outline Dimensions........................................................14

Rev. G | Page 2 of 20

AD603

SPECIFICATIONS

@ TA = 25°C, VS = ±5 V, –500 mV ≤ VG ≤ +500 mV, GNEG = 0 V, –10 dB to +30 dB gain range, RL = 500 Ω, and CL = 5 pF, unless otherwise

noted.

Table 1.

Parameter Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Input Resistance Pin 3 to Pin 4 97 100 103 Ω

Input Capacitance 2 pF

Input Noise Spectral Density

Noise Figure f = 10 MHz, gain = max, RS = 10 Ω 8.8 dB

1 dB Compression Point f = 10 MHz, gain = max, RS = 10 Ω −11 dBm

Peak Input Voltage ±1.4 ±2 V

OUTPUT CHARACTERISTICS

−3 dB Bandwidth V

Slew Rate RL ≥ 500 Ω 275 V/µs

Peak Output

2

Output Impedance f ≤ 10 MHz 2 Ω

Output Short-Circuit Current 50 mA

Group Delay Change vs. Gain f = 3 MHz; full gain range ±2 ns

Group Delay Change vs. Frequency VG = 0 V; f = 1 MHz to 10 MHz ±2 ns

Differential Gain 0.2 %

Differential Phase 0.2 Degree

Total Harmonic Distortion f = 10 MHz, V

Third Order Intercept f = 40 MHz, gain = max, RS = 50 Ω 15 dBm

ACCURACY

Gain Accuracy, f = 100 kHz; Gain (dB) = (40 VG + 10) dB −500 mV ≤ VG ≤ +500 mV, −1 ±0.5 +1 dB

T

to T

MIN

MAX

Gain, f = 10.7 MHz VG = -0.5 V −10.3 −9.0 −8.0 dB

V

V

Output Offset Voltage

T

to T

MIN

MAX

Output Offset Variation vs. V

T

to T

MIN

MAX

GAIN CONTROL INTERFACE

Gain Scaling Factor 100 kHz 39.4 40 40.6 dB/V

T

to T

MIN

MAX

10.7 MHz 38.7 39.3 39.9 dB/V

GNEG, GPOS Voltage Range

Input Bias Current 200 nA

Input Offset Current 10 nA

Differential Input Resistance Pin 1 to Pin 2 50 MΩ

Response Rate Full 40 dB gain change 80 dB/µs

POWER SUPPLY

Specified Operating Range ±4.75 ±6.3 V

Quiescent Current 12.5 17 mA

T

to T

MIN

1

Typical open or short-circuited input; noise is lower when system is set to maximum gain and input is short-circuited. This figure includes the effects of both voltage

and current noise sources.

2

Using resistive loads of 500 Ω or greater, or with the addition of a 1 kΩ pull-down resistor when driving lower loads.

3

The dc gain of the main amplifier in the AD603 is ×35.7; thus, an input offset of 100 µV becomes a 3.57 mV output offset.

4

GNEG and GPOS, gain control, and voltage range are guaranteed to be within the range of −VS + 4.2 V to +VS − 3.4 V over the full temperature range of −40°C to +85°C.

MAX

1

Input short-circuited 1.3 nV/√Hz

= 100 mV rms 90 MHz

OUT

RL ≥ 500 Ω ±2.5 ±3.0 V

= 1 V rms −60 dBc

OUT

−1.5 +1.5 dB

= 0.0 V +9.5 +10.5 +11.5 dB

G

= 0.5 V +29.3 +30.3 +31.3 dB

3

G

VG = 0 V −20 +20 mV

−30 +30 mV

G

−500 mV ≤ VG ≤ +500 mV −20 +20 mV

−30 +30 mV

38 42 dB/V

4

−1.2 +2.0 V

20 mA

Rev. G | Page 3 of 20

AD603

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage ±V

S

±7.5 V

Internal Voltage VINP (Pin 3) ±2 V Continuous

±VS for 10 ms

GPOS, GNEG (Pins 1, 2) ±V

Internal Power Dissipation

1

S

400 mW

Operating Temperature Range

AD603A −40°C to +85°C

AD603S −55°C to +125°C

Storage Temperature Range −65°C to +150°C

Lead Temperature Range (Soldering 60 sec) 300°C

1

Thermal Characteristics:

8-Lead SOIC Package: θ

8-Lead CERDIP Package: θ

= 155°C/W, θJC = 33°C/W,

JA

= 140°C/W, θJC = 15°C/W.

JA

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Rev. G | Page 4 of 20

AD603

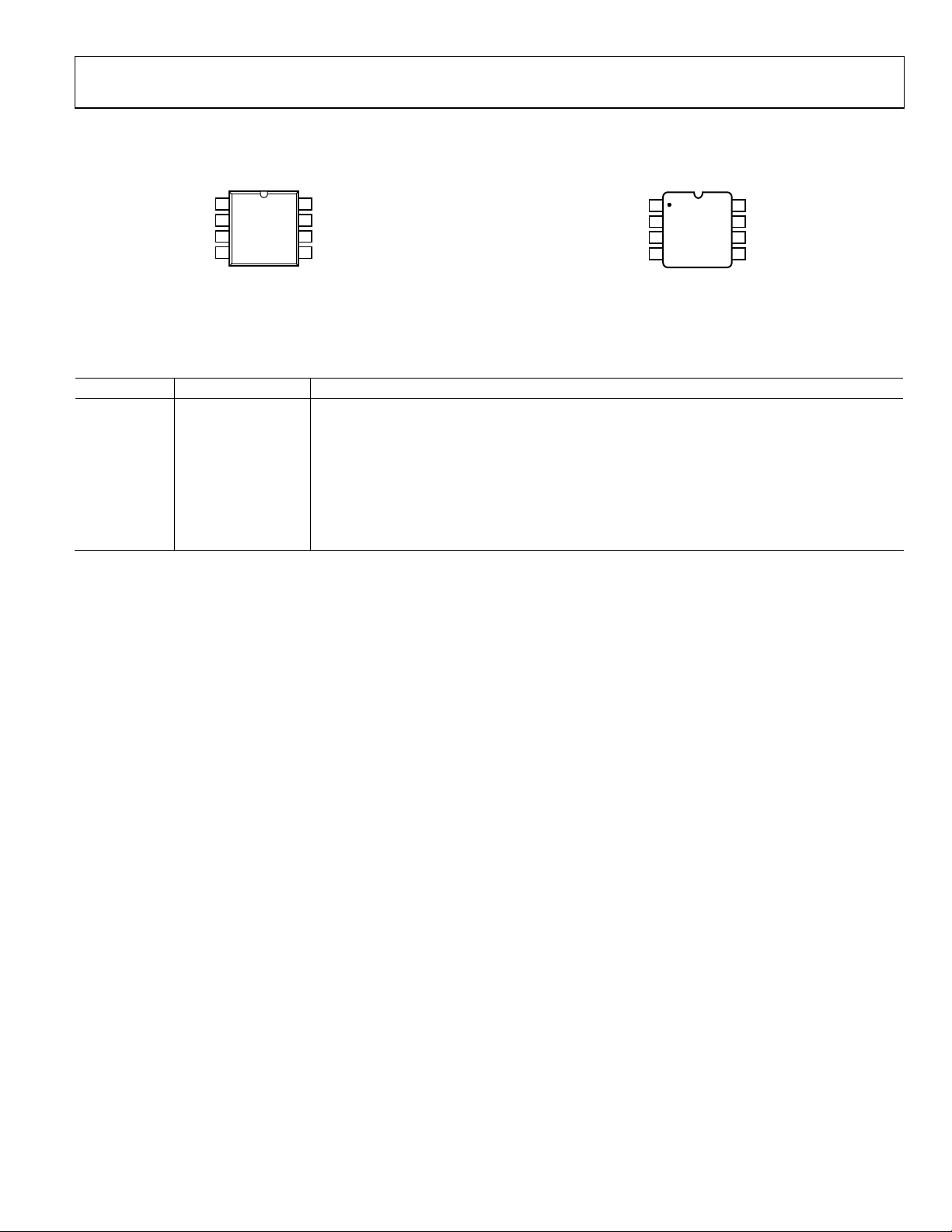

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

GPOS

GNEG

VINP

COMM

1

AD603

2

3

TOP VIEW

(Not to Scale)

4

8

7

6

5

VPOS

VOUT

VNEG

FDBK

00539-002

Figure 2. 8-Lead Plastic SOIC (R) Package

1

GPOS

GNEG

VINP

COMM

AD603

2

TOP VIEW

3

(Not to Scale)

4

Figure 3. 8-Lead Ceramic CERDIP (Q) Package

8

7

6

5

VPOS

VOUT

VNEG

FDBK

00539-003

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1 GPOS Gain Control Input High (Positive Voltage Increases Gain).

2 GNEG Gain Control Input Low (Negative Voltage Increases Gain).

3 VINP Amplifier Input.

4 COMM Amplifier Ground.

5 FDBK Connection to Feedback Network.

6 VNEG Negative Supply Input.

7 VOUT Amplifier Output.

8 VPOS Positive Supply Input.

Rev. G | Page 5 of 20

AD603

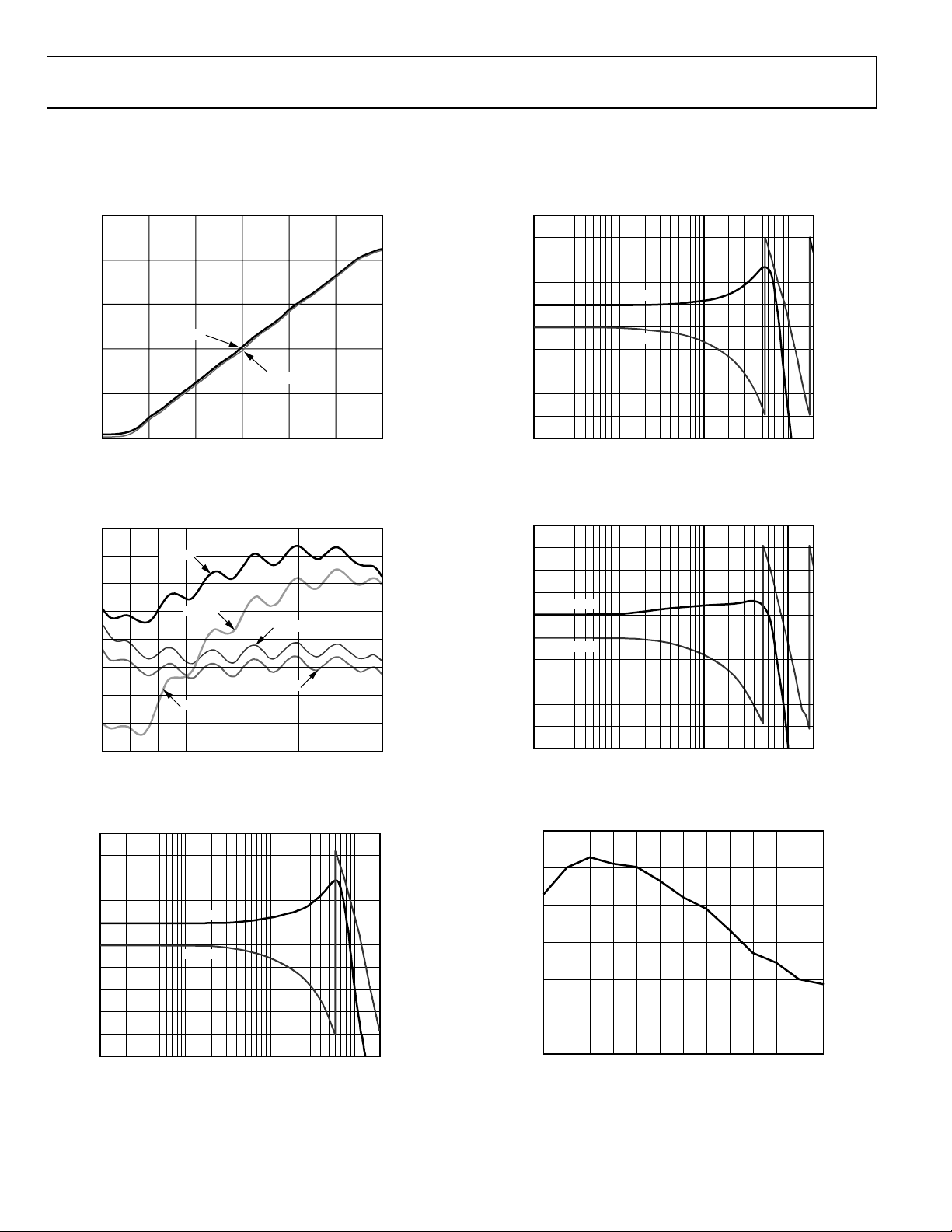

TYPICAL PERFORMANCE CHARACTERISTICS

@ TA = 25°C, VS = ±5 V, –500 mV ≤ VG ≤ +500 mV, GNEG = 0 V, –10 dB to +30 dB gain range, RL = 500 Ω, and CL = 5 pF, unless otherwise

noted.

40

30

20

10

GAIN (dB)

0

–10

10.7MHz

Figure 4. Gain vs. V

100kHz

VG (V)

at 100 kHz and 10.7 mHz

G

2.5

2.0

1.5

1.0

0.5

0

GAIN ERROR (dB)

–0.5

–1.0

–1.5

45MHz

70MHz

10.7MHz

455kHz

70MHz

GAIN VOLTAGE (Volts)

Figure 5. Gain Error vs. Gain Control Voltage at 455 kHz,

10.7 MHz, 45 MHz, 70 MHz

4

3

2

1

0

–1

–2

GAIN (dB)

–3

–4

–5

–6

100k 1M 10M 100M

GAIN

PHASE

FREQUENCY (Hz)

Figure 6. Frequency and Phase Response vs. Gain

(Gain = −10 dB, P

= −30 dBm)

IN

0.6–0.6 –0.4 –0.2 0 0.2 0.4

0.5–0.5 –0.4 –0.3 –0.2 –0.1 0 0.1 0.2 0.3 0.4

225

180

135

90

45

0

–45

–90

–135

–180

–225

00539-004

00539-005

PHASE (Degrees)

00539-006

4

3

2

1

0

–1

–2

GAIN (dB)

–3

–4

–5

–6

100k 1M 10M 100M

GAIN

PHASE

FREQUENCY (Hz)

Figure 7. Frequency and Phase Response vs. Gain

(Gain = +10 dB, P

4

3

2

1

GAIN

0

–1

PHASE

–2

GAIN (dB)

–3

–4

–5

–6

100k 1M 10M 100M

FREQUENCY (Hz)

= −30 dBm)

IN

Figure 8. Frequency and Phase Response vs. Gain

(Gain = +30 dB, P

7.60

7.40

7.20

7.00

6.80

GROUP DELAY (ns)

6.60

6.40

GAIN CONTROL VOLTAGE (V)

= −30 dBm)

IN

Figure 9. Group Delay vs. Gain Control Voltage

225

180

135

90

45

0

–45

–90

–135

–180

–225

225

180

135

90

45

0

–45

–90

–135

–180

–225

0.6–0.6 –0.4 –0.2 0 0.2 0.4

PHASE (Degrees)

PHASE (Degrees)

00539-009

00539-007

00539-008

Rev. G | Page 6 of 20

AD603

0.1µF

+5V

HP3326A

DUAL-

CHANNEL

SYNTHESIZER

100Ω

0.1µF

8

3

AD603

4

6

–5V

1

DATEL

DVC 8500

5

2

10×

7

PROBE

511Ω

Figure 10. Third Order Intermodulation Distortion Test Setup

HP3585A

SPECTRUM

ANALYZER

00539-010

–1.0

–1.2

–1.4

–1.6

–1.8

–2.0

–2.2

–2.4

–2.6

–2.8

–3.0

NEGATIVE OUTPUT VOLTAGE (V)

–3.2

–3.4

0 50 100 200 500 1000 2000

LOAD RESISTANCE (Ω)

Figure 13. Typical Output Voltage Swing vs. Load Resistance

(Negative Output Swing Limits First)

00539-013

10dB/DIV

Figure 11. Third Order Intermodulation Distor tion at 455 kHz

(10× Probe Used to HP3585A Spectrum Analyzer, Gain = 0 dB, P

10dB/DIV

00539-011

= 0 dBm)

IN

102

100

98

96

INPUT IMPEDANCE (Ω)

94

FREQUENCY (Hz)

Figure 14. Input Impedance vs. Frequency (Gain = −10 dB)

102

100

98

96

INPUT IMPEDANCE (Ω)

100M100k 1M 10M

00539-014

Figure 12. Third Order Intermodulation Distortion at 10.7 MHz

(10× Probe Used to HP3585A Spectrum Analyzer, Gain = 0 dB, P

00539-012

= 0 dBm)

IN

Rev. G | Page 7 of 20

94

FREQUENCY (Hz)

Figure 15. Input Impedance vs. Frequency (Gain = +10 dB)

100M100k 1M 10M

00539-015

AD603

102

3V

100

98

96

INPUT IMPEDANCE (Ω)

94

FREQUENCY (Hz)

Figure 16. Input Impedance vs. Frequency (Gain = +30 dB)

1V

100

90

10

0%

INPUT GND

100MV/DIV

1V

OUTPUT GND

1V/DIV

100M100k 1M 10M

00539-016

–2V

451ns–49ns 50ns

00539-019

Figure 19. Output Stage Overload Recovery Time

(Input Is 500 ns Period, 50% Duty Cycle Square Wave, Output is Captured

Using Tektronix 11402 Digitizing Oscilloscope)

3.5V

INPUT

500mV/DIV

GND

500mV

OUTPUT

500mV/DIV

GND

1V

200ns

00539-017

Figure 17. Gain Control Channel Response Time

4.5V

INPUT GND

1V/DIV

500mV

OUTPUT GND

500mV/DIV

–500mV

451ns–49ns 50ns

Figure 18. Input Stage Overload Recovery Time

(Input is 500 ns Period, 50% Duty Cycle Square Wave, Output is Captured

Using Tektronix 11402 Digitizing Oscilloscope)

00539-018

–1.5V

456ns–44ns 50ns

Figure 20. Transient Response, G = 0 dB

(Input is 500 ns Period, 50% Duty Cycle Square Wave, Output is Captured

Using Tektronix 11402 Digitizing Oscilloscope)

3.5V

INPUT GND

100mV/DIV

500mV

OUTPUT GND

500mV/DIV

–1.5V

456ns–44ns 50ns

00539-021

Figure 21. Transient Response, G = +20 dB

(Input is 500 ns Period, 50% Duty Cycle Square Wave, Output is Captured

Using Tektronix 11402 Digitizing Oscilloscope)

00539-020

Rev. G | Page 8 of 20

AD603

–10

–20

–30

–40

–50

PSRR (dB)

–60

21

0

NOISE FIGURE (dB)

19

17

15

13

11

9

7

10MHz

20MHz

TA = 25°C

= 50

Ω

R

S

TEST SETUP FIGURE 23

FREQUENCY (Hz)

100M100k 1M 10M

Figure 22. PSRR v s. Frequency

(Worst Case is Negative Supply PSRR, Shown Here)

µ

F

0.1

+5V

HP3326A

DUAL-

CHANNEL

SYNTHESIZER

100

0.1

8

3

AD603

Ω

4

µ

F

–5V

6

DATEL

DVC 8500

5

7

2

1

HP3585A

Ω

50

SPECTRUM

ANALYZER

Figure 23. Test Setup Used for: Noise Figure, Third Order Intercept and

1 dB Compression Point Measurements

NOISE FIGURE (dB)

23

21

19

17

15

13

11

9

7

5

70MHz

30MHz

GAIN (dB)

TA = 25°C

R

= 50V

S

TEST SETUP FIGURE 23

50MHz

10MHz

3020 21 22 23 24 25 26 27 28 29

Figure 24. Noise Figure in −10 dB/+30 dB Mode

00539-022

00539-023

00539-024

5

GAIN (dB)

4030 31 32 33 34 35 36 37 38 39

00539-025

Figure 25. Noise Figure in 0 dB/40 dB Mode

0

–5

–10

–15

INPUT LEVEL (dBm)

–20

–25

INPUT FREQUENCY (MHz)

TA = 25°C

TEST SETUP FIGURE 23

7010 30 50

00539-026

Figure 26. 1 dB Compression Point, −10 dB/+30 dB Mode, Gain = +30 dB

20

18

16

14

12

OUTPUT LEVEL (dBm)

10

0

30MHz

40MHz

70MHz

INPUT LEVEL (dBm)

TA = 25°C

TEST SETUP FIGURE 23

0–20 –10

00539-027

Figure 27. Third Order Intercept −10 dB/+30 dB Mode, Gain = +10 dB

Rev. G | Page 9 of 20

AD603

20

18

16

14

12

OUTPUT LEVEL (dBm)

10

40MHz

70MHz

30MHz

TA = 25°C

= 50

Ω

R

S

RIN = 50

Ω

RL = 100

Ω

TEST SETUP FIGURE 23

8

INPUT LEVEL (dBm)

Figure 28. Third Order Intercept −10 dB/+30 dB Mode, Gain = +30 dB

–20–40 –30

00539-028

Rev. G | Page 10 of 20

AD603

THEORY OF OPERATION

The AD603 comprises a fixed-gain amplifier, preceded by a

broadband passive attenuator of 0 dB to 42.14 dB, having a gain

control scaling factor of 40 dB per volt. The fixed gain is lasertrimmed in two ranges, to either 31.07 dB (×35.8) or 50 dB

(×358), or may be set to any range in between using one

external resistor between Pin 5 and Pin 7. Somewhat higher

gain can be obtained by connecting the resistor from Pin 5 to

common, but the increase in output offset voltage limits the

maximum gain to about 60 dB. For any given range, the

bandwidth is independent of the voltage-controlled gain. This

system provides an underrange and overrange of 1.07 dB in all

cases; for example, the overall gain is −11.07 dB to +31.07 dB in

the maximum bandwidth mode (Pin 5 and Pin 7 strapped).

This X-AMP structure has many advantages over former

methods of gain control based on nonlinear elements. Most

importantly, the fixed-gain amplifier can use negative feedback

to increase its accuracy. Since large inputs are first attenuated,

the amplifier input is always small. For example, to deliver a

±1 V output in the −1 dB/+41 dB mode (that is, using a fixed

amplifier gain of 41.07 dB) its input is only 8.84 mV; thus the

distortion can be very low. Equally important, the small-signal

gain and phase response, and thus the pulse response, are

essentially independent of gain.

Figure 29 is a simplified schematic. The input attenuator is a

seven-section R-2R ladder network, using untrimmed resistors

of nominally R = 62.5 Ω, which results in a characteristic

resistance of 125 Ω ±20%. A shunt resistor is included at the

input and laser trimmed to establish a more exact input

resistance of 100 Ω ±3%, which ensures accurate operation

(gain and HP corner frequency) when used in conjunction with

external resistors or capacitors.

The nominal maximum signal at input VINP is 1 V rms (±1.4 V

peak) when using the recommended ±5 V supplies, although

operation to ±2 V peak is permissible with some increase in HF

distortion and feedthrough. Pin 4 (COMM) must be connected

directly to the input ground; significant impedance in this

connection will reduce the gain accuracy.

The signal applied at the input of the ladder network is

attenuated by 6.02 dB by each section; thus, the attenuation to

each of the taps is progressively 0 dB, 6.02 dB, 12.04 dB,

18.06 dB, 24.08 dB, 30.1 dB, 36.12 dB, and 42.14 dB. A unique

circuit technique is employed to interpolate between these tap

points, indicated by the slider in Figure 29, thus providing

continuous attenuation from 0 dB to 42.14 dB. It will help in

understanding the AD603 to think in terms of a mechanical

means for moving this slider from left to right; in fact, its

position is controlled by the voltage between Pin 1 and Pin 2.

The details of the gain control interface are discussed later.

The gain is at all times very exactly determined, and a linear-indB relationship is automatically guaranteed by the exponential

nature of the attenuation in the ladder network (the X-AMP

principle). In practice, the gain deviates slightly from the ideal

law, by about ±0.2 dB peak (see, for example, Figure 5).

NOISE PERFORMANCE

An important advantage of the X-AMP is its superior noise

performance. The nominal resistance seen at inner tap points is

41.7 Ω (one third of 125 Ω), which exhibits a Johnson noise

spectral density (NSD) of 0.83 nV/√Hz (that is, √4kTR) at 27°C,

which is a large fraction of the total input noise. The first stage

of the amplifier contributes a further 1 nV/√Hz, for a total input

noise of 1.3 nV/√Hz. It will be apparent that it is essential to use

a low resistance in the ladder network to achieve the very low

specified noise level. The signal’s source impedance forms a

voltage divider with the AD603’s 100 Ω input resistance. In

some applications, the resulting attenuation may be

unacceptable, requiring the use of an external buffer or

preamplifier to match a high impedance source to the low

impedance AD603.

The noise at maximum gain (that is, at the 0 dB tap) depends on

whether the input is short-circuited or open-circuited: when

shorted, the minimum NSD of slightly over 1 nV/√Hz is

achieved; when open, the resistance of 100 Ω looking into the

first tap generates 1.29 nV/√Hz, so the noise increases to a total

of 1.63 nV/√Hz. (This last calculation would be important if the

AD603 were preceded by, for example, a 900 Ω resistor to allow

operation from inputs up to 10 V rms.) As the selected tap

moves away from the input, the dependence of the noise on

source impedance quickly diminishes.

Apart from the small variations just discussed, the signal-tonoise (S/N) ratio at the output is essentially independent of the

attenuator setting. For example, on the −11 dB/+31 dB range,

the fixed gain of ×35.8 raises the output NSD to 46.5 nV/√Hz.

Thus, for the maximum undistorted output of 1 V rms and a

1 MHz bandwidth, the output S/N ratio would be 86.6 dB, that

is, 20 log (1 V/46.5 µV).

Rev. G | Page 11 of 20

AD603

C

VPOS

VNEG

GPOS

GNEG

VINP

OMM

8

6

1

2

3

4

SCALING

REFERENCE

V

G

GAIN-

CONTROL

INTERFACE

0dB –6.02dB –12.04dB –18.06dB –24.08dB –30.1dB –36.12dB –42.14dB

RRRRRRR

2R 2R 2R 2R 2R 2R R

R-2R LADDER NETWORK

PRECISION PASSIVE

INPUT ATTENUATOR

AD603

Figure 29. Simplified Block Diagram

FIXED-GAIN

AMPLIFIER

6.44kΩ

694Ω

20Ω

1

NOMINAL VALUES.

7

V

OUT

1

5

FDBK

1

1

00539-029

THE GAIN CONTROL INTERFACE

The attenuation is controlled through a differential, high

impedance (50 MΩ) input, with a scaling factor which is lasertrimmed to 40 dB per volt, that is, 25 mV/dB. An internal band

gap reference ensures stability of the scaling with respect to

supply and temperature variations.

When the differential input voltage V

slider is centered, providing an attenuation of 21.07 dB. For the

maximum bandwidth range, this results in an overall gain of

10 dB (= −21.07 dB + 31.07 dB). When the control input is

−500 mV, the gain is lowered by 20 dB (= 0.500 V × 40 dB/V) to

−10 dB; when set to +500 mV, the gain is increased by 20 dB to

30 dB. When this interface is overdriven in either direction, the

gain approaches either −11.07 dB (= − 42.14 dB + 31.07 dB) or

31.07 dB (= 0 + 31.07 dB), respectively. The only constraint on

the gain control voltage is that it be kept within the commonmode range (−1.2 V to +2.0 V assuming +5 V supplies) of the

gain control interface.

The basic gain of the AD603 can thus be calculated using the

following simple expression:

Gain (dB) = 40 V

where V

is in volts. When Pin 5 and Pin 7 are strapped (see

G

+10 (1)

G

next section), the gain becomes

Gain (dB) = 40 V

+ 20 for 0 to +40 dB

G

= 0 V, the attenuator

G

For example, if the gain is to be controlled by a DAC providing

a positive only ground-referenced output, the Gain Control Low

(GNEG) pin should be biased to a fixed offset of 500 mV to set

the gain to −10 dB when Gain Control High (GPOS) is at zero,

and to 30 dB when at 1.00 V.

It is a simple matter to include a voltage divider to achieve other

scaling factors. When using an 8-bit DAC having an FS output

of 2.55 V (10 mV/bit), a divider ratio of 2 (generating 5 mV/bit)

would result in a gain-setting resolution of 0.2 dB/bit. The use

of such offsets is valuable when two AD603s are cascaded, when

various options exist for optimizing the S/N profile, as will be

shown later.

PROGRAMMING THE FIXED-GAIN AMPLIFIER USING PIN STRAPPING

Access to the feedback network is provided at Pin 5 (FDBK).

The user may program the gain of the AD603’s output amplifier

using this pin, as shown in Figure 30, Figure 31, and Figure 32.

There are three modes: in the default mode, FDBK is

unconnected, providing the range +9 dB/+51 dB; when V

and FDBK are shorted, the gain is lowered to −11 dB/+31 dB;

and when an external resistor is placed between V

OUT

any intermediate gain can be achieved, for example, −1 dB/+41

dB. Figure 33 shows the nominal maximum gain vs. external

resistor for this mode.

OUT

and FDBK

and

VC1

1

GPOS

VPOS

8

VPOS

AD603

Gain (dB) = 40 V

The high impedance gain control input ensures minimal

+ 30 for +10 to +50 dB (2)

G

VIN

VC2

2

3

GNEG

VINP

VOUT

VNEG

7

6

VNEG

VOUT

loading when driving many amplifiers in multiple channel or

4

cascaded applications. The differential capability provides

COMM

flexibility in choosing the appropriate signal levels and

polarities for various control schemes.

Rev. G | Page 12 of 20

Figure 30. −10 dB to +30 dB; 90 MHz Bandwidth

FDBK

5

00539-030

AD603

V

Optionally, when a resistor is placed from FDBK to COMM,

higher gains can be achieved. This fourth mode is of limited

value because of the low bandwidth and the elevated output

offsets; it is thus not included in Figure 30, Figure 31, or

Figure 32.

The gain of this amplifier in the first two modes is set by the

ratio of on-chip laser-trimmed resistors. While the ratio of these

resistors is very accurate, the absolute value of these resistors

can vary by as much as ±20%. Thus, when an external resistor is

connected in parallel with the nominal 6.44 kΩ ±20% internal

resistor, the overall gain accuracy is somewhat poorer. The

worst-case error occurs at about 2 kΩ (see Figure 34).

1.2

1.0

0.8

0.6

0.4

0.2

0

DECIBELS

–0.2

–0.4

–0.6

–0.8

–1.0

Figure 34. Worst-Case Gain Error, Assuming Internal Resistors have a

Maximum Tolerance of −20% (Top Curve) or =20% (Bottom Curve)

–1:VdB (OUT) – (–1):VdB (O

VdB (OUT) – VdB (O

R

(Ω)

EXT

REF

REF

)

)

1M10 100 1k 10k 100k

00539-034

While the gain bandwidth product of the fixed-gain amplifier is

about 4 GHz, the actual bandwidth is not exactly related to the

maximum gain. This is because there is a slight enhancing of

the ac response magnitude on the maximum bandwidth range,

due to higher order poles in the open-loop gain function; this

mild peaking is not present on the higher gain ranges. Figure 30,

Figure 31, and Figure 32 show how an optional capacitor may

be added to extend the frequency response in high gain modes.

IN

VIN

52

50

48

46

44

42

40

DECIBELS

38

36

34

32

30

Figure 33. Gain vs. R

VC1

1

GPOS

VPOS

8

VPOS

AD603

VC2

2

3

4

GNEG

VINP

COMM

VOUT

VNEG

FDBK

7

6

VNEG

2.15kΩ

5

5.6pF

Figure 31. 0 dB to 40 dB; 30 MHz Bandwidth

VC1

1

GPOS

VPOS

8

VPOS

AD603

VC2

2

3

4

GNEG

VINP

COMM

VOUT

VNEG

FDBK

7

6

VNEG

5

18pF

Figure 32. 10 dB to 50 db; 9 MHz to Set Gain

–1:VdB (OUT)

VdB (OUT)

–2:VdB (OUT)

R

(Ω)

EXT

Showing Worst-Case Limits Assuming Internal

EXT,

Resistors have a Maximum Tolerance of 20%

VOUT

VOUT

00539-031

00539-032

1M10 100 1k 10k 100k

00539-033

Rev. G | Page 13 of 20

AD603

USING THE AD603 IN CASCADE

Two or more AD603s can be connected in series to achieve

higher gain. Invariably, ac coupling must be used to prevent the

dc offset voltage at the output of each amplifier from

overloading the following amplifier at maximum gain. The

required high-pass coupling network will usually be just a

capacitor, chosen to set the desired corner frequency in

conjunction with the well-defined 100 Ω input resistance of the

following amplifier.

For two AD603s, the total gain control range becomes 84 dB

(2 × 42.14 dB); the overall −3 dB bandwidth of cascaded stages

will be somewhat reduced. Depending on the pin strapping, the

gain and bandwidth for two cascaded amplifiers can range from

−22 dB to +62 dB (with a bandwidth of about 70 MHz) to

+22 dB to +102 dB (with a bandwidth of about 6 MHz).

There are several ways of connecting the gain control inputs in

cascaded operation. The choice depends on whether it is

important to achieve the highest possible instantaneous signalto-noise ratio (ISNR), or, alternatively, to minimize the ripple in

the gain error. The following examples feature the AD603

programmed for maximum bandwidth; the explanations apply

to other gain/bandwidth combinations with appropriate

changes to the arrangements for setting the maximum gain.

SEQUENTIAL MODE (OPTIMAL S/N RATIO)

In the sequential mode of operation, the ISNR is maintained at

its highest level for as much of the gain control range as

possible. Figure 35 shows the SNR over a gain range of −22 dB

to +62 dB, assuming an output of 1 V rms and a 1 MHz

bandwidth; Figure 36, Figure 37, and Figure 38 show the general

connections to accomplish this. Here, both the positive gain

control inputs (GPOS) are driven in parallel by a positive-only,

ground-referenced source with a range of 0 V to +2 V, while the

negative gain control inputs (GNEG) are biased by stable

voltages to provide the needed gain offsets. These voltages may

A1

–40.00dB –51.07dB

be provided by resistive dividers operating from a common

voltage reference.

90

85

80

75

70

65

S/N RATIO (dB)

60

55

50

VC (V)

2.2–0.2 0.60.2 1.41.0 1.8

00539-035

Figure 35. SNR vs. Control Voltage–Sequential Control (1 MHz Bandwidth)

The gains are offset (Figure 39) such that A2’s gain is increased

only after A1’s gain has reached its maximum value. Note that

for a differential input of –600 mV or less, the gain of a single

amplifier (A1 or A2) will be at its minimum value of −11.07 dB;

for a differential input of +600 mV or more, the gain will be at

its maximum value of 31.07 dB. Control inputs beyond these

limits will not affect the gain and can be tolerated without

damage or foldover in the response. This is an important aspect

of the AD603’s gain control response. (See the Specifications

section for more details on the allowable voltage range.) The

gain is now

Gain (dB) = 40 V

where V

is the applied control voltage and GO is determined by

G

+ GO (3)

G

the gain range chosen. In the explanatory notes that follow, it is

assumed the maximum bandwidth connections are used, for

which G

is −20 dB.

O

A2

INPUT

0dB

V

C

= 0V

–42.14dB

GPOS GNEG

V

G1

VO1 = 0.473V VO2 = 1.526V

31.07dB

–8.93dB

–42.14dB

GPOS GNEG

V

G2

31.07dB

Figure 36. AD603 Gain Control Input Calculations for Sequential Control Operation V

0dB –11.07dB

INPUT

0dB

V

= 1.0V

C

0dB

GPOS GNEG

V

G1

VO1 = 0.473V VO2 = 1.526V

31.07dB

31.07dB

–42.14dB

GPOS GNEG

V

G2

31.07dB

Figure 37. AD603 Gain Control Calculations for Sequential Control Operation V

Rev. G | Page 14 of 20

OUTPUT

–20dB

C

OUTPUT

20dB

= 1.0 V

C

00539-036

= 0 V

00539-037

AD603

0dB –28.93dB

INPUT

0dB

= 2.0V

V

C

0dB

GPOS GNEG

V

G1

VO1 = 0.473V VO2 = 1.526V

31.07dB

Figure 38. AD603 Gain Control Input Calculations for Sequential Operation V

+31.07dB

+10dB

A1 A2

–8.93dB

0.473 1.526

GAIN

(dB)

0

–20

1

GAIN OFFSET OF 1.07dB, OR 26.75mV.

–11.07dB

0.5

0

1

+31.07dB +28.96dB

1

1.0

20

1.50

40

2.060VC(V)

–11.07dB

62.14–22.14

Figure 39. Explanation of Offset Calibration for Sequential Control

With reference to Figure 36, Figure 37, and Figure 38, note that

V

refers to the differential gain control input to A1, and VG2

G1

refers to the differential gain control input to A2. When V

V

= −473 mV and thus the gain of A1 is −8.93 dB (recall that

G1

is 0,

G

the gain of each individual amplifier in the maximum

bandwidth mode is –10 dB for V

= 0 V); meanwhile, V

= −1.908 V so the gain of A2 is pinned at

G2

= −500 mV and 10 dB for VG

G

−11.07 dB. The overall gain is thus –20 dB. See Figure 36.

When V

= +1.00 V, VG1 = 1.00 V − 0.473 V = +0.526 V, which

G

sets the gain of A1 to at nearly its maximum value of 31.07 dB,

while V

= 1.00 V − 1.526 V = 0.526 V, which sets A2’s gain at

G2

nearly its minimum value of −11.07 dB. Close analysis shows

that the degree to which neither AD603 is completely pushed to

its maximum nor minimum gain exactly cancels in the overall

gain, which is now +20 dB. See Figure 37.

When V

= 2.0 V, the gain of A1 is pinned at 31.07 dB and that

G

of A2 is near its maximum value of 28.93 dB, resulting in an

overall gain of 60 dB (see Figure 38). This mode of operation is

further clarified by Figure 40, which is a plot of the separate

gains of A1 and A2 and the overall gain vs. the control voltage.

Figure 41 is a plot of the SNR of the cascaded amplifiers vs. the

control voltage. Figure 42 is a plot of the gain error of the

cascaded stages vs. the control voltages.

31.07dB

00539-039

–2.14dB

GPOS GNEG

V

G2

31.07dB

OUTPUT

60dB

00539-038

= 2.0 V

C

70

OVERALL GAIN (dB)

–10

–20

–30

60

50

40

30

20

10

0

A1

COMBINED

V

C

A2

Figure 40. Plot of Separate and Overall Gains in Sequential Control

90

80

70

60

50

40

S/N RATIO (dB)

30

20

10

V

C

Figure 41. SNR for Cascaded Stages—Sequential Control

2.0–0.2 0.2 0.6 1.0 1.4 1.8

00539-040

2.0–0.2 0.2 0.6 1.0 1.4 1.8

00539-041

Rev. G | Page 15 of 20

AD603

2.0

90

1.5

1.0

0.5

0

–0.5

GAIN ERROR (dB)

–1.0

–1.5

–2.0

V

C

2.2–0.2 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

Figure 42. Gain Error for Cascaded Stages–Sequential Control

PARALLEL MODE (SIMPLEST GAIN CONTROL INTERFACE)

In this mode, the gain control of voltage is applied to both

inputs in parallel—the GPOS pins of both A1 and A2 are

connected to the control voltage and the GNEW inputs are

grounded. The gain scaling is then doubled to 80 dB/V,

requiring only a 1.00 V change for an 80 dB change of gain:

Gain = (dB) = 80 V

where, as before, G

in the maximum bandwidth mode, G

the GNEG pins may be connected to an offset voltage of

0.500 V, in which case G

The amplitude of the gain ripple in this case is also doubled, as

shown in Figure 43, while the instantaneous signal-to-noise

ratio at the output of A2 now decreases linearly as the gain

increases, as shown in Figure 44.

2.0

1.5

1.0

0.5

0

–0.5

GAIN ERROR (dB)

–1.0

+ GO (4)

G

depends on the range selected; for example,

O

is +20 dB. Alternatively,

O

is −20 dB.

O

00539-042

85

80

75

70

65

IS/N RATIO (dB)

60

55

50

V

C

1.2–0.2 0 0.2 0.4 0.6 0.8 1.0

00539-044

Figure 44. ISNR for Cascaded Stages—Parallel Control

LOW GAIN RIPPLE MODE (MINIMUM GAIN ERROR)

As can be seen in Figure 42 and Figure 43, the error in the gain

is periodic, that is, it shows a small ripple. (Note that there is

also a variation in the output offset voltage, which is due to the

gain interpolation, but this is not exact in amplitude.) By

offsetting the gains of A1 and A2 by half the period of the

ripple, that is, by 3 dB, the residual gain errors of the two

amplifiers can be made to cancel. Figure 45 shows much lower

gain ripple when configured in this manner. Figure 46 plots the

ISNR as a function of gain; it is very similar to that in the

parallel mode.

3.0

2.5

2.0

1.5

1.0

0.5

0

–0.5

–1.0

GAIN ERROR (dB)

–1.5

–2.0

–2.5

–3.0

V

C

Figure 45. Gain Error for Cascaded Stages—Low Ripple Mode

1.1–0.1 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

00539-045

–1.5

–2.0

V

C

Figure 43. Gain Error for Cascaded Stages—Parallel Control

2.2–0.2 0 0.2 0.4 0.6 1.0 1.20.8 1.6 1.8 2.01.4

00539-043

Rev. G | Page 16 of 20

AD603

90

85

80

75

70

65

IS/N RATIO (dB)

60

55

50

V

C

1.2–0.2 0 0.2 0.4 0.6 0.8 1.0

00539-046

Figure 46. ISNR vs. Control Voltage—Low Ripple Mode

Rev. G | Page 17 of 20

AD603

APPLICATIONS

A LOW NOISE AGC AMPLIFIER

Figure 47 shows the ease with which the AD603 can be

connected as an AGC amplifier. The circuit illustrates many of

the points previously discussed: It uses few parts, has linear-indB gain, operates from a single supply, uses two cascaded

amplifiers in sequential gain mode for maximum S/N ratio, and

an external resistor programs each amplifier’s gain. It also uses a

simple temperature-compensated detector.

The circuit operates from a single 10 V supply. Resistors R1, R2,

R3, and R4 bias the common pins of A1 and A2 at 5 V. This pin

is a low impedance point and must have a low impedance path

to ground, provided here by the 100 µF tantalum capacitors and

the 0.1 µF ceramic capacitors.

The cascaded amplifiers operate in sequential gain. Here, the

offset voltage between the Pin 2 (GNEG) of A1 and A2 is 1.05 V

(42.14 dB × 25 mV/dB), provided by a voltage divider

consisting of resistors R5, R6, and R7. Using standard values, the

offset is not exact, but it is not critical for this application.

The gain of both A1 and A2 is programmed by resistors R13

and R14, respectively, to be about 42 dB; thus the maximum

gain of the circuit is twice that, or 84 dB. The gain control range

can be shifted up by as much as 20 dB by appropriate choices of

R13 and R14.

The circuit operates as follows. A1 and A2 are cascaded.

Capacitor C1 and the 100 Ω of resistance at the input of A1

form a time constant of 10 µs. C2 blocks the small dc offset

voltage at the output of A1 (which might otherwise saturate A2

at its maximum gain) and introduces a high-pass corner at

about 16 kHz, eliminating low frequency noise.

A half-wave detector is used, based on Q1 and R8. The current

into capacitor C

is just the difference between the collector

AV

current of Q2 (biased to be 300 µA at 300 K, 27°C) and the

collector current of Q1, which increases with the amplitude of

the output signal.

The automatic gain control voltage, V

this error current. In order for V

AGC

, is the time integral of

AGC

(and thus the gain) to

remain insensitive to short-term amplitude fluctuations in the

output signal, the rectified current in Q1 must, on average,

exactly balance the current in Q2. If the output of A2 is too

small to do this, V

will increase, causing the gain to increase,

AGC

until Q1 conducts sufficiently.

Consider the case where R8 is zero and the output voltage V

OUT

is a square wave at, say, 455 kHz, which is well above the corner

frequency of the control loop.

10V

C7

0.1µF

C1

0.1µF

10V

R2

2.49kΩ

5.49kΩ

3

4

J1

2

C3

100µFC40.1µF

1

RT

100Ω

R1

2.49kΩ

+

1

RT PR OVIDES A 5 0Ω INPUT IMPEDANCE.

2

C3 AND C5 ARE TANTALUM.

10V

R13

8

A1

AD603

1

R5

2.49kΩ

6

5

7

2

C5

100µFC60.1µF

5.5V 6.5V

C2

0.1µF

2

+

1V OFFSET FOR

SEQUENTIAL GAIN

2.49kΩ

R6

1.05kΩ

R3

C8

0.1µF

10V

Figure 47. A Low Noise AGC Amplifier

R4

2.49kΩ

THIS CAPACITOR SETS

AGC TIME CONSTANT

10V

8

6

3

AD603

4

1

A2

5

2

R14

2.49kΩ

7

0.1µF

R7

3.48kΩ

V

AGC

C

AV

AGC LINE

10V

1.54kΩ

2N3906

2N3904

806Ω

Q2

Q1

R9

R8

R10

1.24kΩ

R11

3.83kΩ

5V

R12

4.99kΩ

C10

0.1µF

C11

0.1µF

C9

0.1µF

J2

00539-047

Rev. G | Page 18 of 20

AD603

During the time V

voltage of Q1, Q1 conducts; when V

Since the average collector current of Q1 is forced to be 300 µA,

and the square wave has a duty cycle of 1:1, Q1’s collector

current when conducting must be 600 µA. With R8 omitted, the

peak amplitude of V

600 µA, typically about 700 mV, or 2 V

voltage, the amplitude at which the output stabilizes, has a

strong negative temperature coefficient (TC), typically

−1.7 mV/°C. Although this may not be troublesome in some

applications, the correct value of R8 will render the output

stable with temperature.

To understand this, note that the current in Q2 is made to be

proportional to absolute temperature (PTAT). For the moment,

continue to assume that the signal is a square wave.

When Q1 is conducting, V

voltage that is PTAT and that can be chosen to have an equal

but opposite TC to that of the V

than an application of the band gap voltage reference principle.

When R8 is chosen such that the sum of the voltage across it

and the V

V

OUT

of Q1 is close to the band gap voltage of about 1.2 V,

BE

will be stable over a wide range of temperatures, provided,

of course, that Q1 and Q2 share the same thermal environment.

Since the average emitter current is 600 µA during each half

cycle of the square wave, a resistor of 833 Ω would add a PTAT

voltage of 500 mV at 300 K, increasing by 1.66 mV/°C. In

practice, the optimum value will depend on the type of

transistor used and, to a lesser extent, on the waveform for

which the temperature stability is to be optimized; for the

is negative with respect to the base

OUT

is positive, it is cut off.

OUT

is forced to be just the VBE of Q1 at

OUT

peak-to-peak. This

BE

is now the sum of VBE and a

OUT

. This is actually nothing more

BE

inexpensive 2N3904/2N3906 pair and sine wave signals, the

recommended value is 806 Ω.

This resistor also serves to lower the peak current in Q1 when

more typical signals (usually sinusoidal) are involved, and the

1.8 kHz LP filter it forms with C

due to ripple in V

. Note that the output amplitude under sine

AGC

helps to minimize distortion

AV

wave conditions will be higher than for a square wave, since the

average value of the current for an ideal rectifier would be 0.637

times as large, causing the output amplitude to be 1.88

(= 1.2/0.637) V, or 1.33 V rms. In practice, the somewhat

nonideal rectifier results in the sine wave output being regulated

to about 1.4 V rms, or 3.6 V p-p.

The bandwidth of the circuit exceeds 40 MHz. At 10.7 MHz, the

AGC threshold is 100 µV (−67 dBm) and its maximum gain is

83 dB (20 log 1.4 V/100 µV). The circuit holds its output at

1.4 V rms for inputs as low as −67 dBm to +15 dBm (82 dB),

where the input signal exceeds the AD603’s maximum input

rating. For a 30 dBm input at 10.7 MHz, the second harmonic is

34 dB down from the fundamental and the third harmonic is

35 dB down.

CAUTION

Careful component selection, circuit layout, power supply

decoupling, and shielding are needed to minimize the AD603’s

susceptibility to interference from signals such as those from

radio and TV stations. In bench evaluation, it is recommended

to place all of the components into a shielded box and using

feedthrough decoupling networks for the supply voltage. Circuit

layout and construction are also critical, since stray capacitances

and lead inductances can form resonant circuits and are a

potential source of circuit peaking, oscillation, or both.

Rev. G | Page 19 of 20

AD603

OUTLINE DIMENSIONS

0.005 (0.13)

PIN 1

0.200 (5.08)

MAX

0.200 (5.08)

0.125 (3.18)

0.023 (0.58)

0.014 (0.36)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 48. 8-Lead Ceramic Dual In-Line Package [CERDIP]

Dimensions shown in inches and (millimeters)

ORDERING GUIDE

Part Number Temperature Range Package Description Package Option

AD603AR −40°C to +85°C 8-Lead SOIC R-8

AD603AR-REEL −40°C to +85°C 8-Lead SOIC, 13" Reel R-8

AD603AR-REEL7 −40°C to +85°C 8-Lead SOIC, 7" Reel R-8

AD603ARZ

AD603ARZ-REEL

AD603ARZ-REEL7

AD603AQ −40°C to +85°C 8-Lead CERDIP Q-8

AD603SQ/883B

AD603-EB Evaluation Board

AD603ACHIPS DIE

1

Z = Pb-free part.

2

Refer to AD603 Military data sheet. Also available as 5962-9457203MPA.

1

0.055 (1.40)

8

1

MAX

5

4

0.070 (1.78)

0.030 (0.76)

MIN

0.100 (2.54) BSC

0.405 (10.29) MAX

0.310 (7.87)

0.220 (5.59)

0.060 (1.52)

0.015 (0.38)

0.150 (3.81)

MIN

SEATING

PLANE

(Q-8)

0.320 (8.13)

0.290 (7.37)

15°

0°

0.015 (0.38)

0.008 (0.20)

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

85

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-AA

Figure 49. 8-Lead Standard Small Outline Package [SOIC-N]

BSC

6.20 (0.2440)

5.80 (0.2284)

41

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

−40°C to +85°C 8-Lead SOIC R-8

1

−40°C to +85°C 8-Lead SOIC, 13" Reel R-8

1

−40°C to +85°C 8-Lead SOIC, 7" Reel R-8

2

−55°C to +125°C 8-Lead CERDIP Q-8

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

8°

1.27 (0.0500)

0°

0.40 (0.0157)

× 45°

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

C00539–0–3/05(G)

Rev. G | Page 20 of 20

Loading...

Loading...