250 kSPS 12-Bit Impedance Converter,

Preliminary Technical Data

FEATURES

100 kHz max excitation output

Impedance range 0.1 kΩ to 10 MΩ, 12-bit resolution

DSP real and imaginary calculation (DFT)

3 V/5 V power supply

Programmable sinewave output

Frequency resolution 27 bits (<0.1 Hz)

Frequency sweep capability with serial I

12-Bit sampling ADC

ADC sampling 1 MSPS, INL ± 1 LSB max

On-chip temp sensor allows ±2 °C accuracy

Temperature range −40°C to +125°C

16 lead SSOP package

APPLICATIONS

Complex impedance measurement

Corrosion monitoring

Impedance spectrometry

Biomedical and automotive sensors

Proximity sensors

DFT processing

GENERAL DESCRIPTION

The AD5934 is a high precision impedance converter system

solution which combines an on board frequency generator with

a 12 Bit 1MSPS ADC. The frequency generator allows an

external complex impedance to be excited with a known

frequency. The response signal from the impedance is sampled

by the on board ADC and DFT processed by an on-board DSP

engine. The DFT algorithm returns a Real (R) and imaginary (I)

data word at each output frequency. This magnitude of these data

words must be further scaled by calibrated Gain Factor in order

to return the actual impedance value at each frequency point. The

magnitude of the impedance and relative phase of the

2

C loading

Network Analyzer

AD5934

impedance at each frequency point along the sweep is easily

calculated using the following equations:

122

−

)/(

=+=

To determine the value of the unknown impedance Z(w),

generally a frequency sweep is performed. The impedance can

be calculated at each point and an impedance profile i.e. frequency

vs. magnitude plot can be created. The system allows the user to

program a 2 V p-p sinusoidal signal as excitation to an external

load. Output voltage excitation ranges of 1 V, 400 mV, 200 mV

can also be programmed. The signal is provided on chip using

DDS techniques. Frequency resolution of 27 bits (less than

0.1 HZ) can be achieved using this method. To perform the

frequency sweep, the user must first program the conditions

required for the sweep; start frequency, step frequency, and

number of incremental points along the sweep into onboard

registers. Once the relevant registers have been programmed, a

Start Command to the control register is required in order to

begin the sweep. To determine the impedance of the load at any

one frequency point, Z(w), a measurement system comprised of

a transimpedance amplifier, gain stage, and ADC are used to

record data. The gain stage for the response stage is 1 or 5. At

each point on the sweep the ADC will take 1024 samples and

calculate a Discrete Fourier Transform to provide the real and

imaginary data for the response signal waveform. The real and

imaginary data stored in memory and is available to the user

through the 1

2

C interface. The ADC is a low noise; high speed

1 MSPS sampling ADC that operates from 3 V supply. Clocking

for both the DDS and ADC signals is provided externally via

the MCLK reference clock, which is provided externally from a

crystal oscillator or system clock. The AD5934 is available in a

16 lead SSOP.

RITanPhaseIRMagnitude

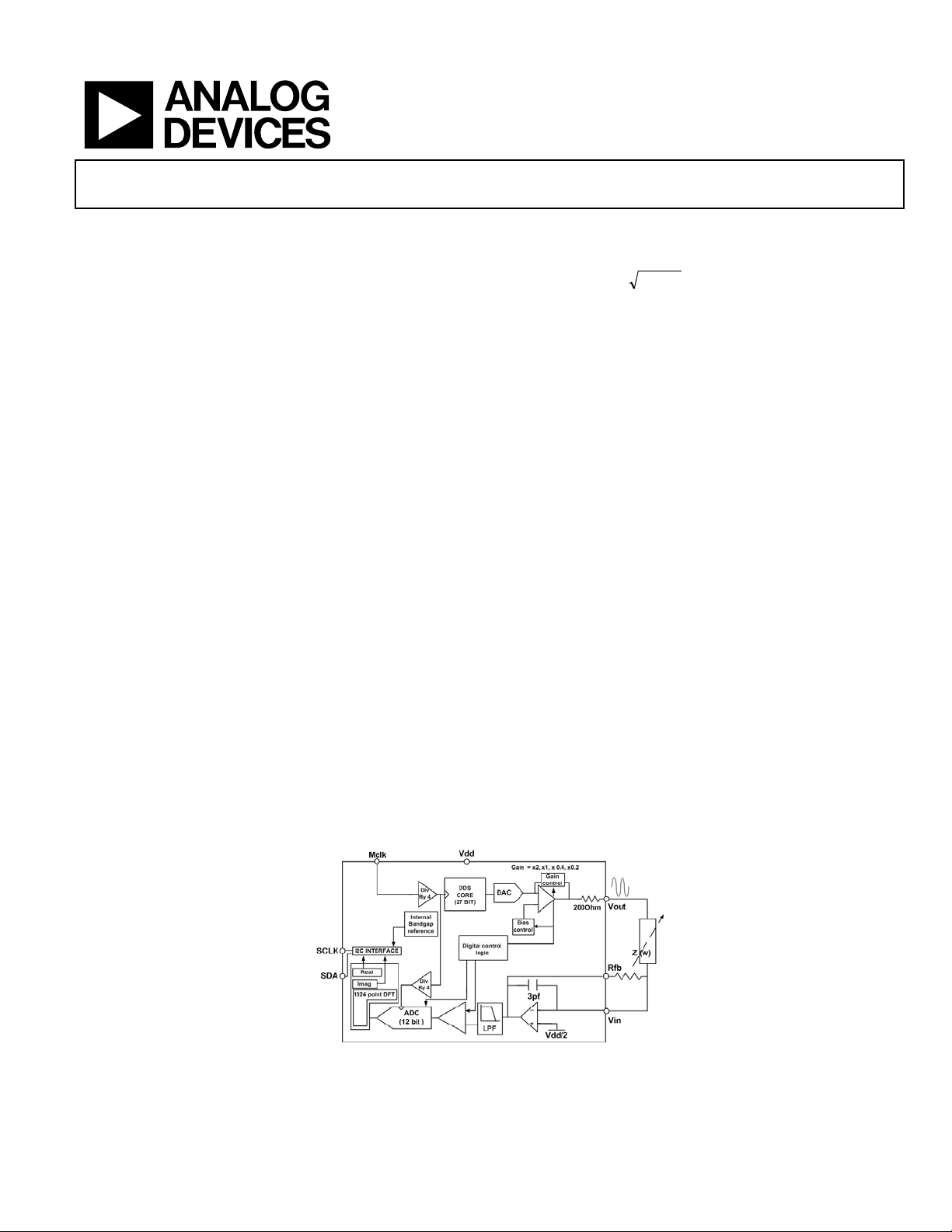

Figure 1. AD5934 Block Diagram

Rev. PrB

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.3113 © 2005 Analog Devices, Inc. All rights reserved.

AD5934 Preliminary Technical Data

TABLE OF CONTENTS

Specifications..................................................................................... 3

The Analog-to-Digital Converter ............................................ 24

Timing Characteristics..................................................................... 9

Absolute Maximum Ratings.......................................................... 10

ESD Caution................................................................................ 10

Pin Configuration and Descriptions............................................ 11

Typical Performance Characteristics........................................... 12

Terminology .................................................................................... 17

DAC/DDS core: ..........................................................................17

ADC: ............................................................................................ 18

System Architecture Description.................................................. 19

Output Stage................................................................................ 19

DDS Core: Circuit Description ................................................ 19

Numerical Controlled Oscillator.............................................. 20

SIN ROM..................................................................................... 20

Digital-to-Analog Converter & Output Gain Stage............... 20

Response Stage............................................................................ 20

The Discrete Fourier Transform .............................................. 24

AD5934 Discrete Fourier Transform Leakage ....................... 25

Gain Factor Calculation ............................................................ 27

AD5934 System Calibration ..................................................... 28

Performing a Frequency Sweep—Flow Chart............................ 31

Register Map (Each Row Equals 8 Bits of Data) ........................ 32

Control Register ......................................................................... 35

Control Register Decode........................................................... 36

Status Register:............................................................................ 36

Serial Bus Interface..................................................................... 38

General I

Writing/Reading to the AD5934.............................................. 39

Block Write.................................................................................. 41

AD5934 Read Operations ......................................................... 42

Error Correction......................................................................... 43

2

C Timing.................................................................... 38

ADC Operation ..........................................................................21

DFT Conversion......................................................................... 21

AD5934 Theory of Operation....................................................... 23

DDS Core..................................................................................... 23

Analog Channel and Filter Network........................................ 24

REVISION HISTORY

3/05—Revision PrB

Checksum.................................................................................... 43

User Command Codes .............................................................. 43

Writing to Memory: Storing Calibration Variables............... 44

Outline Dimensions....................................................................... 47

Ordering Guide .......................................................................... 47

Rev. PrB | Page 2 of 48

Preliminary Technical Data AD5934

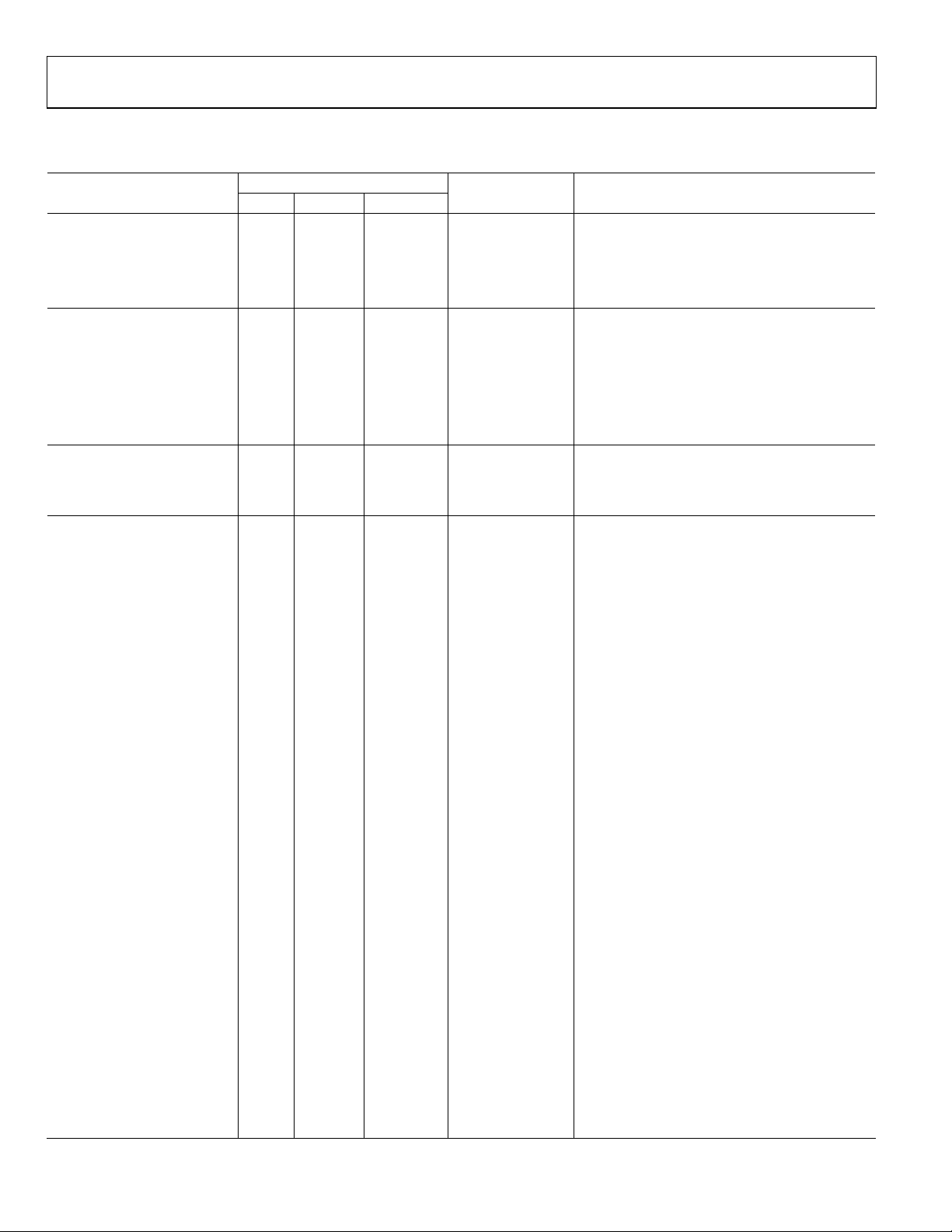

SPECIFICATIONS

VDD = +3.0 V ±10% T

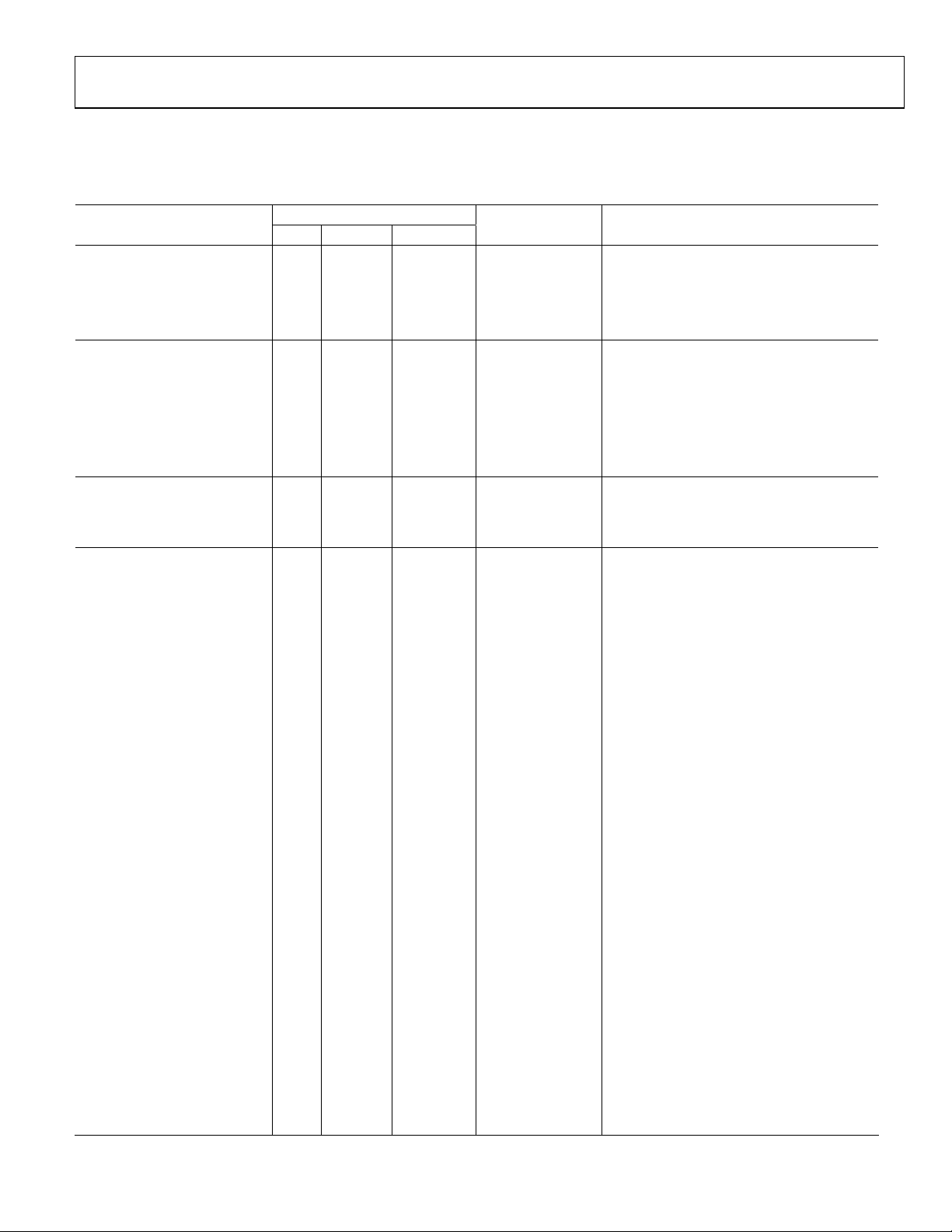

Table 1.

Y Version

Parameter Min Typ Max Unit Test Conditions/Comments

SYSTEM SPECS

Impedance Range 0.001 10 MΩ

Total System Accuracy 1 %

System ppm 250 ppm/°C Vdd = 3.3 V @ 25°C, 500 Hz bandwidth

MCLK Update Rate 16 MSPS System clock update rate

OUTPUT STAGE

FREQUENCY SPECS

Output Frequency Range 0 100 kHz Hz

Output Frequency Resoltuion 27 Bits

MCLK External Rerference Clock.

Initial Frequency Accuracy 0.1 Hz

OUTPUT VOLTAGE SPECS

AC Voltage Range (div by 1) 2.0 Volts peak to peak

Output Voltage Error 0.9 %

DC Bias (vdd/2 ) 1.65 Volts DC bias of AC Signal vdd = 3.3 V

DC Bias Error ±9 % Tolerance of DC Bias

AC Voltage Range div by 2 1.0 Volts peak to peak

Output Voltage Error 0.8 %

DC Bias (Vdd/4) 0.79 Volts DC bias of AC Signal vdd = 3.3 V

DC Bias Error ±10 % Tolerance of DC Bias

AC Voltage Range div by 5 0. 4 Volts peak to peak

Output Voltage Error 0.7 %

DC Bias (Vdd/10) 0.32 Volts DC bias of AC Signal vdd = 3.3 V

DC Bias Error ±9 % Tolerance of DC Bias

AC Voltage Range div by 10 0.2 Volts peak to peak

Output Voltage Error 0.4 %

DC Bias (Vdd/20) 0.16 Volts DC bias of AC Signal vdd = 3.3 V

DC Bias Error ±7 % Tolerance of DC Bias

DC Output Impedance

(at Vout)

DC Output Impedance 2.4 kΩ

DC Output Impedance 1 KΩ

DC Output Impedance 600 Ω

MIN

to T

unless otherwise noted.

MAX

1,2

400 Ω

Uni-Polar Sinusoidal Signal at Vout. System

accuracy only guarentted in this range.

>100 kHz achievable by device but accuracy

not guarenteed.

<0.1 Hz Resolution achievable using DDS

techniques

System Output Exitation Frequency

Accuracy using external clock/crystal post

triml. 0-100 kHz Range.

Pk-Pk Unipolar output excitation Voltage on

Vout. Vdd = 3.3 V

Voltage Error on Pk-Pk Output Excitation

voltage. Vdd = 3.3 V

Pk-Pk Unipolar output excitation Voltage on

VOut. Vdd = 3.3 V

Voltage Error on Pk-Pk Output excitation

voltage. Vdd = 3.3 V

Pk-Pk Unipolar output excitation Voltage on

Vout. Vdd = 3.3 V

Voltage Error on Pk-Pk Output excitation

voltage. Vdd = 3.3 V

Pk-Pk Unipolar output excitation Voltage on

VOut. Vdd = 3.3 V

Voltage Error on Pk-Pk Output excitation

voltage. Vdd = 3.3 V

2.0 Vp-p, Output frequency = 30 kHz

(external oscillator), vdd = 3.3 V, Ta = 25°C

1.0 Vp-p, Output frequency = 30 kHz

(external oscillator), vdd = 3.3 V, Ta = 25°C

400 mVp-p, Output frequency = 30 kHz,

(external oscillator) vdd = 3.3 V, Ta = 25°C

200 mVp-p, Output frequency = 30 kHz

(external oscillator), vdd = 3.3 V, Ta = 25°C

Rev. PrB | Page 3 of 48

AD5934 Preliminary Technical Data

Y Version

Parameter Min Typ Max Unit Test Conditions/Comments

Short Circuit Current (at Vout) ±7 mA

Short Circuit Current ±1 mA

Short Circuit Current ±2. 5 mA

Short Circuit Current ±4. .5 mA

AC CHARACTERISTICS

Signal to Noise Ratio 60 dB

Total Harmonic Distortion −52 dB

Spurious free Dynamic

Range (SFDR)

Wideband (0 to 1 MHz) 56 dB

Narrowband (± 5 kHz) 85 dB

Clock Feedthrough

(0 to 17 MHz)

SYSTEM RESPONSE STAGE

ANALOG INPUT VIN

Input Leakage Current 1 nA To Pin VIN

Input Capacitance 3.5 pF

Input Impedance 68.5G Ω

ADC ACCURACY

Resolution 12 bits

Sampling Rate 1 MSPS

Integral Nonlinearity ±1 LSB No missing Codes

Differential Nonlinearity ±1 LSB Guarentted monitonic

Offset Error ±3 LSB

Gain Error ±6 LSB

TEMPERATURE SENSOR

Accuracy ±1 °C Ta = −40 °C to 125 °C

Resolution 0.03125 °C

Auto Conversion Update Rate 1 sec Temperature measurement every 1 second

Temperature Conversion

Time

−60 dB

800 µs Vdd = 3.3 V

1,2

2.0 Vp-p, Output frequency = 30 kHz

(external oscillator), vdd = 3.3 V, Ta = 25°C

2.0 Vp-p, Output frequency = 30 kHz

(external oscillator), vdd = 3.3 V, Ta = 25°C

2.0 Vp-p, Output frequency = 30 kHz

(external oscillator), vdd = 3.3v, Ta = 25°C

2.0 Vp-p, Output frequency = 30 kHz

(external oscillator), vdd = 3.3 V, Ta = 25°C

Output excitation voltage = 30kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 3.3 V

Output excitation voltage = 30kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 3.3 V

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 3.3 V

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 3.3 V

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 3.3 V

Pin capacitance between VouT and Gnd.

Vdd = 3.3 V, @ 25°C

Input impedance between Vout and Gnd.

vdd = 3.3 V,@ 25°C. No feedback resistor

connected.

Rev. PrB | Page 4 of 48

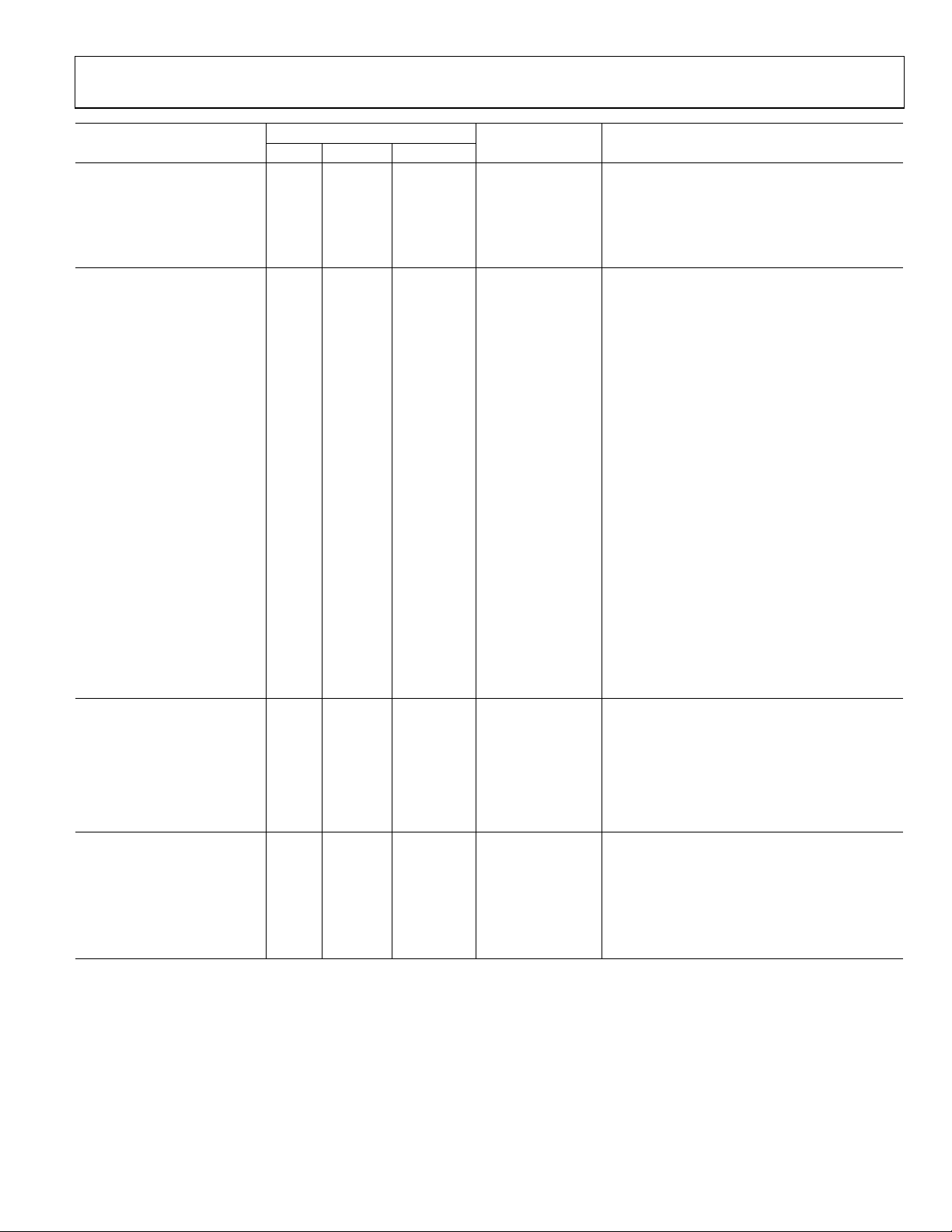

Preliminary Technical Data AD5934

Y Version

1,2

Parameter Min Typ Max Unit Test Conditions/Comments

LOGIC INPUTS

Vih, Input High Voltage 2.3 VDD = 3 V

Vil, Input Low Voltage 0.9 VDD = 3 V

Input Current ±4.2 µA Vdd = 3.3 V, Ta =25°C,

Input Capacitance 7 pF Vdd = 3.3 V, Ta = 25°C

POWER REQUIREMENTS

Vdd 3.3 Volts

IDD (Normal Mode) 9 mA Digital and analog supply currents

IDD (Powerdown Mode) 0.7 µA Digital and analog supply currents

1

Temperature ranges are as follows: Y version = −40°C to +125°C, typical at 25°C.

2

Guaranteed by design and characterization, not production tested.

Rev. PrB | Page 5 of 48

AD5934 Preliminary Technical Data

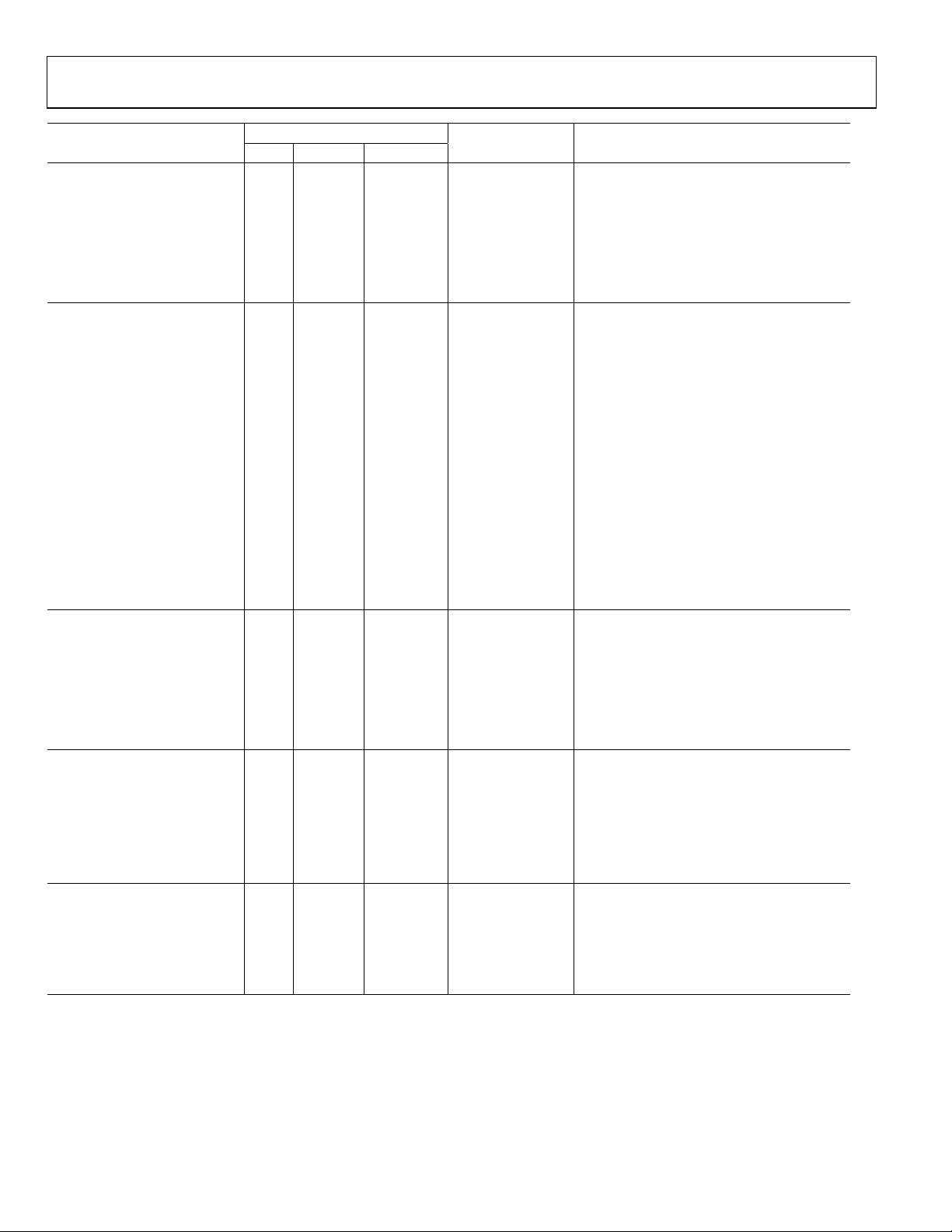

VDD = +5.0 V ±10% T

Table 2.

Y Version

Parameter Min Typ Max Unit Test Conditions/Comments

SYSTEM SPECS

Impedance Range 0.001 10 MΩ

Total System Accuracy 1 %

System ppm 250 ppm/°C Vdd = 5.5 V @ 25°C, 500 Hz bandwidth

MCLK Update Rate 16 MSPS System clock update rate

OUTPUT STAGE

FREQUENCY SPECS

Output Frequency Range 0 100 kHz Hz

Output Frequency

Resoltuion

MCLK External Rerference Clock.

Initial Frequency Accuracy 0.1 Hz

OUTPUT VOLTAGE SPECS

AC Voltage Range div by 1 2.0 Volts peak to peak

Output Voltage Error 0.9 %

DC Bias (vdd/2 ) 1.65 Volts DC bias of AC Signal vdd = 5.5 V

DC Bias Error ±9 % Tolerance of DC Bias

AC Voltage Range div by 2 1.0 Volts peak to peak

Output Voltage Error 0. 8 %

DC Bias (Vdd/4) 0.79 Volts DC bias of AC Signal vdd = 5.5 V

DC Bias Error ±10 % Tolerance of DC Bias

AC Voltage Range div by 5 0.4 Volts peak to peak

Output Voltage Error 0.7 %

DC Bias (Vdd/10) 0.32 Volts DC bias of AC Signal vdd = 5.5 V

DC Bias Error ±9 % Tolerance of DC Bias

AC Voltage Range div by

10

Output Voltage Error 0.4 %

DC Bias (Vdd/20) 0.16 Volts DC bias of AC Signal vdd = 5.5 V

DC Bias Error ±7 % Tolerance of DC Bias

DC Output Impedance

(at Vout)

DC Output Impedance 2.4 kΩ

DC Output Impedance 1 kΩ

DC Output Impedance 600 Ω

Short Circuit Current

(at Vout)

MIN

to T

unless otherwise noted.

MAX

1,2

27 Bits

0. 2 Volts peak to peak

400 Ω

±7 mA

Uni-Polar Sinusoidal Signal at Vout.System

accuracy only guarentted in this range. >100 kHz

achievable by device but accuracy not

guarenteed.

<0.1 Hz Resolution achievable using DDS

techniques

System Output Exitation Frequency Accuracy

using external clock/crystal post triml. 0-100 kHz

Range.

Pk-Pk Unipolar output excitation Voltage on

VOut. Vdd = 5.5 V

Voltage Error on Pk-Pk Output Excitation

voltage. Vdd = 5.5 V

Pk-Pk Unipolar output excitation Voltage on

Vout. Vdd = 5.5 V

Voltage Error on Pk-Pk Output excitation

voltage. Vdd = 5.5 V

Pk-Pk Unipolar output excitation Voltage on

Vout. Vdd = 5.5 V

Voltage Error on Pk-Pk Output excitation

voltage. Vdd = 5.5 V

Pk-Pk Unipolar output excitation Voltage on

VOut. Vdd = 5.5 V

Voltage Error on Pk-Pk Output excitation

voltage. Vdd = 5.5 V

2.0 Vp-p, Output frequency = 30 kHz (external

oscillator), vdd = 5.5 V, Ta = 25°C

1.0 Vp-p, Output frequency = 30 kHz (external

oscillator), vdd = 5.5 V, Ta = 25°C

400 mVp-p, Output frequency = 30 kHz, (external

oscillator) vdd = 5. 5 V, Ta = 25°C

200 mVp-p, Output frequency = 30 kHz (external

oscillator), vdd = 5. 5 V, Ta = 25°C

2.0 Vp-p, Output frequency = 30 kHz (external

oscillator), vdd = 5. 5 V, Ta = 25°C

Rev. PrB | Page 6 of 48

Preliminary Technical Data AD5934

Y Version

Parameter Min Typ Max Unit Test Conditions/Comments

Short Circuit Current ±1 mA

Short Circuit Current ±2.5 mA

Short Circuit Current ±4.5 mA

AC CHARACTERISTICS

Signal to Noise Ratio 60 dB

Total Harmonic Distortion −52 dB

Spurious free Dynamic

Range (SFDR)

Wideband (0 to 1 MHz) 56 dB

Narrowband (±5 kHz) 85 dB

Clock Feedthrough

(0 to 17 MHz)

SYSTEM RESPONSE STAGE

ANALOG INPUT VIN

Input Leakage Current 1 nA To Pin VIN

Input Capacitance 3.5 pF

Input Impedance 68.5G Ω

ADC ACCURACY

Resolution 12 Bits

Sampling Rate 1 MSPS

Integral Nonlinearity ±1 LSB No missing Codes

Differential Nonlinearity ±1 LSB Guaraunted monitonic

Offset Error

Gain Error

TEMPERATURE SENSOR

Accuracy ±1 °C Ta = −40°C to 125°C

Resolution 0.03125 °C

Auto Conversion Update

Rate

Temperature Conversion

Time

−60 dB

1 sec Temperature measurement every 1 sec

800 µs Vdd = 5. 5 V

1,2

2.0 Vp-p, Output frequency = 30 kHz (external

oscillator), vdd = 5. 5 V, Ta = 25°C

2.0 Vp-p, Output frequency = 30 kHz (external

oscillator), vdd = 5. 5 V, Ta = 25°C

2.0Vp-p, Output frequency = 30 kHz (external

oscillator), vdd = 5. 5 V, Ta = 25°C

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 5. 5 V

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 5.5 V

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 5.5 V

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 5.5 V

Output excitation voltage = 30 kHz, external

oscillator mclk = 16.776 MHz, Ta = 25°C

vdd = 5.5 V

Pin capacitance between VouT and Gnd = 5. 5 V

@ 25°C

Input impedance between Vout and Gnd = 5.5 V

@ 25°C. No feedback resistor connected.

Rev. PrB | Page 7 of 48

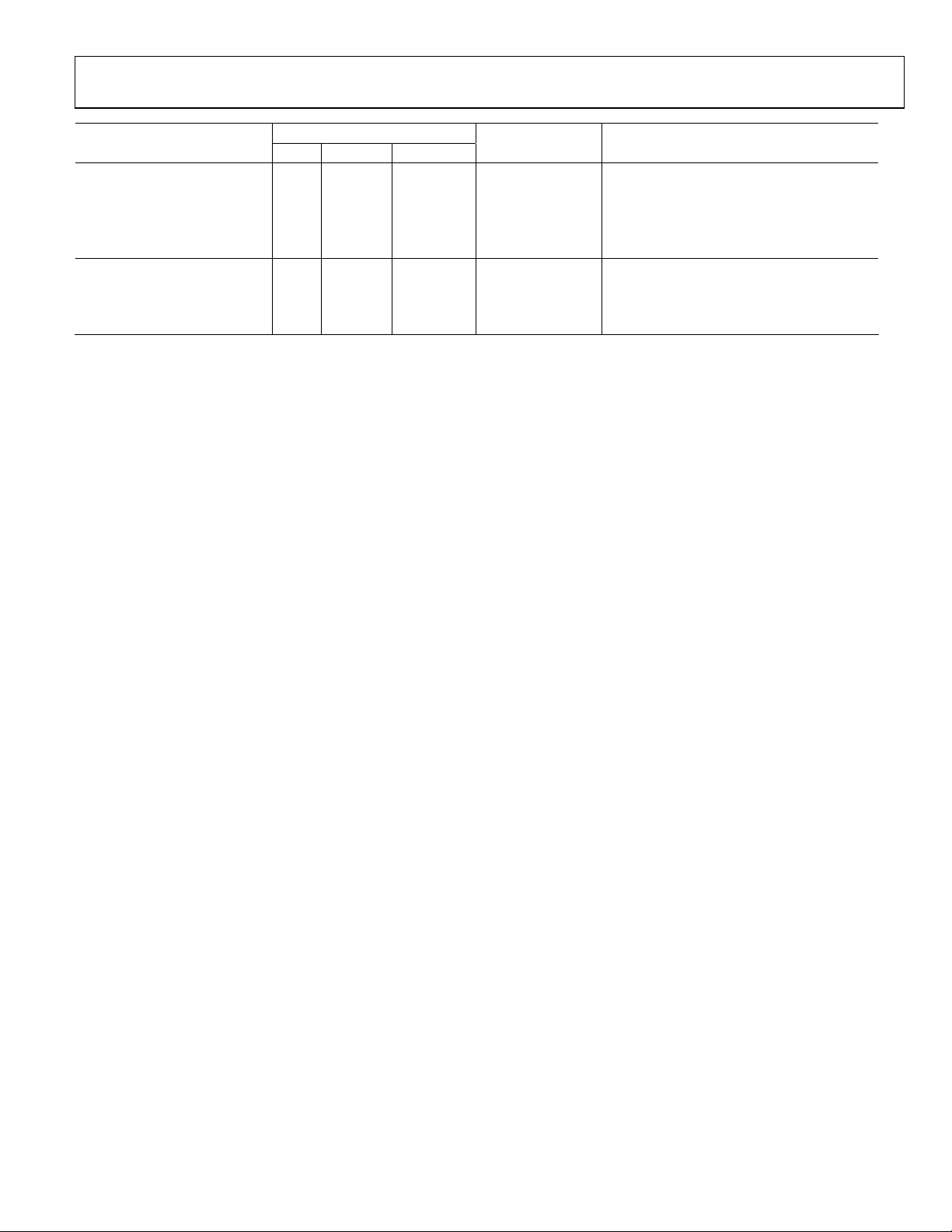

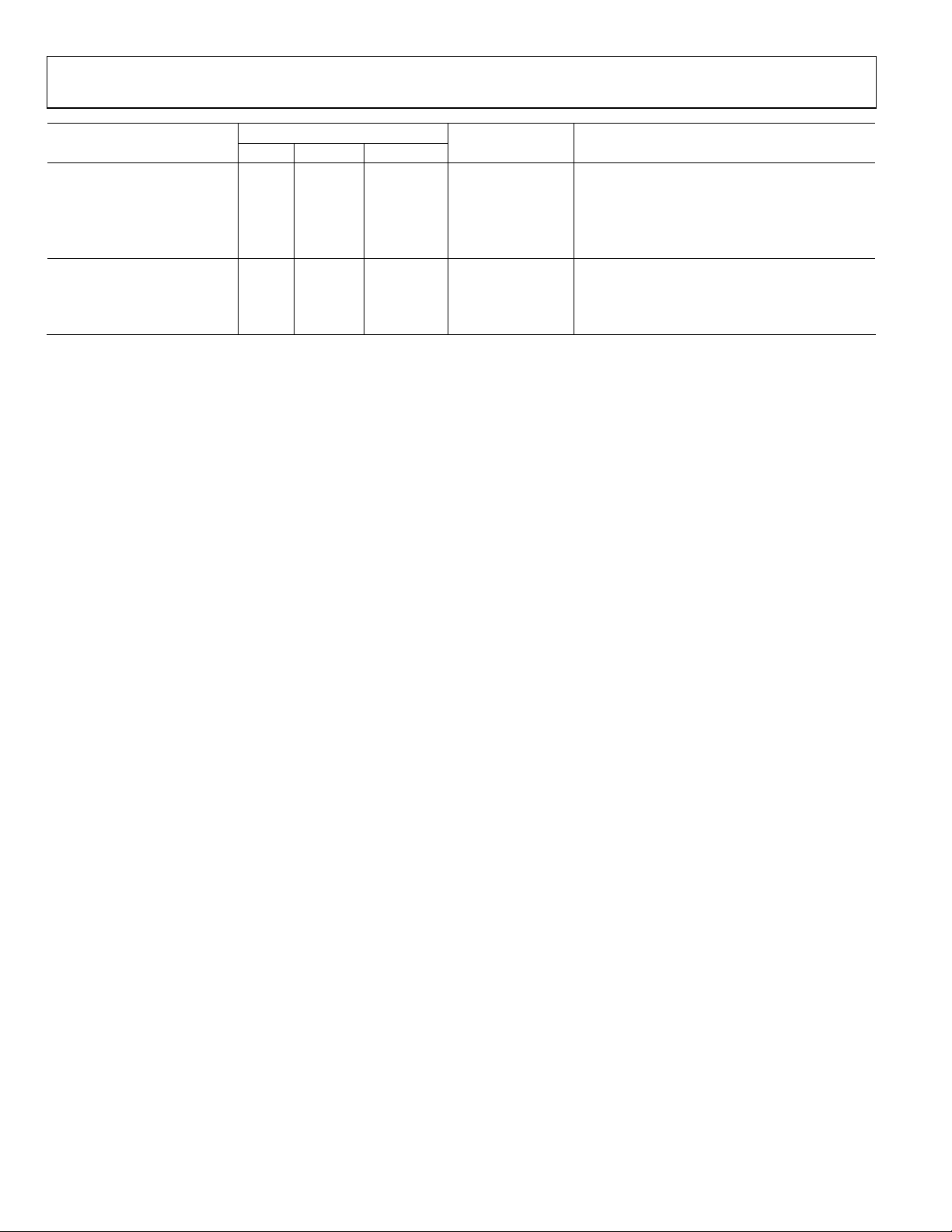

AD5934 Preliminary Technical Data

Y Version

1,2

Parameter Min Typ Max Unit Test Conditions/Comments

LOGIC INPUTS

Vih, Input High Voltage 2.3 VDD = 3 V

Vil, Input Low Voltage 0.9 VDD = 3 V

Input Current ±4.2 µA Vdd = 5. 5 V,Ta =25°C,

Input Capacitance 7 pF Vdd = 5. 5 V,Ta = 25°C

POWER REQUIREMENTS

Vdd 3.3 Volts

IDD (Normal Mode) 9 mA Digital and analog supply currents

IDD (Powerdown Mode) 0.7 µA Digital and analog supply currents

1

Temperature ranges are as follows: Y version = −40°C to +125°C, typical at 25°C.

2

Guaranteed by design and characterization, not production tested.

Rev. PrB | Page 8 of 48

Preliminary Technical Data AD5934

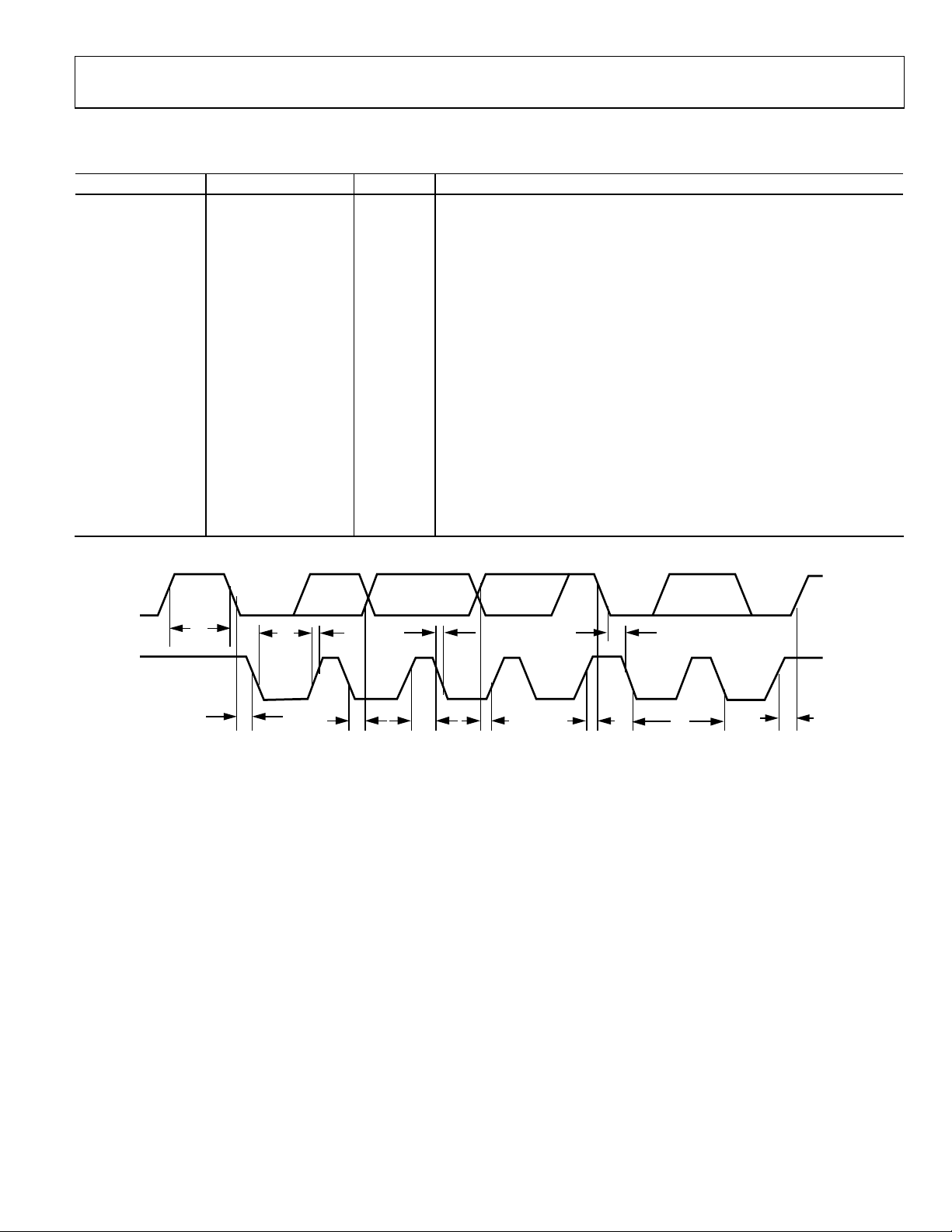

TIMING CHARACTERISTICS

Table 3. I2C Serial Interface

Parameter Limit at T

F

1483 kHz max SCL clock frequency

SCL

t1 0.7 µs min SCL cycle time

t2 0. 2 µs min t

t3 0. 6 µs min t

t4 0.6 µs min tHD,

t5 3 ns min tSU,

t6 0.9 µs max tHD,

0 µs min tHD,

t7 0.007 µs min tSU,

t8 0.6 µs min tSU,

t9 0.161 µs min t

t10 55 ns max tF, fall time of SDA when transmitting

0 ns min tR, rise time of SCL and SDA when receiving (CMOS compatible)

t11 300 ns max tF, fall time of SDA when transmitting

0 ns min tF, fall time of SDA when receiving (CMOS compatible)

300 ns max tF, fall time of SCL and SDA when receiving

20 + 0.1 CB ns min tF, fall time of SCL and SDA when transmitting

CB 400 pF max Capacitive load for each bus line

MIN

, T

Unit Description

MAX

, SCL high time

HIGH

, SCL low time

LOW

, start/repeated start condition hold time

STA

, data setup time

DAT

data hold time

DAT

data hold time

DAT

setup time for repeated start

STA

stop condition setup time

STO

, bus free time between a stop and a start condition

BUF

SDA

t

SCL

9

t

START

CONDITION

t

3

4

t

t

11

10

t

6

t

2

Figure 2. I

t

t

5

7

2

C Interface Timing Diagram

t

4

REPEATED

START

CONDITION

t

1

t

8

STOP

CONDITION

03773-0-007

Rev. PrB | Page 9 of 48

AD5934 Preliminary Technical Data

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise note

Table 4.

Parameter Rating

VDD to GND −0.3 V to +7. 0 V

Digital Input Voltage to GND −0.3 V to VDD +0.3 V

V

to GND −0.3 V to VDD +0.3 V

OUT

Vin to GND −0.3 V to VDD +0.3 V

Operating Temperature Range

Extended Industrial (Y grade) −40°C to +125°C

Storage Temperature Range −65°C to +160°C

Maximum Junction Temperature 150°C

uSOIC Package

θJA Thermal Impedance 332°C/W

θJC Thermal Impedance 120°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) 215°C

Infrared (15 sec) 220°C

ESD 2.0 kV

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on

the human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. PrB | Page 10 of 48

Preliminary Technical Data AD5934

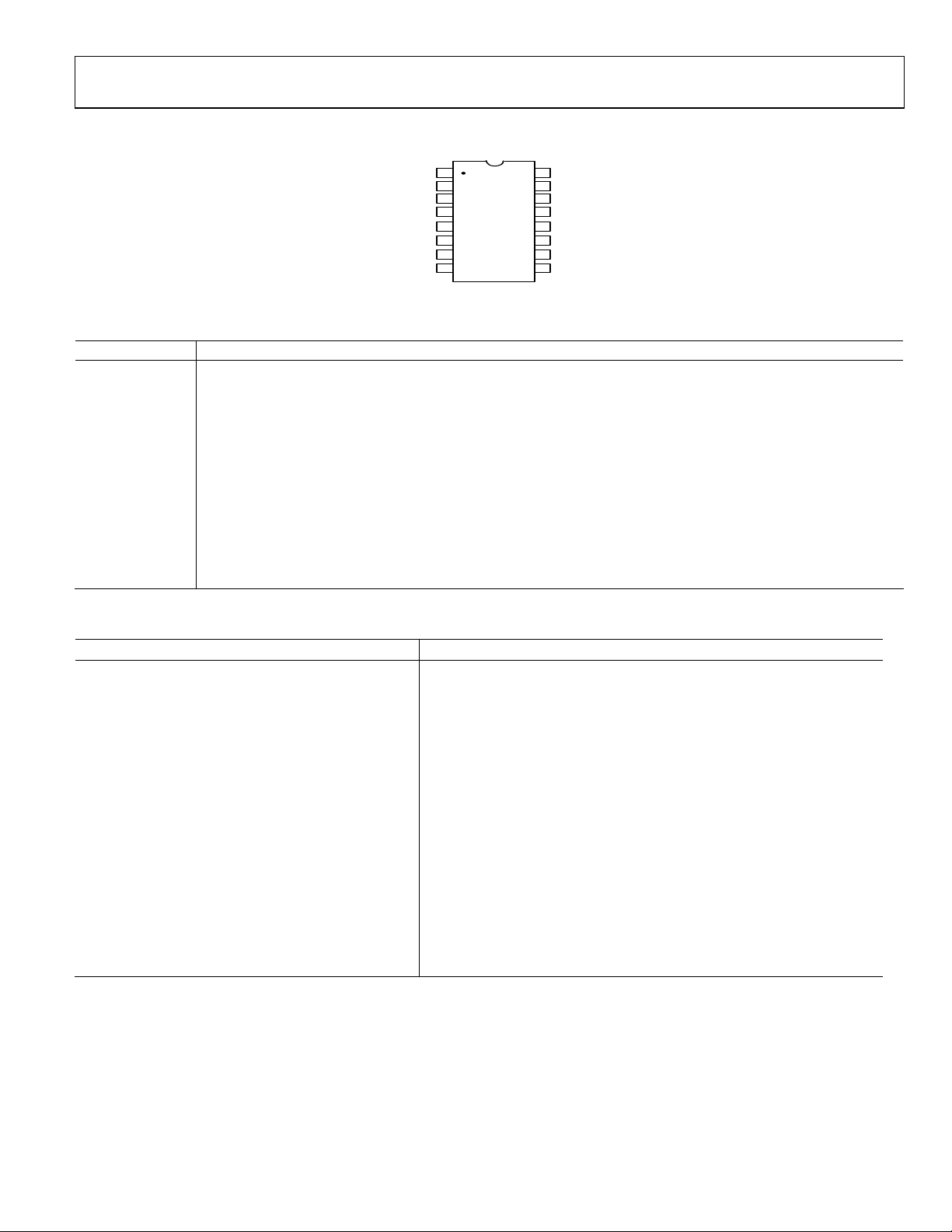

PIN CONFIGURATION AND DESCRIPTIONS

1

N/C

2

N/C

N/C

3

4

AD5934

5

VIN

VOUT

N/C

MCLK

TOP VIEW

(Not to Scale)

6

7

8

Figure 3. Pin Configuration

Table 5. Pin Function Descriptions

Mnemonic Description

N/C No Connect.

RFB_PIN External Feedback Resistor. This is used to set the gain of the input signal of the VIN node.

VOUT Input Signal to transimpedance amplifier. External Feedback resistor will control gain of transimpedance amplifier.

MCLK Master Clock for the system. Used to provide output excitation signal and as sampling of ADC.

DVDD Digital Supply Voltage

AVDD1 Analog Supply Voltage 1

AVDD2 Analog Supply Voltage 2

DGND Digital Ground

AGND1 Analog Gnd 1

AGND2 Analog Gnd 2

SDA I2C Data Input

SCL I2C Clock Input

Table 6. Recommended Pin Connections for AD5934

Mnemonic Function

Pin 1 Ext_Out Test Pin—Leave unconnected

Pin 2 NC No Connect—Do not apply any signal

Pin 3 NC No Connect—Do not apply any signal

Pin4 NC No Connect—Do not apply any signal

Pin5 Vin (Receive side of impedance) Test Impedance is connected between this pin and vout pin

Pin6 Vout (Excitation side of impedance) Test Impedance is connected between this pin and vin pin

Pin 7 NC No Connect—Do not apply any signal

Pin 8 Ext_Clk Extclk Pad—Only used if external clk option is selected

Pin 9 AVDD1 Recommended to be tied to 3.3 V

Pin10 AVDD2 Recommended to be tied to 3.3 V

Pin11 DVDD Recommended to be tied to 3.3 V

Pin12 DGND Must be tied to GND

Pin13 AGND1 Must be tied to GND

Pin14 AGND2 Must be tied to GND

Pin15 SDA I2C Data Pin

Pin16 SCL I2C Clk Pin

16

15

14

13

12

11

10

9

SCL

SDA

AGND2

AGND1RFB_PIN

DGND

AVDD2

AVDD1

DVDD

It is recommended to tie all supply connections (Pins 9, 10, 11) and run from a single supply between 3. 0 V and 5.5 V. Also, it is

recommended to connect all ground signals together (Pins 12, 13, 14).

Rev. PrB | Page 11 of 48

AD5934 Preliminary Technical Data

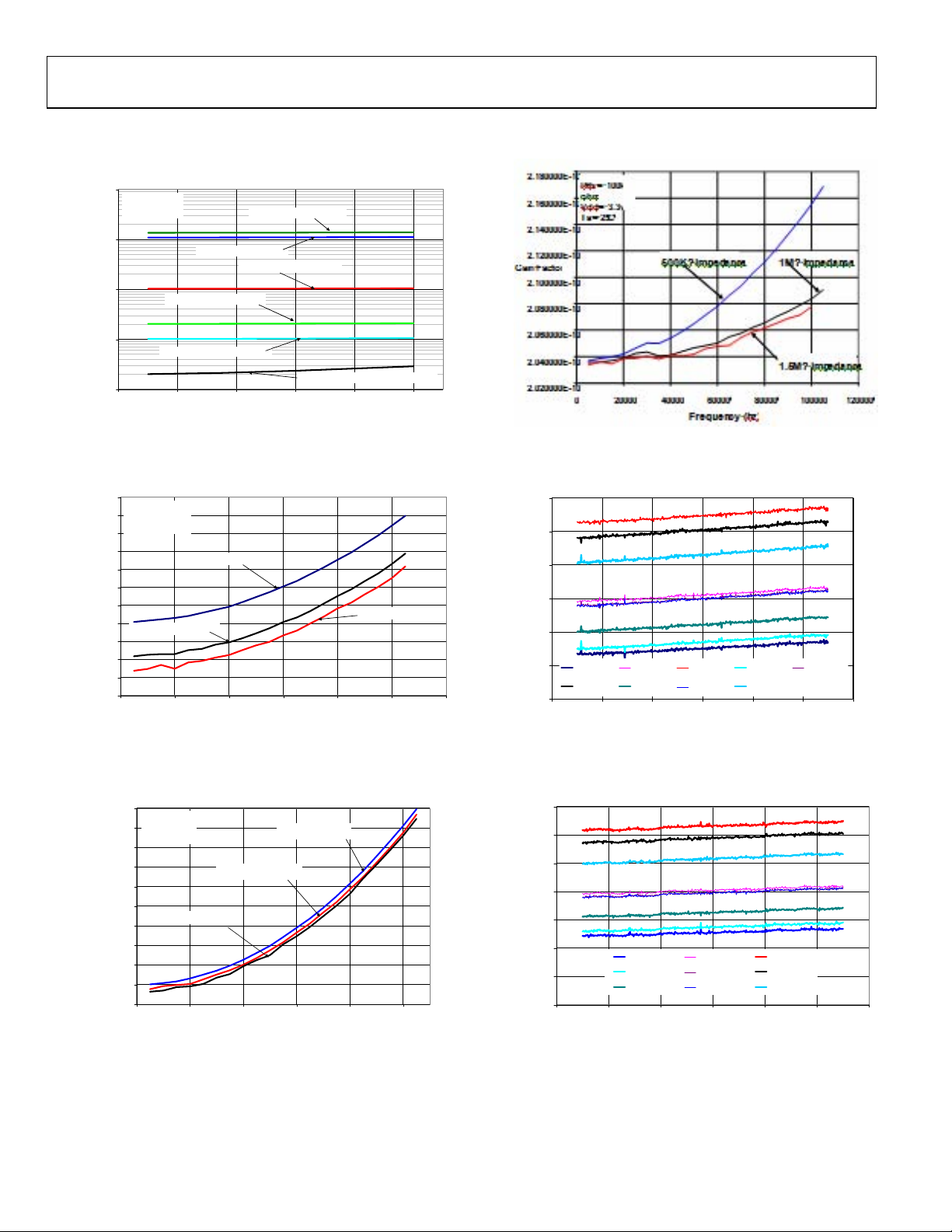

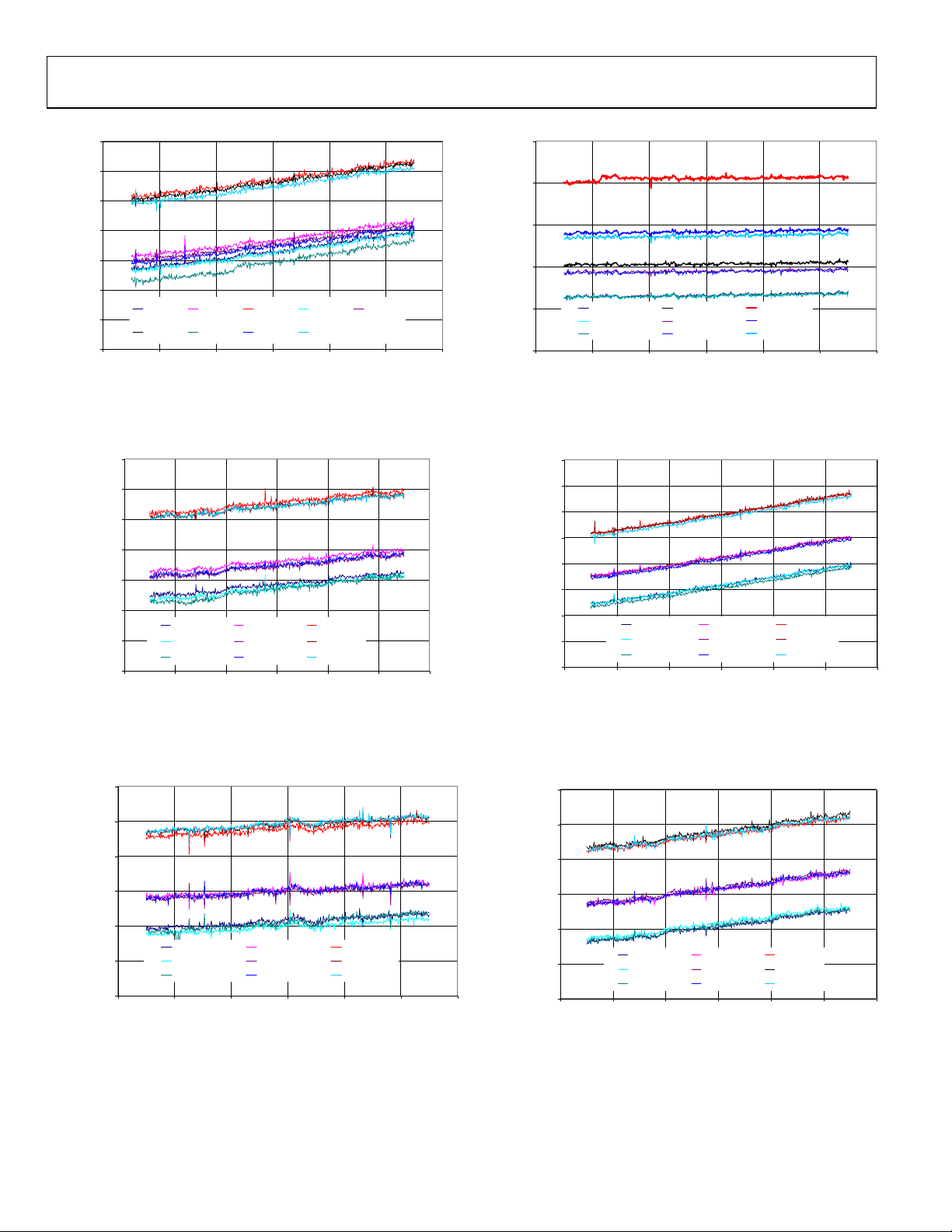

TYPICAL PERFORMANCE CHARACTERISTICS

1.00E-06

Ta = 25°C

Vdd = 3.3v

Rfb = 1k, 0.5k impedance

1.00E-07

1.00E-08

Gain Factor

1.00E-09

1.00E-10

0 20000 40000 60000 80000 100000

Rfb = 1k, 1k impedance

Rfb = 10k, 10k impedance

Rfb = 50k, 50k impedance

Rfb = 100k, 100k impedance

Rfb = 1M, 1M impedance

Frequency (Hz)

Figure 4. Gain Factor vs. Frequency for Various Rfb/Impedance Ranges

2.000E-08

1.980E-08

1.960E-08

1.940E-08

1.920E-08

1.900E-08

1.880E-08

Gain Factor

1.860E-08

1.840E-08

1.820E-08

1.800E-08

1.780E-08

Rfb = 1k ohm

Vdd = 3.3v

Ta = 25°C

5KΩ impedance

15KΩ impedance

10KΩ impedance

0 20000 40000 60000 80000 100000 120000

Frequency (Hz)

Figure 5. Gain Factor vs. Frequency for 5 Ωk to 15 kΩ Impedance Range

Figure 7. Gain Factor vs. Frequency for 500 kΩ to 1.5 MΩ Impedance Range

1.03E+03

1.02E+03

1.01E+03

1.00E+03

Impedance (Ohm)

9.90E+02

9.80E+02

9.70E+02

2.7V -40C

3.3V 125C

94.0E+3 96.0E+3 98.0E+3 100.0E+3 102.0E+3 104.0E+3 106.0E+3

2.7V 25C

5.5V -40C

2.7V 125C

5.5V 25C

Frequency (Hz)

3.3V -40C

5.5V 125C

3.3V 25C

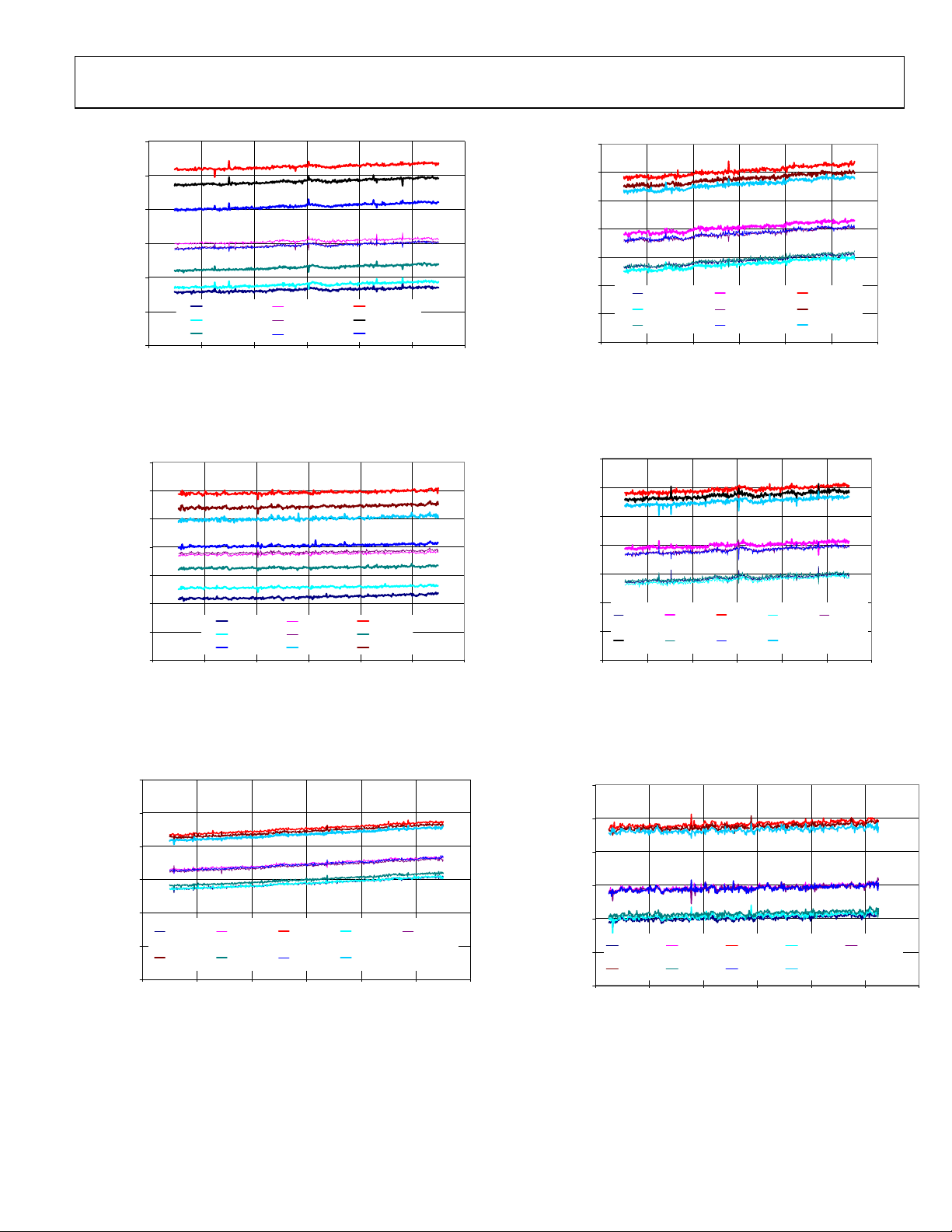

Figure 8. Impedance vs. Frequency for a 1 kΩ Rfb Impedance, Gain Factor @100 kHz

2.200E-09

Rfb = 10k ohm

Vdd = 3.3v

2.180E-09

Ta = 25°C

2.160E-09

2.140E-09

2.120E-09

2.100E-09

2.080E-09

gain factor

2.060E-09

2.040E-09

2.020E-09

2.000E-09

150KΩ impedance

0 20000 40000 60000 80000 100000

100KΩ impedance

50KΩ impedance

Frequency (hz)

Figure 6. Gain Factor vs. Frequency for 50 kΩ to 150 kΩ Impedance Range

Rev. PrB | Page 12 of 48

1.03E+03

1.02E+03

1.01E+03

1.00E+03

9.90E+02

Impedance (ohms)

9.80E+02

9.70E+02

9.60E+02

54000 56000 58000 60000 62000 64000 66000

2.7V -40C

3.3V -40C

5.5V -40C

2.7V 25C

3.3V 25C

5.5V 25C

Frequency (Hz)

2.7V 125C

3.3V 125C

5.5V 125C

Figure 9. Impedance vs. Frequency for a 1 kΩ Rfb, impedance, Gain Factor @ 60 kHz

Preliminary Technical Data AD5934

0

1.03E+03

1.02E+04

1.02E+03

1.01E+03

1.00E+03

9.90E+02

Impedance ( ohm )

9.80E+02

9.70E+02

29000 31000 33000 35000 37000 39000 41000

2.7 -40C

3.3v -40C

5.5 -40C

2.7 25C

3.3 25C

5.5 25C

Frequency (Hz)

2.7 125

3.3 125C

5.5 125C

Figure 10. Impedance vs. Frequency 1 kΩ Rfb, Impedance, Gain Factor @ 35 kHz

1.03E+03

1.02E+03

1.01E+03

1.00E+03

9.90E+02

Impedance ( ohm )

9.80E+02

9.70E+02

9.60E+02

4.00E+03 6.00E+03 8.00E+03 1.00E+04 1.20E+04 1.40E+04 1.60E+04

2.7 -40

3.3 -40

5.5 25

2.7 25

3.3 25

5.5 125

Frequency (Hz)

2.7 125

5.5 -40

3.3 125

Figure 11. Impedance vs. Frequency 1 kΩ Rfb, Impedance, Gain Factor @ 10 kHz

1.01E+04

1.01E+04

1.00E+04

9.95E+03

Impedance

9.90E+03

9.85E+03

9.80E+03

54000 56000 58000 60000 62000 64000 66000

2.7V -40C

3.3V -40C

5.5V -40C

2.7V 25C

3.3V 25C

5.5V 25C

Frequency (Hz)

2.7V 125C

3.3V 125C

5.5V 125C

Figure 13. Impedance vs. Frequency 10 kΩ Rfb, Impedance, Gain Factor @ 60 kHz

1.02E+04

1.01E+04

1.01E+04

1.00E+04

9.95E+03

Impedance

9.90E+03

9.85E+03

9.80E+03

2.7V -40C

3.3V 125C

29000 31000 33000 35000 37000 39000 41000

2.7V 25C

5.5V -40C

2.7V 125C

5.5V 25C

Frequency (Hz)

3.3V -40C

5.5V 125C

3.3V 25C

Figure 14. Impedance vs. Frequency 10 kΩ Rfb, Impedance, Gain Factor @ 35 kHz

1.03E+04

1.02E+04

1.01E+04

9.95E+03

Impedance (Ohm)

9.85E+03

9.75E+03

9.65E+03

2.7V -40C 2.7V 25C 2.7V 125C 3.3V -40C 3.3V 25C

3.3V 125C 5.5V -40C 5.5V 25C 5.5V 125C

94.0E+3 96.0E+3 98.0E+3 100.0E+3 102.0E+3 104.0E+3 106.0E+3

Frequency (Hz)

Figure 12. Impedance vs. Frequency 10 kΩ Rfb, Impedance, Gain Factor @ 100 kHz

1.02E+04

1.01E+04

1.01E+04

1.00E+04

Impedance

9.95E+03

9.90E+03

9.85E+03

2.7V -40C

3.3V 125C

4500 6500 8500 10500 12500 14500 1650

2.7V 25C

5.5V -40C

2.7V 125C

5.5V 25C

Frequency (Hz)

3.3V -40C

5.5V 125C

3.3V 25C

Figure 15. Impedance vs. Frequency 10 kΩ Rfb, Impedance, Gain Factor @ 10 kHz

Rev. PrB | Page 13 of 48

AD5934 Preliminary Technical Data

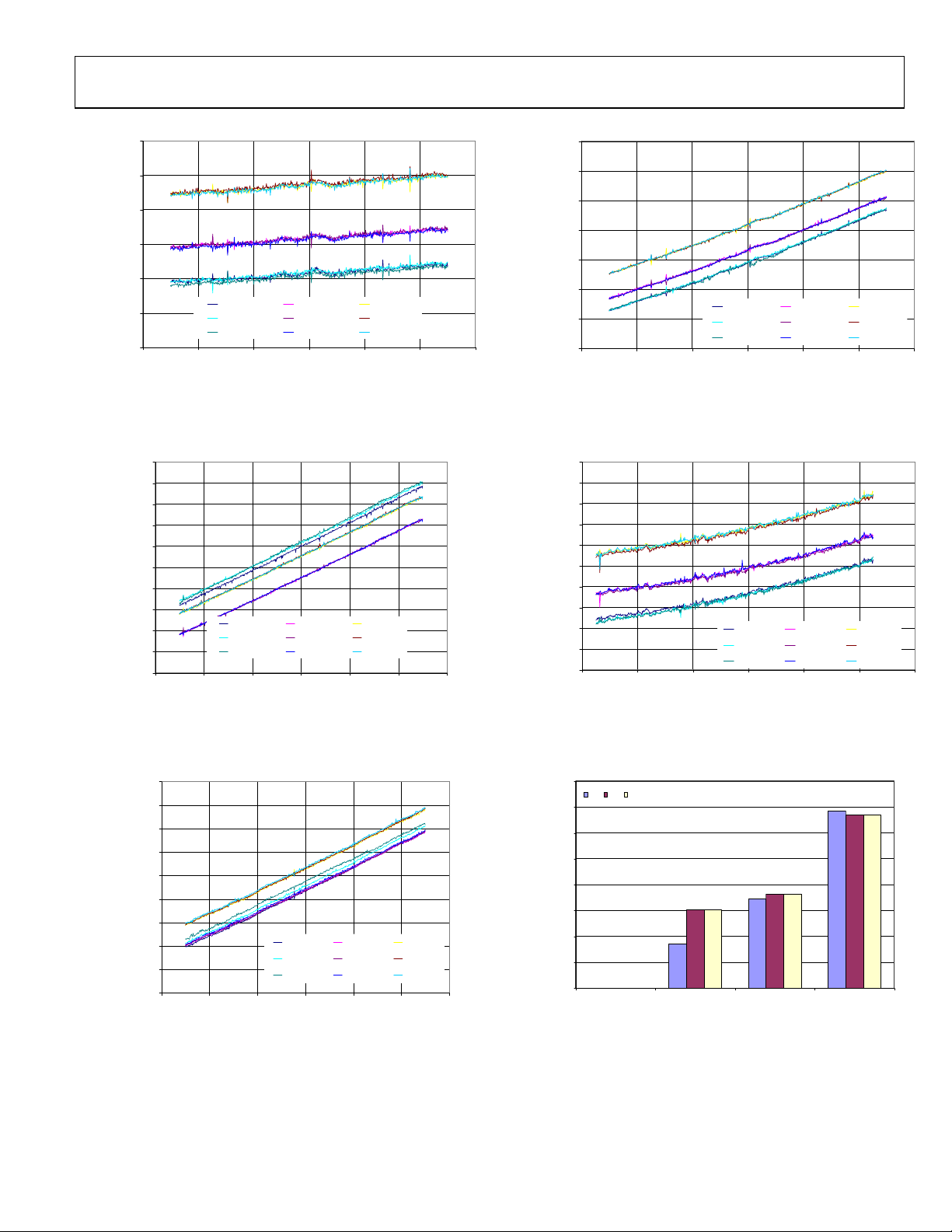

0

0

0

50600

51500

50400

50200

50000

49800

Impedance

49600

49400

49200

94000 96000 98000 100000 102000 104000 106000

2.7V -40C 2. 7V 25C 2.7V 125C 3.3V -40C 3.3V 25C

3.3V 125C 5.5V -40C 5.5V 25C 5.5V 125C

Frequency

Figure 16. Impedance vs. Frequency 50 kΩ Rfb, Impedance, Gain Factor @ 100 kHz

5.06E+04

5.04E+04

5.02E+04

5.00E+04

4.98E+04

Impedance

4.96E+04

4.94E+04

4.92E+04

54000 56000 58000 60000 62000 64000 66000

2.7V -40C

3.3V -40C

5.5V -40C

2.7V 25C

3.3V 25C

5.5V 25C

Frequency (Hz)

2.7V 125C

3.3V 125C

5.5V 125C

Figure 17. Impedance vs. Frequency 50 kΩ Rfb, Impedance, Gain Factor @ 60 kHz

51000

50500

Impedance

50000

49500

49000

4000 6000 8000 10000 12000 14000 16000

2.7V -40C 2.7V 25C 2.7V 125C

3.3V -40C 3.3V 25C 3.3V 125C

5.5V -40C 5.5V 25C 5.5V 125C

Frequency (Hz)

Figure 19. Impedance vs. Frequency 50 kΩ Rfb, Impedance, Gain Factor @ 10 kHz

1.02E+05

1.02E+05

1.01E+05

1.01E+05

1.00E+05

Impedance

9.95E+04

9.90E+04

9.85E+04

9.80E+04

9.40E+04 9.60E+04 9.80E+04 1.00E+05 1.02E+05 1.04E+05 1.06E+

2.7V -40C

3.3V -40C

5.5V -40C

2.7V 25C

3.3V 25C

5.5V 25C

Frequency (Hz)

2.7V 125C

3.3V 125C

5.5V 125C

Figure 20. Impedance vs. Frequency 100 kΩ Rfb, Impedance, Gain Factor @ 100 kHz

5.05E+04

5.03E+04

5.01E+04

4.99E+04

Impedance

4.97E+04

4.95E+04

4.93E+04

29000 31000 33000 35000 37000 39000 4100

2.7V -40C

3.3V -40C

5.5V -40C

2.7V 25C

3.3V 25C

5.5V 25C

Frequency (Hz)

2.7V 125C

3.3V 125C

5.5V 125C

Figure 18. Impedance vs. Frequency 50 kΩ Rfb, Impedance, Gain Factor @ 35 kHz

1.02E+05

1.01E+05

1.01E+05

1.00E+05

Impedance

9.95E+04

9.90E+04

9.85E+04

54000 56000 58000 60000 62000 64000 660

2.7V -40C

3.3V -40C

5.5V -40C

2.7V 25C

3.3V 25C

5.5V 25C

Frequency ( Hz)

2.7V 125C

3.3V 125C

5.5V 125C

Figure 21. Impedance vs. Frequency 100 kΩ Rfb, Impedance, Gain Factor @ 60 kHz

Rev. PrB | Page 14 of 48

Preliminary Technical Data AD5934

1.02E+05

5.30E+05

1.01E+05

1.01E+05

1.00E+05

Impedance

9.95E+04

9.90E+04

9.85E+04

29000 31000 33000 35000 37000 39000 41000

2.7V -40C 2.7V 25C 2.7V 125C

3.3V -40C 3.3V 25C 3.3V 125C

5.5V -40C 5.5V 25C 5.5V 125C

Frequency (Hz)

Figure 22. Impedance vs. Frequency 100 kΩ Rfb, Impedance, Gain Factor @ 35 kHz

540000

535000

530000

525000

520000

515000

Impedance

510000

505000

500000

495000

490000

9.40E+04 9.60E+04 9.80E+04 1.00E+05 1.02E+05 1.04E+05 1.06E+05

2.7V -40C

3.3V -40C

5.5V -40C

2.7V 25C

3.3V 25C

5.5V 25C

Frequency (Hz)

2.7V 125C

3.3V 125C

5.5V 125C

Figure 23. Impedance vs. Frequency 500 kΩ Impedance, Gain Factor @ 100 kHz

5.25E+05

5.20E+05

5.15E+05

5.10E+05

Impedance

5.05E+05

5.00E+05

4.95E+05

29000 31000 33000 35000 37000 39000 41000

2.7V -40C 2.7V 25C 2.7V 125C

3.3V -40C 3.3V 25C 3.3V 125C

5.5V -40C 5.5V 25C 5.5V 125C

Frequency (Hz)

Figure 25. Impedance vs. Frequency 500 kΩ Impedance, Gain Factor @ 35 kHz

5.22E+05

5.20E+05

5.18E+05

5.16E+05

5.14E+05

5.12E+05

Impedance

5.10E+05

5.08E+05

5.06E+05

5.04E+05

5.02E+05

4500 6500 8500 10500 12500 14500 16500

2.7V -40C 2.7V 25C 2.7V 125C

3.3V -40C 3.3V 25C 3.3V 125C

5.5V -40C 5.5V 25C 5.5V 125C

Frequency (Hz)

Figure 26. Impedance vs. Frequency 500 kΩ Impedance, Gain Factor @ 10 kHz

5.35E+05

5.30E+05

5.25E+05

5.20E+05

5.15E+05

5.10E+05

Impedance

5.05E+05

5.00E+05

4.95E+05

4.90E+05

54000 56000 58000 60000 62000 64000 66000

2.7V -40C

3.3V -40C

5.5V -40C

Frequency (Hz)

2.7V 25C

3.3V 25C

5.5V 25C

2.7V 125C

3.3V 125C

5.5V 125C

Figure 24. Impedance vs. Frequency 500 kΩ Impedance, Gain Factor @ 60 kHz

Rev. PrB | Page 15 of 48

0.8

2.7V

3.3V

0.7

0.6

0.5

0.4

% Error

0.3

0.2

0.1

0

5.5V

10kHz 35kHz 60kHz 100kHz

Frequency

Figure 27. Impedance Error over 10 kHz to 100 kHz Range, Gain Factor @ 10 kHz

AD5934 Preliminary Technical Data

0.4

vdd = 3.3

Ta =25°C

Freq = 32khz

0.2

0

-0.2

-0.4

phase error (degrees)

-0.6

-0.8

-1

0 50 100 150 200 250 300 350 400

Phase (degrees)

Figure 28. Typical AD5934 Phase Error

50.1E+3

Rf = 50kΩ

impedance = 50kΩ

50.0E+3

50.0E+3

49.9E+3

49.9E+3

Impedance (Ohm)

49.8E+3

49.8E+3

49.7E+3

54.0E+3 56.0E+3 58.0E+3 60.0E+3 62.0E+3 64.0E+3 66.0E+3

vdd = 5.5v

vdd = 3.3v vdd = 2.7v

Frequency (Hz)

Figure 31. Typical Impedance e vs. Frequency for 49.992 kΩ Impedance,

Single Point Calibrated Gain Factor @ 60 kHz

3.0E+3

2.5E+3

2.0E+3

1.5E+3

1.0E+3

Impedance (Ohm)

500.0E+0

000.0E+0

k

k

k

k

P

P

V

4

.

0

k

P

P

-

-

k

k

P

V

0

2

.

.

2

0

DDS Output Voltag e Range

P

P

-

-

k

k

P

P

V

.

1

V

V

0

4

.

0

k

P

-

k

k

P

P

V

V

0

0

.

.

2

1

Vdd 3.3V Vdd 5.5V

Figure 29. Typical AD5934 Output Impedance

30.4E+3

30.4E+3

30.3E+3

30.3E+3

30.2E+3

Frequency (Hz)

30.2E+3

30.1E+3

30.1E+3

30.0E+3

vdd = 3.3

vdd = 3.3

output freq = 30khz @25°

-60 -40 -20 0 20 40 60 80 100 120 140

C

Temperature (degree C)

vdd = 5.5v

Figure 30. Typical AD5934 Frequency Temperature Coefficient

50.0E+3

50.0E+3

49.9E+3

49.9E+3

49.9E+3

49.9E+3

Impedance (ohm)

49.9E+3

49.8E+3

Rf = 50kΩ

impedance = 50kΩ

k

k

P

P

-

-

k

k

P

P

V

2

.

0

49.8E+3

49.8E+3

54.0E+3 56.0E+3 58.0E+3 60.0E+3 62.0E+3 64.0E+3 66.0E+3

vdd = 3.3v

vdd = 5.5v

vdd = 2.7v

Frequency (Hz)

Figure 32. Typical Impedance e vs. Frequency for 49.992 kΩ Impedance,

End Point Calibrated Gain Factor

Rev. PrB | Page 16 of 48

Preliminary Technical Data AD5934

TERMINOLOGY

DAC/DDS CORE:

Relative Accuracy

For the DAC, relative accuracy or Integral Nonlinearity (INL) is

a measure of the maximum deviation, in LSBs, from a straight

line passing through the endpoints of the DAC transfer

function.

Differential Nonlinearity

Differential Nonlinearity (DNL) is the difference between the

measured change and the ideal 1 LSB change between any two

adjacent codes. A specified differential nonlinearity of ±1 LSB

maximum ensures monotonicity. This DAC is guaranteed

monotonic by design.

Zero-Code Error

Zero-code error is a measure of the output error when zero

code (0000 Hex) is loaded to the DAC register. Ideally the

output should be 0 V. The zero-code error is always positive in

the AD5934 because the output of the DAC cannot go below 0

V. It is due to a combination of the offset errors in the DAC and

output amplifier. Zero-code error is expressed in mV.

Full-Scale Error

Full-scale error is a measure of the output error when full-scale

code (FFFF Hex) is loaded to the DAC register. Ideally the

output should be VDD − 1 LSB. Full-scale error is expressed in

percent of full-scale range.

Gain Error

This is a measure of the span error of the DAC. It is the

deviation in slope of the DAC transfer characteristic from ideal

expressed as a percent of the full-scale range.

Tot a l U n ad ju s te d E rr o r

Total Unadjusted Error (TUE) is a measure of the output error

taking all the various errors into account.

Zero-Code Error Drift

This is a measure of the change in zero-code error with a

change in temperature. It is expressed in µV/°C.

Gain Error Drift

This is a measure of the change in gain error with changes in

temperature. It is expressed in (ppm of full-scale range)/°C.

Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the

analog output when the input code in the DAC register changes

state. It is normally specified as the area of the glitch in nV secs

and is measured when the digital input code is changed by

1 LSB at the major carry transition (7FFF Hex to 8000 Hex).

Digital Feedthrough

Digital feedthrough is a measure of the impulse injected into

the analog output of the DAC from the digital inputs of the

DAC but is measured when the DAC output is not updated. It is

specified in nV secs and measured with a full-scale code change

on the data bus, i.e., from all 0s to all 1s and vice versa.

Spurious-Free Dynamic Range

Along with the frequency of interest, harmonics of the

fundamental frequency and images of these frequencies are

present at the output of a DDS device. The spurious-free

dynamic range (SFDR) refers to the largest spur or harmonic

present in the band of interest. The wideband SFDR gives the

magnitude of the largest harmonic or spur relative to the

magnitude of the fundamental frequency in the “0” to Nyquist

bandwidth. The narrow band SFDR gives the attenuation of the

largest spur or harmonic in a bandwidth of ±200 kHz about the

fundamental frequency.

Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured output signal

to the rms sum of all other spectral components below the

Nyquist frequency. The value for SNR is expressed in decibels.

Rev. PrB | Page 17 of 48

AD5934 Preliminary Technical Data

ADC:

Integral Nonlinearity

This is the maximum deviation from a straight line passing

through the endpoints of the ADC transfer function. The

endpoints of the transfer function are zero scale, a point 1/2

LSB below the first code transition, and full scale, a point 1/2

LSB above the last code transition.

Differential Nonlinearity

This is the difference between the measured and the ideal 1 LSB

change between any two adjacent codes in the ADC.

Integral Nonlinearity

This is the maximum deviation from a straight line passing

through the endpoints of the ADC transfer function. The

endpoints of the transfer function are zero scale, a point 1/2

LSB below the first code transition, and full scale, a point 1/2

LSB above the last code transition.

Differential Nonlinearity

This is the difference between the measured and the ideal 1 LSB

change between any two adjacent codes in the ADC.

Offset Error

This is the deviation of the first code transition (00 . . . 000) to

(00 . . . 001) from the ideal, i.e., AGND + 0.5 LSB.

Total Harmonic Distortion

Total harmonic distortion (THD) is the ratio of the rms sum of

harmonics to the fundamental. where V1 is the rms amplitude

of the fundamental and V2, V3, V4, V5 and V6 are the rms

amplitudes of the second through the sixth harmonics. For the

AD5934, it is defined as

2

2

2

2

THD

2

=

2

log20)dB(

4

3

V

1

++++

VVVVV

6

5

Gain Error

This is the deviation of the last code transition (111 . . . 110) to

(111 . . . 111) from the ideal (i.e., VREF − 1.5 LSB) after the

offset error has been adjusted out.

Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the

output of the A/D converter. The signal is the rms amplitude of

the fundamental. Noise is the sum of all non fundamental signals

up to half the sampling frequency (fS/2), excluding dc. The ratio is

dependent on the number of quantization levels in the digitization

process; the more levels, the smaller the quantization noise. The

theoretical signal to (noise + distortion) ratio for an ideal N-bit

converter with a sine wave input is given by

Signal to (Noise + Distortion) = (6.02N + 1.76)dB

Thus for a 12-bit converter, this is ≈74 dB.

Rev. PrB | Page 18 of 48

Preliminary Technical Data AD5934

∆=∆

SYSTEM ARCHITECTURE DESCRIPTION

The AD5934 is a high precision impedance converter system

solution which combines an on board frequency generator with a

12 Bit 1MSPS ADC. The frequency generator allows an external

complex impedance to be excited with a known frequency. The

response signal from the impedance is sampled by the on board

ADC and DFT processed by an on-board DSP engine. The DFT

algorithm returns both a Real (R) and Imaginary (I) data word at

each frequency point along the sweep. The impedance magnitude

and phase is easily calculated using the following equations:

MCLK

/2π

Figure 34.

Figure 35.

= Δt)

22

IRMagnitude +=

)/(1RITanPhase−=

To determine the actual real impedance value Z(W), generally a

frequency sweep is performed. The impedance can be

calculated at each point and a frequency vs. magnitude plot can

be created like that shown in Figure 33.

Figure 33.

The system allows the user to program a 2V PK-PK sinusoidal

signal as excitation to an external load. Output ranges of 1V,

500mV, 200mV can also be programmed. The signal is provided

on chip using DDS techniques. Frequency resolution of 27 bits

(less than 0.1HZ) can be achieved. The clock for the DDS can

be generated from an external reference clock. The following

section will describe the internal architecture of both the input

and output stages of the AD5934.

OUTPUT STAGE

The output stage of the AD5934, shown in Figure 34, provides a

constant output frequency or frequency sweep function which

has a programmable output voltage of 2/1/0.4/0.2V. The

frequency sweep sequence is preprogrammed to the onboard

RAM through the I

start the excitation sequence.

2

C interface. An I2C command is used to

DDS CORE: CIRCUIT DESCRIPTION

The AD5934 has a fully integrated Direct Digital Synthesis

(DDS) core to generate required frequencies. The block requires

a reference clock to provide digitally created sine waves up to 50

kHz. This is provided through an external reference clock,

MCLK. This clock is internally divided down by 4 to provide

the reference clock or fMCLK to the DDS.

The internal circuitry of the DDS consists of the following main

sections: a Numerical Controlled Oscillator (NCO), a Frequency

Modulator, SIN ROM, and a Digital-to-Analog Converter.

DDS Theory of Operation

Sine waves are typically thought of in terms of their magnitude

form A (t) = sin (2πft). However, these are nonlinear and not

easy to generate except through piecewise construction. On the

other hand, the angular information is linear in nature. That is,

the phase angle rotates through a fixed angle for each unit of

time. The angular rate depends on the frequency of the signal

by the traditional rate of 2πf.

Knowing that the phase of a sine wave is linear and given a

reference interval (clock period), the phase rotation for the

period can be determined.

twphase

Solving for w = Δ phase / Δ t = 2 π f

Solving for f and substituting the reference clock frequency for

the reference period (1/f

f = Δ phase x f

MCLK

Rev. PrB | Page 19 of 48

AD5934 Preliminary Technical Data

The AD5934 builds the output based on this simple equation. A

simple DDS core can implement this equation with three major

subcircuits: Numerically Controlled Oscillator + Phase Modulator,

SIN ROM, and Digital-to-Analog Converter. Each of these sub

circuits is discussed in the following section.

NUMERICAL CONTROLLED OSCILLATOR

The main component of the NCO as shown in Figure 36, is a

27-bit phase accumulator. Continuous time signals have a phase

range of 0 to 2π. Outside this range of numbers, the sinusoid

functions repeat themselves in a periodic manner. The digital

implementation is no different. The accumulator simply scales

the range of phase numbers into a multi-bit digital word. The

phase accumulator in the AD5934 is implemented with 27 bits.

Therefore in the AD5934, 2π = 2

scaled into this range of numbers:

0 < ∆ Phase < 2

27

− 1

Making these Substitutions into the equation above

f = Δ Phase × f

MCLK

/227

The input to the phase accumulator is taken from the contents

of the start frequency register (see RAM locations 82h, 83h, 84h).

Although the phase accumulator offers 27 bits of resolution the

start frequency register has the three MSBs set to zero, thus the

register only gives 24 bit frequency tune ability to the user whilst

retaining 27 bit resolution therefore the minimum clock frequency

which can be used for the AD5934 to retain system accuracy

is ≈ 500 kHz.

27

, Likewise, the ∆Phase term is

This requires the SIN ROM to have two bits of phase resolution

more than the 9-bit DAC.

DIGITAL-TO-ANALOG CONVERTER & OUTPUT GAIN STAGE

The DDS includes a high impedance current source 9-bit DAC.

The output from the DAC is a current (0 − 2 ma, this is ratiometric with the supply voltage), so in order to develop a current

the output current is passed through a precision grounded load

resistor such that the output will be a sinusoid voltage. This

voltage is subsequently delivered to an inverting gain stage gain

stage as shown in Figure 37. The output voltage amplitude from

the DAC may be set to a value of 2 V p-p, 1 V p-p, 400 mV p-p

or 200mv p-p depending upon the state of switches on the

feedback path of the amplifier. Only one switch will be closed at

any time. The output voltage amplitude can be programmed by

setting bits D10 and D9 in the control register. (See control

register section for further details).The output bias voltage of

the excitation voltage will also vary depending upon the value

of the excitation voltage amplitude set by the user as is

summarized in Table 7. The DC bias level is ratio metric with

respect to the supply voltage to the AD5934

Figure 36.

SIN ROM

To make the output from the NCO useful, it must be converted

from phase information into a sinusoidal value. Since phase

information maps directly into amplitude, the SIN ROM uses

the digital phase information as an address to a look-up table,

and converts the phase information into amplitude. Although

the NCO contains a 27-bit phase accumulator, the output of the

NCO is truncated to 12 bits. Using the full resolution of the

phase accumulator is impractical and unnecessary as this would

require a look-up table of 2

sufficient phase resolution such that the errors due to

truncation are smaller than the resolution of the 9-bit DAC.

27

entries. It is necessary only to have

Rev. PrB | Page 20 of 48

Figure 37.

Table 7.

Output Excitation Voltage

Amplitude Output DC Bias Level

2vp-p 1.6 V (vdd/2)

1vp-p 0.8 V (vdd/4)

400mv p-p 0.32 V (vdd/10)

200mv p-p 0.16 V (vdd/20)

RESPONSE STAGE

The diagram in Figure 38 shows the input stage to pin VOUT.

Current from the external sensor/unknown impedance/ load

flows through the VOUT pin and into a trans-impedance

amplifier which has a user determined external resistor across

its feedback path. The feedback resistor is connected between

pin 4 and pin 5. The user needs to choose a precision resistor in

the feedback loop such that the dynamic range of the ADC is

used and that the response signal resides within the linear range

of the ADC whilst ensuring the gain factor variation over the

impedance and frequency range of interest is minimized. The

Preliminary Technical Data AD5934

positive node of the Trans-impedance amplifier and gain

amplifier are biased at a fixed value of VDD/2. The output of

the Trans-impedance amplifier can then be gained by either 1

or 5, and is fed directly into the input of the ADC. The value of

this pre-ADC gain is determined by the status of bit D8 in the

control register.

Figure 38.

ADC OPERATION

The AD5934 has an integrated on board 12 bit ADC. The ADC

contains an on-chip track and hold amplifier, a successive

approximation A/D converter. Clocking for the A/D is provided

using a divided down ratio of the reference clock.

The A/D is a successive approximation analog to digital

converter, based on a Capacitive DAC design Architecture.

Figure 39 shows a simplified schematics of the ADC. The ADC

is comprised of control logic, a SAR, and a capacitive DAC, all

of which are used to add and subtract fixed amounts of charge

from the Sampling capacitor to bring the comparator back into

a balanced condition. Figure 39 shows the ADC during its

acquisition phase. SW2 is closed and SW1 is in position A, the

comparator is held in a balanced condition, and the sampling

capacitor acquires the signal on ADC input pin.

comparator to become unbalanced. The control logic and the

capacitive DAC are used to add and subtract fixed amounts of

charge from the sampling capacitor to bring the comparator

back into a balanced condition. When the comparator is

rebalanced, the conversion is complete. The control logic

generates the ADC output code.

Figure 40.

The start conversion (CS ) for the ADC is controlled via an

internal gated signal which provides the delay from the start of

the excitation signal to the time from which the ADC starts

converting the response signal. The gate enable signal is

determined by the status of the reset bit, update frequency bit

start frequency sweep bit of the control register (80h, 81h).The

delay between the time the DDS core outputs the current

excitation signal and the time the ADC starts converting the

response signal is determined by the value programmed into

the “settling time cycles” register and the inherent

multiplication factor which maybe performed on this register

contents (see ram location 8Ah, 8Bh). The data from the ADC

is directly made available to a window coefficient generator

prior to being passed to the DSP core of the AD5934 which

performs a dft on this windowed sampled data.

Figure 39.

When the ADC starts a conversion, SW2 will open and SW1

will move to position B, as shown in Figure 40, causing the

DFT CONVERSION

A discrete Fourier transform is calculated for each frequency

point in the sweep. The return signal is converted by the ADC,

windowed and then multiplied with a test phasor value to give a

real and imaginary output. This is repeated for 1024 sample

points of the input signal and the results of each multiplication

summed to give a final answer as a complex number. The

resultant answer at each frequency is two 16 bit words, the real

and imaginary data in complex form.

Rev. PrB | Page 21 of 48

AD5934 Preliminary Technical Data

Prior to performing a sweep the user will need to calibrate the

system in order to set the Correct output voltage excitation

value, external feedback resistor and pre-ADC voltage gain

setting in order to place the response signal in the linear range

of the ADC and more importantly such that GAIN FACTOR

returned by the setting is accurate. The user calculates this

GAIN FACTOR value from the real and imaginary components

returned from the device when the calibration impedance is

between Vin and Vout.

Figure 41.

The DFT algorithm is represented by

1023

()

∑

n

=

0

−=

))sin())(cos(()(

njnnxfX

Where X (f) is the frequency component corresponding to

windowed response sample x (n). The details of the dft

conversion are explained in detail in the section:AD5934:

theory of operation. Both the real and imaginary data register

have 15 bits of data and one sign bit. The 15 bits of data are in

twos compliment format. The magnitude of the response signal

after each conversion can be calculated by the real and

2

imaginary components returned through the I

22

IRMagnitude +=

C interface

factorGain

=

Z

NCALIBRATIO

22

IR

+

Where Z

CALIBRATION

is a known precision impedance (e.g.

precision resistor) value .R and I are the real and imaginary

components returned from the AD5934 which has been

previously calibrated to set the various gain, bias settings, and

external feedback value.

The real and imaginary components

are stored at location 94h to 97h (see register map)

The calibration impedance should be chosen such that the

known impedance lies within the middle of the unknown

impedance range. The calibration should be carried out at

frequency point which lies in the mid frequency band of

interest. The calibration should also be carried out at a

temperature which lies in the mid temperature range of interest.

The gain factor returned may be subsequently used to

recursively calibrate the system. The results returned by the

AD5934 may be improved upon by carrying out a two point

calibration. System calibration and the calculation of the gain

factor is explained in more detail in section: Gain factor

calculation, system calibration.

This magnitude which is must be calculated off chip is a scaled

valued of the actual impedance being measured between Vout

and Vin. The multiplication factor between the magnitude

returned and the actual impedance value is called the GAIN

FACTOR.

Rev. PrB | Page 22 of 48

Preliminary Technical Data AD5934

AD5934 THEORY OF OPERATION

Figure 42. AD5934 Block Overview

DDS CORE

The DDS allows for a 0.1 Hz resolution frequency output which

the user can program via a 24 bit word, loaded serially over the

2

C interface. The word loaded is the result of a simple formula

I

shown in equation 1, based on the master clock frequency and

the desired frequency output of the DDS.

)1(

Eqn

⎧

⎛

⎜

⎪

⎪

coderequired

⎜

=

⎨

⎜

⎪

⎜

⎪

⎝

⎩

⎛

⎜

⎝

Mclk

4

FrequencyOutputDDS

⎞

⎟

⎠

⎫

⎞

⎟

⎪

⎪

27

⎟

2

×

⎬

⎟

⎪

⎟

⎪

⎠

⎭

In addition the DDS provides both the sin and cosine

coefficients for the DFT operation. These coefficients are

applied to the Multiply/Accumulate (MAC) blocks on every

rising edge of the system clock. One of the generated sinusoids

is simultaneously converted into a voltage waveform by passing

the output of the phase accumulator core to a high impedance

output current DAC with a precision load resistor to ground on

the output.The output of the DDS/DAC is a current from 0 to

2 mA. This current is passed through a grounded precision

resistor such that maximum voltage by default is ±2 V peak to

peak. This voltage is applied to the VOUT pin. There is the

provision for dividing down this voltage as the application

requires. By writing to the control register, the user can set this

voltage applied to VOUT to be a divide by 10, 5 or 2 (200mV pp, 400mVp-p, 1Vp-p by setting bits D10, D9 of the control

register. The DC bias level changes on the output excitation

voltage will change according to the selected output amplitude

value programmed as shown in Figure 43.

Figure 43. Output Excitation Voltage Levels and Bias Values

The DDS can be programmed with a start frequency, a

frequency increment, a delay to allow a complex impedance

system to settle and the ability to repeat the same frequency

point multiple times (for example in the event of an interface

error).The complex impedance network to be excited by the

DDS output voltage is connected between VOUT (pin 6) and

VIN (Pin 5).

Rev. PrB | Page 23 of 48

AD5934 Preliminary Technical Data

ANALOG CHANNEL AND FILTER NETWORK

The output of the complex impedance network is applied to

VIN (pin 5).This is the input node to an Trans impedance

amplifier with a feedback resistance determined by the user

Rfb—thus the gain of this first amplifier is Rfb/Z(w), where

Z(w) is the value of the impedance under test, for example, if

the value of Rfb

is chosen to be 200 kΩ and the value of the

complex impedance at a given frequency say 100 kHz is 1MΩ,

then this first amplification stage would be an attenuation of

0.2. The second stage of amplification can be either a gain of 1

or a gain of 5. The gain of 5 would correct the above mentioned

attenuation, the gain of one is necessary when large impedances

between Vout and Vin are to be measured, as the signal into the

ADC has to be controlled so as not to go outside its dynamic

range. The gain of 5 and gain of 1 is user programmed via bit

D8 of the control register. After the gain stage the signal is

buffered and has to settle a pre ADC sampling cap (~12p) to

12 bits within 180 ns) and filtered before it is applied to the

12-bit SAR ADC. Filter poles have been designed into the

channel to roll of noise. In addition to this, the subsequent DFT

operation narrows bands noise to −3 dB at freq ±1 kHz (2 kHz

noise band width) around the DDS output drive frequency, due

to an integrated hanning window function (see dft and

windowing).

THE ANALOG-TO-DIGITAL CONVERTER

The function of the ADC is to implement the digitization of the

return signal from the complex network for use with DFT. The

ADC samples the return signal at 1 MHz, and provides the

samples to the digital engine. The details of the ADC are

explained in the section: system architecture description.

THE DISCRETE FOURIER TRANSFORM

The AD5934 method of determining the amplitude of the

sensor/impedance network signal involves the use of the DFT.

The DFT is a purely digital approximation of the Continuous

Fourier Transform. It takes a number N, of samples from a time

domain signal (the sine-wave in this case x(t)) and returns the

spectral content of that signal as a complex number R + jI.

These complex numbers describe the x (t). The DFT offers

excellent dc rejection, an averaging of errors and provides the

phase information. The AD5934 implemented DFT assumes

that a sequence of periodic data samples x(n) of which we wish

to determine the spectral content of the original continuous

excitation signal on Vout. These samples come from the 12-bit

ADC which has the complex impedance/sensor signal as its

input, for a range of signal-frequency values. The method

employed differs from the conventional DFT, in that only a

single frequency bin is transformed, rather than a fundamental

and its harmonics—it’s a single-point DFT.

With the conventional DFT, a sequence of input samples is

correlated with samples from a phasor. The frequency of this

phasor is at integer multiples of a fundamental frequency given

by fs/N. The correlation is performed for each frequency

multiple, if the resulting correlation of the phasor (consisting of

both a sine and a cosine at that multiple frequency) is non-zero,

then we can deduce that there is energy in the input signal at

that particular frequency bin. (Dividing the frequency axis into

n, equally spaced analysis phasor-bins is common in DFT

analysis). If no energy is found in a bin then there can be no

energy at that test frequency. With the single-point DFT the

analysis frequency is always the same as the input frequency (by

design), we are only looking for energy at one particular

frequency. So we only perform the DFT for one frequency bin,

which is fixed for the particular input frequency.

For example, if the complex impedance is excited with a 27 kHz

sinusoid, then the output of the complex impedance is sampled

and quantized. The resulting sample values are then used as the

input values to the DFT, which uses an analysis frequency (from

the DDS) also at 27K HZ. What this effectively does is correlate

the output voltage samples with the test phasor. For a coherent

system this will give us back exactly the correct answer in the

form of a single complex number (R + jI).

In rectangular or trigonometric form, the DFT has the form

shown in Equation 1.

)2(

−

1

N

⎛

nxmX

=

∑

⎜

⎝

=

0

n

mn

2

π

cos()()(

N

2

j

sin()

−

Eqn

mn

π

⎞

)

⎟

N

⎠

where:

th

X(m) is the m

DFT output, corresponding to the complex

output for that input sample.

m is the index of the DFT outputs component in the frequency

domain.

n is the time-domain index of the input samples—both n, m

0,1,2...N-1

N is the number of samples in the input sequence that will be

transformed to the frequency domain, and the number of

frequency points in the DFT output.

x(n) is the discrete sequence of time-domain sampled values of

the continuous waveform. (The ADC output in this

application),The number of points taken for the DFT, that is,

the DFT length N is an important number, it determines both

the accuracy of the final result and the complexity of the

circuitry required to calculate the results.

To highlight the dft with an example, assume the following

values.

• Sampling Frequency = 1 MHz = Fs

• N = 1024

• Input Signal = A sin (2πft+Ø)

• A = 1, f = 27k to 32k, t = 1/Fs, Ø = 0

Rev. PrB | Page 24 of 48

Preliminary Technical Data AD5934

N

The conventional DFT returns the spectral content at discrete

frequency bins given by Fs/N = roughly every 1 kHz in this

case. For N input (time-domain) samples the DFT will return N

frequency-domain results in complex - or rectangular form, a

real and an imaginary component. The simplified sequence of

events that results in a DFT is as follows.

1.

DDS outputs a single frequency of amplitude A and phase

Ø .

2.

For each value output from the DDS (A sin (2fπn/N)),

where n = 0 … N-1, the DDS also passes the cos and sin of

this value to the DFT multiply and Accumulator block

(MAC).

3.

The MACs (one for both the sin and cos) will multiply the

values passed by the DDS with the sampled values returned

from the sensor/network (which has been multiplied with

a hanning window function—see below for further details)

4.

This is repeated for N samples.

5.

After N cycles the values in the MACs contain the digital

equivalent of the real (cos*x(t)) and imaginary (sin*x(t)),

DFT output values. This is essentially a correlation of the

response signal with the current DDS output waveform.

6.

These values are transmitted to the off-chip by the user to a

microcontroller where the real and imaginary components

are conditioned into an impedance of the sensor/

impedance network for that particular frequency.

7.

The process is repeated for point along the frequency

sweep range conditions programmed into the AD5934

RAM (see section on AD5934 registers for further details)

Subsequently the microcontroller will process the data returned

from AD5934 for each sweep point to extract the Impedance.

AD5934 DISCRETE FOURIER TRANSFORM LEAKAGE

Leakage causes the DFT results to be only an approximation of

the true spectra of the original input signal. DFTs are

constrained to operate on a finite set of N input values sampled

at a sample rate of Fs, to produce an N-point transform whose

discrete outputs are associated with the individual analytical

frequencies, that are integer multiples of (m*Fs)/N. The

problem is that the DFT only produces correct results when the

input data sequence contains energy precisely at the analysis

frequencies that are integral multiples of the fundamental

frequency. If the input signal has a component at some

intermediate frequency between these frequency bins, this input

signal will show up to some degree in all of the N output

frequency bins of the DFT. In a conventional DFT this can have

the undesirable effect of masking out weaker signals that are

present close to stronger ones in the input signal.

Leakage is caused by the discontinuities caused by the DFT

assuming a periodic input signal. If the input signal does not

have an exact integral number of cycles over the N-point sample

interval then we will not have a smooth transition from the end

of one period to the start of the next. Firstly the very fact that a

finite number of points have been sampled to form the DFT, we

are in effect multiplying the input sequence by a rectangular

window of an assumed infinite signal in the time domain. The

CFT of a rectangular function is the sinc function (which we

approximate with the DFT), and if the input signal contains

components at exactly integer multiples of the fundamental

analysis frequency, then these side lobes will be zero at bin

frequencies and will not show up in the DFT output. If however,

the input signal contains components that do not fall exactly on

these bin frequencies, then the sinc functions side lobes will

contain energy at the bin frequencies. It is the high-frequency

components inherent in the discontinuities of non-periodic

sampling that causes these side lobes to exist.

In the single-point DFT that the AD5934 is concerned with, the

sampling frequency for this is set at 1 MHz, and N =1024. This

gives bin frequencies at integer multiples of ~1 kHz. So if we

wanted accurate DFT outputs, the input signal would be

restricted to 1 kHz multiples – the resolution of the DFT is said

to be 1 kHz, i.e., the DFT will only give the correct results for

these frequencies locations. Because for the AD5934 the input

signal can take on any value, the leakage effects must be

considered

The most popular method for reducing the effects of spectral

leakage is windowing. Windowing has the effect of reducing the

energy contained in the side lobes of the sinc function. When

the input signal does not contain an integer number of cycles

within the sample interval we will have leakage as described

above. AD5934 Applications may have the additional problem

of a non-periodic analysis frequency. A conventional DFT is

performed with analysis phasors that are multiples of the

fundamental bin frequency given by Fs/N. Because the AD5934

is only performing a single-point DFTs, this is no longer the

case. The analysis phasors are not periodic between binfrequencies. In addition we also end up with cosine and sine

squared function when building up the DFT results. The result

of this is the unusual ripple that is seen on the output values

between bin frequencies. Windowing will reduce these effects

considerably.

The AD5934 uses the Hanning window to achieve the system

accuracy The Hanning window equation is an inverted, raised

cosine of half-unit amplitude peak to peak as shown in Equation 3.

...2

nf

1

)(

Where f = the sampling interval and, n = 0…N-1, and N = DFT

length.

×−=

212

π

(

CosnHanning

)3.(

Eqn

)

Rev. PrB | Page 25 of 48

AD5934 Preliminary Technical Data

The Hanning window offers good side lobe rejection and due to

its symmetrical properties is efficient to implement in a digital

engine. The window function will reduce the discontinuities at

the end of the sampling interval period and the start of the next

period (in the time domain), and forces the input time sequence

at both the beginning and end of the sample interval to go

smoothly towards a single common amplitude value. As the

output of the DFT is periodic, the periods will line up better,

with less of a transition from the last sample value to the first

sample of the next period resulting in less energy in the side

lobes of the sinc function.

Hanning Windows also have the effect of reducing the timedomain signal levels applied to the DFT; as such the main lobe

peak values are reduced (−13 dB) relative to the unwindowed

input data sequence. This leads to a predictable processing loss

that must be accounted for (with a multiplier value) when

computing the windowed DFT output values. Windowing in

the conventional sense will also widen the main lobe width,

reducing the resolution of the data, leakage effects are reduced,

but this doesn’t become a problem for AD5934 single-point

DFT.

The input data samples from the ADC are windowed, that is,

they are multiplied by a set of coefficients that are calculated

from the window function on a point for point basis. The data

samples take on the tapered profile of the window. In hardware

terms this is performed in the digital engine (just a multiplier of

sufficient bit width). The actual DFT operation must then be

done – the windowed samples are point for point multiplied

with both the sin and cosine values from the DDS and a

multiply and accumulate operation is performed in the digital

engine to give us the DFT result.

)4(

1

N

−

()(){}

∑

0

n

=

Eqn

)()cos()()()(

nxnnxnSinfX

×+×=

For N values where N=1024.

The above general equation outlines what is done on each data

sample where f is the test frequency.

Rev. PrB | Page 26 of 48

Preliminary Technical Data AD5934

e

GAIN FACTOR CALCULATION

The AD5934 device is capable of measuring impedances values

to within 1% for impedances which lie within the range of 100Ω

to 10MΩ.The DFT of the response signal from the unknown

impedance will return both a 16 bit twos complement real and

an imaginary word for each frequency point on the sweep. Each

of the data components is stored in a single 16 bit register

location (see register map).The user must read these values to

an off chip microprocessor/DSP through the I

order to calculate the impedance value at each point. The user

must poll the status register to see when there is valid data

available to read and finally to check if the entire frequency

sweep has been completed. Once valid data has become

available the user must read the current contents of the real and

imaginary data register before the next frequency sweep point

has updated the current contents with new valid data.

The magnitude of the real and the imaginary data contents each

frequency point is given by the following

22

)( IRfMagnitude +=

Where R and I correspond to the real and imaginary code

returned for the current sweep point.

This magnitude value is equal to a scaled value of the actual

impedance under test at the frequency point f. In order to

determine actual impedance value the user must multiply the

magnitude by a Gain Factor GF(freq, Vdd, temp).There fore the

actual impedance any sample instant is given by the following

2

C interface in

of the code returned by the DFT at a single frequency chosen

and by the user. This constitutes a single point gain factor

calibration. The Gain Factor is measured at a particular

frequency in the mid range of the frequency of interest. The

calibration impedance should be chosen by the user to lie in the

middle of the unknown impedance range and also in the

middle of the temperature range of interest. The gain factor

essentially is a number representing the accumulative gain

through the signal path of the system for know measured

calibration impedance and for a specified value of output

voltage excitation value and frequency/pre ADC gain setting

and feedback resistor chosen by the user. Therefore the Gain

factor will depend upon the frequency point at which it is

calculated, the AD5934 supply voltage, as the output bias level is