Dual-Current Output, Parallel Input, 16-Bit

V

V

Multiplying DAC with 4-Quadrant Resistors

Data Sheet

FEATURES

Dual channel

16-bit resolution: AD5547-EP

2- or 4-quadrant, 6.8 MHz bandwidth multiplying DAC

±1 LSB DNL

±2 LSB INL

Operating supply voltage: 2.7 V to 5.5 V

Low noise: 12 nV/√Hz

Low power: I

0.5 μs settling time

Built-in R

Built-in 4-quadrant resistors allow 0 V to –10 V, 0 V to +10 V,

or ±10 V outputs

2 mA full-scale current ± 20%, with V

Extended automotive operating temperature range

−55°C to +125°C

Selectable zero-scale/midscale power-on presets

Compact 38-lead TSSOP package

ENHANCED PRODUCT FEATURES

Supports defense and aerospace applications (AQEC

standard)

Military temperature range (such as −55°C to +125°C).

Controlled manufacturing baseline

One assembly/test site

One fabrication site

Enhanced product change notification

Qualification data available on request

APPLICATIONS

Automatic test equipment

Instrumentation

Digitally controlled calibration

Digital waveform generation

= 10 μA maximum

DD

facilitates current-to-voltage conversion

FB

= 10 V

REF

REF

U1

–VREF

AD5547-EP

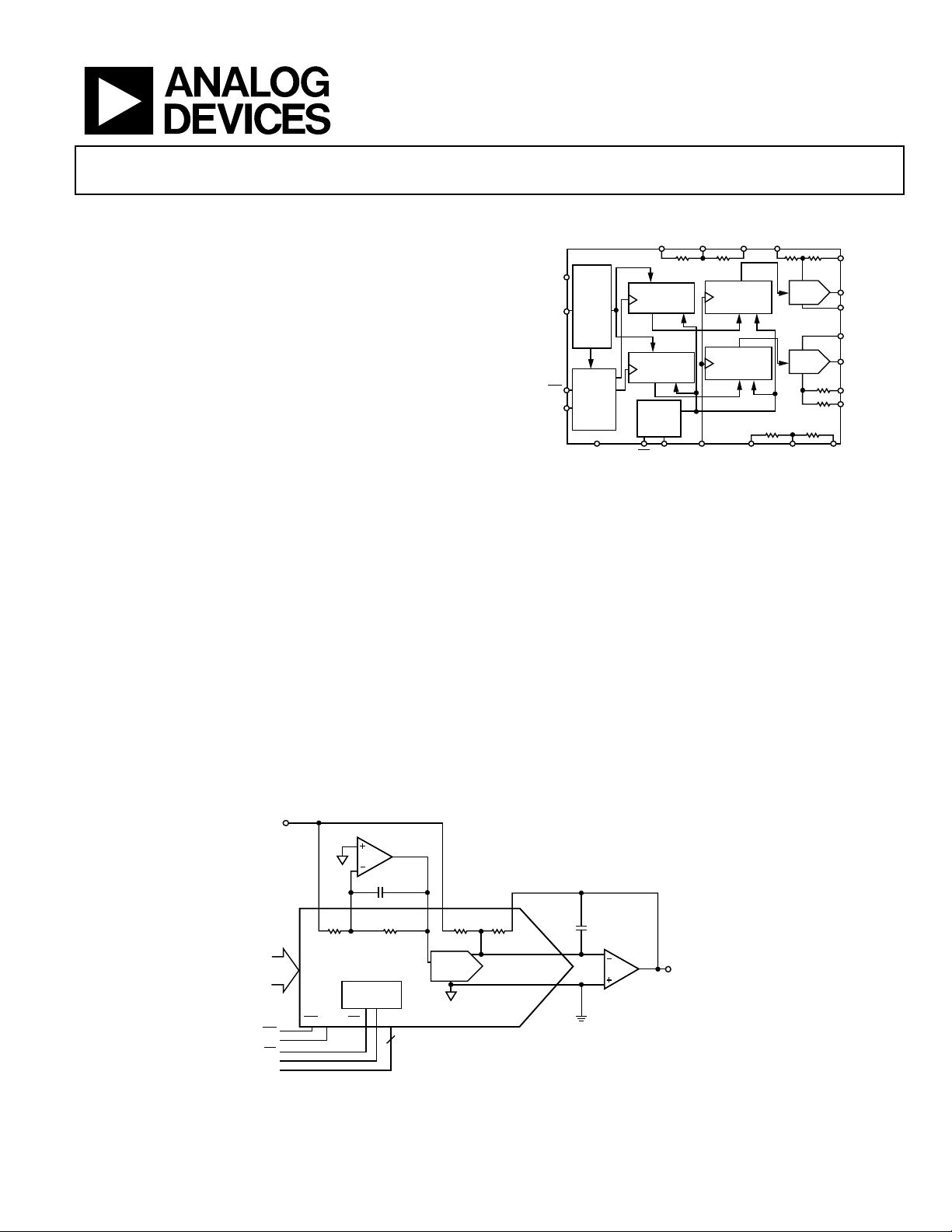

FUNCTIONAL BLOCK DIAGRAM

R

R

COMA

1A

V

D0 TO D15

WR

A0, A1

DD

D0 TO

D15

DAC A

DAC B

ADDR

DECODE

INPUT

REGISTER

INPUT

REGISTER

POWER

ON

RESET

MSB LDACDGND

RS

REGISTER

RS

REGISTER

RS

Figure 1.

GENERAL DESCRIPTION

The AD5547-EP is a dual precision, 16-bit, multiplying, low power,

current-output, parallel input, digital-to-analog converter (DAC). It

is designed to operate from a single +5 V supply with ±10 V

multiplying references for 4-quadrant outputs with a 6.8 MHz

bandwidth.

The built-in, 4-quadrant resistors facilitate resistance matching

and temperature tracking, which minimize the number of

components needed for multiquadrant applications. In addition,

the feedback resistor (R

an external buffer.

The AD5547-EP is available in a compact, 38-lead TSSOP

package and operates at the extended automotive temperature

range of −55°C to +125°C. Additional application and technical

information can be found in the AD5547 data sheet.

) simplifies the I-to-V conversion with

FB

R

OFSA

REFA

DAC A

RS

DAC B

RS

AD5547-EP

R

1B

R

DAC A

DAC B

COMB

V

REFB

R

FBA

I

OUTA

AGNDA

AGNDB

I

OUTB

R

FBB

R

OFSB

10108-013

C1

R

R

1A

R1 R2

16-BIT DATA

WR

LDAC

RS

MSB

A0, A1

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

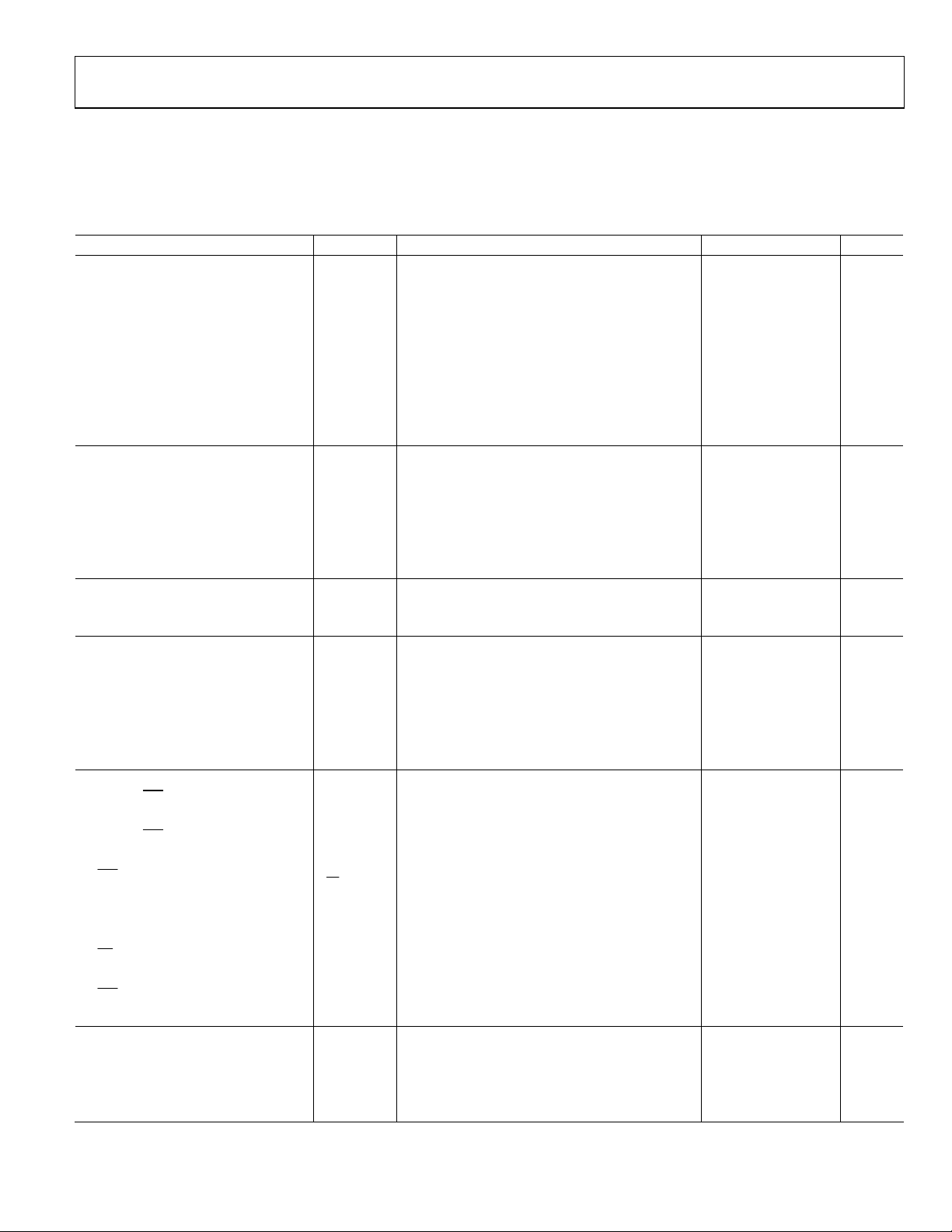

Figure 2. 16-Bit 4-Quadrant Multiplying DAC with Minimum of External Components (Only One Channel Is Shown)

AD5547-EP

POWER-ON

WR RSLDAC

COMA

RESET

V

MSB A0,A1

2

R

REFA

OFSARFBA

RFBROFS

16-BIT

DAC A

(ONE CHANNEL SHOWN O NLY)

C2

IOUTA

AGNDA

U2

VOUTA

–VREF TO +VREF

10108-002

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

AD5547-EP Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Enhanced Product Features ............................................................ 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

REVISION HISTORY

9/11—Revision 0: Initial Version

Electrical Characteristics..............................................................3

Absolute Maximum Ratings ............................................................5

ESD Caution...................................................................................5

Pin Configuration and Function Descriptions..............................6

Typical Performance Characteristics..............................................8

Outline Dimensions....................................................................... 10

Ordering Guide .......................................................................... 10

Rev. 0 | Page 2 of 12

Data Sheet AD5547-EP

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VDD = 2.7 V to 5.5 V, I

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

STATIC PERFORMANCE1

Resolution N 1 LSB = V

Relative Accuracy INL ±2 LSB

Differential Nonlinearity DNL Monotonic ±1 LSB

Output Leakage Current I

Data = zero scale, TA = TA maximum 20 nA

Full-Scale Gain Error G

Bipolar Mode Gain Error GE Data = full scale ±1 ±5 mV

Bipolar Mode Zero-Scale Error G

Full-Scale Temperature Coefficient2 TCVFS 1 ppm/°C

REFERENCE INPUT

V

Range V

REF

REF Input Resistance REF 4 5 6 kΩ

R1 and R2 Resistance R1 and R2 4 5 6 kΩ

R1-to-R2 Mismatch Δ(R1 to R2) ±0.5 ±1.5 Ω

Feedback and Offset Resistance RFB, R

Input Capacitance2 C

ANALOG OUTPUT

Output Current I

Output Capacitance2 C

LOGIC INPUT AND OUTPUT

Logic Input Low Voltage VIL V

V

Logic Input High Voltage VIH V

V

Input Leakage Current IIL 10 μA

Input Capacitance2 C

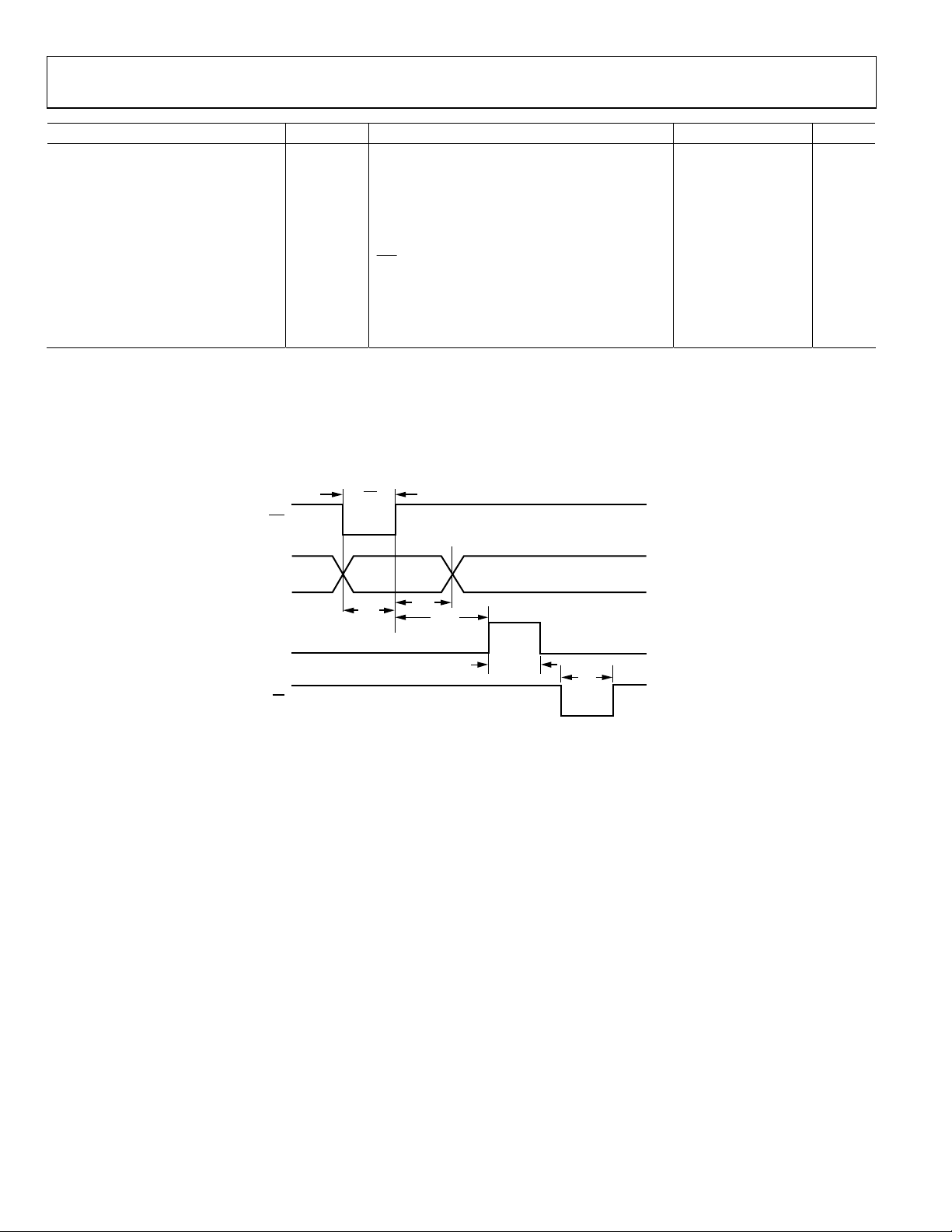

INTERFACE TIMING

Data to WR Setup Time

V

Data to WR Hold Time

V

WR Pulse Width

V

LDAC Pulse Width t

V

RS Pulse Width

V

WR to LDAC Delay Time

V

SUPPLY CHARACTERISTICS

Power Supply Range V

Positive Supply Current IDD Logic inputs = 0 V 10 μA

Power Dissipation P

Power Supply Sensitivity

= virtual GND, GND = 0 V, V

OUT

Data = zero scale, TA = 25°C 10 nA

OUT

Data = full scale ±1 ±5 mV

FSE

Data = full scale ±1 ±4 mV

ZSE

−18 +18 V

REF

8 10 12 kΩ

OFS

5 pF

REF

Data = full scale 2 mA

OUT

Code dependent 200 pF

OUT

10 pF

2, 3

See Figure 3

IL

t

V

DS

t

V

DH

t

V

WR

V

LDAC

t

V

RS

t

V

LWD

2.7 5.5 V

DD RANGE

Logic inputs = 0 V 0.055 mW

DISS

P

∆VDD = ±5% 0.003 %/%

SS

= −10 V to +10 V, TA = −55°C to +125°C, unless otherwise noted.

REF

/216 = 153 μV at V

REF

= 5 V 0.8 V

DD

= 3 V 0.4 V

DD

= 5 V 2.4 V

DD

= 3 V 2.1 V

DD

= 5 V 20 ns

DD

= 3 V 35 ns

DD

= 5 V 0 ns

DD

= 3 V 0 ns

DD

= 5 V 20 ns

DD

= 3 V 35 ns

DD

= 5 V 20 ns

DD

= 3 V 35 ns

DD

= 5 V 20 ns

DD

= 3 V 35 ns

DD

= 5 V 0 ns

DD

= 3 V 0 ns

DD

= 10 V 16 Bits

REF

Rev. 0 | Page 3 of 12

AD5547-EP Data Sheet

C

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

AC CHARACTERISTICS4

Output Voltage Settling Time tS

To ±0.1% of full scale, data cycles from zero scale

to full scale to zero scale

Reference Multiplying Bandwidth BW V

DAC Glitch Impulse Q V

Multiplying Feedthrough Error V

OUT/VREF

V

Digital Feedthrough QD

Total Harmonic Distortion THD V

= 100 mV rms, data = full scale 6.8 MHz

REF

= 0 V, midscale – 1 to midscale −3.5 nV-s

REF

= 100 mV rms, f = 10 kHz −78 dB

REF

= 1, LDAC toggles at 1 MHz

WR

= 5 V p-p, data = full scale, f = 1 kHz −104 dB

REF

Output Noise Density eN f = 1 kHz, BW = 1 Hz 12 nV/√Hz

Analog Crosstalk CAT

Signal input at Channel A and measures the

output at Channel B, f = 1 kHz

1

All static performance tests (except I

tied to the amplifier output. The +IN pin of the OP97 is grounded, and the I

measured at 25°C.

2

Guaranteed by design; not subject to production testing.

3

All input control signals are specified with tR = tF = 2.5 ns (10% to 90% of 3 V) and are timed from a voltage level of 1.5 V.

4

All ac characteristic tests are performed in a closed-loop system using an AD8038 I-to-V converter amplifier except for THD where the AD8065 was used.

) are performed in a closed-loop system using an external precision OP97 I-to-V converter amplifier. The device RFB terminal is

OUT

of the DAC is tied to the OP97’s −IN pin. Typical values represent average readings

OUT

Timing Diagram

t

WR

WR

0.5 μs

7 nV-s

−95 dB

DATA

t

DH

t

LWD

t

LDAC

t

RS

10108-018

LDA

RS

t

DS

Figure 3. AD5547-EP Timing Diagram

Rev. 0 | Page 4 of 12

Data Sheet AD5547-EP

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

VDD to GND –0.3 V to +8 V

RFB, R

OFS

, R1, R

, and VREF to GND –18 V to +18 V

COM

Logic Inputs to GND –0.3 V to +8 V

V(I

) to GND –0.3 V to VDD + 0.3 V

OUT

Input Current to Any Pin except Supplies ±50 mA

Thermal Resistance (θJA)1

Maximum Junction Temperature (TJ

) 150°C

MAX

Operating Temperature Range −55°C to +125°C

Storage Temperature Range −65°C to +150°C

Lead Temperature

Vapor Phase, 60 sec 215°C

Infrared, 15 sec 220°C

1

Package power dissipation = (T

J MAX

− TA)/θJA.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 5 of 12

AD5547-EP Data Sheet

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 3. Pin Function Descriptions

Pin No. Mnemonic Description

1, 2, 24 to

D0 to D15 Digital Input Data Bits D0 to D15. Signal level must be ≤ V

28, 30 to

38

3 R

4 R

5 R1A

OFSA

Internal Matching Feedback Resistor A. Connects to the external op amp for I-to-V conversion.

FBA

Bipolar Offset Resistor A. Accepts up to ±18 V. In 2-quadrant mode, R

ties to R

and the external reference.

1A

4-Quandrant Resistor. In 2-quadrant mode, R

not connect when operating in unipolar mode.

6 R

COMA

Center Tap Point of the Two 4-Quadrant Resistors, R

node of the reference amplifier. In 2-quadrant mode, R

operating in unipolar mode.

7 V

REFA

DAC A Reference Input in 2-Quadrant Mode, R2 Terminal in 4-Quadrant Mode. In 2-quadrant mode, V

reference input with constant input resistance vs. code. In 4-quadrant mode, V

reference amplifier.

8 I

DAC A Current Output. Connects to the inverting terminal of external precision I-to-V op amp for voltage output.

OUTA

9 AGNDA DAC A Analog Ground.

10 DGND Digital Ground.

11 AGNDB DAC B Analog Ground.

12 I

13 V

DAC B Current Output. Connects to inverting terminal of external precision I-to-V op amp for voltage output.

OUTB

REFB

DAC B Reference Input Pin. Establishes DAC full-scale voltage. Constant input resistance vs. code. If configured

with an external op amp for 4-quadrant multiplying, V

14 R

COMB

Center Tap Point of the Two 4-Quadrant Resistors, R

node of the reference amplifier. In 2-quadrant mode, R

unipolar mode.

15 R1B

4-Quandrant Resistor. In 2-quadrant mode, R

connect if operating in unipolar mode.

16 R

17 R

18

Internal Matching Feedback Resistor B. Connects to external op amp for I-to-V conversion.

FBB

OFSB

Write Control Digital Input In, Active Low. WR transfers shift register data to the DAC register on the rising edge.

WR

Bipolar Offset Resistor B. Accepts up to ±18 V. In 2-quadrant mode, R

ties to R

and an external reference.

1B

Signal level must be ≤VDD + 0.3 V.

1

D1

D0

2

3

R

OFSA

4

R

FBA

5

R

1A

6

R

COMA

7

V

REFA

8

I

OUTA

AGNDA

DGND

AGNDA

I

OUTB

V

REFB

R

COMB

R

R

OFSB

R

FBB

WR

A0

1B

AD5547-EP

9

10

(Not to Scale)

11

12

13

14

15

16

17

18

19

TOP VIEW

Figure 4. Pin Configuration

Rev. 0 | Page 6 of 12

38

D2

D3

37

D4

36

35

D5

D6

34

D7

33

32

D8

D9

31

D10

30

29

VDD

D11

28

D12

27

26

D13

D14

25

D15

24

23

RS

MSB

22

LDAC

21

20

A1

shorts to the V

1A

and R2A. In 4-quadrant mode, R

1A

COMA

REFB

and R2B. In 4-quadrant mode, R

1B

COMB

shorts to the V

1B

10108-003

+ 0.3 V.

DD

ties to R

OFSA

pin. In 4-quadrant mode, R1A ties to R

REFA

shorts to the associated V

becomes –V

shorts to the V

REFB

.

REF

REFB

pin. In 4-quadrant mode, R1B ties to R

ties to R

OFSB

. In 4-quadrant mode, R

FBA

COMA

REFA

is driven by the external

REFA

COMB

pin. Do not connect if operating in

. In 4-quadrant mode, R

FBB

OFSA

. Do

OFSA

ties to the inverting

pin. Do not connect if

is the

REFA

ties to the inverting

. Do not

OFSB

OFSB

Data Sheet AD5547-EP

Pin No. Mnemonic Description

19 A0 Address Pin 0. Signal level must be ≤VDD + 0.3 V.

20 A1 Address Pin 1. Signal level must be ≤VDD + 0.3 V.

21 LDAC Digital Input Load DAC Control. Signal level must be ≤VDD + 0.3 V.

22 MSB

23

29 VDD Positive Power Supply Input. The specified range of operation is 2.7 V to 5.5 V.

Active low resets both input and DAC registers. Resets to zero-scale if MSB = 0 and resets to midscale if MSB = 1.

RS

Table 4. Address Decoder Pins

A1 A0 Output Update

0 0 DAC A

0 1 None

1 0 DAC A and DAC B

1 1 DAC B

Table 5. Control Inputs

RS

0 X X Reset the output to 0 with MSB = 0; reset the output to midscale with MSB = 1.

1 0 0 Load the input register with data bits.

1 1 1 Load the DAC register with the contents of the input register.

1 0 1 The input and DAC registers are transparent.

1

1 1 0 No register operation.

LDAC Register Operation

WR

Power-On Reset State. MSB = 0 corresponds to zero-scale reset; MSB = 1 corresponds to midscale reset. The

signal level must be ≤V

Signal level must be ≤V

When LDAC and WR

on the falling edge of the pulse and are then loaded into the DAC register on the rising edge of the pulse.

are tied together and programmed as a pulse, the data bits are loaded into the input register

+ 0.3 V.

DD

+ 0.3 V.

DD

Rev. 0 | Page 7 of 12

AD5547-EP Data Sheet

TYPICAL PERFORMANCE CHARACTERISTICS

1.0

0.8

0.6

0.4

0.2

0

INL (LSB)

–0.2

–0.4

–0.6

–0.8

–1.0

0 8192 16,384 24,576 32,768 40,960 49,152 57,344 65,536

CODE (Decimal)

Figure 5. AD5547-EP Integral Nonlinearity Error

1.0

0.8

0.6

0.4

0.2

0

DNL (LSB)

–0.2

–0.4

–0.6

–0.8

–1.0

0 8192 16,384 24,576 32,768 40,960 49,152 57,344 65,536

CODE (Deci mal)

Figure 6. AD5547-EP Differential Nonlinearity Error

1.5

V

= 2.5 V

REF

T

= 25° C

A

1.0

0.5

INL

0

–0.5

LINEARITY E RROR (LSB)

–1.0

–1.5

24

SUPPLY VOLTAGE VDD (V)

DNL

GE

68

Figure 7. Linearity Error vs. Supply Voltage, V

DD

10108-019

10108-020

10

10108-022

5

V

= 5V

DD

= 25° C

T

A

4

(LSB)

DD

3

2

SUPPLY CURRENT I

1

0

0 0.5 1.0 1.5 2.0 3.0 3.52.5 4.0 4.5 5.0

LOGIC INPUT VOLTAGE VIH (V)

Figure 8. Supply Current vs. Logic Input Voltage

3.0

2.5

2.0

1.5

1.0

SUPPLY CURRENT (mA)

0.5

0

10k 100k 1M 10M 100M

CLOCK FREQ UENC Y ( Hz)

0x5555

0x8000

0xFFFF

0x0000

Figure 9. AD5547-EP Supply Current vs. Clock Frequency

90

V

= 5V ± 10%

80

70

60

50

40

PSRR (–dB)

30

20

10

0

10 100 1k 10k 100k 1M

FREQUENCY (Hz)

DD

= 10V

V

REF

Figure 10. Power Supply Rejection Ratio (PSRR) vs. Frequency

10108-023

10108-024

10108-014

Rev. 0 | Page 8 of 12

Data Sheet AD5547-EP

–

2

0

1

2

CH1 5.00V CH2 2.00V M 200ns A CH1 2.70V

B CH1 –6.20V

400.00ns

Figure 11. Settling Time from Full Scale to Zero Scale

3.85

–3.90

–3.95

–4.00

(V)

OUT

–4.05

V

LDAC

V

OUT

–2

–4

–6

–8

GAIN (dB)

–10

–12

–14

–16

10108-025

–18

10k 100M

100k 1M 10M

FREQUENCY (Hz)

10108-017

Figure 13. AD5547-EP Unipolar Reference Multiplying Bandwidth

–4.10

–4.15

–4.20

–20–100 10203040

TIME (ns)

Figure 12. AD5547-EP Midscale Transition and Digital Feedthrough

10108-016

Rev. 0 | Page 9 of 12

AD5547-EP Data Sheet

0

0

OUTLINE DIMENSIONS

9.80

9.70

9.60

SEATING

PLANE

20

4.50

4.40

4.30

6.40 BSC

191

1.20

MAX

8°

0.20

0.09

0°

0.70

0.60

0.45

38

PIN 1

.15

.05

COPLANARITY

0.10

0.50

0.27

BSC

0.17

COMPLIANT TO JEDEC STANDARDS MO-153-BD-1

Figure 14. 38-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-38)

Dimension s shown in millimeters

ORDERING GUIDE

Model1 Resolution (Bits) DNL (LSB) INL (LSB) Temperature Range Package Description Package Option

AD5547SRU-EP 16 ±1 ±2 −55°C to +125°C 38-Lead TSSOP RU-38

1

Z = RoHS Compliant Part.

Rev. 0 | Page 10 of 12

Data Sheet AD5547-EP

NOTES

Rev. 0 | Page 11 of 12

AD5547-EP Data Sheet

NOTES

©2011 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D10108-0-9/11(0)

Rev. 0 | Page 12 of 12

Loading...

Loading...