8-Channel, 16-/14-Bit,

VDDV

FEATURES

8-channel DAC in 52-lead LQFP and 56-lead LFCSP packages

Guaranteed monotonic to 16/14 bits

Nominal output voltage range of −10 V to +10 V

Multiple output voltage spans available

Thermal shutdown function

Channel monitoring multiplexer

GPIO function

System calibration function allowing user-programmable

offset and gain

Channel grouping and addressing features

Data error checking feature

SPI-compatible serial interface

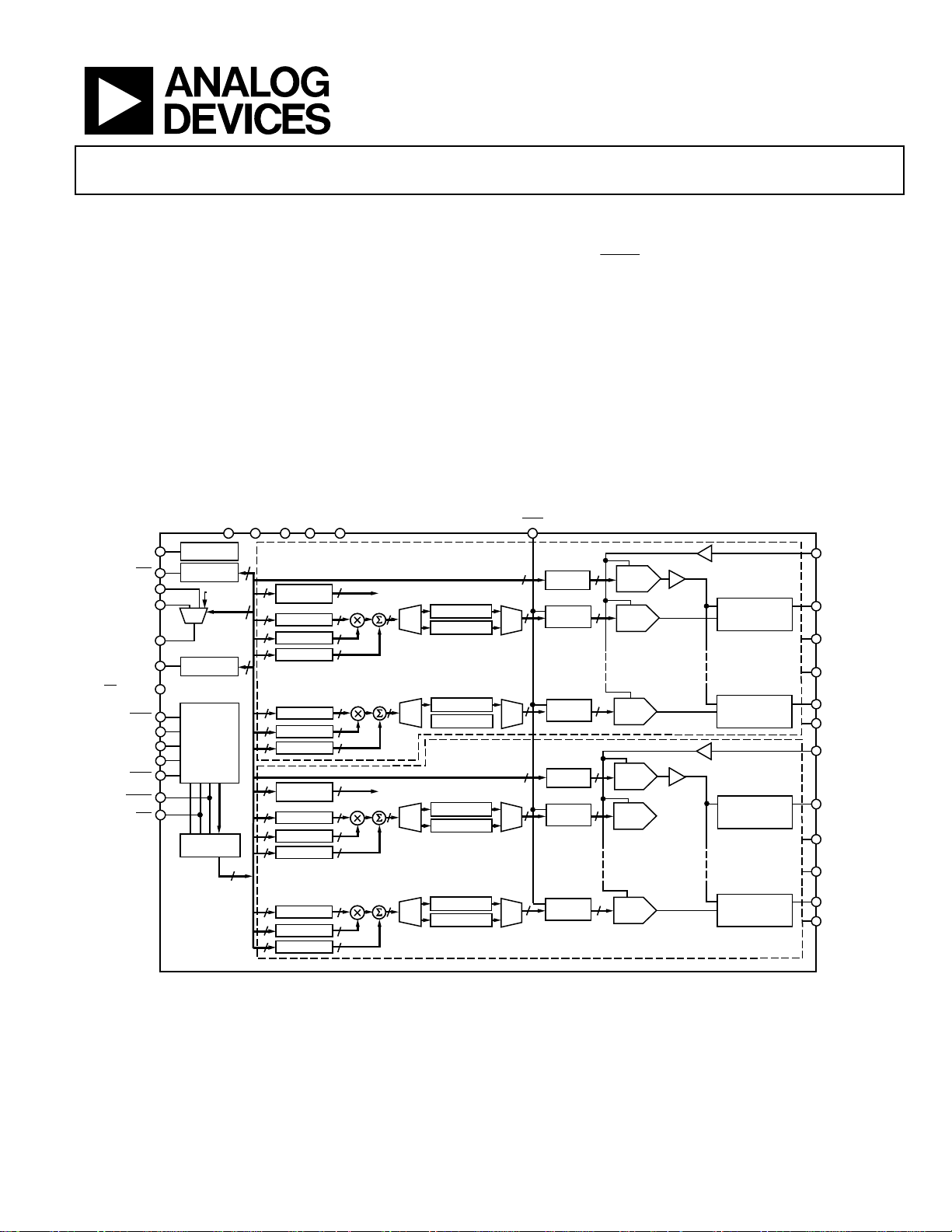

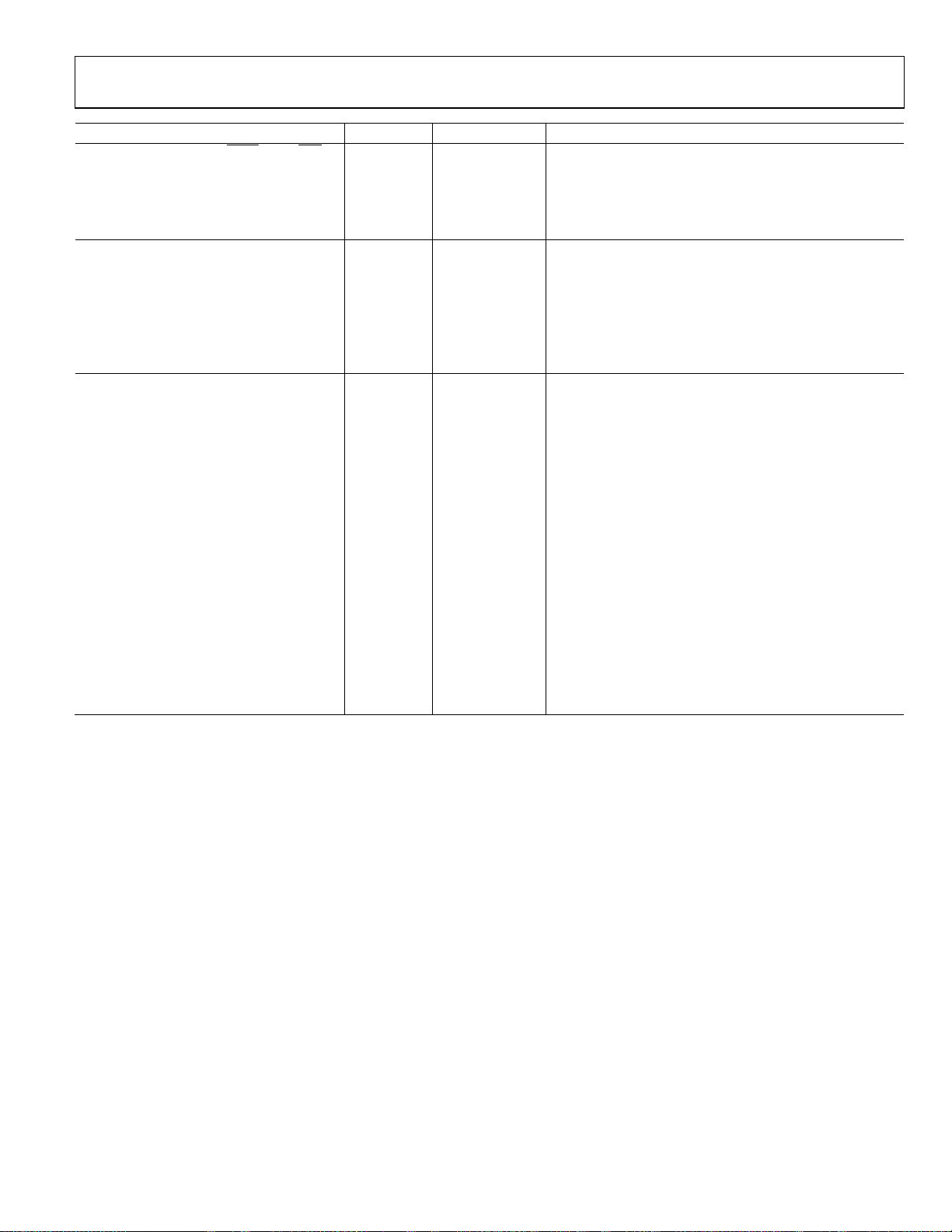

FUNCTIONAL BLOCK DIAGRAM

8

TO

MUX 2s

n

X2A REGISTER

n

n

n

n

n

n

8

n

n

n

n

n

n

A/B

MUX

X2B REGISTER

·

·

·

n

TO

MUX 2s

n

·

·

·

n

·

·

·

A/B

MUX

A/B

MUX

·

·

·

A/B

MUX

X2A REG ISTER

X2B REG ISTER

X2A REGISTER

X2B REGISTER

X2A REGISTER

X2B REGISTER

·

·

·

·

·

·

TEMP_OUT

PEC

MON_IN0

MON_IN1

MON_OUT

GPIO

BIN/2S COMP

SYNC

SDI

SCLK

SDO

BUSY

RESET

CLR

DV

TEMP

SENSOR

CONTROL

REGISTER

VOUT0 TO

VOUT7

MUX

GPIO

REGISTER

SERIAL

INTERFACE

STATE

MACHINE

AD5362/

AD5363

CC

8

6

2

n

AGND DGND LDAC

SS

n = 16 FOR AD5362

n = 14 FOR AD5363

8

A/B SELECT

REGI STER

n

X1 REGI STER

n

M REGI STER

n

C REG ISTER

·

·

·

n

X1 REGI STER

n

M REGISTER

n

C REG ISTER

8

A/B SELECT

REGI STER

n

X1 REGI STER

n

M REGI STER

n

C REG ISTER

·

·

·

n

X1 REGI STER

n

M REGI STER

n

C REG ISTER

Serial Input, Voltage Output DAC

AD5362/AD5363

2.5 V to 5.5 V digital interface

·

·

·

·

·

·

Figure 1.

Digital reset (

Clear function to user-defined SIGGNDx

Simultaneous update of DAC outputs

APPLICATIONS

Instrumentation

Industrial control systems

Level setting in automatic test equipment (ATE)

Variable optical attenuators (VOA)

Optical line cards

14

OFS0

REGI STER

nn

MUX

MUX

MUX

MUX

2

2

2

2

DAC 0

REGI STER

·

·

·

n

DAC 3

REGISTER

14

OFS1

REGISTER

nn

DAC 4

REGI STER

·

·

·

·

n

DAC 7

REGI STER

RESET

14

n

n

n

OFFSET

DAC 0

DAC 0

DAC 3

OFFSET

DAC 1

DAC 4

DAC 7

)

BUFFER

BUFFER

·

·

·

BUFFER

BUFFER

·

·

·

GROUP 0

OUTPUT B UFFER

AND POWER-

DOWN CONTROL

·

·

·

OUTPUT B UFFER

AND POWER-

DOWN CONTROL

GROUP 1

OUTPUT B UFFER

AND POWER-

DOWN CONTROL

·

·

·

OUTPUT B UFFER

AND POWER-

DOWN CONTROL

VREF0

VOUT0

VOUT1

VOUT2

VOUT3

SIGGND0

VREF1

VOUT4

VOUT5

VOUT6

VOUT7

SIGGND1

05762-001

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

AD5362/AD5363

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

General Description ......................................................................... 3

Specifications ..................................................................................... 4

AC Characteristics ........................................................................ 6

Timing Characteristics ................................................................ 7

Absolute Maximum Ratings .......................................................... 10

ESD Caution ................................................................................ 10

Pin Configuration and Function Descriptions ........................... 11

Typical Performance Characteristics ........................................... 13

Terminology .................................................................................... 15

Theory of Operation ...................................................................... 16

DAC Architecture ....................................................................... 16

Channel Groups .......................................................................... 16

A/B Registers and Gain/Offset Adjustment ............................ 17

Offset DACs ................................................................................ 17

Output Amplifier ........................................................................ 18

Transfer Function ....................................................................... 18

Reference Selection .................................................................... 18

Calibration ................................................................................... 19

Additional Calibration ............................................................... 19

Reset Function ............................................................................ 20

Clear Function ............................................................................ 20

BUSY

BIN

Temperature Sensor ................................................................... 20

Monitor Function ....................................................................... 21

GPIO Pin ..................................................................................... 21

Power-Down Mode .................................................................... 21

Thermal Shutdown Function ................................................... 21

Toggle Mode ................................................................................ 21

Serial Interface ................................................................................ 22

SPI Write Mode .......................................................................... 22

SPI Readback Mode ................................................................... 22

Register Update Rates ................................................................ 22

Packet Error Checking ............................................................... 23

Channel Addressing and Special Modes ................................. 23

Special Function Mode .............................................................. 24

Applications Information .............................................................. 26

Power Supply Decoupling ......................................................... 26

Power Supply Sequencing ......................................................... 26

Interfacing Examples ................................................................. 26

Outline Dimensions ....................................................................... 27

Ordering Guide .......................................................................... 28

LDAC

and

/2SCOMP Pin ...................................................................... 20

Functions...................................................... 20

REVISION HISTORY

3/08—Rev. 0 to Rev. A

Added 56-Lead LFCSP_VQ .............................................. Universal

Changes to Table 2 ............................................................................ 4

Added t

Changes to Figure 4 .......................................................................... 8

Changes to Table 6 .......................................................................... 11

Changes to A/B Registers and Gain/Offset Adjustment

Section .............................................................................................. 17

Parameter ......................................................................... 7

23

Rev. A | Page 2 of 28

Changes to Calibration Section .................................................... 19

Changes to Reset Function Section and

Functions Section ........................................................................... 20

Changes to Channel Addressing and Special Modes Section .. 23

Updated Outline Dimensions ....................................................... 27

Changes to Ordering Guide .......................................................... 28

1/08—Revision 0: Initial Version

BUSY

and

LDAC

AD5362/AD5363

GENERAL DESCRIPTION

The AD5362/AD5363 contain eight 16-/14-bit DACs in a single

52-lead LQFP package or 56-lead LFCSP package. The devices

provide buffered voltage outputs with a span of 4× the reference

voltage. The gain and offset of each DAC can be independently

trimmed to remove errors. For even greater flexibility, the device

is divided into two groups of four DACs, and the output range

of each group can be independently adjusted by an offset DAC.

The AD5362/AD5363 offer guaranteed operation over a wide

supply range with V

from −16.5 V to −4.5 V and VDD from 8 V

SS

to 16.5 V. The output amplifier headroom requirement is 1.4 V,

operating with a load current of 1 mA.

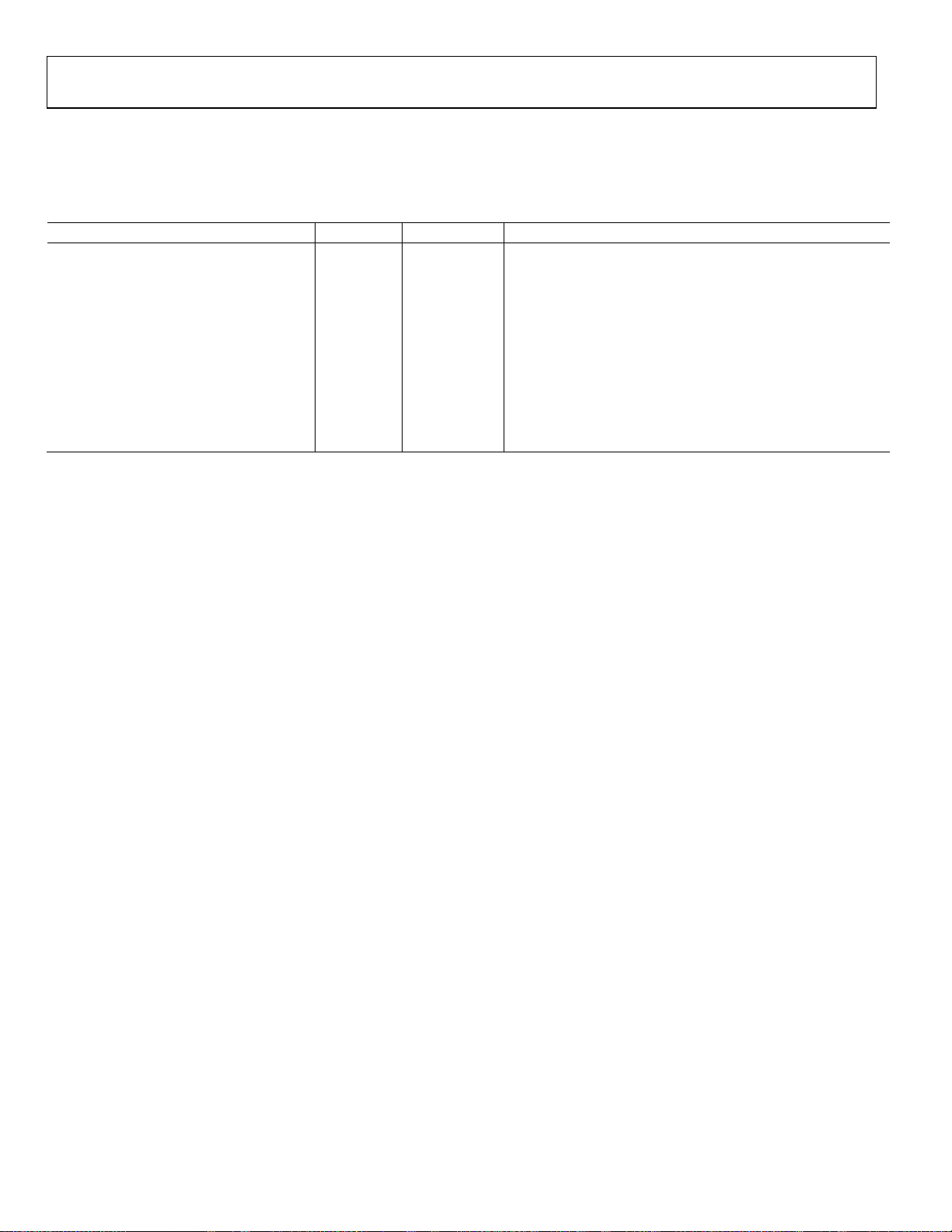

Table 1. High Channel Count Bipolar DACs

Model Resolution (Bits) Nominal Output Span Output Channels Linearity Error (LSB)

AD5360 16 4 × V

AD5361 14 4 × V

AD5362 16 4 × V

AD5363 14 4 × V

AD5370 16 4 × V

AD5371 14 4 × V

AD5372 16 4 × V

AD5373 14 4 × V

(20 V) 16 ±4

REF

(20 V) 16 ±1

REF

(20 V) 8 ±4

REF

(20 V) 8 ±1

REF

(12 V) 40 ±4

REF

(12 V) 40 ±1

REF

(12 V) 32 ±4

REF

(12 V) 32 ±1

REF

AD5378 14 ±8.75 V 32 ±3

AD5379 14 ±8.75 V 40 ±3

The AD5362/AD5363 have a high speed 4-wire serial interface

that is compatible with SPI, QSPI™, MICROWIRE™, and DSP

interface standards and can handle clock speeds of up to

50 MHz. All the outputs can be updated simultaneously by

taking the

LDAC

input low. Each channel has a programmable

gain and an offset adjust register.

Each DAC output is gained and buffered on chip with respect

to an external SIGGNDx input. The DAC outputs can also be

switched to SIGGNDx via the

CLR

pin.

Rev. A | Page 3 of 28

AD5362/AD5363

SPECIFICATIONS

DVCC = 2.5 V to 5.5 V; VDD = 9 V to 16.5 V; VSS = −16.5 V to −4.5 V; V

R

= open circuit; gain (M), offset (C), and DAC offset registers at default values; all specifications T

L

Table 2.

Parameter B Version1Unit Test Conditions/Comments

ACCURACY

Resolution 16 Bits AD5362

14 Bits AD5363

Integral Nonlinearity (INL) ±4 LSB max AD5362

±1 LSB max AD5363

Differential Nonlinearity (DNL) ±1 LSB max Guaranteed monotonic by design over temperature

Zero-Scale Error ±15 mV max Before calibration

Full-Scale Error ±20 mV max Before calibration

Gain Error 0.1 % FSR Before calibration

Zero-Scale Error

Full-Scale Error

2

2

1 LSB typ After calibration

1 LSB typ After calibration

Span Error of Offset DAC ±75 mV max See the Offset DACs section for details

VOUTx3 Temperature Coefficient 5 ppm FSR/°C typ Includes linearity, offset, and gain drift

DC Crosstalk

REFERENCE INPUTS (VREF0, VREF1)

2

180 μV max

2

VREFx Input Current ±10 μA max Per input; typically ±30 nA

VREFx Range

SIGGND0 AND SIGGND1 INPUTS

2

2/5 V min/V max ±2% for specified operation

2

DC Input Impedance 50 kΩ min Typically 55 kΩ

Input Range ±0.5 V min/V max

SIGGNDx Gain 0.995/1.005 min/max

OUTPUT CHARACTERISTICS

2

Output Voltage Range VSS + 1.4 V min I

V

− 1.4 V max I

DD

Nominal Output Voltage Range −10 to +10 V

Short-Circuit Current 15 mA max VOUTx3 to DVCC, VDD, or VSS

Load Current ±1 mA max

Capacitive Load 2200 pF max

DC Output Impedance 0.5 Ω max

MONITOR PIN (MON_OUT)

2

Output Impedance

DAC Output at Positive Full Scale 1000 Ω typ

DAC Output at Negative Full Scale 500 Ω typ

Three-State Leakage Current 100 nA typ

Continuous Current Limit 2 mA max

DIGITAL INPUTS

Input High Voltage 1.7 V min DVCC = 2.5 V to 3.6 V

2.0 V min DV

Input Low Voltage 0.8 V max DVCC = 2.5 V to 5.5 V

Input Current ±1 μA max

±20 μA max

Input Capacitance

2

10 pF max

= 5 V; AGND = DGND = SIGGND0 = SIGGND1 = 0 V;

REF

MIN

to T

, unless otherwise noted.

MAX

Typically 20 μV; measured channel at midscale, full-scale

change on any other channel

= 1 mA

LOAD

= 1 mA

LOAD

= 3.6 V to 5.5 V

CC

, SYNC, SDI, and SCLK pins

RESET

, BIN/2SCOMP, and GPIO pins

CLR

Rev. A | Page 4 of 28

AD5362/AD5363

Parameter B Version1Unit Test Conditions/Comments

DIGITAL OUTPUTS (SDO, BUSY, GPIO, PEC)

Output Low Voltage 0.5 V max Sinking 200 μA

Output High Voltage (SDO) DVCC − 0.5 V min Sourcing 200 μA

High Impedance Leakage Current ±5 μA max SDO only

High Impedance Output Capacitance

TEMPERATURE SENSOR (TEMP_OUT)

2

Accuracy ±1 °C typ @ 25°C

±5 °C typ −40°C < T < +85°C

Output Voltage at 25°C 1.46 V typ

Output Voltage Scale Factor 4.4 mV/°C typ

Output Load Current 200 μA max Current source only

Power-On Time 10 ms typ To within ±5°C

POWER REQUIREMENTS

DVCC 2.5/5.5 V min/V max

VDD 8/16.5 V min/V max

VSS −16.5/−4.5 V min/V max

Power Supply Sensitivity

2

∆Full Scale/∆VDD −75 dB typ

∆Full Scale/∆VSS −75 dB typ

∆Full Scale/∆DVCC −90 dB typ

DICC 2 mA max DVCC = 5.5 V, VIH = DVCC, VIL = GND

IDD 8.5 mA max Outputs = 0 V and unloaded

ISS 8.5 mA max Outputs = 0 V and unloaded

Power-Down Mode Bit 0 in the control register is 1

DICC 5 μA typ

IDD 35 μA typ

ISS −35 μA typ

Power Dissipation

Power Dissipation Unloaded (P) 209 mW max VSS = −12 V, VDD = 12 V, DVCC = 2.5 V

Junction Temperature

1

Temperature range for B version: −40°C to +85°C. Typical specifications are at 25°C.

2

Guaranteed by design and characterization; not production tested.

3

VOUTx refers to any of VOUT0 to VOUT7.

4

θJA represents the package thermal impedance.

4

2

10 pF typ

130 °C max TJ = TA + P

TOTAL

× θJA

Rev. A | Page 5 of 28

AD5362/AD5363

AC CHARACTERISTICS

DVCC = 2.5 V; VDD = 15 V; VSS = −15 V; V

offset (C), and DAC offset registers at default values; all specifications T

Table 3.

Parameter B Version1Unit Test Conditions/Comments

DYNAMIC PERFORMANCE1

Output Voltage Settling Time 20 μs typ Full-scale change

30 μs max DAC latch contents alternately loaded with all 0s and all 1s

Slew Rate 1 V/μs typ

Digital-to-Analog Glitch Energy 5 nV-s typ

Glitch Impulse Peak Amplitude 10 mV max

Channel-to-Channel Isolation 100 dB typ VREF0, VREF1 = 2 V p-p, 1 kHz

DAC-to-DAC Crosstalk 10 nV-s typ

Digital Crosstalk 0.2 nV-s typ

Digital Feedthrough 0.02 nV-s typ Effect of input bus activity on DAC output under test

Output Noise Spectral Density @ 10 kHz 250 nV/√Hz typ VREF0 = VREF1 = 0 V

1

Guaranteed by design and characterization; not production tested.

= 5 V; AGND = DGND = SIGGND0 = SIGGND1 = 0 V; CL = 200 pF; RL = 10 kΩ; gain (M),

REF

MIN

to T

, unless otherwise noted.

MAX

Rev. A | Page 6 of 28

AD5362/AD5363

TIMING CHARACTERISTICS

DVCC = 2.5 V to 5.5 V; VDD = 9 V to 16.5 V; VSS = −16.5 V to −8 V; V

R

= open circuit; gain (M), offset (C), and DAC offset registers at default values; all specifications T

L

= 5 V; AGND = DGND = SIGGND = 0 V; CL = 200 pF to GND;

REF

MIN

to T

, unless otherwise noted.

MAX

Table 4. SPI Interface

1, 2, 3

Parameter

t

1

Limit at T

MIN

, T

Unit Description

MAX

20 ns min SCLK cycle time

t2 8 ns min SCLK high time

t3 8 ns min SCLK low time

t4 11 ns min

t

5

20 ns min

t6 10 ns min

t

7

5 ns min Data setup time

falling edge to SCLK falling edge setup time

SYNC

Minimum SYNC

th

SCLK falling edge to SYNC rising edge

24

high time

t8 5 ns min Data hold time

4

t

9

t

1/1.5 μs typ/μs max

10

42 ns max

rising edge to BUSY falling edge

SYNC

pulse width low (single-channel update); see Table 9

BUSY

t11 600 ns max Single-channel update cycle time

t12 20 ns min

t13 10 ns min

t14 3 μs max

t15 0 ns min

t16 3 μs max

rising edge to LDAC falling edge

SYNC

pulse width low

LDAC

rising edge to DAC output response time

BUSY

rising edge to LDAC falling edge

BUSY

falling edge to DAC output response time

LDAC

t17 20/30 μs typ/μs max DAC output settling time

t18 140 ns max

t19 30 ns min

t20 400 μs max

t21 270 ns min

5

t

22

25 ns max SCLK rising edge to SDO valid

t23 80 ns max

1

Guaranteed by design and characterization; not production tested.

2

All input signals are specified with tR = tF = 2 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V.

3

See Figure 4 and Figure 5.

4

t9 is measured with the load circuit shown in Figure 2.

5

t22 is measured with the load circuit shown in Figure 3.

/RESET pulse activation time

CLR

pulse width low

RESET

time indicated by BUSY low

RESET

Minimum SYNC

rising edge to BUSY falling edge

RESET

high time in readback mode

TO

OUTPUT

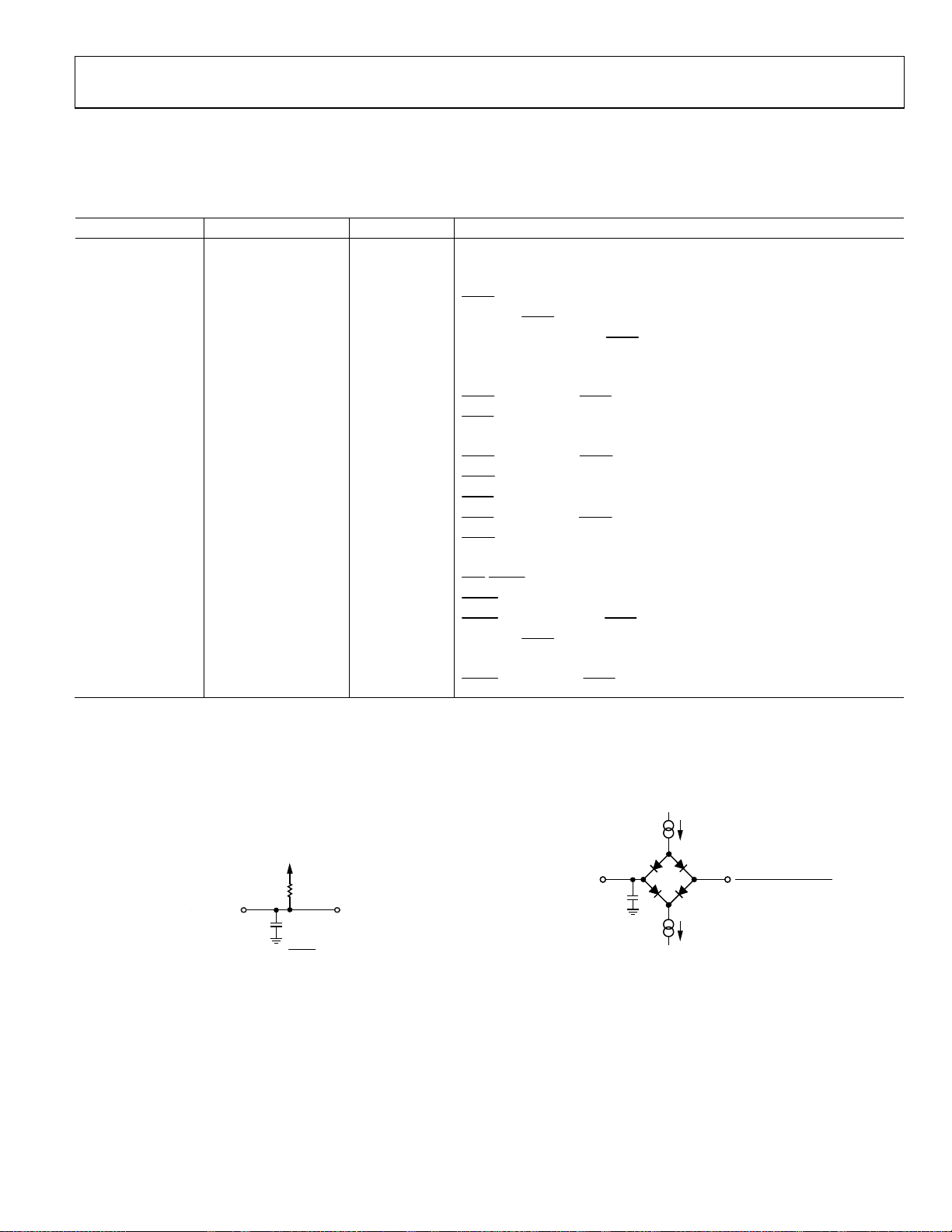

PIN

Figure 2. Load Circuit for

DV

CC

R

2.2k

C

L

50pF

BUSY

L

Ω

V

OL

05762-002

Timing Diagram

Rev. A | Page 7 of 28

TO OUTPUT

PIN

50pF

C

200µA I

L

200µA I

OL

OH

Figure 3. Load Circuit for SDO Timing Diagram

VOH (MIN) – VOL (MAX)

2

05762-003

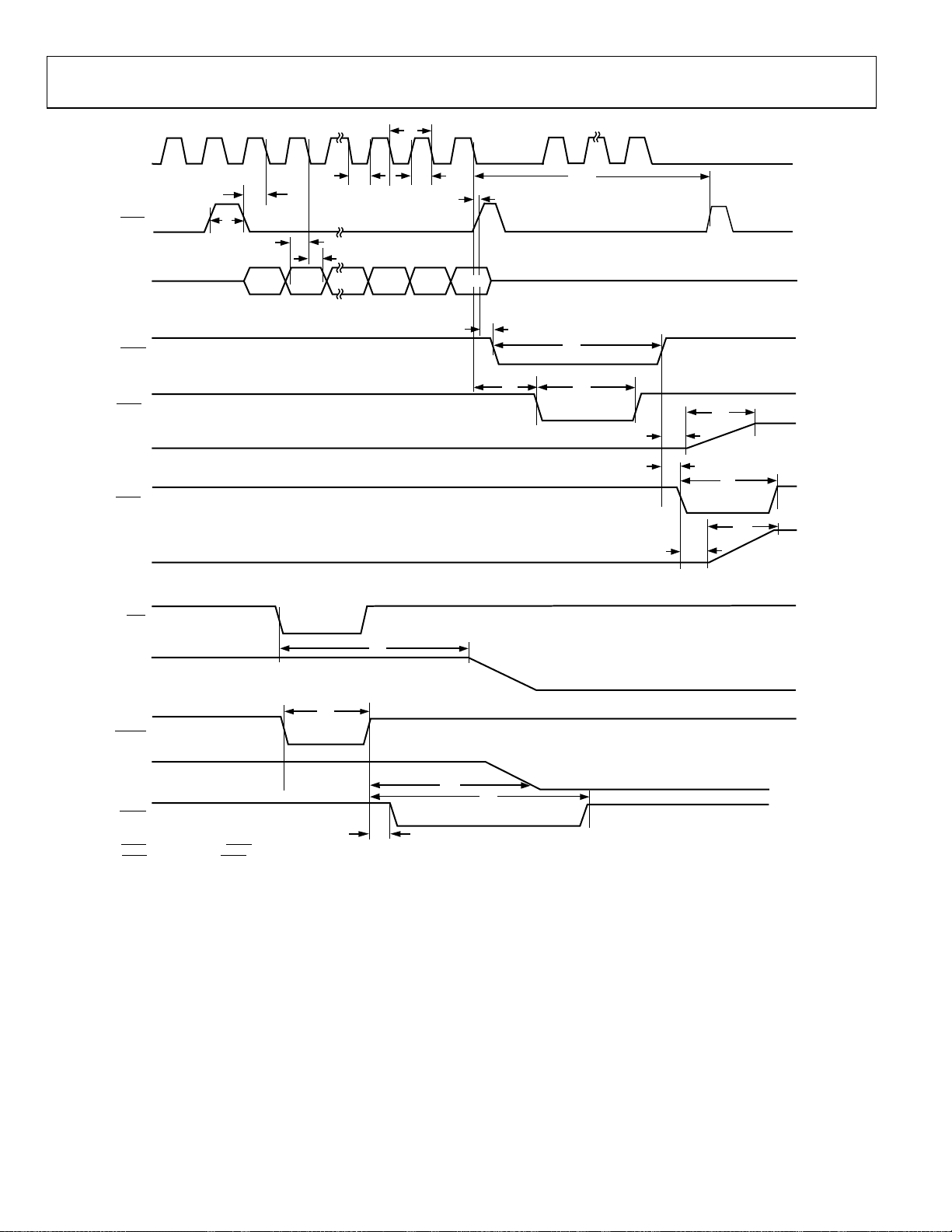

AD5362/AD5363

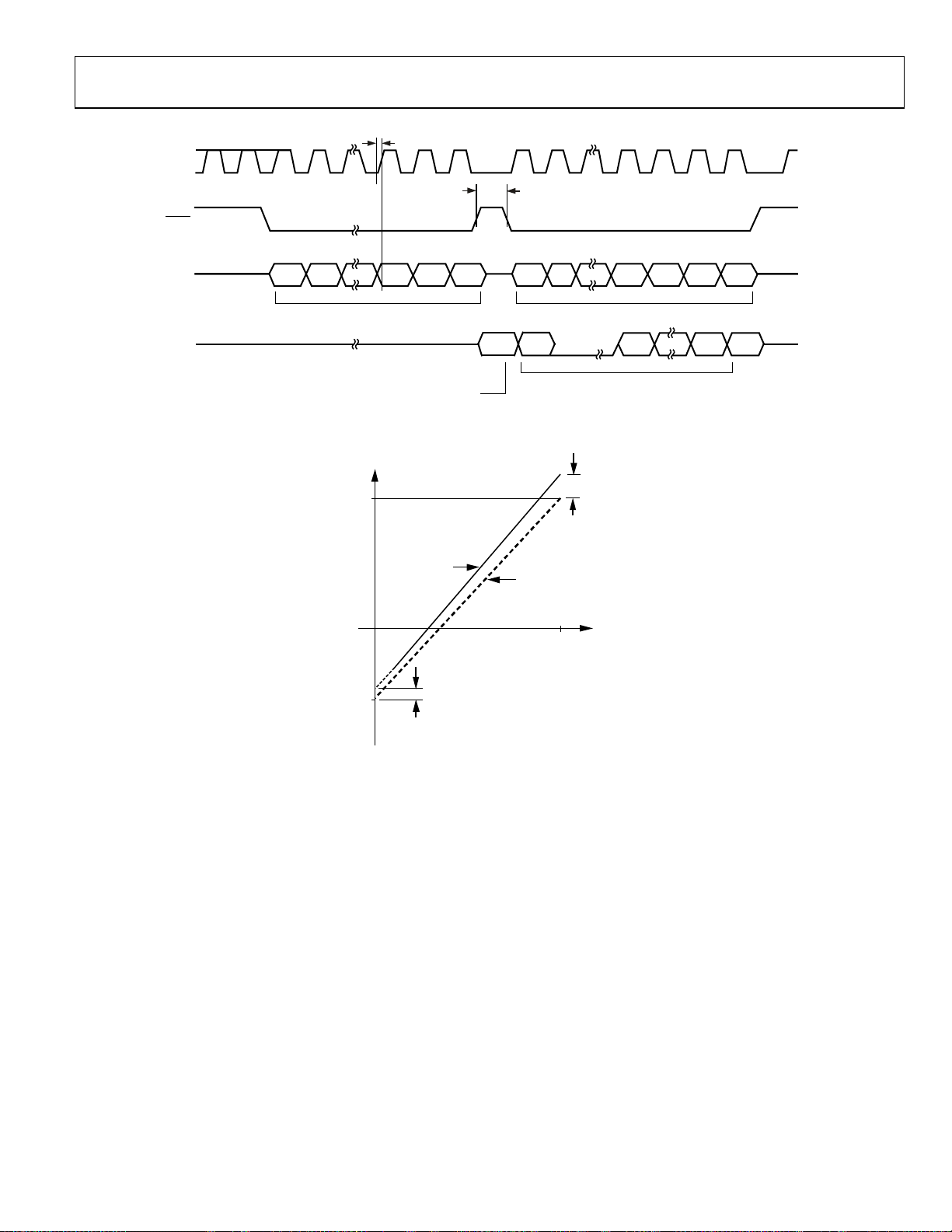

t

1

SCLK

SYNC

BUSY

LDAC

VOUTx

LDAC

VOUTx

SDI

1

1

2

2

1

2

t

3

t

4

t

5

t

7

t

8

DB23

24

t

2

t

6

DB0

t

9

t

1

t

11

t

10

12

t

13

24

t

17

t

14

t

15

t

13

t

17

t

16

CLR

VOUTx

RESET

VOUTx

BUSY

1

LDAC ACTIVE DURING BUSY.

2

LDAC ACTIVE AFTER BUSY.

t

18

t

19

t

18

t

20

t

23

05762-004

Figure 4. SPI Write Timing

Rev. A | Page 8 of 28

AD5362/AD5363

SCLK

SYNC

SDI

INPUT WORD SPECIFIES

REGISTER TO BE READ

SDO

t

22

DB0 DB23DB23

LSB FRO M PREVIOUS W RITE

t

21

NOP CONDITI ON

DB0

DB23 DB15

SELECTED REG ISTER DATA CLOCKED OUT

48

DB0

DB0

05762-005

Figure 5. SPI Read Timing

OUTPUT

VOLTAGE

V

MAX

ACTUAL

TRANSFER

FUNCTION

IDEAL

TRANSFER

FUNCTION

FULL-SCAL E

ERROR

+

ZERO-SCALE

ERROR

0

V

MIN

DAC CODE

ZERO-SCALE

ERROR

N

2

– 1

n = 16 FOR AD5362

n = 14 FOR AD5363

05762-006

Figure 6. DAC Transfer Function

Rev. A | Page 9 of 28

AD5362/AD5363

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted. Transient currents of up to

60 mA do not cause SCR latch-up.

Table 5.

Parameter Rating

VDD to AGND −0.3 V to +17 V

VSS to AGND −17 V to +0.3 V

DVCC to DGND −0.3 V to +7 V

Digital Inputs to DGND −0.3 V to DVCC + 0.3 V

Digital Outputs to DGND −0.3 V to DVCC + 0.3 V

VREF0, VREF1 to AGND −0.3 V to +5.5 V

VOUT0 through VOUT7 to AGND VSS − 0.3 V to VDD + 0.3 V

SIGGND0, SIGGND1 to AGND −1 V to +1 V

AGND to DGND −0.3 V to +0.3 V

V

MON_IN0, MON_IN1, MON_OUT

to AGND

Operating Temperature Range (TA)

Industrial (J Version) −40°C to +85°C

Storage Temperature Range −65°C to +150°C

Operating Junction Temperature

max)

(T

J

θJA Thermal Impedance

52-Lead LQFP 38°C/W

56-Lead LFCSP 25°C/W

Reflow Soldering

Peak Temperature 230°C

Time at Peak Temperature 10 sec to 40 sec

− 0.3 V to VDD + 0.3 V

SS

130°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. A | Page 10 of 28

AD5362/AD5363

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

D

D

C

C

N

N

C

A

G

G

V

D

L

A

D

D

2

3

4

5

5

5

5

5

PIN 1

INDICATOR

AD5362/

AD5363

TOP VIEW

(Not to Scale)

6

9

8

7

1

1

1

1

4

5

6

C

T

T

T

N

U

U

U

O

O

O

V

V

V

O

C

D

E

S

P

0

1

5

5

1

0

2

2

7

1

T

D

U

N

O

G

V

G

I

S

LDAC

CLR

RESET

BIN/2SCOMP

BUSY

GPIO

MON_OUT

MON_IN0

NC

NC

V

DD

V

SS

VREF1

NC = NO CONNECT

AGND

DVCCSDO

PEC

SDI

SCLK

SYNC

DGND

52 51 50 49 48 43 42 41 4047 46 45 44

1

2

PIN 1

3

INDICATOR

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

NC

VOUT4

(Not to Scale)

VOUT5

VOUT6

AD5362/

AD5363

TOP VIEW

VOUT7

DVCCDGNDNCNC

NCNCNCNCNCNCNC

SIGGND1

NC

39

NC

38

SIGGND0

37

VOUT3

36

VOUT2

35

VOUT1

34

VOUT0

33

TEMP_OUT

32

MON_IN1

31

VREF0

30

NC

29

V

SS

28

V

DD

27

NC

R

L

C

6

5

RESET

BUSY

GPIO

NC

NC

NC

NC

NC

V

V

VREF1

1

2

3

4

5

6

7

8

9

10

11

12

DD

13

SS

14

5

1

C

N

BIN/2SCOMP

MON_OUT

MON_IN0

NC = NO CONNECT

05762-007

Figure 7. 52-Lead LQFP Pin Configuration Figure 8. 56-Lead LFCSP Pin Configuration

Table 6. Pin Function Descriptions

Pin No.

LQFP LFCSP

1 55

Mnemonic Description

Load DAC Logic Input (Active Low). See the BUSY and LDAC Functions section

LDAC

for more information.

2 56

Asynchronous Clear Input (Level Sensitive, Active Low). See the Clear Function

CLR

section for more information.

3 1

4 2

RESET

/2SCOMP Data Format Digital Input. Connecting this pin to DGND selects offset binary.

BIN

Digital Reset Input.

Setting this pin to 1 selects twos complement. This input has a weak pull-down.

5 3

Digital Input/Open-Drain Output. BUSY is open drain when it is an output. See

BUSY

the BUSY and LDAC Functions section for more information.

6 4 GPIO

Digital I/O Pin. This pin can be configured as an input or output that can be

read back or programmed high or low via the serial interface. When configured

as an input, this pin has a weak pull-down.

7 5 MON_OUT

Analog Multiplexer Output. Any DAC output, the MON_IN0 input, or the

MON_IN1 input can be routed to this output for monitoring.

8, 32 6, 34

MON_IN0,

Analog Multiplexer Inputs. Can be routed to MON_OUT.

MON_IN1

9, 10, 14, 20 to

27, 30, 39 to 42

7 to 11, 15, 16,

22 to 28, 31, 32,

NC No Connect.

41 to 44

11, 28 12, 29 VDD

Positive Analog Power Supply; 9 V to 16.5 V for specified performance. These

pins should be decoupled with 0.1 μF ceramic capacitors and 10 μF capacitors.

12, 29 13, 30 VSS

Negative Analog Power Supply; −16.5 V to −8 V for specified performance.

These pins should be decoupled with 0.1 μF ceramic capacitors and 10 μF

capacitors.

13 14 VREF1 Reference Input for DAC 4 to DAC 7. This reference voltage is referred to AGND.

34 to 37, 15 to 18 36 to 39, 17 to 20 VOUT0 to VOUT7

DAC Outputs. Buffered analog outputs for each of the eight DAC channels.

Each analog output is capable of driving an output load of 10 kΩ to ground.

Typical output impedance of these amplifiers is 0.5 Ω.

19 21 SIGGND1

Reference Ground for DAC 4 to DAC 7. VOUT4 to VOUT7 are referenced to this

voltage.

31 33 VREF0 Reference Input for DAC 0 to DAC 3. This reference voltage is referred to AGND.

D

C

K

C

N

C

I

L

N

G

V

D

C

Y

NC

NC

D

S

S

S

D

3

4

5

6

7

8

9

4

4

2

3

2

2

C

C

N

N

4

4

4

4

4

42

NC

NC

41

SIGGND0

40

VOUT3

39

VOUT2

38

VOUT1

37

VOUT0

36

TEMP_OUT

35

MON_IN1

34

VREF0

33

NC

32

NC

31

V

30

SS

V

29

DD

7

8

6

5

4

2

2

2

2

2

C

C

C

C

C

N

N

N

N

N

05762-025

Rev. A | Page 11 of 28

AD5362/AD5363

Pin No.

LQFP LFCSP

33 35 TEMP_OUT

38 40 SIGGND0

43, 51 45, 53 DGND

44, 50 46, 52 DVCC

45 47

46 48 SCLK

47 49 SDI

48 50

49 51 SDO

52 54 AGND

Exposed Paddle EP Exposed Paddle. Connect to VSS.

Mnemonic Description

Provides an output voltage proportional to the chip temperature, typically

1.46 V at 25°C with an output variation of 4.4 mV/°C.

Reference Ground for DAC 0 to DAC 3. VOUT0 to VOUT3 are referenced to this

voltage.

Ground for All Digital Circuitry. Both DGND pins should be connected to the

DGND plane.

Logic Power Supply; 2.5 V to 5.5 V. These pins should be decoupled with 0.1 μF

ceramic capacitors and 10 μF capacitors.

Active Low or SYNC Input for SPI Interface. This is the frame synchronization

SYNC

signal for the SPI serial interface. See , , and the

Figure 4 Figure 5 Serial Interface

section for more details.

Serial Clock Input for SPI Interface. See Figure 4, Figure 5, and the Serial Interface

section for more details.

Serial Data Input for SPI Interface. See Figure 4, Figure 5, and the Serial Interface

section for more details.

PEC

Packet Error Check Output. This is an open-drain output with a 50 kΩ pull-up

that goes low if the packet error check fails.

Serial Data Output for SPI Interface. See Figure 4, Figure 5, and the Serial

Interface section for more details.

Ground for All Analog Circuitry. The AGND pin should be connected to the

AGND plane.

Rev. A | Page 12 of 28

AD5362/AD5363

TYPICAL PERFORMANCE CHARACTERISTICS

2

1

0

INL (LSB)

–1

–2

0 65535

1.0

0.5

0

INL ERROR (LSB)

–0.5

16384 32768 4 9152

DAC CODE

VDD = +15V

= –15V

V

SS

DV

= +5V

CC

= +3V

V

REF

05762-008

0.0050

0.0025

0

AMPLITUDE ( V)

–0.0025

–0.0050

05

1234

TIME (µs)

TA = 25°C

= –15V

V

SS

= +15V

V

DD

V

= +4.096V

REF

05762-011

Figure 12. Digital Crosstalk Figure 9. Typical AD5362 INL Plot

1.0

0.5

0

DNL (LSB)

–0.5

–1.0

08

0

TA = 25°C

V

SS

V

DD

V

REF

–0.01

AMPLITUDE ( V)

–0.02

024681

20 40 60

TEMPERATURE ( °C)

= –15V

= +15V

= +4.096V

TIME (µs)

Figure 11. Analog Crosstalk Due to

LDAC

0

05762-009

0

05762-010

–1.0

0 65535

600

500

400

300

200

OUTPUT NOI SE (nV/ √Hz)

100

0

05

16384 32768 49152

DAC CODE

Figure 13. Typical AD5362 DNL Plot Figure 10. Typical INL Error vs. Temperature

1234

FREQUENCY (Hz)

Figure 14. Output Noise Spectral Density

05762-012

05762-013

Rev. A | Page 13 of 28

AD5362/AD5363

0.50

VSS = –12V

= +12V

V

DD

= +3V

V

REF

0.45

0.40

(mA)

CC

DI

0.35

0.30

DVCC = +5.5V

DV

= +2.5V

CC

DV

CC

= +3.6V

14

12

10

8

6

NUMBER OF UNITS

4

2

DV

T

A

= 5V

CC

= 25°C

0.25

6.5

6.0

(mA)

5.5

SS

/I

DD

I

5.0

4.5

14

12

10

–20 0 20 6040

–40 80

TEMPERATURE (° C)

Figure 15. DI

VSS= –12V

VDD = +12V

= +3V

V

REF

–40 80

–20 0 20 6040

Figure 16. I

vs. Temperature

CC

I

DD

I

SS

TEMPERATURE ( °C)

vs. Temperature

DD/ISS

V

V

T

= –15V

SS

= +15V

DD

= 25°C

A

0

0.30 0.35 0. 40

05762-014

DICC (mA)

Figure 18. Typical DI

2.0

1.9

1.8

1.7

1.6

1.5

1.4

VOLTAGE (V)

1.3

1.2

1.1

1.0

–40 –25 –10 5 20 35 5 0 65 80

05762-015

TEMPERATURE ( °C)

0.45 0.50

Distribution

CC

05762-017

05762-018

Figure 19. TEMP_OUT Voltage vs. Temperature

1.0

FULL-SCALE

0.5

MIDSCALE

8

6

NUMBER OF UNITS

4

2

0

5.8 6.0 6.2

Figure 17. Typical I

IDD (mA)

DD

6.4 6.6

Distribution

05762-016

ZERO-SCALE

0

VOUTx – MON_O UT (V)

–0.5

–1.0

–1.0 –1.0

–0.5 0 0.5

MON_OUT CURRENT (mA)

Figure 20. VOUTx MON_OUT Error vs. MON_OUT Current

05762-019

Rev. A | Page 14 of 28

AD5362/AD5363

TERMINOLOGY

Integral Nonlinearity (INL)

Integral nonlinearity, or endpoint linearity, is a measure of

the maximum deviation from a straight line passing through

the endpoints of the DAC transfer function. It is measured

after adjusting for zero-scale error and full-scale error and is

expressed in least significant bits (LSB).

Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between the measured

change and the ideal 1 LSB change between any two adjacent

codes. A specified differential nonlinearity of 1 LSB maximum

ensures monotonicity.

Zero-Scale Error

Zero-scale error is the error in the DAC output voltage when

all 0s are loaded into the DAC register. Zero-scale error is a

measure of the difference between VOUT (actual) and VOUT

(ideal), expressed in millivolts, when the channel is at its minimum value. Zero-scale error is mainly due to offsets in the

output amplifier.

Full-Scale Error

Full-scale error is the error in the DAC output voltage when

all 1s are loaded into the DAC register. Full-scale error is a

measure of the difference between VOUT (actual) and VOUT

(ideal), expressed in millivolts, when the channel is at its maximum value. Full-scale error does not include zero-scale error.

Gain Error

Gain error is the difference between full-scale error and

zero-scale error. It is expressed as a percentage of the fullscale range (FSR).

Gain Error = Full-Scale Error − Zero-Scale Error

VOUT Temperature Coefficient

The VOUT temperature coefficient includes output error

contributions from linearity, offset, and gain drift.

DC Output Impedance

DC output impedance is the effective output source resistance.

It is dominated by package lead resistance.

DC Crosstalk

The DAC outputs are buffered by op amps that share common

V

and VSS power supplies. If the dc load current changes in

DD

one channel (due to an update), this change can result in a

further dc change in one or more channel outputs. This effect is

more significant at high load currents and is reduced as the load

currents are reduced. With high impedance loads, the effect is

virtually immeasurable. Multiple V

provided to minimize dc crosstalk.

and VSS terminals are

DD

Output Voltage Settling Time

Output voltage settling time is the amount of time it takes for

the output of a DAC to settle to a specified level for a full-scale

input change.

Digital-to-Analog Glitch Energy

Digital-to-analog glitch energy is the amount of energy that is

injected into the analog output at the major code transition. It is

specified as the area of the glitch in nV-s. It is measured by

toggling the DAC register data between 0x7FFF and 0x8000

(AD5362) or 0x1FFF and 0x2000 (AD5363).

Channel-to-Channel Isolation

Channel-to-channel isolation refers to the proportion of input

signal from one DAC reference input that appears at the output

of another DAC operating from another reference. It is

expressed in decibels and measured at midscale.

DAC-to-DAC Crosstalk

DAC-to-DAC crosstalk is the glitch impulse that appears at

the output of one converter due to both the digital change

and subsequent analog output change at another converter.

It is specified in nV-s.

Digital Crosstalk

Digital crosstalk is defined as the glitch impulse transferred to

the output of one converter due to a change in the DAC register

code of another converter. It is specified in nV-s.

Digital Feedthrough

When the device is not selected, high frequency logic activity

on the digital inputs of the device can be capacitively coupled

both across and through the device to appear as noise on the

VOUT pins. It can also be coupled along the supply and ground

lines. This noise is digital feedthrough.

Output Noise Spectral Density

Output noise spectral density is a measure of internally

generated random noise. Random noise is characterized as a

spectral density (voltage per √Hz). It is measured by loading

all DACs to midscale and measuring noise at the output. It is

measured in nV/√Hz.

Rev. A | Page 15 of 28

AD5362/AD5363

THEORY OF OPERATION

DAC ARCHITECTURE

The AD5362/AD5363 contain eight DAC channels and eight

output amplifiers in a single package. The architecture of a

single DAC channel consists of a 16-bit (AD5362) or 14-bit

(AD5363) resistor-string DAC followed by an output buffer

amplifier. The resistor-string section is simply a string of resistors,

of equal value, from VREF0 or VREF1 to AGND. This type of

architecture guarantees DAC monotonicity. The 16-bit (AD5362)

or 14-bit (AD5363) binary digital code loaded to the DAC

register determines at which node on the string the voltage is

Table 7. AD5362/AD5363 Registers

Register Name Word Length in Bits Description

X1A (Group) (Channel) 16 (14) Input Data Register A, one for each DAC channel.

X1B (Group) (Channel) 16 (14) Input Data Register B, one for each DAC channel.

M (Group) (Channel) 16 (14) Gain trim registers, one for each DAC channel.

C (Group) (Channel) 16 (14) Offset trim registers, one for each DAC channel.

X2A (Group) (Channel) 16 (14)

X2B (Group) (Channel) 16 (14)

DAC (Group) (Channel)

OFS0 14 Offset DAC 0 data register: sets offset for Group 0.

OFS1 14 Offset DAC 1 data register: sets offset for Group 1.

Control 5

Monitor 6

GPIO 2

A/B Select 0 8

A/B Select 1 8

Output Data Register A, one for each DAC channel. These registers store the final,

calibrated DAC data after gain and offset trimming. They are not readable or directly

writable.

Output Data Register B, one for each DAC channel. These registers store the final,

calibrated DAC data after gain and offset trimming. They are not readable or directly

writable.

Data registers from which the DACs take their final input data. The DAC registers are

updated from the X2A or X2B registers. They are not readable or directly writable.

Bit 4 = overtemperature indicator.

Bit 3 = PEC error flag.

Bit 2 = A

Bit 1 = thermal shutdown.

Bit 0 = software power-down.

Bit 5 = monitor enable.

Bit 4 = monitor DACs or monitor MON_INx pin.

Bit 3 to Bit 0 = monitor selection control.

Bit 1 = GPIO configuration.

Bit 0 = GPIO data.

Bits [3:0] in this register determine whether a DAC in Group 0 takes its data from

Register X2A or Register X2B (0 = X2A, 1 = X2B).

Bits [3:0] in this register determine whether a DAC in Group 1 takes its data from

Register X2A or Register X2B (0 = X2A, 1 = X2B).

/B select.

tapped off before being fed into the output amplifier. The output

amplifier multiplies the DAC output voltage by 4. The nominal

output span is 12 V with a 3 V reference and 20 V with a 5 V

reference.

CHANNEL GROUPS

The eight DAC channels of the AD5362/AD5363 are arranged

into two groups of four channels. The four DACs of Group 0

derive their reference voltage from VREF0. The four DACs of

Group 1 derive their reference voltage from VREF1. Each group

has its own signal ground pin.

Table 8. AD5362/AD5363 Input Register Default Values

Register Name AD5362 Default Value AD5363 Default Value

X1A, X1B 0x8000 0x2000

M 0xFFFF 0x3FFF

C 0x8000 0x2000

OFS0, OFS1 0x2000 0x2000

Control 0x00 0x00

A/B Select 0 and A/B Select 1 0x00 0x00

Rev. A | Page 16 of 28

AD5362/AD5363

A/B REGISTERS AND GAIN/OFFSET ADJUSTMENT

Each DAC channel has seven data registers. The actual DAC

data-word can be written to either the X1A or X1B input

register, depending on the setting of the

register. If the

A

If the

A

/B bit is 0, data is written to the X1A register.

/B bit is 1, data is written to the X1B register. Note that

this single bit is a global control and affects every DAC channel

in the device. It is not possible to set up the device on a perchannel basis so that some writes are to X1A registers and some

writes are to X1B registers.

X1A

REGISTER

X1B

REGISTER

REGISTER

REGISTER

Figure 21. Data Registers Associated with Each DAC Channel

MUX

M

C

X2A

REGISTER

X2B

REGISTER

Each DAC channel also has a gain (M) register and an offset (C)

register, which allow trimming out of the gain and offset errors

of the entire signal chain. Data from the X1A register is operated

on by a digital multiplier and adder controlled by the contents of

the M and C registers. The calibrated DAC data is then stored in

the X2A register. Similarly, data from the X1B register is operated

on by the multiplier and adder and stored in the X2B register.

Although a multiplier and an adder symbol are shown in Figure 21

for each channel, there is only one multiplier and one adder in

the device, which are shared among all channels. This has implications for the update speed when several channels are updated

at once, as described in the Register Update Rates section.

Each time data is written to the X1A register, or to the M or C

register with the

A

/B control bit set to 0, the X2A data is recalculated and the X2A register is automatically updated. Similarly,

X2B is updated each time data is written to X1B, or to M or C

A

with

/B set to 1. The X2A and X2B registers are not readable

or directly writable by the user.

Data output from the X2A and X2B registers is routed to the

final DAC register by a multiplexer. A 4-bit A/B select register

associated with each group of four DACs controls whether each

individual DAC takes its data from the X2A or X2B register. If a

bit in this register is 0, the DAC takes its data from the X2A

register; if 1, the DAC takes its data from the X2B register.

Note that because there are eight bits in two registers, it is possible

to set up, on a per-channel basis, whether each DAC takes its

data from the X2A or X2B register. A global command is also

provided that sets all bits in the A/B select registers to 0 or to 1.

A

/B bit in the control

MUX

DAC

REGISTER

DAC

05762-020

All DACs in the AD5362/AD5363 can be updated simultaneously by taking

LDAC

low when each DAC register is updated

from either its X2A or X2B register, depending on the setting of

the A/B select registers. The DAC register is not readable or

directly writable by the user.

LDAC

can be permanently tied

low, and the DAC output is updated whenever new data appears

in the appropriate DAC register.

OFFSET DACS

In addition to the gain and offset trim for each DAC, there are

two 14-bit offset DACs, one for Group 0 and one for Group 1.

These allow the output range of all DACs connected to them to

be offset within a defined range. Thus, subject to the limitations

of headroom, it is possible to set the output range of Group 0 or

Group 1 to be unipolar positive, unipolar negative, or bipolar,

either symmetrical or asymmetrical about 0 V. The DACs in the

AD5362/AD5363 are factory trimmed with the offset DACs set

at their default values. This gives the best offset and gain performance for the default output range and span.

When the output range is adjusted by changing the value of the

offset DAC, an extra offset is introduced due to the gain error of

the offset DAC. The amount of offset is dependent on the magnitude of the reference and how much the offset DAC moves

from its default value. See the Specifications section for this

offset. The worst-case offset occurs when the offset DAC is at

positive or negative full scale. This value can be added to the

offset present in the main DAC channel to give an indication of

the overall offset for that channel. In most cases, the offset can

be removed by programming the C register of the channel with

an appropriate value. The extra offset caused by the offset DAC

needs to be taken into account only when the offset DAC is

changed from its default value. Figure 22 shows the allowable

code range that can be loaded to the offset DAC, depending on

the reference value used. Thus, for a 5 V reference, the offset

DAC should not be programmed with a value greater than 8192

(0x2000).

5

4

3

)

V

(

F

E

R

V

2

1

0

0 4096 8192 12288 16383

OFFSET DAC CODE

Figure 22. Offset DAC Code Range

RESERVED

05762-021

Rev. A | Page 17 of 28

AD5362/AD5363

OUTPUT AMPLIFIER

Because the output amplifiers can swing to 1.4 V below the

positive supply and 1.4 V above the negative supply, this limits

how much the output can be offset for a given reference voltage.

For example, it is not possible to have a unipolar output range

of 20 V, because the maximum supply voltage is ±16.5 V.

S1

OUTPUT

S2

CLR

R6

10kΩ

S3

SIGGNDx

CLR

SIGGNDx

DAC

CHANNEL

R5

60kΩ

R1

20kΩ

CLR

R4

R3

60kΩ

20kΩ

OFFSET

DAC

Figure 23. Output Amplifier and Offset DAC

R2

20kΩ

Figure 23 shows details of a DAC output amplifier and its connections to the offset DAC. On power-up, S1 is open, disconnecting

the amplifier from the output. S3 is closed, so the output is pulled

to SIGGNDx (R1 and R2 are greater than R6). S2 is also closed to

prevent the output amplifier from being open-loop. If

power-up, the output remains in this condition until

CLR

CLR

is low at

is taken

high. The DAC registers can be programmed, and the outputs

assume the programmed values when

CLR

is high at power-up, the output remains in this condition

until V

> 6 V and VSS < −4 V and the initialization sequence has

DD

CLR

is taken high. Even if

finished. The outputs then go to their power-on default value.

TRANSFER FUNCTION

The output voltage of a DAC in the AD5362/AD5363 is dependent on the value in the input register, the value of the M and C

registers, and the value in the offset DAC.

AD5362 Transfer Function

The input code is the value in the X1A or X1B register that is

applied to the DAC (X1A, X1B default code = 32,768).

16

– 1.

15

.

16

+ C − 215

DAC_CODE = INPUT_CODE × (M + 1)/2

where:

M = code in gain register − default code = 2

C = code in offset register − default code = 2

The DAC output voltage is calculated as follows:

VOUT = 4 × VREF × (DAC_CODE − (OFFSET_CODE ×

16

4))/2

+ V

SIGGND

where:

DAC_CODE should be within the range of 0 to 65,535.

For 12 V span, VREF = 3.0 V.

For 20 V span, VREF = 5.0 V.

OFFSET_CODE is the code loaded to the offset DAC. It is

multiplied by 4 in the transfer function because this DAC is a

14-bit device. On power-up, the default code loaded to the

05762-022

offset DAC is 8192 (0x2000). With a 5 V reference, this gives

a span of −10 V to +10 V.

AD5363 Transfer Function

The input code is the value in the X1A or X1B register that is

applied to the DAC (X1A, X1B default code = 8192).

DAC_CODE = INPUT_CODE × (M + 1)/2

14

+ C − 213

where:

M = code in gain register − default code = 2

C = code in offset register − default code = 2

14

13

– 1.

.

The DAC output voltage is calculated as follows:

VOUT = 4 × VREF × (DAC_CODE − OFFSET_CODE)/

14

+ V

2

SIGGND

where:

DAC_CODE should be within the range of 0 to 16,383.

For 12 V span, VREF = 3.0 V.

For 20 V span, VREF = 5.0 V.

OFFSET_CODE is the code loaded to the offset DAC. On powerup, the default code loaded to the offset DAC is 8192 (0x2000).

With a 5 V reference, this gives a span of −10 V to +10 V.

REFERENCE SELECTION

The AD5362/AD5363 have two reference input pins. The

voltage applied to the reference pins determines the output

voltage span on VOUT0 to VOUT7. VREF0 determines the

voltage span for VOUT0 to VOUT3 (Group 0), and VREF1

determines the voltage span for VOUT4 to VOUT7 (Group 1).

The reference voltage applied to each VREF pin can be different, if required, allowing each group of four channels to have a

different voltage span. The output voltage range and span can

be adjusted further by programming the offset and gain

registers for each channel as well as programming the offset

DAC. If the offset and gain features are not used (that is, the M

and C registers are left at their default values), the required

reference levels can be calculated as follows:

VREF = (VOUT

− VOUT

MAX

If the offset and gain features of the AD5362/AD5363 are used,

the required output range is slightly different. The selected

output range should take into account the system offset and

gain errors that need to be trimmed out. Therefore, the selected

output range should be larger than the actual, required range.

The required reference levels can be calculated as follows:

1. Identify the nominal output range on VOUT.

2. Identify the maximum offset span and the maximum gain

required on the full output signal range.

3. Calculate the new maximum output range on VOUT,

including the expected maximum offset and gain errors.

4. Choose the new required VOUT

ing the VOUT limits centered on the nominal values. Note

that V

and VSS must provide sufficient headroom.

DD

5. Calculate the value of VREF as follows:

VREF = (VOUT

− VOUT

MAX

MIN

MIN

)/4

and VOUT

MAX

)/4

MIN

, keep-

Rev. A | Page 18 of 28

AD5362/AD5363

Reference Selection Example

If

Nominal output range = 20 V (−10 V to +10 V)

Offset error = ±100 mV

Gain error = ±3%, and

SIGGND = AGND = 0 V

Then

Gain error = ±3%

=> Maximum positive gain error = 3%

=> Output range including gain error = 20 + 0.03(20) = 20.6 V

Offset error = ±100 mV

=> Maximum offset error span = 2(100 mV) = 0.2 V

=> Output range including gain error and offset error =

20.6 V + 0.2 V = 20.8 V

VREF calculation

Actual output range = 20.6 V, that is, −10.3 V to +10.3 V

(centered);

VREF = (10.3 V + 10.3 V)/4 = 5.15 V

If the solution yields an inconvenient reference level, the user

can adopt one of the following approaches:

• Use a resistor divider to divide down a convenient, higher

reference level to the required level.

• Select a convenient reference level above VREF and modify

the gain and offset registers to digitally downsize the reference.

In this way, the user can use almost any convenient reference

level but can reduce the performance by overcompaction of

the transfer function.

• Use a combination of these two approaches.

CALIBRATION

The user can perform a system calibration on the AD5362/

AD5363 to reduce gain and offset errors to below 1 LSB. This

reduction is achieved by calculating new values for the M and

C registers and reprogramming them.

The M and C registers should not be programmed until both

the zero-scale and full-scale errors are calculated.

Reducing Zero-Scale Error

Zero-scale error can be reduced as follows:

1. Set the output to the lowest possible value.

2. Measure the actual output voltage and compare it to the

required value. This gives the zero-scale error.

3. Calculate the number of LSBs equivalent to the error and

add this number to the default value of the C register. Note

that only negative zero-scale error can be reduced.

Reducing Full-Scale Error

Full-scale error can be reduced as follows:

1. Measure the zero-scale error.

2. Set the output to the highest possible value.

3. Measure the actual output voltage and compare it to the

required value. Add this error to the zero-scale error. This

is the span error, which includes the full-scale error.

4. Calculate the number of LSBs equivalent to the span error

and subtract this number from the default value of the M

register. Note that only positive full-scale error can be

reduced.

AD5362 Calibration Example

This example assumes that a −10 V to +10 V output is required.

The DAC output is set to −10 V but measured at −10.03 V. This

gives a zero-scale error of −30 mV.

1 LSB = 20 V/65,536 = 305.176 μV

30 mV = 98 LSBs

The full-scale error can now be calculated. The output is set to

10 V and a value of 10.02 V is measured. This gives a full-scale

error of +20 mV and a span error of +20 mV – (–30 mV) =

+50 mV.

50 mV = 164 LSBs

The errors can now be removed as follows:

1. Add 98 LSBs to the default C register value:

(32,768 + 98) = 32,866

2. Subtract 164 LSBs from the default M register value:

(65,535 − 164) = 65,371

3. Program the M register to 65,371; program the C register

to 32,866.

ADDITIONAL CALIBRATION

The techniques described in the previous section are usually

enough to reduce the zero-scale and full-scale errors in most

applications. However, there are limitations whereby the errors

may not be sufficiently reduced. For example, the offset (C)

register can only be used to reduce the offset caused by the

negative zero-scale error. A positive offset cannot be reduced.

Likewise, if the maximum voltage is below the ideal value, that

is, a negative full-scale error, the gain (M) register cannot be

used to increase the gain to compensate for the error.

These limitations can be overcome by increasing the reference

value. With a 2.5 V reference, a 10 V span is achieved. The ideal

voltage range, for the AD5362 or the AD5363, is −5 V to +5 V.

Using a +2.6 V reference increases the range to −5.2 V to +5.2

Clearly, in this case, the offset and gain errors are insignificant,

and the M and C registers can be used to raise the negative

voltage to −5 V and then reduce the maximum voltage to +5 V

to give the most accurate values possible.

V.

Rev. A | Page 19 of 28

AD5362/AD5363

RESET FUNCTION

The reset function is initiated by the

RESET

edge of

, the AD5362/AD5363 state machine initiates a

reset sequence to reset the X, M, and C registers to their default

values. This sequence typically takes 300 μs, and the user should

not write to the part during this time. On power-up, it is recommended that the user bring

RESET

properly initialize the registers.

When the reset sequence is complete (and provided that

high), the DAC output is at a potential specified by the default

register settings, which is equivalent to SIGGNDx. The DAC

outputs remain at SIGGNDx until the X, M, or C register is

updated and

LDAC

is taken low. The AD5362/AD5363 can be

returned to the default state by pulsing

30 ns. Note that, because the reset function is triggered by the

rising edge, bringing

RESET

low has no effect on the operation

of the AD5362/AD5363.

RESET

pin. On the rising

high as soon as possible to

CLR

RESET

low for at least

is

CLEAR FUNCTION

CLR

is an active low input that should be high for normal

operation. The

resistor. When

CLR

pin has an internal 500 kΩ pull-down

CLR

is low, the input to each of the DAC output

buffer stages (VOUT0 to VOUT7) is switched to the externally

set potential on the relevant SIGGNDx pin. While

all

LDAC

pulses are ignored. When

CLR

is taken high again,

CLR

is low,

the DAC outputs return to their previous values. The contents

of the input registers and DAC Register 0 to DAC Register 7 are

not affected by taking

on the outputs,

CLR

low. To prevent glitches appearing

CLR

should be brought low whenever the

output span is adjusted by writing to the offset DAC.

BUSY AND LDAC FUNCTIONS

The value of an X2 (A or B) register is calculated each time the

user writes new data to the corresponding X1, C, or M registers.

During the calculation of X2, the

BUSY

is low, the user can continue writing new data to the X1,

M, or C registers (see the section for

Register Update Rates

more details), but no DAC output updates can take place.

BUSY

The

pin is bidirectional and has a 50 kΩ internal pull-up

resistor. When multiple AD5362 or AD5363 devices are used in

one system, the

BUSY

pins can be tied together. This is useful

when it is required that no DAC in any device be updated until

all other DACs are ready. When each device has finished updating the X2 (A or B) registers, it releases the

another device has not finished updating its X2 registers, it

BUSY

holds

low, thus delaying the effect of

BUSY

output goes low. While

BUSY

LDAC

pin. If

going low.

The DAC outputs are updated by taking the

LDAC

goes low while

BUSY

is active, the

and the DAC outputs are updated immediately after

high. A user can also hold the

LDAC

this case, the DAC outputs update immediately after

high. Whenever the A/B select registers are written to,

also goes low, for approximately 600 ns.

The AD5362/AD5363 have flexible addressing that allows

writing of data to a single channel, all channels in a group, or

all channels in the device. This means that one, two, four, or

eight DAC register values may need to be calculated and

updated. Because there is only one multiplier shared between

eight channels, this task must be done sequentially, so the

length of the

BUSY

pulse varies according to the number of

channels being updated.

BUSY

Table 9.

Action

Loading input, C, or M to 1 channel2 1.5 μs maximum

Loading input, C, or M to 2 channels 2.1 μs maximum

Loading input, C, or M to 8 channels 5.7 μs maximum

1

BUSY

pulse width = ((number of channels + 1) × 600 ns) + 300 ns.

2

A single channel update is typically 1 μs.

Pulse Widths

The AD5362/AD5363 contain an extra feature whereby a DAC

register is not updated unless its X2A or X2B register has been

written to since the last time

LDAC

when

is brought low, the DAC registers are filled with

LDAC

was brought low. Normally,

the contents of the X2A or X2B registers, depending on the

setting of the A/B select registers. However, the AD5362/

AD5363 update the DAC register only if the X2A or X2B data

has changed, thereby removing unnecessary digital crosstalk.

BIN/2SCOMP PIN

BIN

The

/2SCOMP pin determines if the output data is presented

as offset binary or twos complement. If this pin is low, the data

is straight binary. If it is high, the data is twos complement. This

affects only the X, C, and offset DAC registers; the M register and

the control and command data are interpreted as straight binary.

TEMPERATURE SENSOR

The on-chip temperature sensor provides a voltage output

at the TEMP_OUT pin that is linearly proportional to the

Centigrade temperature scale. The typical accuracy of the

temperature sensor is +1°C at +25°C and ±5°C over the −40°C

to +85°C range. Its nominal output voltage is 1.46 V at 25°C,

varying at 4.4 mV/°C. Its low output impedance, low selfheating, and linear output simplify interfacing to temperature

control circuitry and analog-to-digital converters.

LDAC

input low. If

LDAC

event is stored

BUSY

goes

input permanently low. In

BUSY

goes

BUSY

Pulse Width1

BUSY

Rev. A | Page 20 of 28

AD5362/AD5363

MONITOR FUNCTION

The AD5362/AD5363 contain a channel monitor function

that consists of an analog multiplexer addressed via the serial

interface, allowing any channel output to be routed to the

MON_OUT pin for monitoring using an external ADC. In

addition, two monitor inputs, MON_IN0 and MON_IN1,

are provided, which can also be routed to MON_OUT. The

monitor function is controlled by the monitor register, which

allows the monitor output to be enabled or disabled, and selects

a DAC channel or one of the monitor pins. When disabled, the

monitor output is high impedance so that several monitor

outputs can be connected in parallel with only one enabled at

a time. Table 1 0 shows the monitor register settings.

Table 10. Monitor Register Functions

F5 F4 F3 F2 F1 F0 Function

0 X X X X X MON_OUT disabled

1 X X X X X MON_OUT enabled

1 0 0 0 0 0 MON_OUT = VOUT0

1 0 0 0 0 1 MON_OUT = VOUT1

1 0 0 0 1 0 MON_OUT = VOUT2

1 0 0 0 1 1 MON_OUT = VOUT3

1 0 1 0 0 0 MON_OUT = VOUT4

1 0 1 0 0 1 MON_OUT = VOUT5

1 0 1 0 1 0 MON_OUT = VOUT6

1 0 1 0 1 1 MON_OUT = VOUT7

1 1 0 0 0 0 MON_OUT = MON_IN0

1 1 0 0 0 1 MON_OUT = MON_IN1

The multiplexer is implemented as a series of analog switches.

Because this could conceivably cause a large amount of current

to flow from the input of the multiplexer (VOUTx or MON_INx)

to the output of the multiplexer (MON_OUT), care should be

taken to ensure that whatever is connected to the MON_OUT

pin is of high enough impedance to prevent the continuous

current limit specification from being exceeded. Because the

MON_OUT pin is not buffered, the amount of current drawn

from this pin creates a voltage drop across the switches, which

in turn leads to an error in the voltage being monitored. Where

accuracy is important, it is recommended that the MON_OUT

pin be buffered. Figure 20 shows the typical error due to

MON_OUT current.

GPIO PIN

The AD5362/AD5363 have a general-purpose I/O pin, GPIO.

This pin can be configured as an input or an output and read

back or programmed (when configured as an output) via the

serial interface. Typical applications for this pin include monitoring the status of a logic signal, a limit switch, or controlling

an external multiplexer. The GPIO pin is configured by writing

to the GPIO register, which has the special function code of

001101 (see Table 15 and Tabl e 16).

When Bit F1 is set, the GPIO pin becomes an output and Bit F0

determines whether the pin is high or low. The GPIO pin can be

set as an input by writing 0 to both Bit F1 and Bit F0. The status

of the GPIO pin can be determined by initiating a read operation

using the appropriate bits in Table 17. The status of the pin is

indicated by the LSB of the register read.

POWER-DOWN MODE

The AD5362/AD5363 can be powered down by setting Bit 0 in

the control register to 1. This turns off the DACs, thus reducing

the current consumption. The DAC outputs are connected to

their respective SIGGNDx potentials. The power-down mode

does not change the contents of the registers, and the DACs

return to their previous voltage when the power-down bit is

cleared to 0.

THERMAL SHUTDOWN FUNCTION

The AD5362/AD5363 can be programmed to shut down the

DACs if the temperature on the die exceeds 130°C. Setting Bit 1

in the control register to 1 enables this function (see Tabl e 16 ).

If the die temperature exceeds 130°C, the AD5362/AD5363

enter a thermal shutdown mode, which is equivalent to setting

the power-down bit in the control register. To indicate that the

AD5362/AD5363 have entered thermal shutdown mode, Bit 4

of the control register is set to 1. The AD5362/AD5363 remain

in thermal shutdown mode, even if the die temperature falls,

until Bit 1 in the control register is cleared to 0.

TOGGLE MODE

The AD5362/AD5363 have two X2 registers per channel, X2A

and X2B, which can be used to switch the DAC output between

two levels with ease. This approach greatly reduces the overhead

required by a microprocessor, which would otherwise need to

write to each channel individually. When the user writes to the

X1A, X1B, M, or C register, the calculation engine takes a certain

amount of time to calculate the appropriate X2A or X2B value.

If an application, such as a data generator, requires that the DAC

output switch between two levels only, any method that reduces

the amount of calculation time necessary is advantageous. For

the data generator example, the user needs only to set the high

and low levels for each channel once by writing to the X1A and

X1B registers. The values of X2A and X2B are calculated and

stored in their respective registers. The calculation delay,

therefore, happens only during the setup phase, that is, when

programming the initial values. To toggle a DAC output between

the two levels, it is only required to write to the relevant A/B

select register to set the MUX2 register bit. Furthermore,

because there are four MUX2 control bits per register, it is

possible to update eight channels with just two writes. Tab le 1 8

shows the bits that correspond to each DAC output.

Rev. A | Page 21 of 28

AD5362/AD5363

SERIAL INTERFACE

The AD5362/AD5363 contain a high speed SPI operating at

clock frequencies up to 50 MHz (20 MHz for read operations).

To minimize both the power consumption of the device and

on-chip digital noise, the interface powers up fully only when

the device is being written to, that is, on the falling edge of

SYNC

. The serial interface is 2.5 V LVTTL-compatible when

operating from a 2.5 V to 3.6 V DV

four pins:

SYNC

(frame synchronization input), SDI (serial data

supply. It is controlled by

CC

input pin), SCLK (clocks data in and out of the device), and

SDO (serial data output pin for data readback).

SPI WRITE MODE

The AD5362/AD5363 allow writing of data via the serial interface to every register directly accessible to the serial interface,

that is, all registers except the X2A, X2B, and DAC registers.

The X2A and X2B registers are updated when writing to the

X1A, X1B, M, and C registers, and the DAC data registers are

updated by

is 24 bits long: 16 (AD5362) or 14 (AD5363) of these bits are

data bits; six bits are address bits; and two bits are mode bits

that determine what is done with the data. Two bits are reserved

on the AD5363.

The serial interface works with both a continuous and a burst

(gated) serial clock. Serial data applied to SDI is clocked into

the AD5362/AD5363 by clock pulses applied to SCLK. The first

falling edge of

clock edges must be applied to SCLK to clock in 24 bits of data

before

the 24th falling clock edge, the write operation is aborted.

If a continuous clock is used,

25th falling clock edge. This inhibits the clock within the AD5362/

AD5363. If more than 24 falling clock edges are applied before

SYNC

If an externally gated clock of exactly 24 pulses is used,

can be taken high any time after the 24th falling clock edge.

LDAC

. The serial word (see or )

SYNC

starts the write cycle. At least 24 falling

SYNC

is taken high again. If

SYNC

Table 1 1 Table 12

SYNC

is taken high before

must be taken high before the

is taken high again, the input data becomes corrupted.

SYNC

The input register addressed is updated on the rising edge of

SYNC

. For another serial transfer to take place,

SYNC

must be

taken low again.

SPI READBACK MODE

The AD5362/AD5363 allow data readback via the serial

interface from every register directly accessible to the serial

interface, that is, all registers except the X2A, X2B, and DAC

data registers. To read back a register, it is first necessary to

tell the AD5362/AD5363 which register is to be read. This is

achieved by writing a word whose first two bits are the Special

Function Code 00 to the device. The remaining bits then

determine which register is to be read back.

If a readback command is written to a special function register,

data from the selected register is clocked out of the SDO pin

during the next SPI operation. The SDO pin is normally threestated but becomes driven as soon as a read command is issued.

The pin remains driven until the register data is clocked out.

See Figure 5 for the read timing diagram. Note that due to the

timing requirements of t

(25 ns), the maximum speed of the

22

SPI interface during a read operation should not exceed 20 MHz.

REGISTER UPDATE RATES

The value of the X2A register or the X2B register is calculated

each time the user writes new data to the corresponding X1, C,

or M register. The calculation is performed by a three-stage

process. The first two stages take approximately 600 ns each, and

the third stage takes approximately 300 ns. When the write to an

X1, C, or M register is complete, the calculation process begins.

If the write operation involves the update of a single DAC

channel, the user is free to write to another register, provided

that the write operation does not finish until the first-stage

calculation is complete, that is, 600 ns after the completion of

the first write operation. If a group of channels is being updated

by a single write operation, the first-stage calculation is repeated

for each channel, taking 600 ns per channel. In this case, the

user should not complete the next write operation until this time

has elapsed.

Table 11. AD5362 Serial Word Bit Assignment

I23 I22 I21 I20 I19 I18 I17 I16 I15 I14 I13 I12 I11 I10 I9 I8 I7 I6 I5 I4 I3 I2 I1 I0

M1 M0 A5 A4 A3 A2 A1 A0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Table 12. AD5363 Serial Word Bit Assignment

I23 I22 I21 I20 I19 I18 I17 I16 I15 I14 I13 I12 I11 I10 I9 I8 I7 I6 I5 I4 I3 I2 I11I0

M1 M0 A5 A4 A3 A2 A1 A0 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 0 0

1

Bit I1 and Bit I0 are reserved for future use and should be 0 when writing the serial word. These bits read back as 0.

Rev. A | Page 22 of 28

1

AD5362/AD5363

PACKET ERROR CHECKING

To verify that data has been received correctly in noisy environments, the AD5362/AD5363 offer the option of error checking

based on an 8-bit (CRC-8) cyclic redundancy check. The device

controlling the AD5362/AD5363 should generate an 8-bit

checksum using the polynomial C(x) = x

added to the end of the data-word, and 32 data bits are sent to

the AD5362/AD5363 before taking

AD5363 see a 32-bit data frame, an error check is performed

SYNC

when

goes high. If the checksum is valid, the data is

written to the selected register. If the checksum is invalid, the

packet error check (

PEC

) output goes low and Bit 3 of the

control register is set. After reading the control register, Bit 3

is cleared automatically and

SYNC

SCLK

SDI

MSB

D23

UPDATE ON SYNC HIG H

24-BIT DATA T RANSFER—NO ERRO R CHECKING

PEC

24-BIT DATA

goes high again.

8

+ x2 + x1 + 1. This is

SYNC

high. If the AD5362/

LSB

D0

CHANNEL ADDRESSING AND SPECIAL MODES

If the mode bits are not 00, the data-word D15 to D0 (AD5362)

or D13 to D0 (AD5363) is written to the device. Address Bit A4

to Address Bit A0 determine which channels are written to, and

the mode bits determine to which register (X1A, X1B, C, or M)

the data is written, as shown in Table 13 and Tabl e 14. Data is to

be written to the X1A register when the

register is 0, or to the X1B register when the

The AD5362/AD5363 have very flexible addressing that allows

the writing of data to a single channel, all channels in a group,

or all channels in the device.

Table 14 shows which groups and which channels are addressed

for every combination of Address Bit A4 to Address Bit A0.

Table 13. Mode Bits

M1 M0 Action

1 1 Write to DAC data (X) register

1 0 Write to DAC offset (C) register

0 1

0 0

Write to DAC gain (M) register

Special function, used in combination with other

bits of the data-word

A

/B bit in the control

A

/B bit is 1.

UPDATE AFTER S YNC HIGH

SYNC

SCLK

SDI

PEC

MSB

D31

24-BIT DATA

24-BIT DATA T RANSFER WIT H ERROR CHECKING

Figure 24. SPI Write With and Without Error Checking

ONLY IF ERROR CHECK PASSED

LSB

D7 D0

D8

8-BIT FCS

PEC GOES LOW IF

ERROR CHECK FAIL S

05762-026

Table 14. Group and Channel Addressing

Address Bit A2

to Address Bit A0

00 01 10 11

Address Bit A4 to Address Bit A3

000 All groups, all channels Group 0, Channel 0 Group 1, Channel 0 Unused

001 Group 0, all channels Group 0, Channel 1 Group 1, Channel 1 Unused

010 Group 1, all channels Group 0, Channel 2 Group 1, Channel 2

011 Unused Group 0, Channel 3 Group 1, Channel 3

100 Unused Unused Unused

101 Unused Unused Unused

110 Unused Unused Unused

Unused

Unused

Unused

Unused

Unused

111 Unused Unused Unused Unused

Rev. A | Page 23 of 28

AD5362/AD5363

SPECIAL FUNCTION MODE

If the mode bits are 00, the special function mode is selected, as shown in Table 15. Bit I21 to Bit I16 of the serial data-word select the

special function, and the remaining bits are data required for execution of the special function, for example, the channel address for data

readback. The codes for the special functions are shown in Table 1 6. Table 1 7 shows the addresses for data readback.

Table 15. Special Function Mode

I23 I22 I21 I20 I19 I18 I17 I16 I15 I14 I13 I12 I11 I10 I9 I8 I7 I6 I5 I4 I3 I2 I1 I0

0 0 S5 S4 S3 S2 S1 S0 F15 F14 F13 F12 F11 F10 F9 F8 F7 F6 F5 F4 F3 F2 F1 F0

Table 16. Special Function Codes