2.5 V to 5.5 V, 500 μA, Quad Voltage Output

AD5324-EP

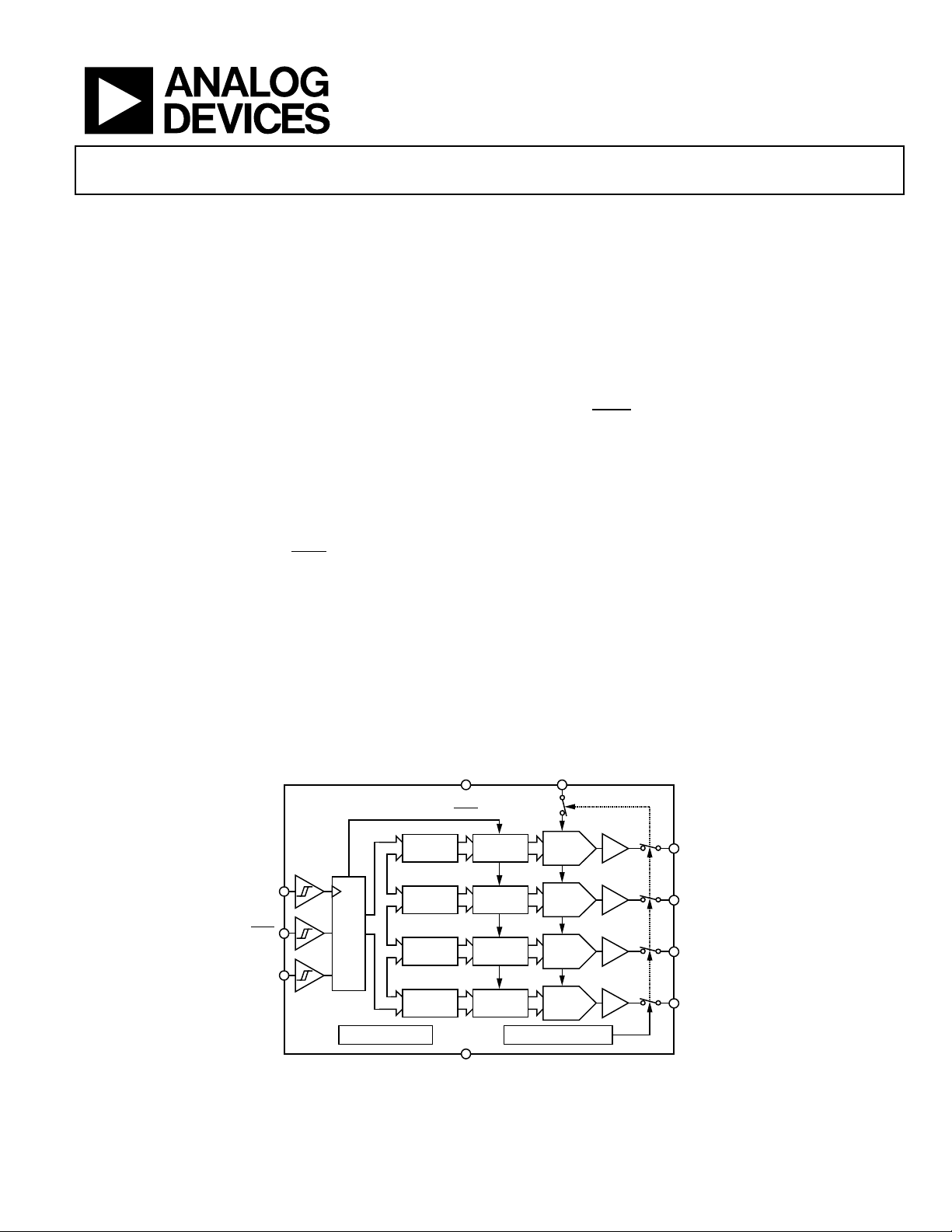

INPUT

REGISTER

DAC

REGISTER

STRING

DAC A

V

OUT

A

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC B

V

OUT

B

BUFFER

AD5324-EP

INPUT

REGISTER

DAC

REGISTER

STRING

DAC C

V

OUT

C

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC D

V

OUT

D

BUFFER

REFINV

DD

GND

POWER-DOWN LOGICPOWER-ON RESET

LDAC

INTERFACE

LOGIC

SCLK

SYNC

DIN

08971-001

FEATURES

Enhanced product features

Supports defense and aerospace applications (AQEC)

Military temperature range (−55°C to +125°C)

Controlled manufacturing baseline

One assembly/test site

One fabrication site

Enhanced product change notification

Qualification data available on request

4 buffered 12-Bit DACs in 10-lead MSOP

S Version: ±10 LSB INL

Low power operation: 500 μA @ 3 V, 600 μA @ 5 V

2.5 V to 5.5 V power supply

Guaranteed monotonic by design over all codes

Power-down to 80 nA @ 3 V, 200 nA @ 5 V

Double-buffered input logic

Output range: 0 V to V

Power-on reset to 0 V

Simultaneous update of outputs (

On-chip, rail-to-rail output buffer amplifiers

Temperature range –55°C to +125°C

APPLICATIONS

Portable battery-powered instruments

Digital gain and offset adjustment

Programmable voltage and current sources

Programmable attenuators

Industrial process control

REF

LDAC

function)

12-Bit DAC in 10-Lead Package

GENERAL DESCRIPTION

The AD5324-EP1 is a quad 12-bit buffered voltage output DAC

in a 10-lead MSOP package that operates from a single 2.5 V to

5.5 V supply, consuming 500 μA a t 3 V. Its on-chip output

amplifiers allows rail-to-rail output swing to be achieved with a

slew rate of 0.7 V/μs. A 3-wire serial interface is used; it operates

at clock rates up to 30 MHz and is compatible with standard SPI,

QSPI™, MICROWIRE™, and DSP interface standards.

The references for the four DACs are derived from one reference

pin. The outputs of all DACs can be updated simultaneously using

the software

reset circuit, and ensures that the DAC outputs power up to 0 V

and remains there until a valid write takes place to the device.

The part contains a power-down feature that reduces the current

consumption of the device to 200 nA at 5 V (80 nA at 3 V).

The low power consumption of this part in normal operation

makes it ideally suited to portable battery-operated equipment. The

power consumption is 3 mW at 5 V, and 1.5 mW at 3 V, reducing

to 1 μW in power-down mode.

Full details about this enhanced product are available in the

AD5324 data sheet, which should be consulted in conjunction

with this data sheet.

1

Protected by U.S. Patent No. 5,969,657; other patents pending.

LDAC

function. The part incorporates a power-on

FUNCTIONAL BLOCK DIAGRAM

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

www.analog.com

Loading...

Loading...