Datasheet AD5282BRU50, AD5282BRU200, AD5280BRU50, AD5280BRU200, AD5280BRU20 Datasheet (Analog Devices)

PRELIMINARY TECHNICAL DATA

+15V, I2C Compatible

a

Digital Potentiometers

Preliminary Technical Data AD5280/AD5282

FEATURES

256 Position

AD5280 – 1-Channel

AD5282 – 2-Channel (Independently Programmable)

Potentiometer Replacement

20K, 50K, 200K Ohm with TC < 50ppm/ºC

Internal Power ON Mid-Scale Preset

+5 to +15V Single-Supply; ±5.5V Dual-Supply Operation

2

I

C Compatible Interface

APPLICATIONS

Multi-Media, Video & Audio

Communications

Mechanical Potentiometer Replacement

Instrumentation: Gain, Offset Adjustment

Programmable Voltage to Current Conversion

Line Impedance Matching

GENERAL DESCRIPTION

The AD5280/AD5282 provides a single/dual channel, 256 position

digitally-controlled variable resistor (VR) device. These devices

perform the same electronic adjustment function as a

potentiometer, trimmer or variable resistor. Each VR offers a

completely programmable value of resistance, between t he A

terminal and the wiper, or the B terminal and the wiper. The fixed

A-to-B terminal resistance of 20, 50 or 200K ohms has a 1%

channel-to-channel matching tolerance with a nominal temperature

coefficient of 30 ppm/°C.

Wiper Position programming defaults to midscale at system power

ON. Once powered the VR wiper position is programmed by a I

2

C

compatible 2-wire serial data interface. Both parts have two

programmable logic outputs available to drive digital loads, gates,

LED drivers, analog switches, etc.

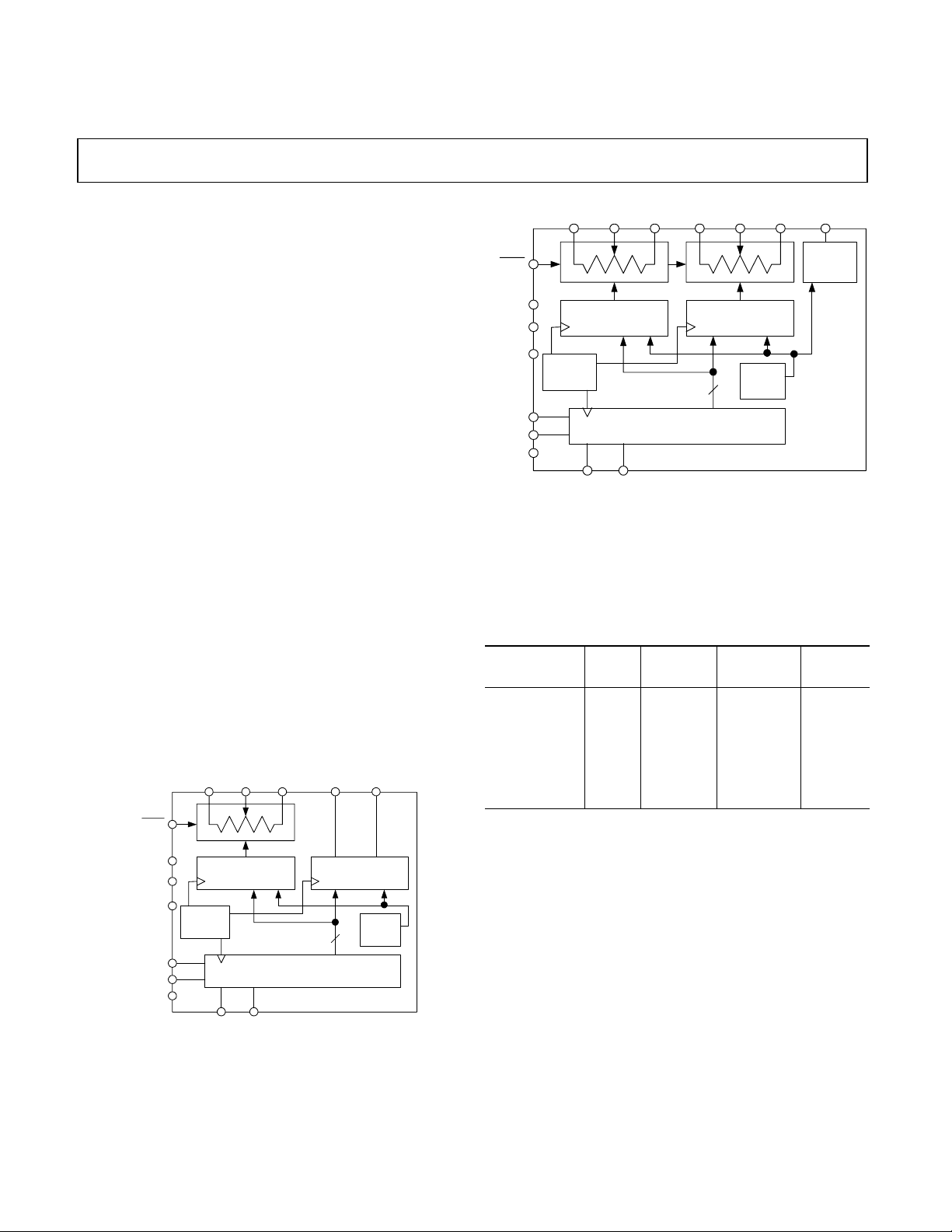

FUNCTIONAL BLOCK DIAGRAMS

SHDN

V

V

SCL

SDA

GND

A

W1B

1

DD

SS

V

L

RDAC1 REGISTER

ADDRESS

DECODE

1

RR

RDAC2 REGISTER

AD5280

SERIAL INPUT REGISTER

O

O

1

2

PWR ON

RESET

8

SHDN

V

DD

V

SS

V

L

SCL

SDA

GND

The AD5280/AD5282 are available in ultra compact surface mount

thin TSSOP-14/-16 packages. All parts are guarant eed to operate

over the extended industrial temperature range of -40°C to +85°C.

For 3-wire, SPI compatibl e i nterface applications, see

AD5203/AD5204/AD5206/AD7376/AD8400/AD8402/AD8403/

AD5260/AD5262/AD5200/AD5201 products.

Kilo Package Package

Model Ohms Temp Description Option

AD5280BRU20 20 -40/+85°C TSSOP-14 RU-14

AD5280BRU50 50 -40/+85°C TSSOP-14 RU-14

AD5280BRU200 200 -40/+85°C TSSOP-14 RU-14

AD5282BRU20 20 -40/+85°C TSSOP-16 RU-16

AD5282BRU50 50 -40/+85°C TSSOP-16 RU-16

AD5282BRU200 200 -40/+85°C TSSOP-16 RU-16

The AD5280/AD5282 die size is 75 mil X 120 mil, 9,000 sq. mil.

Contains xxx transistors. Patent Number xxx ap plies.

A

1

RDAC1 REGISTER

ADDRESS

DECODE

AD0 AD1

W

B

A

W

1

1

2

RR

AD5282

SERIAL INP UT REGISTER

RDAC2 REGISTER

8

2

PWR ON

RESET

B

2

ORDERING GUIDE

O

1

OUTPUT

REGISTER

R

AD0 AD1

REV PrE 12 MAR 02

Information furnished by Analog Devices is beli ev ed to be acc ur ate and r el i abl e. However, no

responsibility is assumed by Analog Devices for its use; nor for any infringements of patents

or other rights of third parties which may result from its use. No license is granted by

implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106,

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 ©Analog Devices, Inc., 2002

Norwood, MA 02062-9106 U.S.A.

PRELIMINARY TECHNICAL DATA

AD5280/AD5282

(V

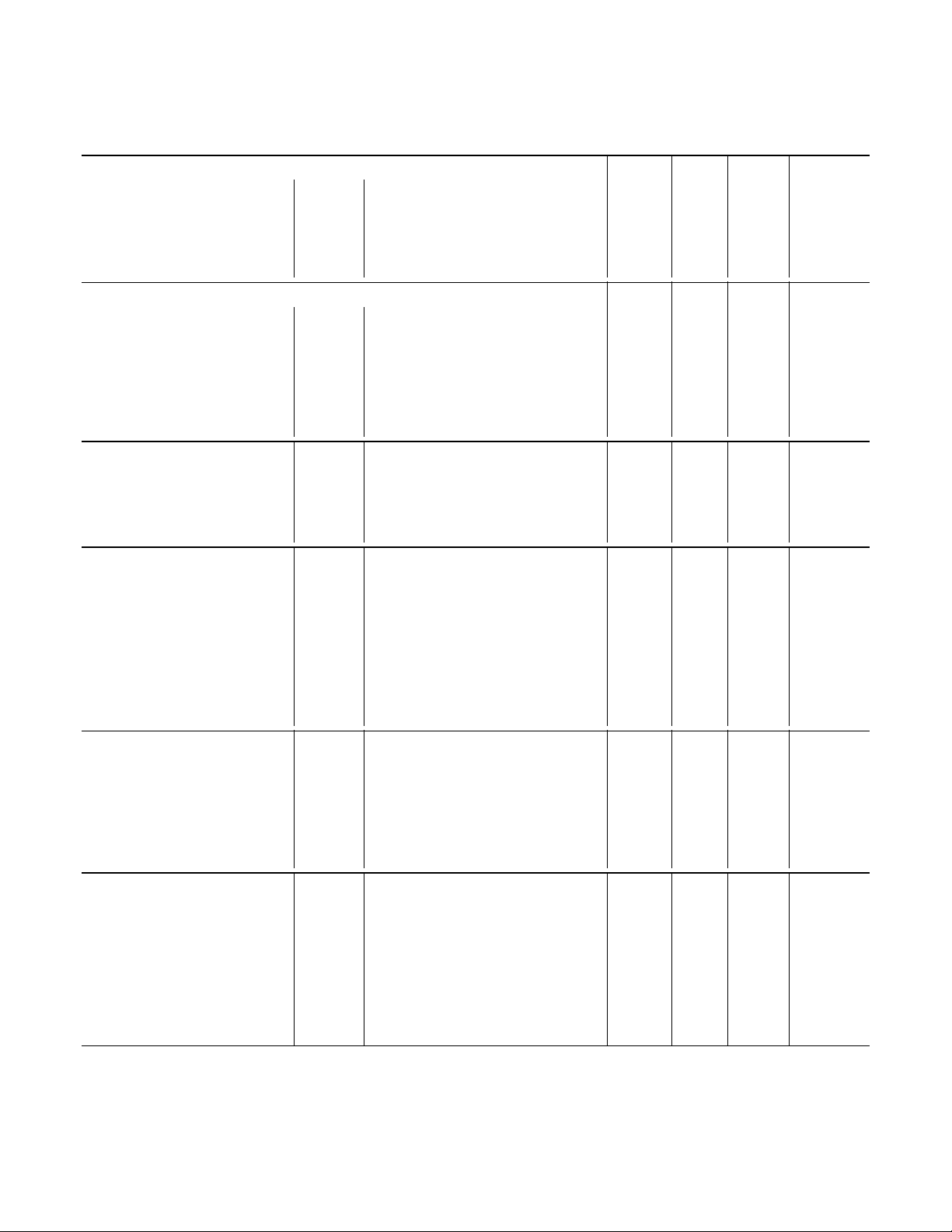

ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION

V

= +VDD, VB = 0V, -40°C < T

A

< +85°C unless otherwise noted.)

A

= +5V, VSS = -5V, V

DD

Parameter Symbol Conditions Min Typ1 Max Units

DC CHARACTERISTICS RHEOSTAT MODE Specifications apply to all VRs

Resistor Differential NL2 R-DNL RWB, VA=NC -1 ±0.4 +1 LSB

Resistor Nonlinearity2 R-INL RWB, VA=NC -1 ±0.5 +1 LSB

Nominal resistor tolerance3 ∆R TA = 25°C -30 30 %

Resistance Temperature Coefficient RAB/∆T V

Wiper Resistance RW I

= VDD, Wiper = No Connect 30 ppm/°C

AB

= VDD /R, VDD = +3V or +5V 40 100 Ω

W

DC CHARACTERISTICS POTENTIOMETER DIVIDER MODE Specifications apply to all VRs

Resolution N 8 Bits

Integral Nonlinearity4 INL RAB=20KΩ, 50KΩ –1 ±0.5 +1 LSB

Integral Nonlinearity4 INL RAB=200KΩ –2 ±0.5 +2 LSB

Differential Nonlinearity4 DNL –1 ±0.4 +1 LSB

Voltage Divider Temperature Coefficient ∆VW/∆T Code = 80H 5 ppm/°C

Full-Scale Error V

Zero-Scale Error V

Code = FFH –1 -0.5 +0 LSB

WFSE

Code = 00H 0 +0.5 +1 LSB

WZSE

RESISTOR TERMINALS

Voltage Range5 V

Capacitance6 A, B C

VSS V

A,B,W

f = 1 MHz, measured to GND, Code = 80H 45 pF

A,B

V

DD

Capacitance6 W CW f = 1 MHz, measured to GND, Code = 80H 60 pF

Common Mode Leakage ICM V

= VB = VW 1 nA

A

DIGITAL INPUTS

Input Logic High VIH SDA & SCL 0.7V

Input Logic Low VIL SDA & SCL -0.5 0.3V

Input Logic High VIH AD0 & AD1 2.4 V

V

LOGIC

+0.5 V

LOGIC

V

LOGIC

V

LOGIC

Input Logic Low VIL AD0 & AD1 0 0.8 V

Input Logic High VIH V

Input Logic Low VIL V

Input Current IIL V

Input Capacitance6 C

3 pF

IL

= +3V, AD0 & AD1 2.1 V

LOGIC

= +3V, AD0 & AD1 0 0.6 V

LOGIC

= 0V or +5V ±1 µA

IN

V

LOGIC

DIGITAL Output

O1, O2 VOH I

O1, O2 VOL I

SDA VOL I

SDA VOL I

Three-State Leakage Current IOZ V

Output Capacitance6 C

3 8 pF

OZ

=0.4mA 2.4 5.5 V

OH

=-1.6mA 0 0.4 V

OL

= -6mA 0.6 V

OL

= -3mA 0.4 V

OL

= 0V or +5V ±1 µA

IN

POWER SUPPLIES

Logic Supply V

Power Single-Supply Range V

Power Dual-Supply Range V

Logic Supply Current I

Positive Supply Current IDD V

+2.7 +5.5 V

LOGIC

VSS = 0V +5 +15 V

DD RANGE

DD/SS RANGE

LOGIC

±4.5 ±5.5 V

V

= +5V 10 µA

LOGIC

= +5V or VIL = 0V 20 60 µA

IH

Negative Supply Current ISS 20 60 µA

Power Dissipation10 P

VIH = +5V or VIL = 0V, VDD = +5V, VSS = -5V 0.2 0.6 mW

DISS

Power Supply Sensitivity PSS 0.05 0.015 %/%

LOGIC

= +5V,

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

2 REV PrE 12 MAR 02

PRELIMINARY TECHNICAL DATA

AD5280/AD5282

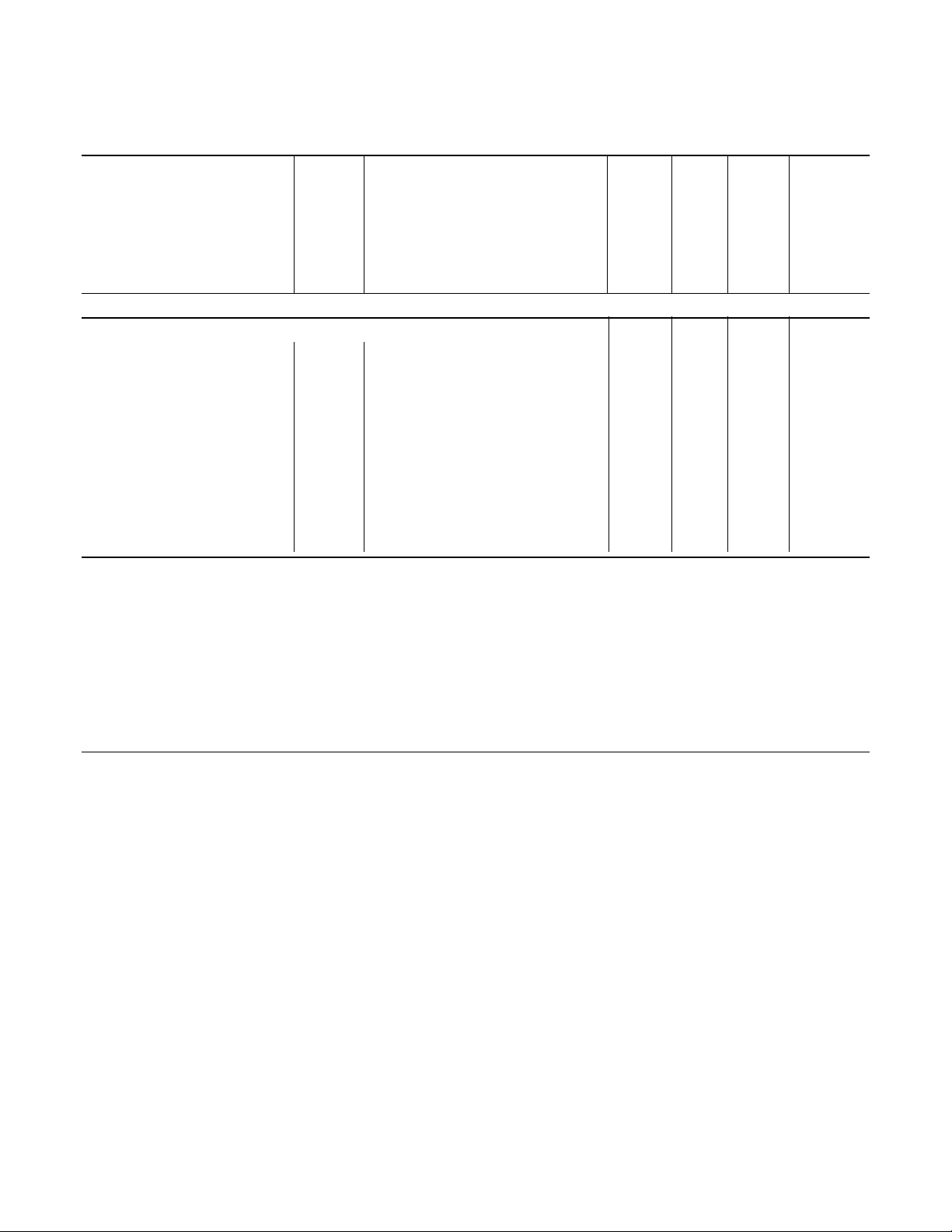

(V

ELECTRICAL CHARACTERISTICS 20K, 50K, 200K OHM VERSION

V

= +VDD, VB = 0V, -40°C < T

A

< +85°C unless otherwise noted.)

A

= +5V, VSS = -5V, V

DD

Parameter Symbol Conditions Min Typ1 Max Units

6,9,11

DYNAMIC CHARACTERISTICS

Bandwidth –3dB BW_20K RAB = 20KΩ, Code = 80H 650 kHz

BW_50K RAB = 50KΩ, Code = 80H 142 kHz

BW_200K RAB = 200KΩ, Code = 80H 69 kHz

Total Harmonic Distortion THDW VA =1Vrms + 2V dc, VB = 2V DC, f=1KHz 0.005 %

VW Settling Time tS V

Resistor Noise Voltage e

RWB = 10KΩ, f = 1KHz 14 nV√Hz

N_WB

= VDD, VB=0V, ±1 LSB error band 2 µs

A

INTERFACE TIMING CHARACTERISTICS applies to all parts(Notes 6,12)

SCL Clock Frequency f

t

Bus free time between STOP & START t1 1.3 µs

BUF

t

Hold Time (repeated START) t2 After this period the first clock pulse is generated 0.6 µs

HD;STA

t

Low Period of SCL Clock t3 1.3 µs

LOW

t

High Period of SCL Clock t4 0.6 µs

HIGH

t

Setup Time For START Condition t5 0.6 µs

SU;STA

t

Data Hold Time t6 0 0.9 µs

HD;DAT

t

Data Setup Time t7 100 ns

SU;DAT

tF Fall Time of both SDA & SCL signals t8 300 ns

tR Rise Time of both SDA & SCL signals t9 300 ns

t

Setup time for STOP Condition t10 0.6 µs

SU;STO

NOTES:

1. Typicals represent average readings at +25°C, VDD = +5V, VSS = -5V.

2. Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the

relative step change from ideal between successive tap positions. Parts are guaranteed monotonic.

3. V

= VDD, Wiper (VW) = No connect

AB

4. INL and DNL are measured at V

DNL specification limits of ±1LSB maximum are Guaranteed Monotonic operating conditions.

5. Resistor terminals A,B,W have no limitations on polarity with respect to each other.

6. Guaranteed by design and not subject to production test.

9. Bandwidth, noise and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R value

result in the minimum overall power consumption.

10. P

11. All dynamic characteristics use V

12. See timing diagram for location of measured values.

is calculated from (IDD x VDD). CMOS logic level inputs result in minimum power dissipation.

DISS

with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0V.

W

= +5V.

DD

0 400 KHz

SCL

LOGIC

= +5V,

REV PrE 12 MAR 02 3

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

PRELIMINARY TECHNICAL DATA

N

N

N

N

N

AD5280/AD5282

ABSOLUTE MAXIMUM RATINGS (TA = +25°C, unless otherwise noted)

V

to GND ............................................................. -0.3, +15V

DD

to GND ..................................................................0V, -7V

V

SS

to VSS ...................................................................... +15V

V

DD

, VB, VW to GND ...................................................VSS, VDD

V

A

– BX, AX – WX, BX – WX.........................................±20mA

A

X

Digital Input Voltage to GND.........................................0V, 7V

Operating Temperature Range...........................-40°C to +85°C

Thermal Resistance

TSSOP-14........................................................206°C/W

TSSOP-16........................................................180°C/W

Maximum Junction Temperature (T

Storage Temperature........................................-65°C to +150°C

Lead Temperature

RU-14, RU-16 (Vapor Phase, 60 sec) ....................... +215°C

RU-14, RU-16 (Infrared, 15 sec) ..............................+220°C

*

θ

JA,

MAX)....................+150°C

J

*

Package Power Dissipation (TJMAX - TA) / θJA

AD5280 PIN CONFIGURATION

SHD

SHDN

SHDNSHD

W

V

DD

SCL

SDA

1

A

2

3

B

4

5

6

7

14

13

12

11

10

9

8

O1

V

L

O2

V

SS

GND

AD1

AD0

AD5282 PIN CONFIGURATION

V

SHD

SHD

SHDNSHD

SCL

SDA

O1

A1

W1

B1

DD

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

A2

W2

B2

V

L

V

SS

GND

AD1

AD0

TABLE 1: AD5280 PIN Function Descriptions

Pin Name Description

1 A Resistor terminal A

2 W Wiper terminal W

3 B Resistor terminal B

4 V

Positive power supply, specified for

DD

operation from +5 to +15V.

5 SHDN Active Low, Asynchronous connection of

the wiper W to terminal B, and open

circuit of terminal A. RDAC register

contents unchanged.

6 SCL Serial Clock Input

7 SDA Serial Data Input/Output

8 AD0 Programmable address bit for multiple

package decoding. Bits AD0 & AD1

provide 4 possible addresses.

9 AD1 Programmable address bit for multiple

package decoding. Bits AD0 & AD1

provide 4 possible addresses.

10 GND Common Ground

11 V

Negative power supply, specified for

SS

operation from 0 to -5V

12 O2 Logic Output terminal O2

13 V

Logic Supply Voltage, needs to be same

L

voltage as the digital logic controlling the

AD5280.

14 O1 Logic Output terminal O1

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

4 REV PrE 12 MAR 02

PRELIMINARY TECHNICAL DATA

TABLE 2: AD5282 PIN Function Descriptions

Pin Name Description

1 O1 Logic Output terminal O1

2 A

3 W1 Wiper terminal W

4 B1 Resistor terminal B1

5 V

6 SHDN Active Low, Asynchronous connection of

7 SCL Serial Clock Input

8 SDA Serial Data Input/Output

Resistor terminal A

1

Positive power supply, specified for

DD

1

1

operation from +5 to +15V.

the wiper W to terminal B, and open

circuit of terminal A. RDAC register

contents unchanged.

t

8

SDA

t

1

t

8

AD5280/AD5282

9 AD0 Programmable address bit for multiple

package decoding. Bits AD0 & AD1

provide 4 possible addresses.

10 AD1 Programmable address bit for multiple

package decoding. Bits AD0 & AD1

provide 4 possible addresses.

11 GND Common Ground

12 V

13 V

14 B

15 W

16 A2 Resistor terminal A2

t

9

Negative power supply, specified for

SS

operation from 0 to -5V

Logic Supply Voltage, needs to be same

L

voltage as the digital logic controlling the

AD5282.

Resistor terminal B2

2

Wiper terminal W

2

t

6

2

SCL

t

2

t

PS Sr P

3

Figure 1. Detail Timing Diagram

Data of AD5280/AD5282 is accepted from the I

S 0 1 0 1 1 A

A

D

1

R/

D

0

2

C bus in the following serial format:

A

WWWW

RS SD O1 O2 X X X A D7 D6 D5 D4 D3 D2 D1 D0 A P

AAAA/

B

Slave Address Byte Instruction Byte Data Byte

Where:

S = Start Condition

P = Stop Condition

A = Acknowledge

X = Don’t Care

AD1, AD0 = Package pin programmable address bits

1

9

A/B RS SD O2O1

ACK. BY

AD5280

Instruction Byte

STARTBY

MASTER

SDA

1

SCL

1

10

1

0

FRAME 1

Slave Address Byte

AD0AD1 R/W

Figure 2. Writing to the RDAC Register

t

4

t

5

t

7

t

10

R/WWWW= Read Enable at High and Write Enable at Lo w

AAAA/B = RDAC sub address select . “Zero” for RDAC1 and “One” for RDAC2

SD = Shutdown, same as SHDN pin operation except inverse logic

O2, O1 = Output logic pin latched values

D7,D6,D5,D4,D3,D2,D1,D0 = Data Bits

FRAME 2

9

1

X

X

D7 D6 D5D3D4 D0

X

ACK. BY

AD5280

FRAME 3

Data B yte

D2

9

D1

ACK.BY

AD5280

REV PrE 12 MAR 02 5

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

PRELIMINARY TECHNICAL DATA

S

W

AD5280/AD5282

19

1

SCL

1

STARTBY

MASTER

SDA

10

1

0

FRAME 1

Slave Address Byte

AD0AD1 R/W

Figure 3. Reading Data from a Previously Selected RDAC Register

OPERATION

The AD5280/AD5282 provides a single/dual channel, 256position digitally-controlled variable resistor (VR) device. The

terms VR and RDAC are used interchangeably throughout this

documentation. To program the VR settings, refer to the Digital

Interface section. Both parts have an internal power ON preset

that places the wiper in mid scal e during power on, which

simplifies the fault condition recovery at power up. In addition,

the shutdown SHDN pin of AD5280/AD5282 places the RDAC

in a zero power consumption state where terminal A is open

circuited and the wiper W is connected to terminal B, resulting

in only leakage currents being consumed in the VR structure. In

shutdown mode the VR latch settings are maintained, so that,

returning to operational mode from power shutdown, the VR

settings return to their previous resistance values.

R

9

D7 D6 D5 D3D4 D0D1D2

ACK. BY

AD5280

Ax

NO ACK.

FRAME 2

Dat a From Selected

for data 02

BYMASTER

STOP BY

MASTER

and so on. Each LSB data value increase moves the

H

wiper up the resistor ladder until the last tap poi nt is reached at

19982Ω [R

–1LSB+RW]. The wiper does not directly connect

AB

to the B terminal. See Figure 4 for a simplified diagram of the

equivalent RDAC circuit.

The general equation determining the digitally programmed

output resistance between W and B is:

D

)(

DR +⋅=

256

RR

WABWB

where D is the decimal equivalent of the binary code which is

loaded in the 8-bit RDAC register, and R

is the nominal end-

AB

to-end resistance.

For example, R

circuit, the following output resistance values R

=20KΩ, when VB = 0V and A–terminal is open

AB

will be set for

WB

the following RDAC latch codes. Result will be the same if

terminal A is tied to W:

1 eqn.

S

x

D R

Output State

WB

(DEC) (Ω)

256 19982Ω Full-Scale (RAB - 1LSB + RW)

128 10060Ω Mid-Scale

R

S

Bx

1 138Ω 1 LSB

0 60Ω Zero-Scale (Wiper contact resistance)

Figure 4. AD5280/AD5282 Equivalent RDAC Circuit

Note that in the zero-scale condition a finite wiper resistance of

60Ω is present. Care should be taken to limit the current flow

PROGRAMMING THE VARIABLE RESISTOR

Rheostat Operation

between W and B in this state t o a maximum current of no more

than 5mA. Otherwise, degradation or possible destruction of the

internal switch contact can occur.

The nominal resistance of the RDAC between terminals A and B

are available in 20KΩ, 50KΩ, and 200KΩ. The final three

digits of the part number determine the nominal resistance

value, e.g. 20KΩ = 20; 50KΩ = 50; 200KΩ = 200. The

nominal resistance (R

) of the VR has 256 contact points

AB

accessed by the wiper terminal, plus the B terminal contact. The

eight bit data in the RDAC latch is decoded to select one of the

256 possible settings. Assume a 20KΩ part is used, the wiper's

first connection starts at the B terminal for data 00

. Since there

H

Similar to the mechanical pot entiometer, the resistance of the

RDAC between the wiper W and terminal A also produ ces a

digitally controlled resistance R

. When these terminals are

WA

used the B–terminal should be let open or tied to the wiper

terminal. Setting the resistance value for R

starts at a

WA

maximum value of resistance and decreases as the data loaded in

the latch is increased in value. The general equation for this

operation is:

is a 60Ω wiper contact resistance, such connection yields a

256

D

minimum of 60Ω resistance between terminals W and B. The

second connection is the first tap point corresponds to 138Ω

(R

= RAB/256 + RW = 78Ω+60Ω) for data 01H. The third

WB

DR +⋅

−

)(

=

256

RR

WABWA

2 eqn.

connection is the next tap point representing 216Ω (78x2+60)

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

6 REV PrE 12 MAR 02

PRELIMINARY TECHNICAL DATA

For example, RAB=20KΩ, when VA = 0V and B–terminal is open

circuit, the following output resistance R

following RDAC latch codes. Result will be the same if terminal

B is tied to W:

will be set for the

WA

AD5280/AD5282

2 bits are determined by the state of the AD0 and AD1 pins of

the device. AD0 and AD1 allow the user to use up to four of

these devices on one bus.

2

The 2-wire I

C serial bus protocol operates as follows:

D R

Outpu t State

WA

(DEC) (Ω)

256 60 Full-Scale

128 10060 Mid-Scale

1 19982 1 LSB

0 20060 Zero-Scale

The typical distribution of the nominal resistance RAB from

channel-to-channel matches within ±1%. Device to device

matching is process lot dependent and is possible to have ±30%

variation. Since the resistance element is processed in thin film

technology, the change in R

with temperature has a 30

AB

ppm/°C temperature coefficient.

PROGRAMMING THE POTENTIOMETER DIVIDER

Voltage Output Operatio n

The digital potentiometer easily generates output voltages at

wiper-to-B and wiper-to-A to be proportional to the input

voltage at A-to-B. Let’s ignore the effect of the wiper resistance

at the moment. For example conn ecting A–terminal to +5V and

B–terminal to ground produces an output voltage at the wiperto-B starting at zero volts up to 1 LSB less than +5V. Each LSB

of voltage is equal to the voltage applied across terminal AB

divided by the 256 position of the potentiometer divider. Since

AD5280/AD5282 can be supplied by dual supplies, the general

equation defining the output voltage at V

with respect to

W

ground for any given input voltage applied to terminals AB is:

256

256

D

−

V

BAW

3 eqn.

D

)(

DV

V

+=

256

1. The master initiates data transfer by establishing a START

condition, which is when a high-to-low transition on the

SDA line occurs while SCL is high, Figure 2. The

following byte is the Slave Address Byte which consists of

the 7-bit slave address followed by an R/W bit (this bit

determines whether data will be read from or written to the

slave device).

The slave whose address corresponds to the transmitted

address responds by pulling the SDA line low during the

ninth clock pulse (this is termed the Acknowledge bit). At

this stage, all other devices on the bus remain idle while the

selected device waits for data to be written to or read from

its serial register. If the R/W bit is high, the master will read

from the slave device. On the other hand, if the R/W bit is

low, the master will write to the slave device.

2. A Write operation contains an extra Instruction Byte more

than the Read operation. Such Instruction Byte in Write

mode follows the Slave Address Byte. The MSB of the

Instruction Byte labeled A/B is the RDAC sub-address

select. A “low” select RDAC1 and a “high” selects RDAC2

for dual channel AD5282. The 2

nd

MSB RS is the Midscale reset. A logic high of this bit moves the wiper of a

selected RDAC to the center tap where R

WA=RWB

. The 3rd

MSB SD is a shutdown bit. A logic high causes the RDAC

open circuit at terminal A while shorting wiper to terminal

B. This operation yields almost a zero Ohm in rheostat

mode or zero volt in potentiometer mode. This SD bit

serves the same function as the SHDN pin except it reacts in

active low. The following two bits are O2 and O1. They are

extra programmable logic output that users can make use of

them by driving other digital loads, logic gates, LED

drivers, and analog switches, etc. The 3 LSBs are DON’T

CARE. See Figure 2.

where D is decimal equivalent of the binary code which is

loaded in the 8-bit RDAC register.

3. After acknowledged the Instruction Byte, the last byte in

Write mode is the Data Byte. Data is transmitted over the

serial bus in sequences of nine clock pulses (eight data bits

Operation of the digital potentiometer in the divider mode

results in a more accurate operation over temperature. Unlike

the rheostat mode, the output voltage is dependent on the ratio

of the internal resistors R

therefore, the temperature dri ft reduces to 5ppm/°C.

and RWB and not the absolute values,

WA

DIGITAL INTERFACE

2-WIRE SERIAL BUS

followed by an “Acknowledge” bit). The transitions on the

SDA line must occur during the low period of SCL and

remain stable during the high period of SCL, Figure 1.

4. In Read mode, the Data Byte goes right after the

acknowledgment of the Slave Address Byte. Data is

transmitted over the serial bus in sequences of nine clock

pulses (slight difference with the Write mode, there are

eight data bits followed by a “No Acknowledge” bit).

Similarly, the transitions on the SDA line must occur

during the low period of SCL and remain stable during the

The AD5280/AD5282 are controlled via an I

2

C compatible

serial bus. The RDACs are connected t o this bus as slave

devices.

Referring from Figures 2 and 3, the first byte of

AD5280/AD5282 is a Slave Address Byte. It has a 7-bit slave

address and a R/W bit. The 5 MSBs are 01011 and the following

REV PrE 12 MAR 02 7

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

high period of SCL.

5. When all data bits have been read or written, a STOP

condition is established by the master. A STOP condition is

defined as a low-to-high transition on the SDA line while

SCL is high. In Write mode, the master will pull the SDA

line high during the 10

th

clock pulse to establish a STOP

PRELIMINARY TECHNICAL DATA

A,B,

AD5280/AD5282

condition, Figure 2. In Read mode, the master will issue a

No Acknowledge for the 9

remains high). The master will then bring the SDA line low

before the 10

th

clock pulse which goes high to establish a

STOP condition, Figure 3.

A repeated Write function gives the user flexibility to update the

RDAC output a number of times after addressing and instructing

the part only once. During the Write cycle, each Data byte will

update the RDAC output. For example, after the RDAC has

acknowledged its Slave Address and Instruction Bytes, the

RDAC output will update after these two bytes. If another byte

is written to the RDAC while it is still addressed to a specific

slave device with the same instruction, this byte will update the

output of the select ed slave device. If different instructions are

needed, the Write mode h as to start with a new Slave Address,

Instruction, and Dat a Bytes again. Similarly, a repeated Read

function of the RDAC is also allowed.

MULTIPLE DEVICES ON ONE BUS

Figure 5 shows four AD5282 devices on the same serial bus.

Each has a different slave address sine the state of their AD0 and

AD1 pins are different. This allows each RDAC within each

device to be written to or read from independently. The master

device output bus line drivers are open-drain pull downs in a

2

C compatible interface.

fully I

th

clock pulse (i.e., the SDA line

+5V

V

=3.3V V

DD1

SDA1

SCL1

Rp Rp

3.3V

E2PROM

G

S

M1

D

S

Rp Rp

G

D

M2

5V

AD5 282

Figure 6. Level Shift for different poten tial operation.

All digital inputs are protected with a series input resistor and

parallel Zener ESD structures shown in figure 7. Applies to

digital input pins SDA, SCL, and SHDN.

340

Ω

Ω

Ω Ω

LOGIC

V

SS

Figure 7. ESD Protection of digital pins

W

DD2

=5V

SDA2

SCL2

Rp Rp

MASTER

VDDVDD

SDA SCL

AD1

AD0

AD5282

SDA SCL

AD1

AD0

AD5282

VDD

SDA SCL

AD1

AD0

AD5282

SDA SCL

AD1

AD0

AD5282

Figure 5. Multiple AD5282 Devices on One Bus

LEVEL SHIFT FOR BI-DIRECTIONAL INTERFACE

While most old systems may be operated at one voltage, a new

component may be optimized at another. When two systems

operate the same signal at two different voltages, proper method

of level shifting is needed. For instance, one can use a 3.3V

2

E

PROM to interface with a 5V digital potentiometer. A level

shift scheme is needed in order to enable a bi-directional

communication so that the setting of the digital potentiometer

can be stored to and retrieved from the E

2

PROM. Figure 6

shows one of the techniques. M1 and M2 can be N-Ch FETs

2N7002 or low threshold FDV301N if V

falls below 2.5V.

DD

SDA

SCL

V

SS

Figure 8. ESD Protection of Resistor Terminals

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

8 REV PrE 12 MAR 02

PRELIMINARY TECHNICAL DATA

TEST CIRCUITS

Figures 9 to 17 define the test conditions used in product specification

table.

Figure 9. Potentiometer Divider Nonlinearity error test circuit

(INL, DNL)

Figure 10. Resistor Position Nonlinearity Error (Rheostat

Operation; R-INL, R-DNL)

AD5280/AD5282

Figure 14. Non-Inverting Gain test circuit

Figure 15. Gain Vs Frequency test circuit

Figure 11. Wiper Resistance test Circuit

Figure 12. Power supply sensitivity test circuit (PSS, PSSR)

Figure 13. Inverting Gain test Circuit

Figure 16. Incremental ON Resistan ce Test Circuit

Figure 17. Common Mode Leakage current test circuit

REV PrE 12 MAR 02 9

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

PRELIMINARY TECHNICAL DATA

AD5280/AD5282

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm)

Information contained in this Product Concept Data Sheet describes a product in the early definition stage. There is no guarantee that the information contained here will become a final

product in its present form. For latest information contact Walt Heinzer/Analog Devices, Santa Clara, CA. TEL 408 382-3107; FAX 408 382-2721; email; walt.heinzer@analog.com

10 REV PrE 12 MAR 02

Loading...

Loading...