1024-/256-Position, 1% Resistor Tolerance Error,

I2C Interface and 50-TP Memory Digital Rheostat

FEATURES

Single-channel, 1024-/256-position resolution

20 kΩ, 50 kΩ, 100 kΩ nominal resistance

Maximum ±1% nominal resistor tolerance error

50-times programmable (50-TP) wiper memory

Rheostat mode temperature coefficient: 5 ppm/°C

2.7 V to 5.5 V single-supply operation

±2.5 V to ±2.75 V dual-supply operation for ac or bipolar

operations

2

I

C-compatible interface

Wiper setting readback

Power on refreshed from 50-TP memory

Thin LFCSP 10-lead, 3 mm × 3 mm × 0.8 mm package

Compact MSOP, 10-lead 3 mm × 4.9 mm × 1.1 mm package

APPLICATIONS

Mechanical rheostat replacements

Op-amp: variable gain control

Instrumentation: gain, offset adjustment

Programmable voltage to current conversions

Programmable filters, delays, time constants

Programmable power supply

Sensor calibration

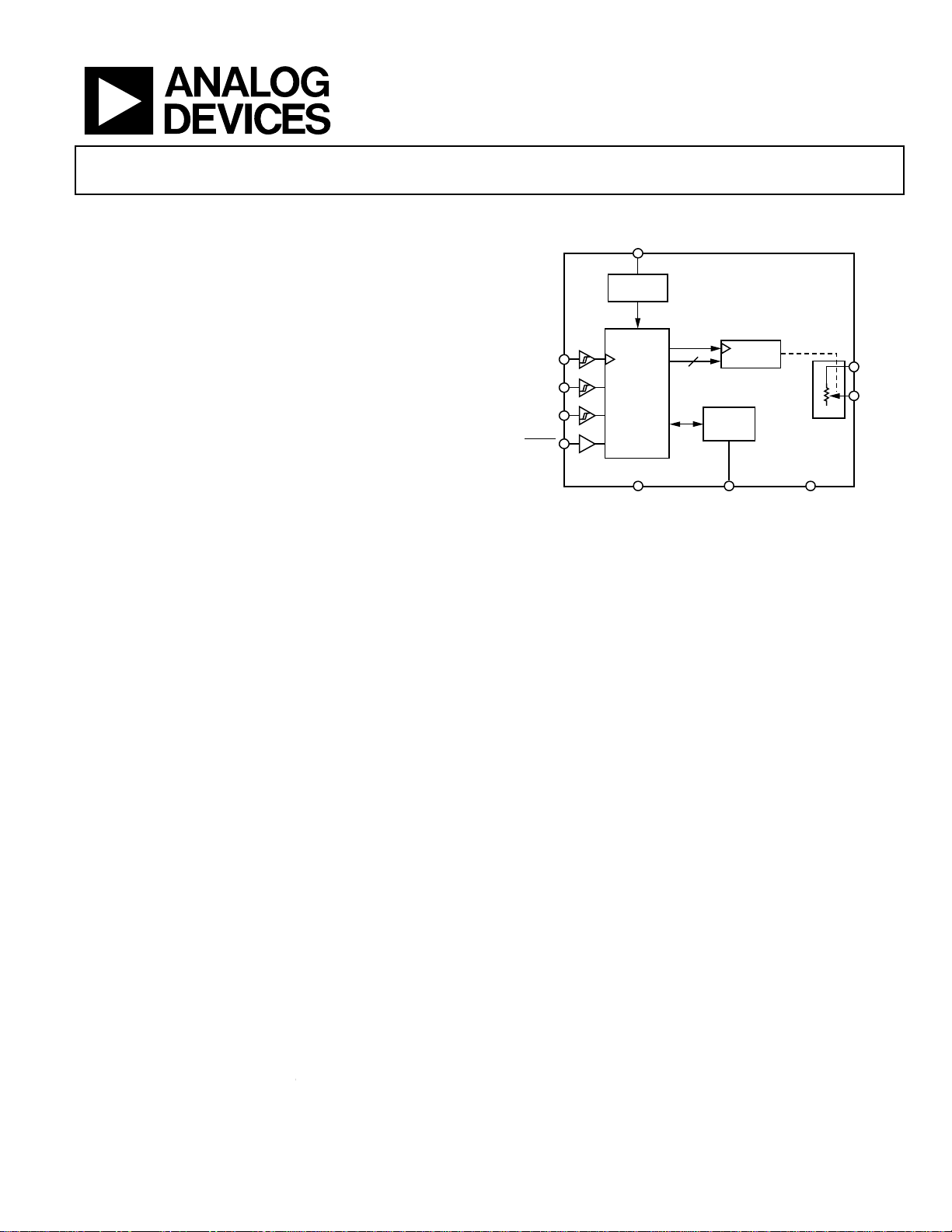

SCL

SDA

ADDR

RESET

AD5272/AD5274

FUNCTIONAL BLOCK DIAGRAM

V

DD

POWER-ON

RESET

I2C

SERIAL

INTERFACE

V

SS

AD5272/AD5274

RDAC

REGIS TER

10/8

50-TP

MEMORY

BLOCK

EXT_CAP GND

Figure 1.

A

W

08076-001

GENERAL DESCRIPTION

The AD5272/AD52741 are single-channel, 1024-/256-position

digital rheostats that combine industry leading variable resistor

performance with nonvolatile memory (NVM) in a compact

package.

The AD5272/AD5274 ensure less than 1% end-to-end resistor

tolerance error and offer 50-times programmable (50-TP) memory.

The guaranteed industry leading low resistor tolerance error

feature simplifies open-loop applications as well as precision

calibration and tolerance matching applications.

1

Protected by U.S. Patent Number 7688240.;

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

The AD5272/AD5274 device wiper settings are controllable

through the I

2

C-compatible digital interface. Unlimited

adjustments are allowed before programming the resistance

value into the 50-TP memory. The AD5272/AD5274 do not

require any external voltage supply to facilitate fuse blow and

there are 50 opportunities for permanent programming. During

50-TP activation, a permanent blow fuse command freezes the

wiper position (analogous to placing epoxy on a mechanical

trimmer).

The AD5272/AD5274 are available in a 3 mm × 3 mm 10-lead

LFCSP package and in a 10-lead MSOP package. The parts are

guaranteed to operate over the extended industrial temperature

range of −40°C to +125°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009–2010 Analog Devices, Inc. All rights reserved.

AD5272/AD5274

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Electrical Characteristics—AD5272 .......................................... 3

Electrical Characteristics—AD5274 .......................................... 5

Interface Timing Specifications.................................................. 7

Absolute Maximum Ratings............................................................ 9

Thermal Resistance ...................................................................... 9

ESD Caution.................................................................................. 9

Pin Configuration and Function Descriptions........................... 10

Typical Performance Characteristics ........................................... 11

Test Circuits..................................................................................... 17

Theory of Operation ...................................................................... 18

Serial Data Interface................................................................... 18

Shift Register............................................................................... 18

Write Operation.......................................................................... 19

Read Operation........................................................................... 20

RDAC Register............................................................................ 21

50-TP Memory Block ................................................................ 21

Write Protection ......................................................................... 21

50-TP Memory Write-Acknowledge Polling.......................... 23

Reset ............................................................................................. 23

Resistor Performance Mode...................................................... 23

Shutdown Mode ......................................................................... 23

RDAC Architecture.................................................................... 23

Programming the Variable Resistor......................................... 23

EXT_CAP Capacitor.................................................................. 24

Terminal Voltage Operating Range ......................................... 24

Power-Up Sequence................................................................... 24

Outline Dimensions....................................................................... 25

Ordering Guide .......................................................................... 26

REVISION HISTORY

11/10—Rev. B to Rev. C

Changes to Figure 24...................................................................... 14

5/10—Rev. A to Rev. B

Added LFCSP Package.................................................. Throughout

Changed OTP to 50-TP ................................................ Throughout

Changes to Features Section and Applications Section............... 1

Added Endnote 1.............................................................................. 1

Changes to Table 1............................................................................ 3

Added Table 3.................................................................................... 4

Changes to Table 4............................................................................ 5

Added Table 6.................................................................................... 6

Changes to Table 8 and Table 9....................................................... 9

Added Figure 5................................................................................ 10

Added Exposed Pad Note to Table 10.......................................... 10

Changes to Typical Performance Characteristics....................... 11

Changes to Resistor Performance Mode Section ....................... 23

Updated Outline Dimensions....................................................... 25

Changes to Ordering Guide.......................................................... 26

3/10—Rev. 0 to Rev. A

Changes to Product Title and General Description Section....... 1

Changes to Theory of Operation Section.................................... 15

10/09—Revision 0: Initial Version

Rev. C | Page 2 of 28

AD5272/AD5274

SPECIFICATIONS

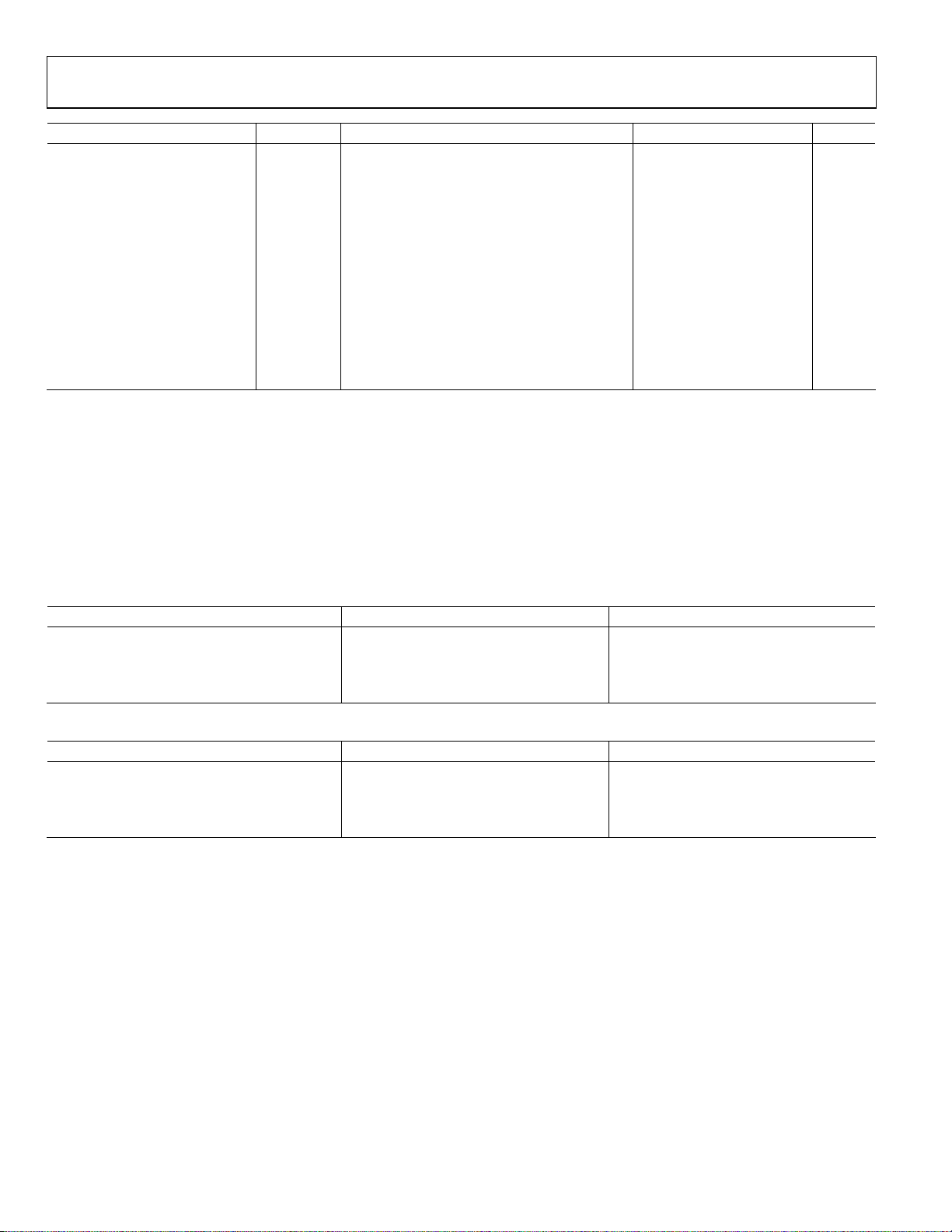

ELECTRICAL CHARACTERISTICS—AD5272

VDD = 2.7 V to 5.5 V, VSS = 0 V; VDD = 2.5 V to 2.75 V, VSS = −2.5 V to −2.75 V; −40°C < TA < +125°C, unless otherwise noted.

Table 1.

Parameter Symbol Test Conditions/Comments Min Typ1 Max Unit

DC CHARACTERISTICS—RHEOSTAT MODE

Resolution 10 Bits

Resistor Integral Nonlinearity

R

R

Resistor Differential Nonlinearity2 R-DNL

Nominal Resistor Tolerance

R-Perf Mode4 See Table 2 and Table 3 −1 ±0.5 +1 %

Normal Mode ±15 %

Resistance Temperature Coefficient

Wiper Resistance Code = zero scale 35 70 Ω

RESISTOR TERMINALS

Terminal Voltage Range

Capacitance5 A f = 1 MHz, measured to GND, code = half scale 90 pF

Capacitance5 W f = 1 MHz, measured to GND, code = half scale 40 pF

Common-Mode Leakage Current5 V

DIGITAL INPUTS

Input Logic5

High V

Low V

Input Current IIN ±1 µA

Input Capacitance5 C

DIGITAL OUTPUT

Output Voltage5

High VOH R

Low VOL R

V

V

Tristate Leakage Current −1 +1 µA

Output Capacitance5 5 pF

POWER SUPPLIES

Single-Supply Power Range VSS = 0 V 2.7 5.5 V

Dual-Supply Power Range ±2.5 ±2.75 V

Supply Current

Positive IDD 1 µA

Negative ISS −1 µA

50-TP Store Current

5, 8

Positive I

Negative I

50-TP Read Current

5, 9

Positive I

Negative I

Power Dissipation10 V

2, 3

R-INL RAW= 20 kΩ, |VDD − VSS| = 3.0 V to 5.5 V −1 +1 LSB

= 20 kΩ, |VDD − VSS| = 2.7 V to 3.0 V −1 +1.5 LSB

AW

= 50 kΩ, 100 kΩ −1 +1 LSB

AW

5, 6

Code = full scale 5 ppm/°C

5, 7

V

= VW 50 nA

A

2.0 V

INH

0.8 V

INL

5 pF

IN

= 2.2 kΩ to VDD V

PULL_UP

= 2.2 kΩ to VDD

PULL_UP

= 2.7 V to 5.5 V, VSS = 0 V 0.4 V

DD

= 2.5 V to 2.75 V, VSS = −2.5 V to −2.75 V 0.6 V

DD

−1 +1 LSB

V

SS

− 0.1 V

DD

V

DD

DD_OTP_STORE

SS_OTP_STORE

4 mA

−4 mA

DD_OTP_READ

SS_OTP_READ

500 µA

−500 µA

= VDD or VIL = GND 5.5 µW

IH

Rev. C | Page 3 of 28

AD5272/AD5274

Parameter Symbol Test Conditions/Comments Min Typ1 Max Unit

Power Supply Rejection Ratio5 PSRR ∆VDD/∆VSS = ±5 V ± 10% dB

R

R

R

DYNAMIC CHARACTERISTICS

5, 11

Bandwidth −3 dB, RAW = 10 kΩ, Terminal W, see Figure 41 kHz

R

R

R

Total Harmonic Distortion VA = 1 V rms, f = 1 kHz, code = half scale dB

R

R

R

Resistor Noise Density Code = half scale, TA = 25°C, f = 10 kHz nV/√Hz

R

R

R

1

Typical specifications represent average readings at 25°C, VDD = 5 V, and VSS = 0 V.

2

Resistor position nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions.

3

The maximum current in each code is defined by IAW = (VDD − 1)/RAW.

4

The terms, resistor performance mode and R-Perf mode, are used interchangeably. See the Resistor Performance Mode section.

5

Guaranteed by design and not subject to production test.

6

See Figure 24 for more details.

7

Resistor Terminal A and Resistor Terminal W have no limitations on polarity with respect to each other. Dual-supply operation enables ground referenced bipolar

signal adjustment.

8

Different from operating current, the supply current for the fuse program lasts approximately 55 ms.

9

Different from operating current, the supply current for the fuse read lasts approximately 500 ns.

10

P

is calculated from (IDD × VDD) + (ISS × VSS).

DISS

11

All dynamic characteristics use VDD = +2.5 V, VSS = −2.5 V.

= 20 kΩ −66 −55

AW

= 50 kΩ −75 −67

AW

= 100 kΩ −78 −70

AW

= 20 kΩ 300

AW

= 50 kΩ 120

AW

= 100 kΩ 60

AW

= 20 kΩ −90

AW

= 50 kΩ −88

AW

= 100 kΩ −85

AW

= 20 kΩ 50

AW

= 50 kΩ 25

AW

= 100 kΩ 32

AW

Table 2. AD5272 Resistor Performance Mode Code Range

Resistor Tolerance Per Code |VDD − VSS| = 4.5 V to 5.5 V |VDD − VSS| = 2.7 V to 4.5 V

R-TOLERANCE

1% R-Tolerance From 0x078 to 0x3FF From 0x0BE to 0x3FF

2% R-Tolerance From 0x037 to 0x3FF From 0x055 to 0x3FF

3% R-Tolerance From 0x028 to 0x3FF From 0x037 to 0x3FF

Table 3. AD5272 50 kΩ and 100 kΩ Resistor Performance Mode Code Range

Resistor Tolerance Per Code RAW = 50 kΩ RAW = 100 kΩ

R-TOLERANCE

1% R-Tolerance From 0x078 to 0x3FF From 0x04B to 0x3FF

2% R-Tolerance From 0x055 to 0x3FF From 0x032 to 0x3FF

3% R-Tolerance From 0x032 to 0x3FF From 0x019 to 0x3FF

Rev. C | Page 4 of 28

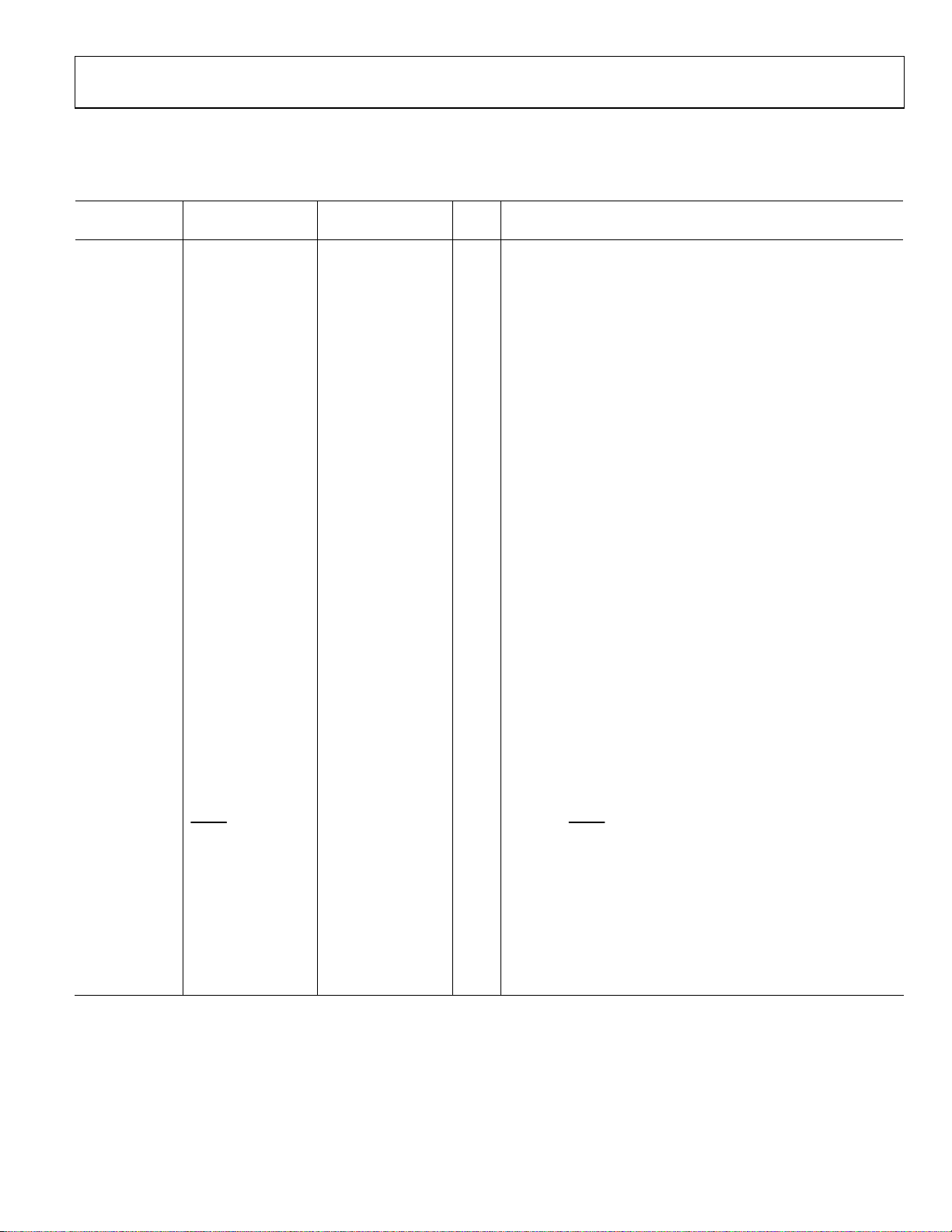

AD5272/AD5274

ELECTRICAL CHARACTERISTICS—AD5274

VDD = 2.7 V to 5.5 V, VSS = 0 V; VDD = 2.5 V to 2.75 V, VSS = −2.5 V to −2.75 V; −40°C < TA < +125°C, unless otherwise noted.

Table 4.

Parameter Symbol Test Conditions/Comments Min Typ1 Max Unit

DC CHARACTERISTICS—

RHEOSTAT MODE

Resolution 8 Bits

Resistor Integral Nonlinearity

Resistor Differential

Nonlinearity

2

Nominal Resistor Tolerance

R-Perf Mode4 See Table 5 and Table 6 −1 ±0.5 +1 %

Normal Mode ±15 %

Resistance Temperature

Coefficient

5, 6

Wiper Resistance Code = zero scale 35 70 Ω

RESISTOR TERMINALS

Terminal Voltage Range

5, 7

Capacitance5 A f = 1 MHz, measured to GND, code = half scale 90 pF

Capacitance5 W f = 1 MHz, measured to GND, code = half scale 40 pF

Common-Mode Leakage

Current

5

DIGITAL INPUTS

Input Logic5

High V

Low V

Input Current IIN ±1 µA

Input Capacitance5 C

DIGITAL OUTPUT

Output Voltage5

High VOH R

Low VOL R

V

V

Tristate Leakage Current −1 +1 µA

Output Capacitance5 5 pF

POWER SUPPLIES

Single-Supply Power Range VSS = 0 V 2.7 5.5 V

Dual-Supply Power Range ±2.5 ±2.75 V

Supply Current

Positive IDD 1 µA

Negative ISS −1 µA

OTP Store Current

5, 8

Positive I

Negative I

OTP Read Current

5, 9

Positive I

Negative I

Power Dissipation10 V

Power Supply Rejection Ratio5 PSRR ∆VDD/∆VSS = ±5 V ± 10% dB

R

R

R

2, 3

R-INL −1 +1 LSB

R-DNL

−1 +1 LSB

Code = full scale 5 ppm/°C

V

V

2.0 V

INH

0.8 V

INL

5 pF

IN

DD_OTP_STORE

SS_OTP_STORE

DD_OTP_READ

SS_OTP_READ

= VW 50 nA

A

= 2.2 kΩ to VDD V

PULL_UP

= 2.2 kΩ to VDD

PULL_UP

= 2.7 V to 5.5 V, VSS = 0 V 0.4 V

DD

= 2.5 V to 2.75 V, VSS = −2.5 V to −2.75 V 0.6 V

DD

4 mA

−4 mA

500 µA

−500 µA

= VDD or VIL = GND 5.5 µW

IH

= 20 kΩ −66 −55

AW

= 50 kΩ −75 −67

AW

= 100 kΩ −78 −70

AW

V

SS

− 0.1 V

DD

V

DD

Rev. C | Page 5 of 28

AD5272/AD5274

Parameter Symbol Test Conditions/Comments Min Typ1 Max Unit

DYNAMIC CHARACTERISTICS

Bandwidth −3 dB, RAW = 10 kΩ, Terminal W, see Figure 41 kHz

R

R

R

Total Harmonic Distortion VA = 1 V rms, f = 1 kHz, code = half scale dB

R

R

R

Resistor Noise Density Code = half scale, TA = 25°C, f = 10 kHz nV/√Hz

R

R

R

1

Typical specifications represent average readings at 25°C, VDD = 5 V, and VSS = 0 V.

2

Resistor position nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions.

3

The maximum current in each code is defined by IAW = (VDD − 1)/RAW.

4

The terms, resistor performance mode and R-Perf mode, are used interchangeably. See the Resistor Performance Mode section.

5

Guaranteed by design and not subject to production test.

6

See Figure 24 for more details.

7

Resistor Terminal A and Resistor Terminal W have no limitations on polarity with respect to each other. Dual-supply operation enables ground referenced bipolar

signal adjustment.

8

Different from operating current, the supply current for the fuse program lasts approximately 55 ms.

9

Different from operating current, the supply current for the fuse read lasts approximately 500 ns.

10

P

is calculated from (IDD × VDD) + (ISS × VSS).

DISS

11

All dynamic characteristics use VDD = +2.5 V, VSS = −2.5 V.

5, 11

= 20 kΩ 300

AW

= 50 kΩ 120

AW

= 100 kΩ 60

AW

= 20 kΩ −90

AW

= 50 kΩ −88

AW

= 100 kΩ −85

AW

= 20 kΩ 50

AW

= 50 kΩ 25

AW

= 100 kΩ 32

AW

Table 5. AD5274 Resistor Performance Mode Code Range

Resistor Tolerance per Code |VDD − VSS| = 4.5 V to 5.5 V |VDD − VSS| = 2.7 V to 4.5 V

R-TOLERANCE

1% R-Tolerance From 0x1E to 0xFF From 0x32 to 0xFF

2% R-Tolerance From 0x0F to 0xFF From 0x19 to 0xFF

3% R-Tolerance From 0x06 to 0xFF From 0x0E to 0xFF

Table 6. AD5274 50 kΩ and 100 kΩ Resistor Performance Mode Code Range

Resistor Tolerance per Code RAW = 50 kΩ RAW = 100 kΩ

R-TOLERANCE

1% R-Tolerance From 0x1E to 0xFF From 0x14 to 0xFF

2% R-Tolerance From 0x14 to 0xFF From 0x0F to 0xFF

3% R-Tolerance From 0x0A to 0xFF From 0x0A to 0xFF

Rev. C | Page 6 of 28

AD5272/AD5274

INTERFACE TIMING SPECIFICATIONS

VDD = 2.5 V to 5.5 V; all specifications T

Table 7.

Limit at T

Parameter Conditions1 Min Max Unit Description

2

f

Standard mode 100 kHz Serial clock frequency

SCL

Fast mode 400 kHz Serial clock frequency

t1 Standard mode 4 µs t

Fast mode 0.6 µs t

t2 Standard mode 4.7 µs t

Fast mode 1.3 µs t

t3 Standard mode 250 ns t

Fast mode 100 ns t

t4 Standard mode 0 3.45 µs t

Fast mode 0 0.9 µs t

t5 Standard mode 4.7 µs t

Fast mode 0.6 µs t

t6 Standard mode 4 µs t

Fast mode 0.6 µs t

High speed mode 160 ns t

t7 Standard mode 4.7 µs t

Fast mode 1.3 µs t

t8 Standard mode 4 µs t

Fast mode 0.6 µs t

t9 Standard mode 1000 ns t

Fast mode 300 ns t

t10 Standard mode 300 ns t

Fast mode 300 ns t

t11 Standard mode 1000 ns t

Fast mode 300 ns t

t

Standard mode 1000 ns

11A

Fast mode 300 ns

t12 Standard mode 300 ns t

Fast mode 300 ns t

t13

3

t

Fast mode 0 50 ns Pulse width of spike suppressed

SP

4, 5

t

500 ns Command execute time

EXEC

t

RDAC_R-PERF

t

RDAC_NORMAL

t

MEMORY_READ

t

MEMORY_PROGRAM

t

RESET

t

POWER-UP

1

Maximum bus capacitance is limited to 400 pF.

2

The SDA and SCL timing is measured with the input filters enabled. Switching off the input filters improves the transfer rate but has a negative effect on EMC behavior

of the part.

3

Input filtering on the SCL and SDA inputs suppress noise spikes that are less than 50 ns for fast mode.

4

Refer to t

5

Refer to t

6

Maximum time after VDD − VSS is equal to 2.5 V.

2 µs RDAC register write command execute time (R-Perf mode)

6 µs Memory readback execute time

350 ms Memory program time

600 µs Reset 50-TP restore time

6

2 ms Power-on 50-TP restore time

and t

RDAC_R-PERF

MEMORY_READ

pulse time

RESET

600 ns RDAC register write command execute time (normal mode)

for RDAC register write operations.

RDAC_NORMAL

t

and

MEMORY_PROGRAM

for memory commands operations.

to T

MIN

, unless otherwise noted.

MAX

, T

MIN

MAX

20 ns

, SCL high time

HIGH

, SCL high time

HIGH

, SCL low time

LOW

, SCL low time

LOW

, data setup time

SU;DAT

, data setup time

SU;DAT

, data hold time

HD;DAT

, data hold time

HD;DAT

, set-up time for a repeated start condition

SU;STA

, set-up time for a repeated start condition

SU;STA

, hold time (repeated) start condition

HD;STA

, hold time (repeated) start condition

HD;STA

, hold time (repeated) start condition

HD;STA

, bus free time between a stop and a start condition

BUF

, bus free time between a stop and a start condition

BUF

, setup time for a stop condition

SU;STO

, setup time for a stop condition

SU;STO

, rise time of SDA signal

RDA

, rise time of SDA signal

RDA

, fall time of SDA signal

FDA

, fall time of SDA signal

FDA

, rise time of SCL signal

RCL

, rise time of SCL signal

RCL

, rise time of SCL signal after a repeated start condition and

t

RCL1

after an acknowledge bit

, rise time of SCL signal after a repeated start condition and

t

RCL1

after an acknowledge bit

, fall time of SCL signal

FCL

, fall time of SCL signal

FCL

Minimum RESET low time

Rev. C | Page 7 of 28

AD5272/AD5274

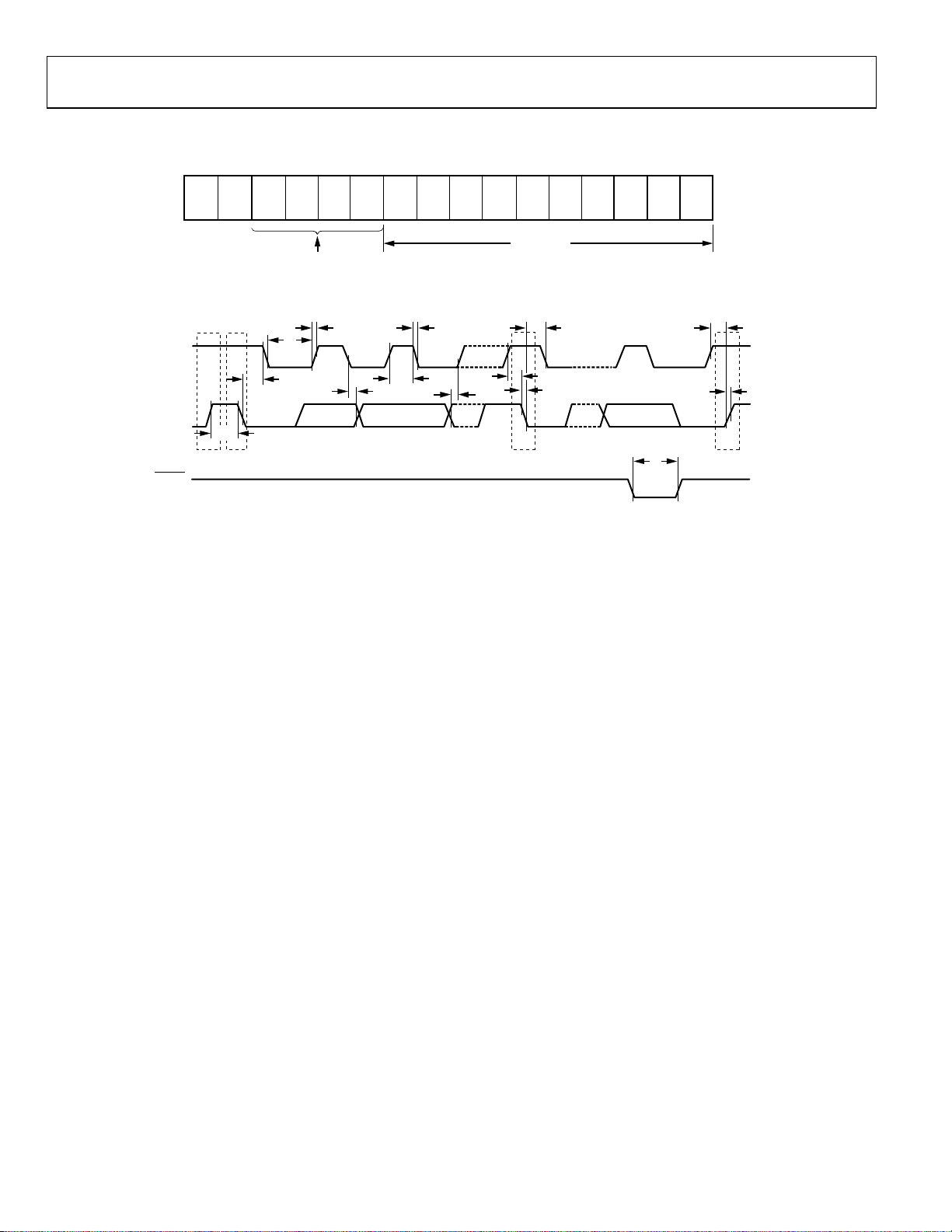

Shift Register and Timing Diagrams

C3

0 0

CONTROL BI TS

SCL

t

6

SDA

t

7

PS S P

RESET

C2

t

2

DB9 (MSB) DB0 (LSB)

C0 C1

D9

D7 D6 D5 D4 D3

D8

Figure 2. Shift Register Content

t

11

t

4

t

12

t

1

t

t

3

5

Figure 3. 2-Wire Serial Interface Timing Diagram

DATA BIT S

t

6

t

10

D2 D1

t

1

3

D0

08076-003

t

8

t

9

08076-002

Rev. C | Page 8 of 28

AD5272/AD5274

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 8.

Parameter Rating

VDD to GND –0.3 V to +7.0 V

VSS to GND +0.3 V to −7.0 V

VDD to VSS 7 V

VA, VW to GND VSS − 0.3 V, VDD + 0.3 V

Digital Input and Output Voltage to GND −0.3 V to VDD + 0.3 V

EXT_CAP to VSS 7 V

IA, IW

Continuous

RAW = 20 kΩ ±3 mA

RAW = 50 kΩ, 100 kΩ ±2 mA

Pulsed1

Frequency > 10 kHz ±MCC2/d3

Frequency ≤ 10 kHz ±MCC2/√d3

Operating Temperature Range4 −40°C to +125°C

Maximum Junction Temperature

(T

Maximum)

J

150°C

Storage Temperature Range −65°C to +150°C

Reflow Soldering

Peak Temperature 260°C

Time at Peak Temperature 20 sec to 40 sec

Package Power Dissipation (TJ max − TA)/θJA

1

Maximum terminal current is bounded by the maximum current handling of

the switches, maximum power dissipation of the package, and maximum

applied voltage across any two of the A and W terminals at a given

resistance.

2

Maximum continuous current

3

Pulse duty factor.

4

Includes programming of 50-TP memory.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or

any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

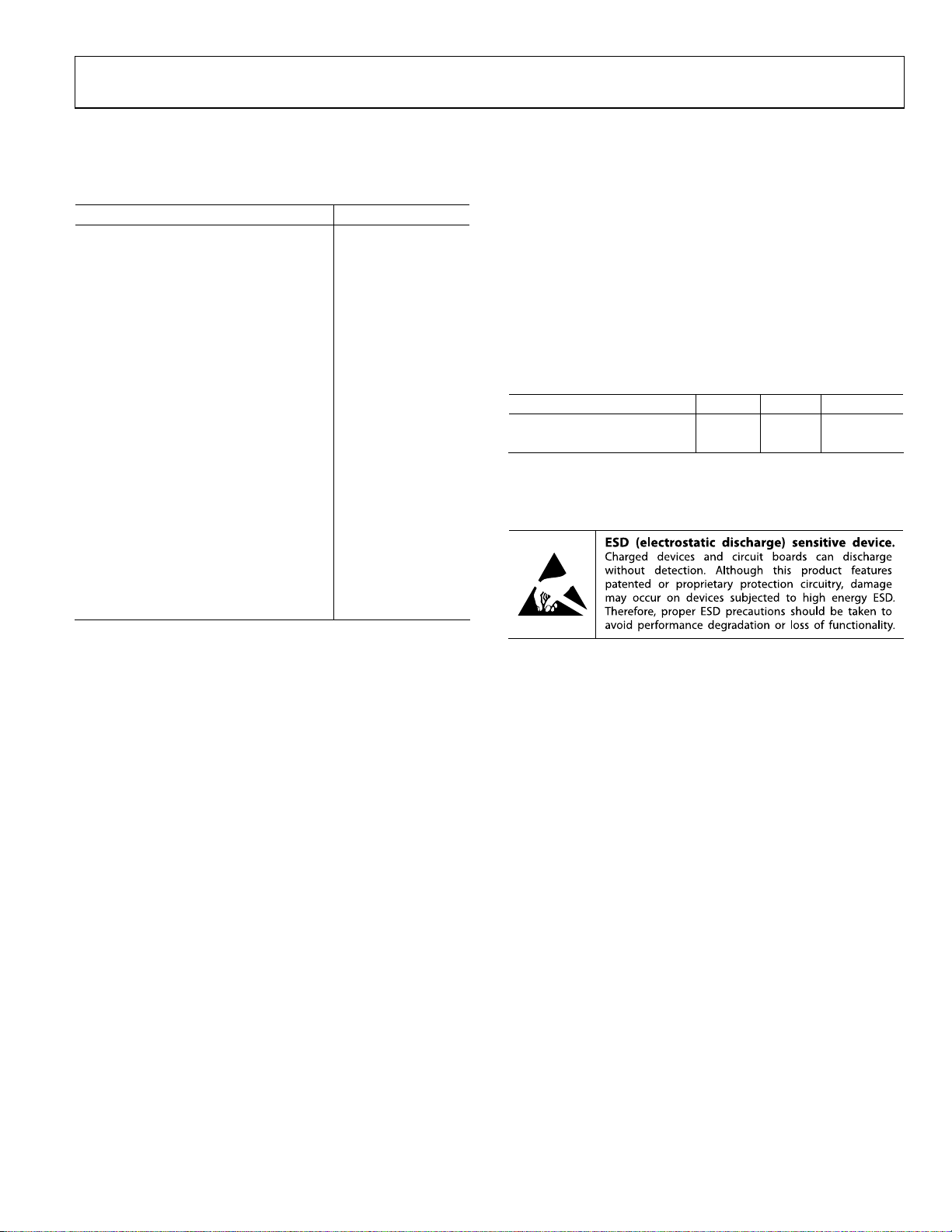

THERMAL RESISTANCE

θJA is defined by JEDEC specification JESD-51 and the value is

dependent on the test board and test environment.

Table 9. Thermal Resistance

Package Type θ

1

θ

JA

Unit

JC

10-Lead LFCSP 50 3 °C/W

10-Lead MSOP 135 N/A °C/W

1

JEDEC 2S2P test board, still air (0 m/s air flow).

ESD CAUTION

Rev. C | Page 9 of 28

AD5272/AD5274

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

V

DD

2

V

1

DD

V

EXT_CAP

A

W

SS

2

3

4

(Not to Scale)

5

AD5272/

AD5274

TOP VIEW

Figure 4. MSOP Pin Configuration

10

9

8

7

6

ADDR

SCL

SDA

RESET

GND

A

W

V

SS

EXT_CAP

NOTES

1. THE EXPOSED PAD IS LEFT FLOATING

08076-004

OR IS TIED TO V

Figure 5. LFCSP Pin Configuration

AD5272/

AD5274

3

(EXPOSED

4

5

PAD)

.

SS

Table 10. Pin Function Descriptions

Pin No. Mnemonic Description

1 VDD Positive Power Supply. Decouple this pin with 0.1 µF ceramic capacitors and 10 µF capacitors.

2 A Terminal A of RDAC. VSS ≤ VA ≤ VDD.

3 W

4 V

SS

Wiper terminal of RDAC. VSS ≤ VW ≤ VDD.

Negative Supply. Connect to 0 V for single-supply applications. Decouple this pin with 0.1 F ceramic capacitors

and 10 F capacitors.

5 EXT_CAP

External Capacitor. Connect a 1 µF capacitor between EXT_CAP and V

. This capacitor must have a voltage

SS

rating of ≥7 V.

6 GND Ground Pin, Logic Ground Reference.

7

RESET Hardware Reset Pin. Refreshes the RDAC register with the contents of the 50-TP memory register. Factory

default loads midscale until the first 50-TP wiper memory location is programmed. RESET

to VDD if not used.

8 SDA

Serial Data Line. This is used in conjunction with the SCL line to clock data into or out of the 16-bit input registers. It is

a bidirectional, open-drain data line that should be pulled to the supply with an external pull-up resistor.

9 SCL

10 ADDR

EPAD

Exposed Pad

Serial Clock Line. This is used in conjunction with the SDA line to clock data into or out of the 16-bit input registers.

Tristate Address Input. Sets the two least significant bits (Bit A1, Bit A0) of the 7-bit slave address (see Table 11).

Leave floating or tie to V

.

SS

(LFCSP Only)

10

9

8

7

6

is active low. Tie RESET

ADDR

SCL

SDA

RESET

GND

08076-040

Rev. C | Page 10 of 28

AD5272/AD5274

TYPICAL PERFORMANCE CHARACTERISTICS

0.8

0.6

+125°C

+25°C

–40°C

RAW = 20kΩ

0.8

0.6

TA = 25°C

20kΩ

50kΩ

100kΩ

0.4

0.2

INL (LSB)

0

–0.2

–0.4

0 128 256 384 512 640 768 896 1023

CODE (Decimal)

Figure 6. R-INL in R-Perf Mode vs. Code vs. Temperature (AD5272)

0.2

0.1

0

–0.1

–0.2

DNL (LSB)

–0.3

–0.4

–0.5

–0.6

0 128 256 384 512 640 768 896 1023

–40°C

+25°C

CODE (Decimal)

RAW = 20kΩ

+125°C

Figure 7. R-DNL in R-Perf Mode vs. Code vs. Temperature (AD5272)

0.4

0.2

INL (LSB)

0

–0.2

–0.4

0 256 512 768 1023

08076-010

CODE (Decimal)

08076-111

Figure 9. R-INL in R-Perf Mode vs. Code vs. Nominal Resistance (AD5272)

0.6

TA = 25°C

0.4

0.2

0

DNL (LSB)

–0.2

–0.4

–0.6

08076-011

20kΩ 50kΩ 100kΩ

0 256 512 768 1023

CODE (Decimal)

08076-120

Figure 10. R-DNL in R-Perf Mode vs. Code vs. Nominal Resistance (AD5272)

0.5

0.4

0.3

0.2

INL (LSB)

0.1

–0.1

+125°C

+25°C

–40°C

0

0 128 256 384 512 640 768 896 1023

CODE (Decimal)

RAW = 20kΩ

Figure 8. R-INL in Normal Mode vs. Code vs. Temperature (AD5272)

08076-014

Figure 11. R-INL in Normal Mode vs. Code vs. Nominal Resistance (AD5272)

Rev. C | Page 11 of 28

0.6

TA = 25°C

0.4

0.2

INL (LSB)

0

–0.2

–0.4

0 256 512 768 1023

CODE (Decimal)

20kΩ

50kΩ

100kΩ

08076-121

AD5272/AD5274

0.15

0.10

+125°C

+25°C

–40°C

RAW = 20kΩ

0.15

0.10

TA = 25°C

20kΩ

50kΩ

100kΩ

0.05

0

DNL (LSB)

–0.05

–0.10

–0.15

0 128 256 384 512 640 768 896 1023

CODE (Decimal)

Figure 12. R-DNL in Normal Mode vs. Code vs. Temperature (AD5272)

0.20

0.15

0.10

0.05

INL (LSB)

–0.05

+125°C

+25°C

–40°C

0

RAW = 20kΩ

0.05

0

–0.05

DNL (LSB)

–0.10

–0.15

–0.20

0 256 512 768 1023

08076-015

CODE (Decimal)

08076-122

Figure 15. R-DNL in Normal Mode vs. Code vs. Nominal Resistance (AD5272)

0.15

INL (LSB)

TA = 25°C

0.10

0.05

0

–0.05

20kΩ

100kΩ

–0.10

0 64 128 192 255

CODE (Decimal)

Figure 13. R-INL in R-Perf Mode vs. Code vs. Temperature (AD5274)

0.06

RAW = 20kΩ

0.04

0.02

0

–0.02

–0.04

DNL (LSB)

–0.06

–0.08

–0.10

–0.12

–0.14

0 64 128 192 255

CODE (Decimal)

+125°C

+25°C

–40°C

Figure 14. R-DNL in R-Perf Mode vs. Code vs. Temperature (AD5274)

–0.10

0 64 128 192 255

08076-013

CODE (Decimal)

08076-123

Figure 16. R-INL in R-Perf Mode vs. Code vs. Nominal Resistance (AD5274)

0.15

TA = 25°C

0.10

0.05

0

DNL (LS B)

–0.05

–0.10

–0.15

08076-012

20kΩ 100kΩ

0 64 128 192 255

CODE (Decimal)

08076-125

Figure 17. R-DNL in R-Perf Mode vs. Code vs. Nominal Resistance (AD5274)

Rev. C | Page 12 of 28

AD5272/AD5274

0.10

0.08

+125°C

+25°C

–40°C

RAW = 20kΩ

0.15

0.10

TA = 25°C

20kΩ

100kΩ

0.06

0.04

INL (LSB)

0.02

0

–0.02

0 64 128 192 255

CODE (Decimal)

Figure 18. R-INL in Normal Mode vs. Code vs. Temperature (AD5274)

DNL (LSB)

0.03

0.02

0.01

–0.01

–0.02

RAW = 20kΩ

0

+125°C

+25°C

–40°C

0.05

INL (LSB)

0

–0.05

–0.10

0 64 128 192 255

08076-016

CODE (Decimal)

08076-126

Figure 21. R-INL in Normal Mode vs. Code vs. Nominal Resistance (AD5274)

DNL (LSB)

0.010

0.008

0.006

0.004

0.002

100kΩ

20kΩ

0

TA = 25°C

–0.03

0 64 128 192 255

CODE (Decimal)

Figure 19. R-DNL in Normal Mode vs. Code vs. Temperature (AD5274)

500

400

300

200

100

0

–100

CURRENT (nA)

–200

–300

–400

–500

–40 –30 –20 –10 0 20 30 40 50 60 70 80 90 100 11010

Figure 20. Supply Current (I

ISS = 3V

TEMPERATURE (°C)

IDD = 5V

IDD = 3V

ISS = 5V

, ISS) vs. Temperature

DD

–0.002

0 64 128 192 255

08076-017

CODE (Decimal)

008076-027

Figure 22. R-DNL in Normal Mode vs. Code vs. Nominal Resistance (AD5274)

0.7

0.6

0.5

0.4

0.3

(mA)

DD

I

0.2

0.1

0

–0.1

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

08076-018

Figure 23. Supply Current (I

(V)

V

LOGIC

) vs. Digital Input Voltage

DD

08076-110

Rev. C | Page 13 of 28

AD5272/AD5274

50

45

40

35

30

25

20

15

10

RHEOSTAT MODE TEMPCO (ppm/° C)

5

0

0 256 512 768 1023

0 64 128 192 255

0

0x200 (0x80)

0x100 (0x40)

–10

0x080 (0x20)

–20

0x040 (0x10)

0x020 (0x08)

–30

0x010 (0x04)

GAIN (dB)

0x008 (0x02)

–40

0x004 (0x01)

0x002

–50

0x001

CODE (Decimal)

Figure 24. Tempco ΔR

/ΔT vs. Code

WA

VDD/VSS= 5V/0V

20kΩ

50kΩ

100kΩ

AD5272 (AD5274)

AD5272

AD5274

7

6

5

(mA)

4

WA_MAX

3

2

THEORETICAL I

1

0

0 256 512 768 1023

08076-019

0 64 128 192 255

CODE (Decimal )

VDD/VSS=5V/0V

20kΩ

50kΩ

100kΩ

AD5272

AD5274

08076-028

Figure 27. Theoretical Maximum Current vs. Code

GAIN (dB)

0

–10

–20

–30

–40

–50

–60

0x200 (0x80)

0x100 (0x40)

0x080 (0x20)

0x040 (0x10)

0x020 (0x08)

0x010 (0x04)

0x008 (0x02)

0x004 (0x01)

0x002

0x001

AD5272 (AD5274)

GAIN (dB)

–60

1k

10k

100k 1M 10M

FREQUENCY (Hz )

Figure 25. 20 kΩ Gain vs. Code vs. Frequency

0

0x200 (0x80)

0x100 (0x40)

–10

0x080 (0x20)

–20

0x040 (0x10)

0x020 (0x08)

–30

0x010 (0x04)

0x008 (0x02)

–40

0x004 (0x01)

0x002

–50

0x001

–60

1k

10k

100k 1M 10M

FREQUENCY (Hz)

Figure 26. 50 kΩ Gain vs. Code vs. Frequency

AD5272 (AD5274)

–70

1k

08076-031

10k

100k 1M 10M

FREQUENCY (Hz)

08076-041

Figure 28. 100 kΩ Gain vs. Code vs. Frequency

0

VDD/VSS = 5V/0V

CODE = HALF SCAL E

–10

–20

–30

–40

–50

PSRR (dB)

–60

–70

–80

–90

08076-032

50kΩ

100kΩ

20kΩ

100 1k 10k 100k

FREQUENCY (Hz )

8076-024

Figure 29. PSRR vs. Frequency

Rev. C | Page 14 of 28

AD5272/AD5274

0

VDD/VSS = 5V/0V

CODE = HALF SCALE

NOISE BW = 22kHz

V

= 1V rms

IN

–20

–40

–60

THD + N (dB)

–80

–100

100

0.03

0.02

0.01

0

1k

FREQUENCY (Hz)

10k

Figure 30. THD + N vs. Frequency

20kΩ

50kΩ

100kΩ

100k

20kΩ

50kΩ

100kΩ

08076-025

0

–10

–20

–30

–40

–50

THD + N (dB)

–60

–70

–80

–90

–100

0.001 0.01 0.1 1

VOLTAGE (V

VDD/VSS = 5V/0V

CODE = HAL F SCALE

f

= 1kHz

IN

NOISE BW = 22kHz

)

RMS

Figure 33. THD + N vs. Amplitude

0.0010

0.0005

0

VDD/VSS = 5V/0V

= 200µA

I

AW

CODE = HALF SCALE

20kΩ

50kΩ

100kΩ

08076-026

–0.01

VOLTAGE (V)

–0.02

–0.03

–0.04

–1 4 9 14 19

TIME (µs)

Figure 31. Maximum Glitch Energy

45

40

35

30

25

20

15

10

NUMBER OF CODES (AD5272)

5

0

2.7 3.2 3.7 4.2 4.7 5.2

VDD (V)

Figure 32. Maximum Code Loss vs. Temperature

TA = 25°C

20kΩ

50kΩ

100kΩ

11.25

10.00

8.75

7.50

6.25

5.00

3.75

2.50

1.25

0

08076-043

08076-021

NUMBER OF CODES (AD5274)

–0.0005

VOLTAGE (V)

–0.0010

–0.0015

0–10 10 20 30 40 50 60

TIME (µs)

Figure 34. Digital Feedthrough

70

60

50

40

30

20

NUMBER OF CODES (AD5272)

10

0

–40 –20 0 20 40 60 80 100 120

TEMPERATURE (° C)

VDD/VSS= 5V/0V

20kΩ

50kΩ

100kΩ

Figure 35. Maximum Code Loss vs. Power Supply Range

15.5

15.0

12.5

10.0

7.5

5.0

2.5

0

08076-046

NUMBER OF CODES (AD5274)

08076-020

Rev. C | Page 15 of 28

AD5272/AD5274

R

8

7

0.006

0.005

0.004

0.003

VDD/VSS = 5V/0V

I

= 10µA

AW

CODE = HALF SCALE

6

VOLTAGE (V)

5

4

0.07 0.09 0.11 0.13 0.15 0.17

Figure 36. V

TIME (Seco nds)

Waveform While Writing Fuse

EXT_CAP

0.002

RESISTANCE (%)

0.001

AW

∆

0

–0.001

–0.002

0 1000900800700600500400300200100

8076-029

OPERATIO N AT 150°C (Ho urs)

08076-038

Figure 37. Long-Term Drift Accelerated Average by Burn-In

Rev. C | Page 16 of 28

AD5272/AD5274

V

V

%

TEST CIRCUITS

Figure 38 to Figure 42 define the test conditions used in the Specifications section.

DUT

W

A

I

W

V

MS

08076-033

Figure 38. Resistor Position Nonlinearity Error

(Rheostat Operation; R-INL, R-DNL)

DUT

W

A

1GΩ

V

V

MS

Figure 41. Gain vs. Frequency

08076-036

MS

RWA=

I

DUT

A

CODE = 0x00

W

I

W

V

MS

RW =

W

R

WA

2

08076-034

Figure 39. Wiper Resistance

+ = VDD ±10

PSRR (dB) = 20 l og

I

W

V

DD

V+

W

A

V

PSS (%/%) =

MS

∆VMS%

∆V

DD

V

MS

V

DD

%

08076-035

DUT

I

CM

W

A

NC

+2.75V –2.75V

GND

Figure 42. Common Leakage Current

GND

GND

NC = NO CONNECT

+2.75V

–2.75V

08076-037

Figure 40. Power Supply Sensitivity (PSS, PSRR)

Rev. C | Page 17 of 28

AD5272/AD5274

THEORY OF OPERATION

The AD5272 and AD5274 digital rheostats are designed to

operate as true variable resistors for analog signals within the

terminal voltage range of V

contents determine the resistor wiper position. The RDAC

register acts as a scratchpad register, which allows unlimited

changes of resistance settings. The RDAC register can be

programmed with any position setting using the I

When a desirable wiper position is found, this value can be

stored in a 50-TP memory register. Thereafter, the wiper

position is always restored to that position for subsequent

power-up. The storing of 50-TP data takes approximately

350 ms; during this time, the AD5272/AD5274 is locked and

does not acknowledge any new command thereby preventing

any changes from taking place. The acknowledge bit can be

polled to verify that the fuse program command is complete.

The AD5272/AD5274 also feature a patented 1% end-to-end

resistor tolerance. This simplifies precision, rheostat mode, and

open-loop applications where knowledge of absolute resistance

is critical.

SERIAL DATA INTERFACE

The AD5272/AD5274 have 2-wire I2C-compatible serial interfaces. Each of these devices can be connected to an I

a slave device under the control of a master device; see Figure 3

for a timing diagram of a typical write sequence.

The AD5272/AD5274 support standard (100 kHz) and fast

(400 kHz) data transfer modes. Support is not provided for

10-bit addressing and general call addressing.

The AD5272/AD5274 each has a 7-bit slave address. The five

MSBs are 01011 and the two LSBs are determined by the state

of the ADDR pin. The facility to make hardwired changes to

ADDR allows the user to incorporate up to three of these

devices on one bus as outlined in Tabl e 11 .

SS

< V

< VDD. The RDAC register

TERM

2

C interface.

2

C bus as

The 2-wire serial bus protocol operates as follows: The master

initiates a data transfer by establishing a start condition, which

is when a high-to-low transition on the SDA line occurs while

SCL is high. The next byte is the address byte, which consists

of the 7-bit slave address and a R/

W

bit. The slave device corresponding to the transmitted address responds by pulling

SDA low during the ninth clock pulse (this is termed the

acknowledge bit). At this stage, all other devices on the bus

remain idle while the selected device waits for data to be

written to, or read from, its shift register.

Data is transmitted over the serial bus in sequences of nine

clock pulses (eight data bits followed by an acknowledge bit).

The transitions on the SDA line must occur during the low

period of SCL and remain stable during the high period of SCL.

When all data bits have been read or written, a stop condition is

established. In write mode, the master pulls the SDA line high

during the 10th clock pulse to establish a stop condition. In read

mode, the master issues a no acknowledge for the ninth clock

pulse (that is, the SDA line remains high). The master then

brings the SDA line low before the 10th clock pulse, and then

high during the 10th clock pulse to establish a stop condition.

SHIFT REGISTER

For the AD5272/AD5274, the shift register is 16 bits wide, as

shown in Figure 2. The 16-bit word consists of two unused bits,

which should be set to zero, followed by four control bits and

10 RDAC data bits (note that for the AD5274 only, the lower

two RDAC data bits are don’t care if the RDAC register is read

from or written to), and data is loaded MSB first (Bit 15). The

four control bits determine the function of the software command

(Tabl e 1 2 ). Figure 43 shows a timing diagram of a typical

AD5272/AD5274 write sequence.

The command bits (Cx) control the operation of the digital

potentiometer and the internal 50-TP memory. The data bits

(Dx) are the values that are loaded into the decoded register.

Table 11. Device Address Selection

ADDR A1 A0 7-Bit I2C Device Address

GND 1 1 0101111

VDD 0 0 0101100

NC (No Connection)1 1 0 0101110

1

Not available in bipolar mode. VSS < 0 V.

Rev. C | Page 18 of 28

AD5272/AD5274

WRITE OPERATION

It is possible to write data for the RDAC register or the control

register. When writing to the AD5272/AD5274, the user must

begin with a start command followed by an address byte (R/

= 0), after which the AD5272/AD5274 acknowledges that it is

prepared to receive data by pulling SDA low.

W

Two bytes of data are then written to the RDAC, the most

significant byte followed by the least significant byte; both of

these data bytes are acknowledged by the AD5272/AD5274. A

stop condition follows. The write operations for the AD5272/

AD5274 are shown in Figure 43.

A repeated write function gives the user flexibility to update the

device a number of times after addressing the part only once, as

shown in Figure 44.

SCL

SDA

START BY

MASTER

SCL

SDA

START BY

MASTER

19

1

0

011A1A0 00C3C2

FRAME 1

SERIAL BUS ADDRESS BYTE

SCL (CONTINUED)

SDA (CONTINUED)

R/W

ACK. BY

AD5272/AD5274

MOST SI GNIFICANT DATA BYTE

99

1

D7 D6 D5 D4 D3 D2 D1 D0

LEAST SIG NIFICANT DATA BYTE

C1 C0

FRAME 2

FRAME 3

D9 D8

ACK. BY

AD5272/AD5274

Figure 43. Write Command

19

1

0

0 1 1 A1 A0 R/W 0 0 C3 C2 C1 C0 D9 D8

ACK.

BY

FRAME 1

SERIAL BUS ADDRESS BYTE

SCL (CONTINUED)

AD52722/AD5274

MOST S IGNIFI CANT DATA BY TE

1

99

FRAME 2

91

ACK. BY

AD5272/AD5274

STOP BY

MASTER

91

ACK.

BY

AD52722/AD5274

8076-005

SDA (CONTI NUED)

SCL (CONTINUED)

SDA (CONTI NUED)

(CONTINUED)

SCL

(CONTINUED)

SDA

Figure 44. Multiple Write

D7 D6 D5 D4 D3 D2 D1 D0

ACK.

BY

LEAST SI GNIFI CANT DATA BY TE

199

0 0 C3C2C1C0D9D8

MOST SIG NIFICANT DATA BYTE

99

1

D7 D6 D5 D4 D3 D2 D1 D0

LEAST SI GNIFI CANT DATA BY TE

FRAME 3

FRAME 4

FRAME 5

AD52722/AD5274

ACK.

BY

AD52722/AD5274

ACK.

BY

AD52722/AD5274

STOP BY

MASTER

8076-006

Rev. C | Page 19 of 28

AD5272/AD5274

A

A

READ OPERATION

When reading data back from the AD5272/AD5274, the user

must first issue a readback command to the device, this begins

with a start command followed by an address byte (R/

after which the AD5272/AD5274 acknowledges that it is

prepared to receive data by pulling SDA low.

Two bytes of data are then written to the AD5272/AD5274, the

most significant byte followed by the least significant byte; both

of these data bytes are acknowledged by the AD5272/AD5274.

19

SCL

W

= 0),

A stop condition follows. These bytes contain the read instruction, which enables readback of the RDAC register, 50-TP

memory, or the control register. The user can then read back

the data beginning with a start command followed by an

address byte (R/

W

= 1), after which the device acknowledges

that it is prepared to transmit data by pulling SDA low. Two

bytes of data are then read from the device, as shown in .

Figure 45

A stop condition follows. If the master does not acknowledge

the first byte, the second byte is not transmitted by the

AD5272/AD5274.

91

SD

START BY

SCL

SD

START BY

MASTER

MASTER

1

0

19

0

0 1 1 A1 A0 R/W 0 0 C3 C2 C1 C0 D9 D8

ACK. BY

FRAME 1

SERIAL BUS ADDRESS BY TE

SCL (CONTI NUED)

SDA (CONTINUED)

1

0 1 1 A1 A0 R/W 0 0 X X X X D9 D8

FRAME 1

SERIAL BUS ADDRESS BYTE

SCL (CONTI NUED)

SDA (CONTINUED)

AD5272/AD5274

MOST SI GNIFICANT DATA BYTE

1

99

D7 D6 D5 D4 D3 D2 D1 D0

LEAST SIG NIFICANT DATA BYTE

ACK. BY

AD5272/AD5274

MOST SI GNIFICANT DATA BYTE

1

99

D7 D6 D5 D4 D3 D2 D1 D0

LEAST SIG NIFICANT DATA BYTE

FRAME 2

FRAME 3

FRAME 2

FRAME 3

ACK. BY

AD5272/AD5274

NO ACK. BY

MASTER

ACK. BY

AD5272/AD5274

STOP BY

MASTER

91

ACK. BY

MASTER

STOP BY

MASTER

08076-007

Figure 45. Read Command

Rev. C | Page 20 of 28

AD5272/AD5274

RDAC REGISTER

The RDAC register directly controls the position of the digital

rheostat wiper. For example, when the RDAC register is loaded

with all zeros, the wiper is connected to Terminal A of the

variable resistor. It is possible to both write to and read from

the RDAC register using the I

2

C interface. The RDAC register

is a standard logic register; there is no restriction on the number

of changes allowed.

50-TP MEMORY BLOCK

The AD5272/AD5274 contain an array of 50-TP programmable

memory registers, which allow the wiper position to be programmed up to 50 times. Tab l e 1 6 shows the memory map.

Command 3 in Tab l e 1 2 programs the contents of the RDAC

register to memory. The first address to be programmed is

Location 0x01, see Tab l e 1 6 , and the AD5272/AD5274 increments the 50-TP memory address for each subsequent program

until the memory is full. Programming data to 50-TP consumes

approximately 4 mA for 55 ms, and takes approximately 350 ms

to complete, during which time the shift register is locked preventing any changes from taking place. Bit C3 of the control

register in Ta ble 1 5 can be polled to verify that the fuse program

command was successful. No change in supply voltage is required

to program the 50-TP memory; however, a 1 μF capacitor on

the EXT_CAP pin is required as shown in Figure 47.

Prior to 50-TP activation, the AD5272/AD5274 is preset to

midscale on power-up. It is possible to read back the contents

of any of the 50-TP memory registers through the I

2

C interface

by using Command 5 in Tabl e 12 . The lower six LSB bits, D0 to

D5 of the data byte, select which memory location is to be read

back. A binary encoded version address of the most recently

programmed wiper memory location can be read back using

Command 6 in Tab l e 1 2 . This can be used to monitor the spare

memory status of the 50-TP memory block.

WRITE PROTECTION

On power-up, serial data input register write commands for

both the RDAC register and the 50-TP memory registers are

disabled. The RDAC write protect bit (Bit C1) of the control

register (see Ta b le 1 4 and Ta b le 1 5) is set to 0 by default. This

disables any change of the RDAC register content regardless of

the software commands, except that the RDAC register can be

refreshed from the 50-TP memory using the software reset,

Command 4, or through hardware by the

programming of the variable resistor wiper position (programming

the RDAC register), the write protect bit (Bit C1) of the control

register must first be programmed. This is accomplished by

loading the serial data input register with Command 7 (see

Tabl e 1 2

). To enable programming of the 50-TP memory block,

Bit C0 of the control register, which is set to 0 by default, must

first be set to 1.

RESET

pin. To enable

Table 12. Command Operation Truth Table

Command

Number

0 0 0 0 0 X X X X X X X X X X NOP: do nothing.

1 0 0 0 1 D9 D8 D7 D6 D5 D4 D3 D2 D12 D0

2 0 0 1 0 X X X X X X X X X X

3 0 0 1 1 X X X X X X X X X X

4 0 1 0 0 X X X X X X X X X X

53 0 1 0 1 X X X X D5 D4 D3 D2 D1 D0

6 0 1 1 0 X X X X X X X X X X

74 0 1 1 1 X X X X X X X D2 D1 D0

8 1 0 0 0 X X X X X X X X X X

9 1 0 0 1 X X X X X X X X X D0 Software shutdown.

D0 = 0; normal mode.

D0 = 1; shutdown mode.

1

X = don’t care.

2

AD5274 = don’t care.

3

See Table 16 for the 50-TP memory map.

4

See Table 15 for bit details.

Command[DB13:DB10] Data[DB9:B0]1

C3 C2 C1 C0 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Operation

2

Write contents of serial register

data to RDAC.

Read contents of RDAC wiper

register.

Store wiper setting: store RDAC

setting to 50-TP.

Software reset: refresh RDAC

with the last 50-TP memory

stored value.

Read contents of 50-TP from the

SDO output in the next frame.

Read address of the last 50-TP

programmed memory location.

Write contents of the serial

register data to the control

register.

Read contents of the control

register.

Rev. C | Page 21 of 28

AD5272/AD5274

Table 13. Write and Read to RDAC and 50-TP memory

DIN SDO1 Action

0x1C03 0xXXXX Enable update of wiper position and 50-TP memory contents through digital interface.

0x0500 0x1C03 Write 0x100 to the RDAC register, wiper moves to ¼ full-scale position.

0x0800 0x0500 Prepare data read from RDAC register.

0x0C00 0x100

0x1800 0x0C00 Prepare data read of last programmed 50-TP memory monitor location.

0x0000 0xXX19

0x1419 0x0000 Prepares data read from Memory Location 0x19.

0x2000 0x0100

0x0000 0xXXXX

1

X is don’t care.

Table 14. Control Register Bit Map

DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

0 0 0 0 0 0 C3 C2 C1 C0

Table 15. Control Register Description

Bit Name Description

C0 50-TP program enable

0 = 50-TP program disabled (default)

1 = enable device for 50-TP program

C1 RDAC register write protect

0 = wiper position frozen to value in 50-TP memory (default)1

1 = allow update of wiper position through a digital interface

C2 Resistor performance enable

0 = RDAC resistor tolerance calibration enabled (default)

1 = RDAC resistor tolerance calibration disabled

C3 50-TP memory program success bit

0 = fuse program command unsuccessful (default)

1 = fuse program command successful

1

Wiper position is frozen to the last value programmed in the 50-TP memory. Wiper freezes to midscale if 50-TP memory has not been previously programmed.

Table 16. Memory Map

Command Number

5

1

X is don’t care.

Stores RDAC register content into 50-TP memory. 16-bit word appears out of SDO, where last 10-bits contain the

contents of the RDAC Register 0x100.

NOP Instruction 0 sends a 16-bit word out of SDO, where the six LSBs last 6-bits contain the binary address of the last

programmed 50-TP memory location, for example, 0x19 (see Table 16).

Prepare data read from the control register. Sends a 16-bit word out of SDO, where the last 10-bits contain the contents

of Memory Location 0x19.

NOP Instruction 0 sends a 16-bit word out of SDO, where the last four bits contain the contents of the control register.

If Bit C3 = 1, fuse program command successful.

Data Byte [DB9:DB8]1

D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Register Contents

X X X 0 0 0 0 0 0 0 Reserved

X X X 0 0 0 0 0 0 1 1st programmed wiper location (0x01)

X X X 0 0 0 0 0 1 0 2nd programmed wiper location (0x02)

X X X 0 0 0 0 0 1 1 3rd programmed wiper location (0x03)

X X X 0 0 0 0 1 0 0 4th programmed wiper location (0x04)

… … … … … … … … … … …

X X X 0 0 0 1 0 1 0 10th programmed wiper location (0xA)

X X X 0 0 1 0 1 0 0 20th programmed wiper location (0x14)

X X X 0 0 1 1 1 1 0 30th programmed wiper location (0x1E)

X X X 0 1 0 1 0 0 0 40th programmed wiper location (0x28)

X X X 0 1 1 0 0 1 0 50th programmed wiper location (0x32)

Rev. C | Page 22 of 28

AD5272/AD5274

A

50-TP MEMORY WRITE-ACKNOWLEDGE POLLING

After each write operation to the 50-TP registers, an internal

2

write cycle begins. The I

C interface of the device is disabled.

To determine if the internal write cycle is complete and the

2

I

C interface is enabled, interface polling can be executed. I2C

interface polling can be conducted by sending a start condition,

followed by the slave address and the write bit. If the I

2

C interface

responds with an acknowledge (ACK), the write cycle is complete

and the interface is ready to proceed with further operations.

Otherwise, I

2

C interface polling can be repeated until it completes.

RESET

The AD5272/AD5274 can be reset through software by executing

Command 4 (see Tabl e 12 ) or through hardware on the low

pulse of the

RESET

pin. The reset command loads the RDAC

register with the contents of the most recently programmed 50-TP

memory location. The RDAC register loads with midscale if no

50-TP memory location has been previously programmed. Tie

RESET

to VDD if the

RESET

pin is not used.

RESISTOR PERFORMANCE MODE

This mode activates a new, patented 1% end-to-end resistor

tolerance that ensures a ±1% resistor tolerance on each code,

that is, code = half scale and R

= 10 kΩ ± 100 Ω. See Tab l e 2 ,

WA

Tabl e 3 , Ta bl e 5, and Tab l e 6 to check which codes achieve ±1%

resistor tolerance. The resistor performance mode is activated by

programming Bit C2 of the control register (see Tabl e 1 4 and

Tabl e 1 5 ).

SHUTDOWN MODE

The AD5272/AD5274 can be shut down by executing the software

shutdown command, Command 9 (see Tabl e 12 ), and setting

the LSB to 1. This feature places the RDAC in a zero-powerconsumption state where Terminal Ax is disconnected from

the wiper terminal. It is possible to execute any command from

Tabl e 1 2 while the AD5272 or AD5274 is in shutdown mode.

The part can be taken out of shutdown mode by executing

Command 9 and setting the LSB to 0, or by issuing a software

or hardware reset.

RDAC ARCHITECTURE

To achieve optimum performance, Analog Devices has patented the

RDAC segmentation architecture for all the digital potentiometers.

In particular, the AD5272/AD5274 employ a three-stage

segmentation approach, as shown in Figure 46. The AD5272/

AD5274 wiper switch is designed with the transmission gate

CMOS topology.

10-/8-BIT

ADDRESS

DECODER

Figure 46. Simplified RDAC Circuit

PROGRAMMING THE VARIABLE RESISTOR

Rheostat Operation—1% Resistor Tolerance

The nominal resistance between Terminal W and Terminal A, RWA,

is available in 20 kΩ, 50 kΩ, and 100 kΩ, and 1024-/256-tap points

accessed by the wiper terminal. The 10-/8-bit data in the RDAC

latch is decoded to select one of the 1024 or 256 possible wiper

settings. The AD5272/ AD5274 contain an internal ±1% resistor

tolerance calibration feature which can be disabled or enabled,

enabled by default, or by programming Bit C2 of the control

register (see Ta b le 1 5). The digitally programmed output resistance between the W terminal and the A terminal, R

calibrated to give a maximum of ±1% absolute resistance error

over both the full supply and temperature ranges. As a result,

the general equations for determining the digitally programmed

output resistance between the W terminal and A terminal are as

follows:

For the AD5272

D

DR ×=

)(

1024

For the AD5274

D

DR ×=

)(

256

where:

D is the decimal equivalent of the binary code loaded in the

10-/8-bit RDAC register.

R

is the end-to-end resistance.

WA

In the zero-scale condition, a finite total wiper resistance of

120 Ω is present. Regardless of which setting the part is operating in, take care to limit the current between the A terminal

to B terminal, W terminal to A terminal, and W terminal to

B terminal, to the maximum continuous current of ±3 mA, or

the pulse current specified in Tabl e 8. Otherwise, degradation or

possible destruction of the internal switch contact can occur.

R

L

R

L

(1)

R

WAWA

(2)

R

WAWA

R

M

S

W

R

M

R

W

W

R

W

08076-008

, is

WA

Rev. C | Page 23 of 28

AD5272/AD5274

V

EXT_CAP CAPACITOR

A 1 μF capacitor to VSS must be connected to the EXT_CAP pin

(see Figure 47) on power-up and throughout the operation of

the AD5272/AD5274.

AD5272/

AD5274

50_OTP

EXT_CAP

C1

1µF

Figure 47. EXT_CAP Hardware Setup

MEMORY

BLOCK

V

SS

V

SS

08076-009

TERMINAL VOLTAGE OPERATING RANGE

The positive VDD and negative VSS power supplies of the

AD5272/AD5274 define the boundary conditions for proper

2-terminal digital resistor operation. Supply signals present on

Ter m in a l A a nd Te rm ina l W t hat ex c ee d V

by the internal forward-biased diodes (see Figure 48). As soon as V

or VSS are clamped

DD

DD

The ground pins of the AD5272/AD5274 devices are primarily

used as digital ground references. To minimize the digital

ground bounce, join the AD5272/AD5274 ground terminal

remotely to the common ground. The digital input control

signals to the AD5272/AD5274 must be referenced to the

device ground pin (GND) and satisfy the logic level defined in

the Specifications section. An internal level shift circuit ensures

that the common-mode voltage range of the three terminals

extends from V

POWER-UP SEQUENCE

Because there are diodes to limit the voltage compliance at

Ter m in a l A a nd Te rm ina l W ( se e Figure 48), it is important to

power V

and Terminal W; otherwise, the diode is forward-biased such

that V

sequence is V

order of powering V

as long as they are powered after V

first sets the RDAC to midscale and then restores the last

programmed 50-TP value to the RDAC register.

DD/VSS

DD/VSS

to VDD, regardless of the digital input level.

SS

first before applying any voltage to Terminal A

are powered unintentionally. The ideal power-up

, GND, VDD, digital inputs, VA, and VW. The

SS

, VW, and digital inputs is not important

A

.

DD/VSS

is powered, the power-on preset activates, which

DD

A

W

V

SS

08076-109

Figure 48. Maximum Terminal Voltages Set by V

DD

and V

SS

Rev. C | Page 24 of 28

AD5272/AD5274

OUTLINE DIMENSIONS

3.10

3.00

2.90

10

6

3.10

3.00

2.90

PIN 1

IDENTIFIER

0.95

0.85

0.75

0.15

0.05

COPLANARITY

1

0.50 BSC

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-BA

Figure 49. 10-Lead Mini Small Outline Package [MSOP]

3.10

3.00 SQ

2.90

5.15

4.90

4.65

5

15° MAX

6°

0°

0.23

0.13

0.30

0.15

1.10 MAX

(RM-10)

Dimensions shown in millimeters

2.48

2.38

2.23

0.70

0.55

0.40

091709-A

0.50 BSC

PIN 1 INDEX

AREA

0.50

6

EXPOSED

PAD

10

1.74

1.64

1.49

0.40

0.80

0.75

0.70

SEATING

PLANE

TOP VIEW

0.30

0.25

0.20

0.30

0.05 MAX

0.02 NOM

0.20 REF

5

BOTTOM VIEW

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

1

1

P

N

I

R

O

C

I

A

T

N

I

D

)

5

1

.

R

0

(

121009-A

Figure 50. 10-Lead Frame Chip Scale Package [LFCSP_WD]

3 mm × 3mm Body, Very Thin, Dual Lead

(CP-10-9)

Dimensions shown in millimeters

Rev. C | Page 25 of 28

AD5272/AD5274

ORDERING GUIDE

Model1 R

AD5272BRMZ-20 20 1,024 −40°C to +125°C 10-Lead MSOP RM-10 DE6

AD5272BRMZ-20-RL7 20 1,024 −40°C to +125°C 10-Lead MSOP RM-10 DE6

AD5272BRMZ-50 50 1,024 −40°C to +125°C 10-Lead MSOP RM-10 DE7

AD5272BRMZ-50-RL7 50 1,024 −40°C to +125°C 10-Lead MSOP RM-10 DE7

AD5272BRMZ-100 100 1,024 −40°C to +125°C 10-Lead MSOP RM-10 DE5

AD5272BRMZ-100-RL7 100 1,024 −40°C to +125°C 10-Lead MSOP RM-10 DE5

AD5272BCPZ-20-RL7 20 1,024 −40°C to +125°C 10-Lead LFCSP_WD CP-10-9 DE4

AD5272BCPZ-100-RL7 100 1,024 −40°C to +125°C 10-Lead LFCSP_WD CP-10-9 DE3

AD5274BRMZ-20 20 256 −40°C to +125°C 10-Lead MSOP RM-10 DEE

AD5274BRMZ-20-RL7 20 256 −40°C to +125°C 10-Lead MSOP RM-10 DEE

AD5274BRMZ-100 100 256 −40°C to +125°C 10-Lead MSOP RM-10 DED

AD5274BRMZ-100-RL7 100 256 −40°C to +125°C 10-Lead MSOP RM-10 DED

AD5274BCPZ-20-RL7 20 256 −40°C to +125°C 10-Lead LFCSP_WD CP-10-9 DE9

AD5274BCPZ-100-RL7 100 256 −40°C to +125°C 10-Lead LFCSP_WD CP-10-9 DE8

EVAL-AD5272SDZ Evaluation Board

1

Z = RoHS Compliant Part.

(kΩ) Resolution Temperature Range Package Description Package Option Branding

AW

Rev. C | Page 26 of 28

AD5272/AD5274

NOTES

Rev. C | Page 27 of 28

AD5272/AD5274

NOTES

I2C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2009–2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D08076-0-11/10( C)

Rev. C | Page 28 of 28

Loading...

Loading...