Am8530H/Am85C30

Serial Communications Controller

1992 Technical Manual

A D V A N C E D M I C R O D E V I C E S

1992 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products

without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry

in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change

without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences

resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of

undescribed features or parameters.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

Trademarks

Z80 and ZBus are registered trademarks of Zilog, Inc.

Z8000, Z8030, and Z8530 are trademarks of Zilog, Inc.

MULTIBUS is a registered trademark of Intel Corporation

PAL is a registered trademark of Advanced Micro Devices, Inc.

ii

PREFACE

Thank you for your interest in the SCC, one of the most popular Serial Data ICs available

today. This manual is intended to provide answers to technical questions about the

Am8530H and Am85C30.

If you have already used the Am8530H and are familiar with the previous editions of this

Technical Manual, you will find that some chapters are virtually unchanged. The

Am8030’s functionality, however, has been omitted from this revision since a CMOS

Am8030 was not developed. You can, however, consult the previous Am8030/8530 Technical Manual revision for information pertaining to Am8030 operation.

Functional descriptions of enhancements added to the Am85C30 have been included in

this Technical Manual revision. These enhancements improve the Am85C30’s functionality and allow it to be used more effectively in high-speed applications. These enhancements include:

■ a 10 x 19-bit SDLC/HDLC frame status FIFO array

■ a 14-bit SDLC/HDLC frame byte counter

■ automatic SDLC/HDLC opening flag transmission

■ automatic SDLC/HDLC Tx Underrun/EOM flag resetting

■ automatic SDLC/HDLC Tx CRC generator presetting

■ RTS pin synchronization to closing SDLC/HDLC flag

■ DTR/REQ deactivation delay significantly reduced

■ external PCLK to RxC or TxC synchronization requirement eliminated for PCLK divide-

by-four operation

■ complete SDLC/HDLC CRC character reception

■ reduced INT response time

■ Write data setup time to rising edge of WR requirement eliminated

■ Write Registers WR3, WR4, WR5, and WR10 made readable

Most users read only chapters that are of interest to them. If you are designing the microcomputer hardware using the SCC as a peripheral, you will want to read the Applications

Section in Chapter 7. Application notes covering the interfacing of the Am8530H (pre Hstep and CMOS versions only) to the 8086/80186, 68000 processors and Am7960 Data

Coded Transceiver have been included.

As was the case with the NMOS SCC, some points to look out for when using the

Am85C30 are:

■ Follow the worksheet for initialization (Chapter 7). Unexplainable operations may occur if

this procedure is not followed.

■ Watch out for the Write Recovery time violation. The specification for this (Trc) was

changed on both the H-step and CMOS version. It is now referenced from falling edge to

falling edge of the Read/Write pulse. Trc is spec’d at 4 PCLKs for the NMOS H-step and 3

PCLKs (best case)/3.5 PCLKs for the Am85C30.

■ Ensure Mode bits are not changed when writing commands. Each Mode bit affects only

one function and a Command bit entry requires a rewrite of the entire register; therefore,

care must be taken to insure the integrity of the Mode bits whenever a new command is

issued.

■ Any unused input pins should be tied high.

TABLE OF CONTENTS

Chapter 1 General Information

1.1 Introduction 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Capabilities 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Block Diagram 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Pin Functions 1–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Pin Descriptions 1–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5.1 System Interface Pin Descriptions 1–8. . . . . . . . . . . . . . .

1.5.2 Serial Channel Pin Descriptions 1–9. . . . . . . . . . . . . . . .

Chapter 2 System Interface

2.1 Introduction 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Registers 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 System Timings 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Read Cycle 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2 Write Cycle 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.3 Interrupt Acknowledge Cycle 2–5. . . . . . . . . . . . . . . . . . .

2.4 Register Access 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Am85C30 Enhancement Register Access 2–7. . . . . . . . . . . . . .

2.6 Reset 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 3 I/O Programming Functional Description

3.1 Introduction 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Polling 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Interrupt Sources 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Interrupt Control 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Interrupt Enable Bit 3–4. . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2 Interrupt Pending Bit 3–5. . . . . . . . . . . . . . . . . . . . . . . . .

3.4.3 Interrupt Under Service Bit 3–5. . . . . . . . . . . . . . . . . . . .

3.4.4 Disable Lower Chain Bit 3–5. . . . . . . . . . . . . . . . . . . . . .

3.5 Interrupt Operations 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Multiple Interrupt Priority Resolution 3–6. . . . . . . . . . . . .

3.5.2 Interrupt Without Acknowledge 3–8. . . . . . . . . . . . . . . . .

3.5.3 Interrupt With Acknowledge With Vector 3–8. . . . . . . . . .

3.5.4 Interrupt With Acknowledge Without Vector 3–10. . . . . . .

3.5.5 Lower Priority Interrupt Masking 3–10. . . . . . . . . . . . . . . .

3.6 Receive Interrupts 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1 Receive Interrupts Disabled 3–10. . . . . . . . . . . . . . . . . . . .

3.6.2 Receive Interrupt on First Character or

Special Condition 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3 Receive Interrupt on All Receive Characters or

Special Conditions 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.4 Receive Interrupt on Special Conditions 3–11. . . . . . . . . .

3.7 Transmit Interrupts 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 External/Status Interrupts 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1 Sync/Hunt 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2 Break/Abort 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.3 Zero Count 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.4 Tx Underrun/EOM 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.5 Clear To Send 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.6 Data Carrier Detect 3–15. . . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

AMD

3.9 Block Transfers 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.1 Wait on Transmit 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.2 Wait on Receive 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3 DMA Requests 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3.1 DMA Request on Transmit

(using W/REQ) 3–17. . . . . . . . . . . . . . . . . . . . . .

3.9.3.2 DMA Request on Transmit

(using DTR/REQ) 3–18. . . . . . . . . . . . . . . . . . . .

3.9.3.3 DTR/REQ Deactivation Timing 3–19. . . . . . . . . .

3.9.3.4 DMA Request on Receive (using W/REQ) 3–20.

Chapter 4 Data Communication Modes Functional Description

4.1 Introduction 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Protocols 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Asynchronous 4–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2 Synchronous Transmission 4–4. . . . . . . . . . . . . . . . . . . .

4.2.2.1 Synchronous Character-Oriented

Protocol 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2.2 Synchronous Bit-Oriented 4–4. . . . . . . . . . . . . .

4.3 Mode Selection 4–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 Receiver Overview 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1 Rx Character Length 4–7. . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2 Rx Parity 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3 Rx Modem Control 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 Transmitter Overview 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.1 Tx Character Length 4–9. . . . . . . . . . . . . . . . . . . . . . . . .

4.5.2 Tx Parity 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.3 Break Generation 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5.4 Transmit Modem Control 4–11. . . . . . . . . . . . . . . . . . . . . .

4.5.5 Auto RTS Reset 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Asynchronous Mode Operation 4–12. . . . . . . . . . . . . . . . . . . . . . .

4.6.1 Receiver Operation 4–12. . . . . . . . . . . . . . . . . . . . . . . . . .

4.6.1.1 Receiver Initialization 4–12. . . . . . . . . . . . . . . . .

4.6.1.2 Framing Error 4–12. . . . . . . . . . . . . . . . . . . . . . .

4.6.1.3 Break Detection 4–13. . . . . . . . . . . . . . . . . . . . . .

4.6.1.4 Clock Selection 4–13. . . . . . . . . . . . . . . . . . . . . .

4.6.2 Transmitter Operation 4–13. . . . . . . . . . . . . . . . . . . . . . . .

4.6.2.1 Transmitter Initialization 4–13. . . . . . . . . . . . . . .

4.6.2.2 Stop Bit Selection 4–13. . . . . . . . . . . . . . . . . . . .

4.7 SDLC Mode Operation 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.1 Receiver Operation 4–14. . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.1.1 Flag Detect Output 4–14. . . . . . . . . . . . . . . . . . .

4.7.1.2 Receiver Initialization 4–14. . . . . . . . . . . . . . . . .

4.7.1.3 10x19-Bit Frame Status FIFO 4–14. . . . . . . . . . .

4.7.1.3.1 FIFO Enabling/Disabling 4–15. . . . . . . .

4.7.1.3.2 FIFO Read Operation 4–15. . . . . . . . . .

4.7.1.3.3 FIFO Write Operation 4–15. . . . . . . . . .

4.7.1.3.4 14-Bit Byte Counter 4–15. . . . . . . . . . .

4.7.1.3.5 Am85C30 Frame Status

FIFO Operation Clarification 4–18. . . . .

4.7.1.3.6 Am85C30 Aborted Frame

Handling When Using the 10x19

Frame Status FIFO 4–19. . . . . . . . . . . .

4.7.1.4 Address Search Mode 4–19. . . . . . . . . . . . . . . . .

4.7.1.5 Abort Detection 4–20. . . . . . . . . . . . . . . . . . . . . .

4.7.1.6 Residue Bits 4–21. . . . . . . . . . . . . . . . . . . . . . . .

4.7.2 SDLC Mode CRC Polynomial Selection 4–21. . . . . . . . . .

4.7.2.1 Rx CRC Initialization 4–22. . . . . . . . . . . . . . . . . .

4.7.2.2 Rx CRC Enabling 4–22. . . . . . . . . . . . . . . . . . . .

AMD

Table of Contents

4.7.2.3 CRC Error 4–22. . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.2.4 CRC Character Reception 4–22. . . . . . . . . . . . . .

4.7.3 End of Frame (EOF) 4–26. . . . . . . . . . . . . . . . . . . . . . . . .

4.8 Transmitter Operation 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.1 Transmitter Initialization 4–27. . . . . . . . . . . . . . . . . . . . . . .

4.8.2 Mark/Flag Idle Generation 4–27. . . . . . . . . . . . . . . . . . . . .

4.8.3 Auto Flag Mode 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.4 Abort Generation 4–28. . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.5 Auto Transmit CRC Generator Preset 4–28. . . . . . . . . . . .

4.8.6 CRC Transmission 4–28. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.8.7 Auto Tx Underrun/EOM Latch Reset 4–29. . . . . . . . . . . . .

4.8.8 Transmitter Disabling 4–29. . . . . . . . . . . . . . . . . . . . . . . . .

4.8.9 NRZI Mode Transmitter Disabling 4–29. . . . . . . . . . . . . . .

4.9 SDLC Loop Mode 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.1 Going on Loop 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.1.1 On Loop Program Sequence 4–31. . . . . . . . . . . .

4.9.1.2 On Loop Message Transmission 4–31. . . . . . . . .

4.9.1.3 On Loop Transmit Message

Programming Sequence 4–31. . . . . . . . . . . . . . .

4.9.2 Going off Loop 4–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.9.2.1 Off Loop Programming Sequence 4–32. . . . . . . .

4.9.3 SDLC Loop Initialization 4–32. . . . . . . . . . . . . . . . . . . . . .

4.9.4 SDLC Loop NRZI Encoding Enabled 4–32. . . . . . . . . . . . .

4.10 Synchronous Mode Operation 4–32. . . . . . . . . . . . . . . . . . . . . . . .

4.10.1 Receiver Operation 4–32. . . . . . . . . . . . . . . . . . . . . . . . . .

4.10.1.1 SYNC Detect Output 4–33. . . . . . . . . . . . . . . . . .

4.10.1.1.1 MONOSYNC Mode 4–33. . . . . . . . .

4.11.1.2 BISYNC Mode 4–33. . . . . . . . . . . . . . . . . . . . . . .

4.10.1.2 SYNC Character Length 4–34. . . . . . . . . . . . . . .

4.10.1.3 Receiver Initialization 4–34. . . . . . . . . . . . . . . . .

4.10.1.4 Sync Character Removal 4–34. . . . . . . . . . . . . . .

4.10.1.5 CRC Polynomial Selection 4–36. . . . . . . . . . . . .

4.10.1.5.1 Rx CRC Initialization 4–36. . . . . . . .

4.10.1.5.2 Rx CRC Enabling 4–36. . . . . . . . . . .

4.10.1.5.3 Rx CRC Character Exclusion 4–36. .

4.10.1.5.4 CRC Error 4–37. . . . . . . . . . . . . . . . .

4.10.2 Transmitter Operation 4–37. . . . . . . . . . . . . . . . . . . . . . . .

4.10.2.1 Transmitter Initialization 4–38. . . . . . . . . . . . . . .

4.10.2.2 CRC Polynomial Selection 4–38. . . . . . . . . . . . .

4.10.2.2.1 Tx CRC Initialization 4–38. . . . . . . . .

4.10.2.2.2 Tx CRC Enabling 4–38. . . . . . . . . . .

4.10.2.2.3 CRC Transmission 4–38. . . . . . . . . .

4.10.2.2.4 Tx CRC Character Exclusion 4–39. .

4.10.2.3 Transparent Transmission 4–39. . . . . . . . . . . . . .

4.10.2.4 Transmitter to Receiver Synchronization 4–39. . .

4.10.2.4.1 Transmitter Disabling 4–40. . . . . . . .

4.10.2.5 External SYNC Mode 4–40. . . . . . . . . . . . . . . . .

4.10.2.5.1 SDLC External SYNC Mode 4–41. . .

4.10.2.5.2 Synchronous External

Sync Mode 4–41. . . . . . . . . . . . . . . .

Chapter 5 Support Circuitry Programming

5.1 Introduction 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Clock Options 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Crystal Oscillator 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.2 Receive Clock Source 5–4. . . . . . . . . . . . . . . . . . . . . . . .

5.2.3 Transmit Clock Source 5–4. . . . . . . . . . . . . . . . . . . . . . .

5.2.4 Clock Programming 5–5. . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Baud Rate Generator (BRG) 5–6. . . . . . . . . . . . . . . . . . . . . . . . .

Table of Contents

AMD

5.3.1 BRG Clock Source 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 BRG Enabling/Disabling 5–8. . . . . . . . . . . . . . . . . . . . . .

5.3.3 BRG Initialization 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Data Encoding/Decoding 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.1 NRZ (Non-Return to Zero) 5–9. . . . . . . . . . . . . . . . . . . . .

5.4.2 NRZI (Non-Return to Zero Inverted) 5–9. . . . . . . . . . . . .

5.4.3 FM1 (Biphase Mark) 5–10. . . . . . . . . . . . . . . . . . . . . . . . .

5.4.4 FM0 (Biphase Space) 5–10. . . . . . . . . . . . . . . . . . . . . . . .

5.4.5 Manchester Decoding 5–10. . . . . . . . . . . . . . . . . . . . . . . .

5.4.6 Data Encoding Programming 5–10. . . . . . . . . . . . . . . . . . .

5.5 Digital Phase-Locked Loop (DPLL) 5–10. . . . . . . . . . . . . . . . . . . .

5.5.1 DPLL Clock Source 5–11. . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.2 DPLL Enabling 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.3 DPLL Modes 5–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.3.1 NRZI Mode 5–11. . . . . . . . . . . . . . . . . . . . . . . . .

5.5.3.2 FM Mode 5–12. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.3.3 Manchester Decoding Mode 5–13. . . . . . . . . . . .

5.5.3.4 FM Mode DPLL Receive Status 5–13. . . . . . . . .

5.5.4 DPLL Initialization 5–15. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.5 Am85C30-16 DPLL Operation at 32 MHz 5–15. . . . . . . . .

5.5.5.1 Introduction 5–15. . . . . . . . . . . . . . . . . . . . . . . . .

5.5.5.2 Benefit 5–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.5.3 Applications 5–15. . . . . . . . . . . . . . . . . . . . . . . . .

5.5.5.4 Description 5–15. . . . . . . . . . . . . . . . . . . . . . . . .

5.5.5.5 Competition 5–15. . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Diagnostic Modes 5–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.1 Local Loopback 5–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.2 Auto Echo 5–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 6 Register Description

6.1 Introduction 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2 Write Registers 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.1 Write Register 0 (Command Register) 6–5. . . . . . . . . . . .

6.2.2 Write Register 1 (Transmit/Receive Interrupt

and Data Transfer Mode Definition) 6–7. . . . . . . . . . . . . .

6.2.3 Write Register 2 (Interrupt Vector) 6–9. . . . . . . . . . . . . . .

6.2.4 Write Register 3 (Receive Parameters

and Control) 6–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.5 Write Register 4 (Transmit/Receiver

Miscellaneous Parameters and Modes) 6–11. . . . . . . . . .

6.2.6 Write Register 5 (Transmit Parameter

and Controls) 6–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.2.7 Write Register 6 (SYNC Characters or

SDLC Address Field) 6–15. . . . . . . . . . . . . . . . . . . . . . . . .

6.2.8 Write Register 7 (SYNC Character or SDLC

FLAG/SDLC Option Register) 6–17. . . . . . . . . . . . . . . . . .

6.2.9 Write Register 8 (Transmit Buffer) 6–18. . . . . . . . . . . . . . .

6.2.10 Write Register 9 (Master Interrupt Control) 6–18. . . . . . . .

6.2.11 Write Register 10 (Miscellaneous Transmitter/

Receiver Control Bits) 6–20. . . . . . . . . . . . . . . . . . . . . . . .

6.2.12 Write Register 11 (Clock Mode Control) 6–23. . . . . . . . . .

6.2.13 Write Register 12 (Lower Byte of Baud

Rate Generator Time Constant) 6–26. . . . . . . . . . . . . . . .

6.2.14 Write Register 13 (Upper Byte of Baud

Rate Generator Time Constant) 6–26. . . . . . . . . . . . . . . .

6.2.15 Write Register 14 (Miscellaneous Control Bits) 6–27. . . . .

6.2.16 Write Register 15 (External/Status

Interrupt Control) 6–29. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Read Registers 6–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AMD

Table of Contents

6.3.1 Read Register 0 (Transmit/Receive Buffer

Status and External Status) 6–30. . . . . . . . . . . . . . . . . . . .

6.3.2 Read Register 1 6–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.3 Read Register 2 6–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.4 Read Register 3 6–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.5 Read Register 6 6–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.6 Read Register 7 6–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.7 Read Register 8 6–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.8 Read Register 10 6–37. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.9 Read Register 12 6–38. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.10 Read Register 13 6–38. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3.11 Read Register 15 6–39. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chapter 7 SCC Application Notes

7.1 Am8530H Initialization 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.1 Introduction 7–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1.1.1 Register Overview 7–3. . . . . . . . . . . . . . . . . . . .

7.1.1.2 Initialization Procedure 7–4. . . . . . . . . . . . . . . .

7.1.1.3 Initialization Table Generation 7–6. . . . . . . . . . .

7.1.1.4 Reset Conditions 7–6. . . . . . . . . . . . . . . . . . . . .

7.2 Polled Asynchronous Mode 7–7. . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.1 Introduction 7–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.2 SCC Interface 7–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.3 SCC Initialization 7–8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.2.3.1 SCC Operating Mode Programming 7–9. . . . . .

7.2.3.2 SCC Operating Mode Enables 7–10. . . . . . . . . .

7.2.4 Transmit and Receive Routines 7–10. . . . . . . . . . . . . . . . .

7.3 Interrupt Without Intack Asynchronous Mode 7–11. . . . . . . . . . . .

7.3.1 Introduction 7–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3.2 SCC Interface 7–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3.3 SCC Initialization 7–11. . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3.3.1 SCC Operating Modes Programming 7–12. . . . .

7.3.3.2 SCC Operating Mode Enables 7–13. . . . . . . . . .

7.3.3.3 SCC Operating Mode Interrupts 7–13. . . . . . . . .

7.3.4 Interrupt Routine 7–14. . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.4 Interfacing to the 8086/80186 7–15. . . . . . . . . . . . . . . . . . . . . . . .

7.4.1 8086 (Also Called iAPX86) Overview 7–15. . . . . . . . . . . .

7.4.1.1 The 8086 and Am8530H Interface 7–15. . . . . . .

7.4.1.2 Initialization Routines 7–18. . . . . . . . . . . . . . . . .

7.5 Interfacing to the 68000 7–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.1 68000 Overview 7–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.2 The 68000 and Am8530H Without Interrupts 7–21. . . . . .

7.5.3 The 68000 and Am8530H With Interrupts 7–23. . . . . . . . .

7.5.4 The 68000 and Am8530H With Interrupts

via a PAL Device 7–25. . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.6 Am7960 and Am8530H Application 7–26. . . . . . . . . . . . . . . . . . . .

7.6.1 Distributed Data Processing Overview 7–26. . . . . . . . . . .

7.6.2 Data Communications at the Physical Layer 7–27. . . . . . .

7.6.3 Hardware Considerations 7–28. . . . . . . . . . . . . . . . . . . . .

7.6.4 Software Considerations 7–32. . . . . . . . . . . . . . . . . . . . . .

CHAPTER 1

General Information

1.1 Introduction 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Capabilities 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Block Diagram 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Pin Functions 1–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Pin Descriptions 1–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5.1 System Interface Pin Descriptions 1–8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5.2 Serial Channel Pin Descriptions 1–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–1

General InformationAMD

1–2

CHAPTER 1

General Information

1.1 INTRODUCTION

The Am85C30 and Am8530H SCCs (Serial Communications Controller) are dual channel, multiprotocol data communications peripherals designed for use with 8- and 16-bit

microprocessors. The SCC functions as a serial-to-parallel, parallel-to-serial converter/

controller. The SCC can be software configured to satisfy a wide variety of serial communications applications, including: Bus Architectures (full- and half-duplex), Token Passing

Ring (SDLC Loop mode), and Star configurations (similar to SLAN).

The SCC contains a variety of internal functions including on-chip baud rate generators,

digital phase-lock loops, and crystal oscillators, which dramatically reduce the need for

external logic. In addition, SDLC/HDLC enhancements have been added to the Am85C30

that allow it to be used more effectively in high speed applications.

The SCC handles asynchronous formats, synchronous character-oriented protocols such

as IBM BISYNC, and Synchronous bit-oriented protocols such HDLC and IBM SDLC.

This versatile device supports virtually any serial data transfer application (telecommunications, cassette, diskette, tape drivers, etc.).

The device can generate and check CRC codes in any Synchronous mode. The SCC

also has facilities for Modem controls in both channels. In applications where these controls are not needed, the Modem controls can be used for general purpose I/O.

With access to the Write registers and Read registers in each channel, the user can configure the SCC so that it can handle all asynchronous formats regardless of data size,

number of stop bits, or parity requirements. The SCC also accommodates all synchronous formats including character, byte, and bit-oriented protocols.

Within each operating mode, the SCC also allows for protocol variations by handling odd

or even parity bits, character insertion or deletion, CRC generation and checking, break/

abort generation and detection, and many other protocol-dependent features.

Unless otherwise stated, the functional description in this Technical Manual applies to

both the NMOS Am8530H and CMOS Am85C30. When the enhancements in the

Am85C30 are disabled, it is completely downward compatible with the Am8530H.

1.2 CAPABILITIES

■ Two independent full-duplex channels

■ Synchronous data rates:

– Up to 1/4 of the PCLK (i.e., 4 Mbit/sec. maximum data rate with 16 MHz PCLK

Am85C30)

– Up to 1Mbit/second with a 16 MHz clock rate (FM encoding using DPLL in

Am85C30)

– Up to 500 Kbit/second with 16 MHz clock rate (NRZI encoding using DPLL in

Am85C30)

1–3

General InformationAMD

■ Asynchronous capabilities:

– 5, 6, 7, or 8 bits per character

– 1, 1-1/2, or 2 stop bits

– Odd or Even Parity

– x1, 16, 32, or 64 clock modes

– Break generation and detection

– Parity, Overrun and Framing Error detection

■ Character-Oriented synchronous capabilities:

– Internal or external character synchronization

– 1 or 2 sync characters in separate registers

– Automatic CRC generation/detection

■ SDLC/HLDC capabilities:

– Abort sequence generation and checking

– Automatic zero bit insertion and deletion

– Automatic flag insertion between messages

– Address field recognition

– I-Field residue handling

– CRC generation/detection

– SDLC Loop mode with EOP recognition/loop entry and exit

■ Receiver data registers quadruply buffered. Transmitter data register doubly buffered

■ NRZ, NRZI, or FM encoding/decoding and Manchester decoding

■ Baud-rate generator in each channel

■ A DPLL in each channel for clock recovery

■ Crystal oscillator in each channel

■ Local Loopback and Auto Echo modes

In addition, the Am85C30 provides enhancements which allow it to be used more effectively in high speed SDLC/HDLC applications. These enhancements include:

– 10 x 19-bit SDLC/HDLC frame status FIFO

– 14-bit SDLC/HDLC frame byte counter

– Automatic SDLC/HDLC opening Flag transmission

– Automatic SDLC/HDLC Tx Underrun/EOM Flag reset

– Automatic SDLC/HDLC CRC generator preset

– TxD forced High in SDLC NRZI mode when in mark idle

– RTS synchronization to closing SDLC/HDLC Flag

– DTR/REQ DMA request deactivation delay reduced

– External PCLK to RTxC or TRxC synchronization requirement removed for one fourth

PCLK operation

– Reduced Interrupt response time

– Reduced Read/Write access recovery time (Trc) to 3 PCLK best case (3 1/2 PCLK

worst case)

– Improved WAIT timing

Other enhancements which make the Am85C30 more user friendly include:

– Write data valid setup time to negative edge of write strobe requirement eliminated

– Write Registers WR3, WR4, WR5, WR10 and WR7′ are readable

– Complete reception of SDLC/HDLC CRC characters

– Lower priority interrupt masking without INTACK generation

1–4

General Information AMD

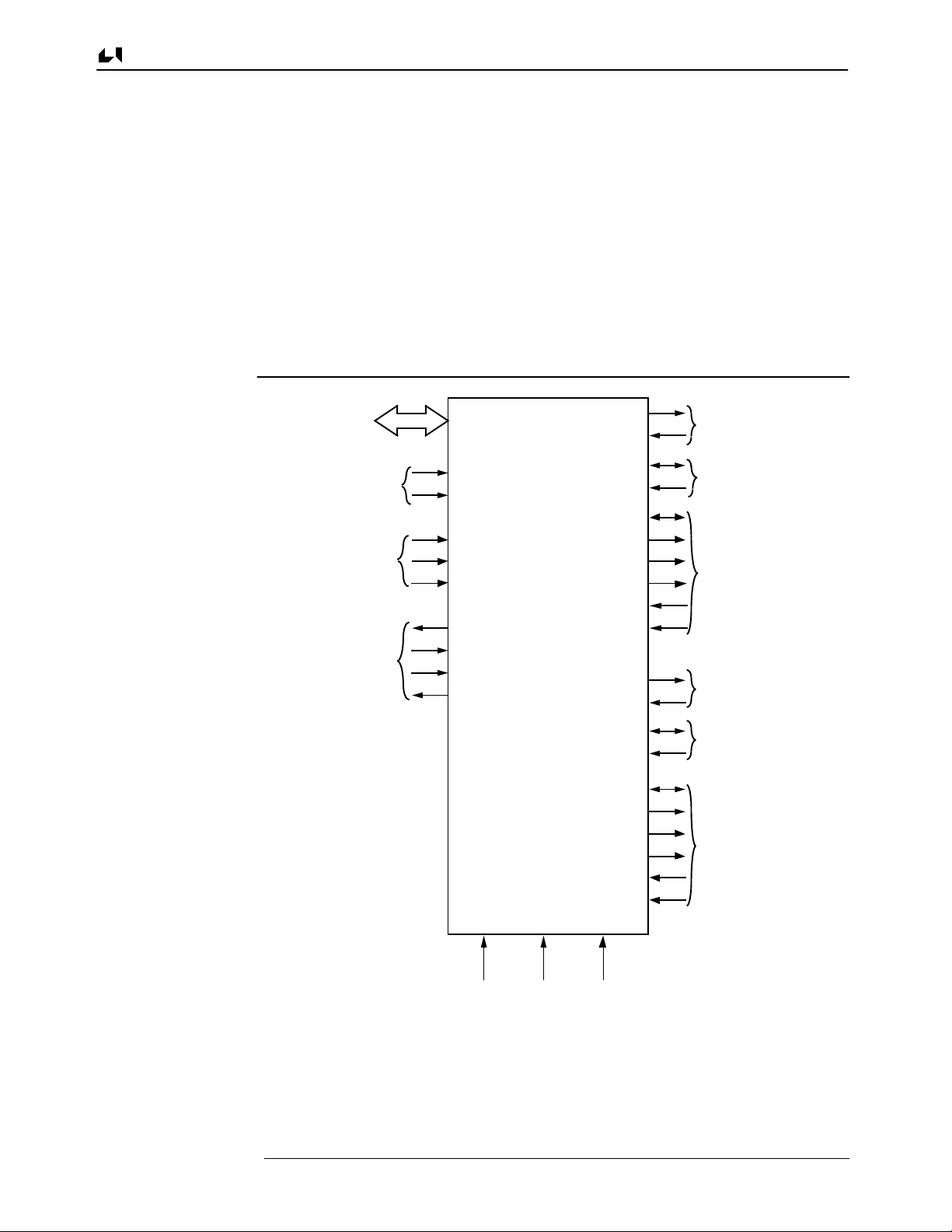

1.3 BLOCK DIAGRAM

Figure 1–1 depicts the block diagram of the Am8530H and Figure 1–2 the block diagram

of the Am85C30. Data being received enters the receive data pins and follows one of

several data paths, depending on the state of the control logic. The contents of the registers and the state of the external control pins establish the internal control logic. Transmitted data follows a similar pattern of control, register, and external pin definition.

Baud

Int

Cont

Logic

Rate

Gen

A

Ch A

Reg

Channel

A

Discrete

Control and

Status A

Serial

Data

Channel Clocks

SYNC

Wait/Request

Modem, DMA,

or

Other Controls

Cont

Data

Data

Control

5

8

CP

Bus

I/O

Cont

Lines

Internal Bus

Discrete

Control and

Int

Int

Cont

Logic

Ch B

Reg

Baud

Rate

Gen

B

Status B

Channel

B

Modem, DMA,

or

Other Controls

Serial

Data

Channel Clocks

SYNC

Wait/Request

07513C-001A

Figure 1–1. Am8530H Block Diagram

Channel A

Baud

Rate

Generator

Internal

Control

Logic

8

CPU

Bus I/O

5

Channel A

Registers

Internal Bus

10 x 19-Bit

Frame

Status

FIFO

Transmitter/

Receiver

Control

Logic

TxDA

RxDA

RTxCA

TRxCA

SYNCA

RTSA

CTSA

DCDA

Interrupt

Control

Lines

+5 V GND PCLK

Interrupt

Control

Logic

Channel B

Registers

Channel B

Figure 1–2. Am85C30 Block Diagram

TxDB

RxDB

RTxCB

TRxCB

SYNCB

RTSB

CTSB

DCDB

10216A-001A

1–5

General InformationAMD

1.4 Pin Functions

The SCC pins are divided into seven functional groups: Address/Data, Bus Timing and

Reset, Device Control, Interrupt, Serial Data (both channels), Peripheral Control (both

channels), and Clocks (both Channels). Figures 1–3 and 1–4 show the pins in each functional group for the 40- and 44-pin SCC versions.

The Address/Data group consists of the bidirectional lines used to transfer data between

the CPU and the SCC. The direction of these lines depends on whether the SCC is selected and whether the operation is a Read or a Write.

The Timing and Control groups designate the type of transaction to occur and when this

transaction will occur. The Interrupt group provides inputs and outputs to conform to the

Z-Bus specifications for handling and prioritizing interrupts. The remaining groups are divided into Channel A and Channel B groups for serial data (transmit or receive), peripheral control (such as DMA or Modem), and the input and output lines for the receive and

transmit clocks.

Data

Bus

Bus

Timing

and Reset

Control

Interrupt

8

D0- D

7

RD

WR

A/B

CE

D/C

INT

INTACK

IEI

IEO

Am85C30/

Am8530H

SCC

TxDA

RxDA

TRxCA

RTxCA

SYNCA

W/REQA

DTR/REQA

RTSA

CTSA

DCDA

TxDB

RxDB

TRxCB

RTxCB

SYNCB

W/REQB

DTR/REQB

RTSB

CTSB

DCDB

Serial

Data

Channel

Clocks

Channel

Controls

for Modem,

DMA, or

Other

Serial

Data

Channel

Clocks

Channel

Controls

for Modem,

DMA, or

Other

1–6

+5 V PCLK

GND

Figure 1–3. SCC Pin Functions

10216A-004A

General Information AMD

D

D

D

D

INT

IEO

IEI

INTACK

+5 V

W/REQA

SYNCA

RTxCA

RxDA

TRxCA

TxDA

DTR/REQA

RTSA

CTSA

DCDA

PCLK

7

INT

D

1

1

2

3

3

5

4

7

5

6

7

Am8530H

8

Am85C30

9

10

11

12

14

15

16

17

18

19

20

5

3

D

D

0

1

D

D

D

40

39

38

37

36

35

34

33

32

31

W/REQB

30

29

SYNCB

2813

RTxCB

27

RxDB

26

TRxCB

25

TxDB

DTR/REQB

24

RTSB

23

CTSB

22

DCDB

21

2D4D6

D

0

D

2

D

4

D

6

RD

WR

A/B

CE

D/C

GND

RD

WR

IEO

IEI

INTACK

+5 V

W/REQA

SYNCA

RTxCA

RxDA

TRxCA

TxDA

NC

7

8

9

10

11

12

13

14

15

16

17

6 5

NC

/REQA

DTR

4 3 2 1

Am85C30

RTSA

CTSA

DCDA

PCLK

DCDB

CTSB

RTSB

4041424344

2827262524232221201918

DTR/REQB

39

38

37

36

35

34

33

32

31

30

29

NC

A/B

CE

D/C

NC

GND

W/REQB

SYNCB

RTxCB

RxDB

TRxCB

TxDB

Figure 1–4. Pin Designation for 40- and 44-Pin SCC

10216A-003A

1–7

General InformationAMD

1.5 PIN DESCRIPTIONS

Figure 1–4 designates the pin locations and signal names for the 40- and 44-pin SCC

versions.

1.5.1 System Interface Pin Descriptions

A/B — Channel A/Channel B Select (input, Channel A active High)

This signal selects the channel in which the Read or Write operation occurs and must be

valid prior to the read or write strobe.

CE — Chip Enable (input, active Low)

This signal selects the SCC for operation. It must remain active throughout the bus

transaction.

D0–D7 — Data Lines (bidirectional, 3-state)

These I/O lines carry data or control information to and from the SCC.

D/C — Data/Control (input, data active High)

This signal defines the type of information transfer performed by the SCC: data or control.

The state of this signal must be valid prior to the read or write strobe.

RD — Read (input, active Low)

This signal indicates a Read operation and, when the SCC is selected, enables the SCC

bus drivers. During the interrupt acknowledge cycle, this signal gates the interrupt vector

onto the bus provided that the SCC is the highest priority device requesting an interrupt.

WR — Write (input, active Low)

When the SCC is selected, this signal indicates a Write operation. On the NMOS

Am8530H data must be valid prior to the rising edge of write strobe. The Am85C30 does

not share this requirement. The coincidence of RD and WR is interpreted as a Reset.

IEI* — Interrupt Enable In (input, active High)

IEI is used with IEO to form an interrupt daisy chain when there is more than one interrupt-driven device. A High on IEI indicates that no other higher priority device has an Interrupt Under Service (IUS) or is requesting an interrupt.

IEO — Interrupt Enable Out (output, active High)

IEO is High only if IEI is High and the CPU is not servicing an SCC or SCC interrupt or

the controller is not requesting an interrupt (interrupt acknowledge cycle only). IEO is connected to the next lower priority device’s IEI input and thus inhibits interrupts from lower

priority devices.

INTACK* — Interrupt Acknowledge (input, active Low)

This signal indicates an active interrupt acknowledge cycle. During this cycle, the interrupt

daisy chain settles. When RD becomes active, the SCC places an interrupt vector on the

data bus (if IEI is High). INTACK is latched by the rising edge of PCLK.

INT — Interrupt Request (output, open-drain, active Low)

This signal is activated when the SCC is requesting an interrupt.

Note:

1–8

*Pull-up resistors are needed on INTACK and IEI inputs if they are not driven by the

system and for the INT output. If INTACK or IEI are left floating, the Am85C30 will

malfunction. INT is an open drain output and must be pulled up to keep a logical high

level.

General Information AMD

1.5.2 Serial Channel Pin Descriptions

CTSA, CTSB — Clear to Send (inputs, active Low)

If the Auto Enable bit in WR3 (D5) is set, a Low on these inputs enables the respective

transmitter; otherwise they may be used as general-purpose inputs. Both inputs are

Schmitt-trigger buffered to accommodate slow rise-time inputs. The SCC detects transitions on these inputs and, depending on whether or not other External/Status Interrupts

are pending, can interrupt the processor on either logic level transitions.

DCDA, DCDB — Data Carrier Detect (inputs, active Low)

These pins function as receiver enables if the Auto Enable bit in WR3 (D5) is set; otherwise they may be used as general-purpose input pins. Both pins are Schmitt-trigger buffered to accommodate slow rise-time signals. The SCC detects transitions on these inputs

and, depending on whether or not other External/Status Interrupts are pending, can interrupt the processor on either logic level transitions.

DTR/REQA, DTR/REQB — Data Terminal Ready/Request (outputs, active Low)

These pins function as DMA requests for the transmitter if bit D2 of WR14 is set; otherwise they may be used as general-purpose outputs following the state programmed into

the DTR bit.

PCLK — Clock (input)

This is the master clock used to synchronize internal signals. PCLK is not required to

have any phase relationship with the master system clock.

RTSA, RTSB — Request to Send (outputs, active Low)

When the Request to Send (RTS) bit in WR5 is set, the RTS pin goes Low. When the

RTS bit is reset in the Asynchronous mode and the Auto Enable bit in WR3 (D5) is set,

the signal goes High after the transmitter is empty. In Synchronous mode or Asynchronous mode with the Auto Enable bit reset, the RTS pins strictly follow the state of the RTS

bits. Both pins can be used as general-purpose outputs. Request to send outputs are not

affected by the state of the Auto Enable (D5) bit in WR3 in synchronous mode.

RTxCA, RTxCB — Receive/Transmit Clocks (inputs, active Low)

The functions of these pins are under program control. In each channel, RTxC may supply the receive clock, the transmit clock, the clock for the baud rate generator, or the clock

for the digital phase-locked loop. These pins can also be programmed for use with the

respective SYNC pins as a crystal oscillator. The receive clock may be 1, 16, 32, or 64

times the data rate in Asynchronous mode.

If a clock is supplied on these pins in NRZI or NRZ mode serial data on the RxD pin will

be sampled on the rising edge of these pins. In FM mode, RxD is sampled on both clock

edges.

RxDA, RxDB — Receive Data (inputs, active High)

Serial data is received through these pins.

SYNCA, SYNCB — Synchronization (inputs/outputs, active Low)

These pins can act as either inputs, outputs, or as part of the crystal oscillator circuit. In

the Asynchronous mode (crystal oscillator option not selected), these pins are inputs similar to CTS and DCD. In this mode, transitions on these lines affect the state of the SYNC/

HUNT status bit in Read Register 0, but have no other function.

In External Synchronization mode, with the crystal oscillator not selected, these lines also

act as inputs. In this mode, SYNC must be driven Low two receive clock cycles after the

last bit of the sync character is received. Character assembly begins on the rising edge of

the receive clock immediately following the activation of SYNC.

In the Internal Synchronization mode (Monosync and Bisync), with the crystal oscillator

not selected, these pins act as outputs and are active only during the part of the receive

clock cycle in which sync characters are recognized. The sync condition is not latched, so

1–9

General InformationAMD

these outputs are active each time a sync character is recognized (regardless of character boundaries). In SDLC mode, these pins act as outputs and are valid on receipt of a

flag.

TRxCA, TRxCB — Transmit/Receive Clocks (inputs or outputs, active Low)

The functions of these pins are under program control. TRxC may supply the receive

clock or the transmit clock in the Input mode or supply the output of the digital phaselocked loop, the crystal oscillator, the baud rate generator, or the transmit clock in the output mode. If a clock is supplied on these pins in NRZI or NRZ mode serial data on the

TxD pin will be clocked out on the negative edge of these pins. In FM mode, TxD is

clocked on both clock edges.

TxDA, TxDB — Transmit Data (outputs, active High)

Serial data from the SCC is sent out these pins.

W/REQA, W/REQB — Wait/Request (outputs, open drain and switches from floating

to Low when programmed for Wait function, driven from High to Low when programmed for a Request function)

These dual-purpose outputs can be programmed as either transmit or receive request

lines for a DMA controller, or as Wait lines to synchronize the CPU to the SCC data rate.

The reset state is Wait.

1–10

CHAPTER 2

System Interface

2.1 Introduction 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Registers 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 System Timings 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Read Cycle 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2 Write Cycle 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.3 Interrupt Acknowledge Cycle 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Register Access 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Am85C30 Enhancement Register Access 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Reset 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1

AMD

System Interface

2–2

CHAPTER 2

System Interface

2.1 INTRODUCTION

The SCC internal structure provides all the interrupt and control logic necessary to interface with non-multiplexed buses. Interface logic is also provided to monitor modem or

peripheral control inputs or outputs. All of the control signals are general-purpose and can

be applied to various peripheral devices as well as used for modem control.

The center for data activity revolves around the internal read and write registers. The programming of these registers provides the SCC with functional “personality;” i.e. register

values can be assigned before or during program sequencing to determine how the SCC

will establish a given communication protocol.

This chapter covers the details of interfacing the SCC to a system. The general timing

requirements are described but the respective data sheets must be referred to for specific

A.C. numbers.

2.2 REGISTERS

All modes of communication are established by the bit values of the write registers. As

data are received or transmitted, read register values may change. These changed values can promote software action or internal hardware action for further register changes.

The register set for each channel includes several write and read registers. Ten write registers are used for control, two for sync character generation, and two for the on-chip

baud rate generator. Two additional write registers are shared by both channels; one is

used as the interrupt vector and one as the master interrupt control. Both registers are

accessed and shared by either channel.

Six read registers indicate status functions; two are used by the baud rate generator, and

one by the receiver buffer. The remaining two read registers are shared by both channels;

one for interrupt pending bits and one for the interrupt vector. On the Am85C30 three additional registers are available. Refer to Chapter 4 and Chapter 6 for further details on

these registers.

Table 2–1 summarizes the assigned functions for each read and write register. Chapter 6

provides a detailed bit legend and description of each register.

2–3

System InterfaceAMD

Table 2–1. Register Set

Read Register Functions

RR0 Transmit/Receive buffer status, and External status

RR1 Special Receive Condition status, residue codes, error conditions

RR2 Modified (Channel B only) interrupt vector and Unmodified interrupt

vector (Channel A only)

RR3 Interrupt Pending bits (Channel A only)

*RR6 14-bit frame byte count (LSB)

*RR7 14-bit frame byte count (MSB), frame status

RR8 Receive buffer

RR10 Miscellaneous XMTR, RCVR status parameters

RR12 Lower byte of baud rate generator time constant

RR13 Upper byte of baud rate generator time constant

RR15 External/Status interrupt control information

* Available only when Am85C30 is programmed in enhanced mode.

Write Register Functions

WR0 Command Register, (Register Pointers), CRC initialization, resets

for various modes

WR1 Interrupt conditions, Wait/DMA request control

WR2 Interrupt vector (access through either channel)

WR3 Receive/Control parameters, number of bits per character, Rx CRC

enable

WR4 Transmit/Receive miscellaneous parameters and codes, clock rate,

number of sync characters, stop bits, parity

WR5 Transmit parameters and control, number of Tx bits per character,

Tx CRC enable

WR6 Sync character (1st byte) or SDLC address

WR7 SYNC character (2nd byte) or SDLC flag

**WR7′ SDLC options; auto flag, RTS, EOM reset, extended read, etc.

WR8 Transmit buffer

WR9 Master interrupt control and reset (accessed through either

channel), reset bits, control interrupt daisy chain

WR10 Miscellaneous transmitter/receiver control bits, NRZI, NRZ, FM

encoding, CRC reset

WR11 Clock mode control, source of Rx and Tx clocks

WR12 Lower byte of baud rate generator time constant

WR13 Upper byte of baud rate generator time constant

WR14 Miscellaneous control bits: baud rate generator, Phase-Locked

Loop control, auto echo, local loopback

WR15 External/Status interrupt control information-control external

conditions causing interrupts

** Only available in Am85C30.

2–4

System Interface AMD

2.3 SYSTEM TIMINGS

Two control signals, RD and WR, are used by the SCC to time bus transactions. In addition, four other control signals, CE, D/C, A/B and INTACK are used to control the type of

bus transaction that will occur.

A bus transaction starts when the D/C and A/B pins are asserted prior to the negative

edge of the RD or WR signal. The coincidence of CE and RD or CE and WR latches the

state of D/C and A/B and starts the internal operation. The INTACK signal must have

been previously sampled High by a rising edge of PCLK for a read or write cycle to occur.

In addition to sampling INTACK, PCLK is used by the interrupt section to set the Interrupt

Pending (IP) bits.

The SCC generates internal control signals in response to a register access. Since RD

and WR have no phase relationship with PCLK, the circuitry generating these internal

control signals provide time for metastable conditions to disappear. This results in a recovery time related to PCLK. This recovery time applies only between transactions involving the Am8530H/Am85C30, and any intervening transactions are ignored. This recovery

time is four PCLK cycles, measured from the falling edge of RD or WR for a read or write

cycle of any SCC register on the Am8530H-step and 3 or 3.5 PCLK cycles for the

Am85C30.

Note that RD and the WR inputs are ignored until CE is activated. The falling edge of RD

and WR can be substituted for the falling edge of CE or vice versa for calculating proper

pulse width for RD or WR low. In other words, if CE goes active after RD or WR have

gone active for a read or a write cycle, respectively, CE must stay active as long as the

minimum pulse width for RD and WR.

2.3.1 Read Cycle

The Read cycle timing for the SCC is shown in Figure 2–1. The A/B and D/C pins are

latched by the coincidence of RD and CE active. CE must remain Low and INTACK must

remain High throughout the cycle. The SCC bus drivers are enabled while CE and RD are

both Low. A read with D/C High does not disturb the state of the pointers and a read cycle

with D/C Low resets the pointers to zero after the internal operation is complete.

2.3.2 Write Cycle

The Write cycle timing for the SCC is shown in Figure 2–2. The A/B and D/C pins are

latched by the coincidence of WR and CE active. CE must remain Low and INTACK must

remain High throughout the cycle. A write cycle with D/C High does not disturb the state

of the pointers and a write cycle with D/C Low resets the pointers to zero after the internal

operation is complete.

2.3.3 Interrupt Acknowledge Cycle

The Interrupt Acknowledge cycle timing for the SCC is shown in Figure 2–3. The state of

INTACK is latched by the rising edge of PCLK. While INTACK is Low, the state of the

A/B, D/C, and WR pins is ignored by the SCC. Between the time INTACK is first sampled

Low and the time RD falls, the internal and external IEI/IEO daisy chains settle; this is

A.C. parameter #38 TdlAi (RD).

If there is an interrupt pending in the SCC, and IEI is High when RD falls, the Interrupt

Acknowledge cycle is intended for the SCC. This being the case, the SCC sets the appropriate Interrupt Under Service (IUS) latch, and places an interrupt vector on D0–D7. If the

falling edge of RD sets an IUS bit in the SCC, the INT pin goes inactive in response to the

falling edge. Note that there should be only one RD per Acknowledge cycle.

Another important fact is that the IP bits in the SCC are updated by a clock half the frequency of PCLK, and this clock is stopped while the pointers point to RR2 and RR3; thus

the interrupt requests will be delayed if the pointers are left pointing at these registers.

2–5

System InterfaceAMD

2.4 REGISTER ACCESS

The registers in the SCC are accessed in a two-step process, using a Register Pointer to

perform the addressing. To access a particular register, the pointer bits must be set by

writing to WR0. The pointer bits may be written in either channel because only one set

exists in the SCC. After the pointer bits are set, the next read or write cycle of the SCC

having D/C Low will access the desired register. At the conclusion of this read or write

cycle, the pointer bits are automatically reset to ‘0’, so that the next control write will be to

the pointers in WR0.

A read from RR8 (the Receive Buffer) or a write to WR8 (Transmit Buffer) may either be

done in this fashion or by accessing the SCC having the D/C pin High. A read or write

with D/C High accesses the receive or transmit buffers directly, and independently, of the

state of the pointer bits. This allows single-cycle access to the receive or transmit buffers

and does not disturb the pointer bits. The fact that the pointer bits are reset to ‘0’, unless

explicitly set otherwise, means that WR0 and RR0 may also be accessed in a single cycle. That is, it is not necessary to write the pointer bits with ‘0’ before accessing WR0 or

RR0. There are three pointer bits in WR0, and these allow access to the registers with

addresses 0 through 7. Note that a command may be written to WR0 at the same time

that the pointer bits are written. To access the registers with addresses 8 through 15, a

special command (point high in WR0) must accompany the pointer bits. This precludes

concurrently issuing a command (point high in WR0) when pointing to these registers.

The SCC register map is shown in Table 2–2. PNT

D0 in WR0, respectively.

If for some reason the state of the pointer bits is unknown, they may be reset to ‘0’ by performing a read cycle with the D/C pin held Low. Once the pointer bits have been set, the

desired channel is selected by the state of the A/B pin during the actual read or write of

the desired register.

, PNT1 and PNT0 are bits D2, D1 and

2

A/B, D/C

INTACK

RD

D0- D

CE

Address Valid

7

Data Valid

10216A-009A

Figure 2–1. SCC Read Cycle

2–6

System Interface AMD

D

0

PCLK

– D

A/B, D/C

INTACK

WR

D0- D

7

CE

Address Valid

7

Data Valid

10216A-010A

Figure 2–2. SCC Write Cycle

Vector

RD

INTACK

IEI

IEO

INT

Figure 2–3. Interrupt Acknowledge Cycle

2.5 Am85C30 Enhancement Register Access

SDLC/HDLC enhancements on the Am85C30 are enabled or disabled via bits D2 and D0

in WR15. Bit D2 determines whether or not the 10x19-bit SDLC/HDLC frame status FIFO

is enabled while bit D0 determines whether or not other SDLC/HDLC mode enhancements are enabled via WR7’. Table 2–3 shows what functions on the Am85C30 are enabled when these bits are set.

When bit D2 of WR15 is set to ‘1’, two additional registers (RR6 and RR7) per channel

specific to the 10x19-bit frame status FIFO are made available. The Am85C30 register

map when this function is enabled is shown in Table 2–4.

2–7

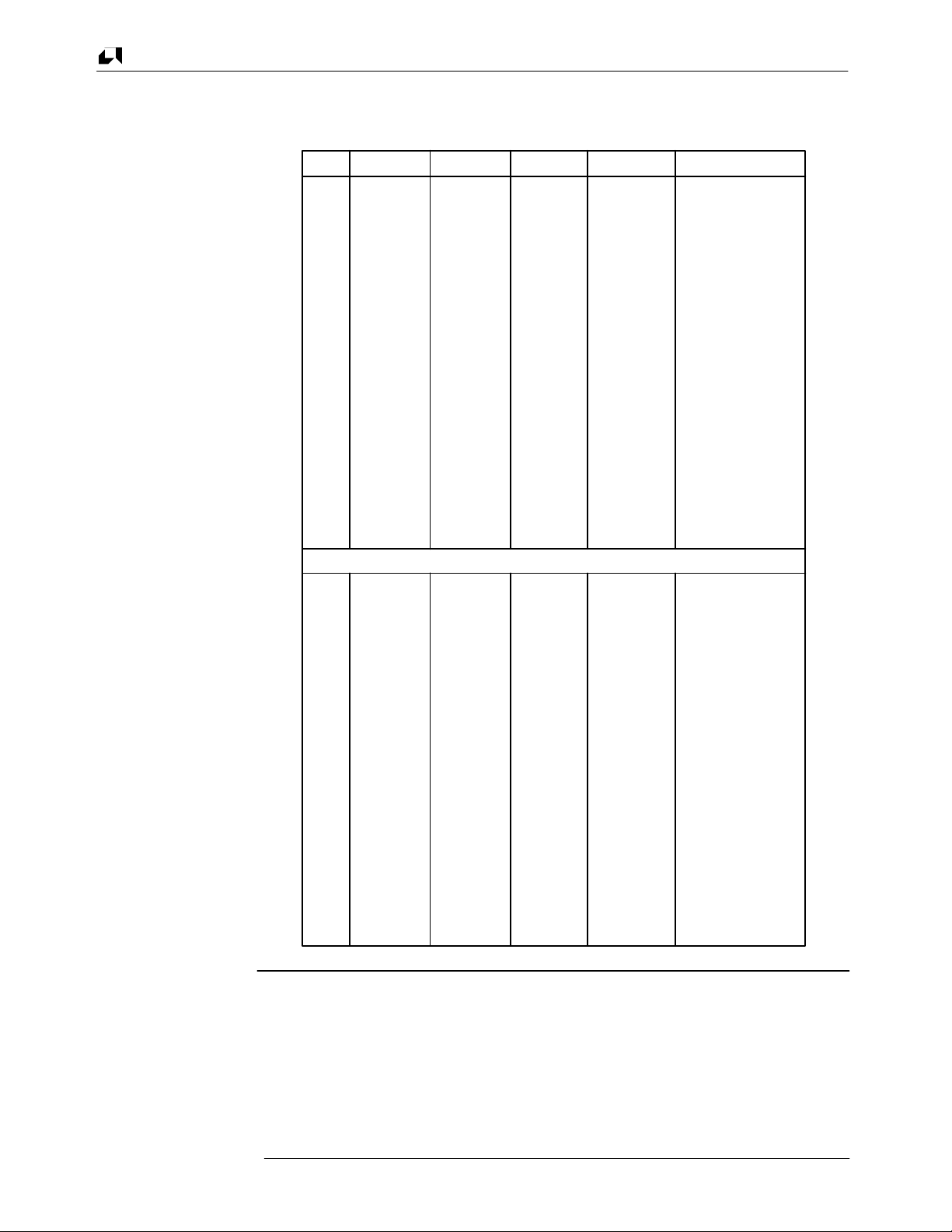

Table 2–2. SCC Register Map

System InterfaceAMD

A/B PNT

2

PNT

1

PNT

WRITE READ

0

0 0 0 0 WR0B RR0B

0 0 0 1 WR1B RR1B

0 0 1 0 WR2 RR2B

0 0 1 1 WR3B RR3B

0 1 0 0 WR4B (RR0B)

0 1 0 1 WR5B (RR1B)

0 1 1 0 WR6B (RR2B)

0 1 1 1 WR7B (RR3B)

1 0 0 0 WR0A RR0A

1 0 0 1 WR1A RR1A

1 0 1 0 WR2 RR2A

1 0 1 1 WR3A RR3A

1 1 0 0 WR4A (RR0A)

1 1 0 1 WR5A (RR1A)

1 1 1 0 WR6A (RR2A)

1 1 1 1 WR7A (RR3A)

Table 2–2. SCC Register Map (Continued)

A/B PNT

2

PNT

1

PNT

WRITE READ

0

With the Point High command: [D5–3 (WR0) = 001]

0 0 0 0 WR8B RR8B

0 0 0 1 WR9 (RR13B)

0 0 1 0 WR10B RR10B

0 0 1 1 WR11B (RR15B)

0 1 0 0 WR12B RR12B

0 1 0 1 WR13B RR13B

0 1 1 0 WR14B (RR10B)

0 1 1 1 WR15B RR15B

1 0 0 0 WR8A RR8A

1 0 0 1 WR9 (RR13A)

1 0 1 0 WR10A RR10A

1 0 1 1 WR11A (RR15A)

1 1 0 0 WR12A RR12A

1 1 0 1 WR13A RR13A

1 1 1 0 WR14A (RR10A)

1 1 1 1 WR15A RR15A

2–8

System Interface AMD

Table 2–3. Enhancement Options

WR15 bit D2 WR15 D0 WR7′ bit D6

10x19-bit SDLC/HDLC Extended

FIFO Enabled Enhance Enabled Read Enable Functions Enabled

1 0 x 10x19-bit FIFO enhancement

enabled only

0 1 0 SDLC/HDLC enhancements

enabled only

0 1 1 SDLC/HDLC enhancements

enabled with extended read

enabled

1 1 0 10x19-bit FIFO and SDLC/

HDLC enhancements enabled

1 1 1 10x19-bit FIFO and SDLC/

HDLC enhancements with

extended read enabled

Bit D0 of WR15 determines whether or not other enhancements pertinent only to SDLC/

HDLC Mode operation are available for programming via WR7′ as shown below. Write

Register 7 prime (WR7′ ) can be written to when bit D0 of WR15 is set to ‘1’. When this

bit is set, writing to WR7 (flag register) actually writes to WR7′. If bit D6 of this register is

set to ‘1’, previously unreadable registers WR3, WR4, WR5, WR10 are readable by the

processor. In addition, WR7′ is also readable by having this bit set. WR3 is read when a

bogus RR9 register is accessed during a read cycle, WR10 is read by accessing RR11,

and WR7′ is accessed by executing a read to RR14. The Am85C30 register map with bit

D0 of WR15 and bit D6 of WR7′ set is shown in Table 2–5.

2–9

Table 2–4. 10 x 19-Bit FIFO Enabled

System InterfaceAMD

A/B PNT

2

PNT

1

PNT

WRITE READ

0

0 0 0 0 WR0B RR0B

0 0 0 1 WR1B RR1B

0 0 1 0 WR2 RR2B

0 0 1 1 WR3B RR3B

0 1 0 0 WR4B (RR0B)

0 1 0 1 WR5B (RR1B)

0 1 1 0 WR6B RR6B

0 1 1 1 WR7B RR7B

1 0 0 0 WR0A RR0A

1 0 0 1 WR1A RR1A

1 0 1 0 WR2 RR2A

1 0 1 1 WR3A RR3A

1 1 0 0 WR4A (RR0A)

1 1 0 1 WR5A (RR1A)

1 1 1 0 WR6A RR6A

1 1 1 1 WR7A RR7A

With the Point High command:

0 0 0 0 WR8B RR8B

0 0 0 1 WR9 (RR13B)

0 0 1 0 WR10B RR10B

0 0 1 1 WR11B (RR15B)

0 1 0 0 WR12B RR12B

0 1 0 1 WR13B RR13B

0 1 1 0 WR14B (RR10B)

0 1 1 1 WR15B RR15B

1 0 0 0 WR8A RR8A

1 0 0 1 WR9 (RR13A)

1 0 1 0 WR10A RR10A

1 0 1 1 WR11A (RR15A)

1 1 0 0 WR12A RR12A

1 1 0 1 WR13A RR13A

1 1 1 0 WR14A (RR10A)

1 1 1 1 WR15A RR15A

2–10

System Interface AMD

Table 2–5. SDLC/HDLC Enhancements Enabled

A/B PNT

2

PNT

1

PNT

WRITE READ

0

0 0 0 0 WR0B RR0B

0 0 0 1 WR1B RR1B

0 0 1 0 WR2 RR2B

0 0 1 1 WR3B RR3B

0 1 0 0 WR4B RR4B(WR4B)

0 1 0 1 WR5B RR5B(WR5B)

0 1 1 0 WR6B (RR6B)

0 1 1 1 WR7B (RR7B)

1 0 0 0 WR0A RR0A

1 0 0 1 WR1A RR1A

1 0 1 0 WR2 RR2A

1 0 1 1 WR3A RR3A

1 1 0 0 WR4A RR4A(WR4A)

1 1 0 1 WR5B RR5A(WR5A)

1 1 1 0 WR6A (RR2A)

1 1 1 1 WR7A (RR3A)

With the Point High command:

0 0 0 0 WR8B RR8B

0 0 0 1 WR9 RR9(WR3B)

0 0 1 0 WR10B RR10B

0 0 1 1 WR11B RR11B(WR10B)

0 1 0 0 WR12B RR12B

0 1 0 1 WR13B RR13B

0 1 1 0 WR14B RR14B(WR7’B)

0 1 1 1 WR15B RR15B

1 0 0 0 WR8A RR8A

1 0 0 1 WR9 RR9A(WR3A)

1 0 1 0 WR10A RR10A

1 0 1 1 WR11A RR11A(WR10A)

1 1 0 0 WR12A RR12A

1 1 0 1 WR13A RR13A

1 1 1 0 WR14A RR14A(WR7’A)

1 1 1 1 WR15A RR15A

D0D1D2D3D4D5D6D7

0

Ext.

Read

Enable

Rx

comp.

CRC

DTR/REQ

Fast

Mode

Force

Txd

High

Auto

RTS

Turnoff

Auto

EOM

Reset

Auto

Tx

Flag

WR7′—SDLC/HDLC Enhancement

2–11

System InterfaceAMD

If both bits D0 and D2 of WR15 are set to ‘1’ then the Am85C30 register map is as shown

in Table 2–6.

Table 2–6. Register Set—All Enhancements Enabled

A/B PNT

2

PNT

1

PNT

WRITE READ

0

0 0 0 0 WR0B RR0B

0 0 0 1 WR1B RR1B

0 0 1 0 WR2 RR2B

0 0 1 1 WR3B RR3B

0 1 0 0 WR4B RR4B(WR4B)

0 1 0 1 WR5B RR5B(WR5B)

0 1 1 0 WR6B RR6B

0 1 1 1 WR7B RR7B

1 0 0 0 WR0A RR0A

1 0 0 1 WR1A RR1A

1 0 1 0 WR2 RR2A

1 0 1 1 WR3A RR3A

1 1 0 0 WR4A RR4A(WR4A)

1 1 0 1 WR5B RR5A(WR5A)

1 1 1 0 WR6A RR6A

1 1 1 1 WR7A RR7A

With the Point High command:

0 0 0 0 WR8B RR8B

0 0 0 1 WR9 RR9B(WR3B)

0 0 1 0 WR10B RR10B

0 0 1 1 WR11B RR11B(WR10B)

0 1 0 0 WR12B RR12B

0 1 0 1 WR13B RR13B

0 1 1 0 WR14B RR14B(WR7’B)

0 1 1 1 WR15B RR15B

1 0 0 0 WR8A RR8A

1 0 0 1 WR9 RR9A(WR3A)

1 0 1 0 WR10A RR10A

1 0 1 1 WR11A RR11A(WR10A)

1 1 0 0 WR12A RR12A

1 1 0 1 WR13A RR13A

1 1 1 0 WR14A RR14A(WR7’A)

1 1 1 1 WR15A RR15A

2.6 RESET

The SCC may be reset by either hardware or software. A hardware reset occurs when

RD and WR are both Low, simultaneously regardless of the state of the CE input, which

is normally an illegal condition. As long as both RD and WR are Low, the SCC recognizes

the reset condition. Once this condition is removed, however, the reset condition is asserted internally for an additional four to five PCLK cycles. During this time, any attempt

to access the SCC will be ignored. However a hardware reset does not clear the receive

FIFO, therefore it may be necessary to perform a few dummy reads immediately after a

2–12

System Interface AMD

hardware reset to ensure that the FIFO is completely flushed before the new data can be

received reliably.

The SCC has three software resets encoded into command bits in WR9. There are two

channel resets, which affect only one channel in the device and some of the bits in the

write registers. The third command forces the same result as a hardware reset. As in the

case of a hardware reset, the SCC stretches the reset signal an additional four to five

PCLK cycles beyond the ordinary valid access recovery time. When the SCC is first powered up, performing a read with the D/C pin held Low will guarantee that the pointers are

reset to ‘0’; then a reset command can be issued by selecting WR9 and writing to it. The

bits in WR9 may be written at the same time as the reset command because these bits

are affected only by a hardware reset. The reset values of the various registers are

shown in Figure 2–4.

Hardware Reset Channel Reset

76543210

00 00 00 00

00 . 0 0. 00 00. 0 0. 00

.. .. .. ..

.. .. .. .

.. .. . ..

0. . 000 0. 0. . 0 00 0.

.......

.

.. .. .. .. .. .. .. ..

11 00 00 . . .. 0

00 00 00 00 0. . 0 00 00

00 00 10 00

.. .. .. .. .. .. .. ..

0 0

1 1

76543210

00 00 00 00

.. .. .. ..

.. .. .. .

.. .. . ..

.. .. .. ..

.....

.. .. .. ..

WR0

WR1

WR2

WR3

WR4

WR5

WR6

WR7

WR9

WR10

WR11

WR12

.. .. .. .. .. .. .. ..

. . 1000 00 . . 1000 . .

11 11 10 00 11 11 10 00

01.. .100 01...100

00 00 01 10 00 00 01 10

00 00 00 00 00 00 00 00

00 00 00 00 00 00 00 00

Figure 2–4. SCC Register Reset Values

WR13

WR14

WR15

RR0

RR1

RR3

RR10

2–13

CHAPTER 3

I/O Programming Functional

Description

3.1 Introduction 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Polling 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Interrupt Sources 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Interrupt Control 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.1 Interrupt Enable Bit 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.2 Interrupt Pending Bit 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.3 Interrupt Under Service Bit 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4.4 Disable Lower Chain Bit 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Interrupt Operations 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Multiple Interrupt Priority Resolution 3–6. . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 Interrupt Without Acknowledge 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.3 Interrupt With Acknowledge With Vector 3–8. . . . . . . . . . . . . . . . . . . . . . .

3.5.4 Interrupt With Acknowledge Without Vector 3–10. . . . . . . . . . . . . . . . . . . .

3.5.5 Lower Priority Interrupt Masking 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6 Receive Interrupts 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1 Receive Interrupts Disabled 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2 Receive Interrupt on First Character or

Special Condition 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3 Receive Interrupt on All Receive Characters or

Special Conditions 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.4 Receive Interrupt on Special Conditions 3–11. . . . . . . . . . . . . . . . . . . . . . .

3.7 Transmit Interrupts 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 External/Status Interrupts 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1 Sync/Hunt 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2 Break/Abort 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.3 Zero Count 3–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.4 Tx Underrun/EOM 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.5 Clear To Send 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.6 Data Carrier Detect 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9 Block Transfers 3–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.1 Wait on Transmit 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.2 Wait on Receive 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3 DMA Requests 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3.1 DMA Request on Transmit

(using W/REQ) 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3.2 DMA Request on Transmit

(using DTR/REQ) 3–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3.3 DTR/REQ Deactivation Timing 3–19. . . . . . . . . . . . . . . . . . . . . . .

3.9.3.4 DMA Request on Receive (using W/REQ) 3–20. . . . . . . . . . . . . .

3–1

I/O Programming Functional Description

AMD

3–2

CHAPTER 3

I/O Programming Functional

Description

3.1 INTRODUCTION

The SCC can work under one of the following three modes of I/O operations: Polling,

Interrupts, and Block transfer. All three modes involve register manipulation during initialization and data transfer. Regardless of the communication mode selected, all three I/O

operating modes are available for use and must be programmed in the initialization

routine.

3.2 POLLING

Polling avoids interrupts and is the simplest mode to implement. In this mode, the software must poll the SCC to determine when data are to be written or read from the SCC.

This mode is enabled when the Master Interrupt Enable (MIE) bit in WR9 (D3) and the

Wait/DMA Request Enable bit in WR1 (D7) are both set to ‘0’.

In this mode the software must poll RR0 to determine the status of the Receive Buffer,

Transmit Buffer and External/Status before jumping to the appropriate interrupt routine.

3.3 INTERRUPT SOURCES

When the MIE bit in WR9 (D3) is set to ‘1’ interrupts will be enabled and, the SCC as a

microprocessor peripheral, will request an interrupt by asserting the INT pin Low from its

open-drain state only when it needs servicing.

Each channel in the SCC contains three sources of interrupts making a total of six.

These three sources of interrupts are: 1) Receiver, 2) Transmitter, and 3) External/Status

conditions as shown in Figure 3–1. In addition, there are several conditions that may

cause these interrupts. Each interrupt source is enabled under program control, with

Channel A having a higher priority than Channel B and with Receive, Transmit, and External/Status interrupts prioritized respectively within each channel as shown in

Table 3–1.

3–3

INT on 1st Rx Char. or

Special Condition

INT on All Rx Char. or

Special Condition

Rx Int on Special

Condition only

Parity

I/O Programming Functional DescriptionAMD

Receiver

Interrupt

Sources

Transmit Buffer Empty

Zero Count

DCD

SYNC/HUNT

CTS

Tx Underrun/EOM

Break/Abort

Transmitter

Interrupt

Source

External/Status

Interrupt

Sources

Figure 3–1. SCC Interrupts

Table 3–1. Interrupt Source Priority

Receiver Channel A High

Transmit Channel A

External/Status Channel A ↓

Receiver Channel B ↓

Transmit Channel B

External/Status Channel B Low

SCC

Interrupt

3.4 INTERRUPT CONTROL

In addition to the MIE bit that enables or disables all SCC interrupts, three control/status

bits are associated with each interrupt source internal to the SCC. These are the Interrupt

Enable (IE), the Interrupt Pending (IP), and the Interrupt Under Service (IUS) bits. Similarly, lower-priority devices on the external daisy chain can be prevented from requesting

interrupts via the Disable Lower Chain bit in WR9 (D2).

3.4.1 Interrupt Enable Bit

The Interrupt Enable (IE) bits are written by the processor and serve to control interrupt

requests from each interrupt source on the SCC. If the IE bit is set to ‘1’ for an interrupt

source, then that source may cause an interrupt request providing all of the necessary

conditions are met. If the IE bit is reset, no interrupt request will be generated by that

source. The IE bits are write-only and are programmed in WR1 as follows.

3–4

I/O Programming Functional Description AMD

D7

W/DMA

REQ

Enable

D6

W/DMA

REQ

Funct.

D5

W/DMA

REQ on

Rx/Tx

D4 D3 D2

Parity

INT

Enable

— Rx INT Disable

0

0

1

1

0

— Rx INT on 1st Char. or

1

Special Condition

— INT on All Rx Char. or

0

Special Condition

— Rx INT on Special Only

1

D1

Tx

INT

Enable

D0

Ext/Sta

INT

Enable

WR1—Interrupt Source IE

3.4.2 Interrupt Pending Bit

The Interrupt Pending (IP) bit for a given source of interrupt may be set by the presence

of an interrupt condition in the SCC and is reset directly by the processor, or indirectly by

some action that the processor may take. If the corresponding IE bit is not set, the IP for

that source of interrupt will never be set. The IP bits in the SCC are read-only via RR3 as

shown above.

D7

0

D6

0

D5

Ch. A

Rx

IP

D4

Ch. A

Tx

IP

D3

Ch. A

Ext/Sta

IP

D2

Ch. B

Rx

IP

D1

Ch. B

Tx

IP

D0

Ch. B

Ext/Sta

IP

RR3—Interrupt Pending

3.4.3 Interrupt Under Service Bit

The Interrupt Under Service (IUS) bits are not observable by the processor. An IUS bit is

set during an Interrupt Acknowledge cycle for the highest-priority IP. The IUS bit is used

to control the operation of internal and external daisy chain interrupts. The internal daisy

chain links the six sources of interrupt in a fixed order, chaining the IUS bits for each

source. While an internal IUS bit is set, all lower-priority interrupt requests are masked

off; during an Interrupt Acknowledge cycle the IP bits are also gated into the daisy chain.

This insures that the highest-priority IP selected will have its IUS bit set. At the end of an

interrupt service routine, the processor must issue a Reset Highest IUS Command in

WR0 to re-enable lower-priority interrupts. This is the only way, short of a software or

hardware reset, that an IUS bit may be reset.

3.4.4 Disable Lower Chain Bit

The Disable Lower Chain (DLC) bit in WR9 (D2) is used to disable all SCCs in a lower

position on the external daisy chain. If this bit is set to ‘1’, the IEO pin is driven Low and

prevents lower-priority devices from generating an interrupt request. Note that the IUS bit,

when set, will have the same effect but is not controllable through software, and the point

where lower-priority interrupts are masked off may not correspond to the chip boundary.

3–5

I/O Programming Functional DescriptionAMD

3.5 INTERRUPT OPERATIONS

Interrupts from the SCC may be acknowledged with a vector, acknowledged without a

vector, or not acknowledged at all. WR2 is used to hold the interrupt vector returned during an interrupt acknowledge cycle. This vector register can be shared among multiple

interrupt sources; some bits of the vector can be encoded with information that identifies

the interrupt source.

Three bits in WR9 determine whether or not a vector is placed on the bus and whether or

not status is included. The Vector Includes Status (VIS) bit (D0) enables status information to be included in the vector, the Status High/Status Low bit (D4) determines which

bits of the vector are encoded as shown in Figure 3–2, and the No Vector (NV) bit (D1)

enables or disables placing the vector on the bus in response to an interrupt acknowledge

cycle.

V3 V2 V1 Status High/Status Low = 0

V4 V5 V6 Status High/Status Low = 1

0 0 0 Ch B Transmit Buffer Empty

0 0 1 Ch B External/Status Change

0 1 0 Ch B Receive Character Available

0 1 1 Ch B Special Receive Condition

1 0 0 Ch A Transmit Buffer Empty

1 0 1 Ch A External/Status Change

1 1 0 Ch A Receive Character Available

1 1 1 Ch A Special Receive Condition

Figure 3–2. Interrupt Vector Modification