■

■

■

■

■

■

■

■

■

■

■

■

■

PRELIMINARY

Am79C989

Quad Ethernet Switching Transceiver (QuEST™)

DISTINCTIVE CHARACTERISTICS

Four independent 10BASE-T transceivers

compliant with the IEEE 802.3 standard

Four digital Manchester Encode/Decode

(MENDEC) units

On-chip filtering enables FCC EMI compliance

without external filters or common mode

chokes

Automatic polarity Correction and Detection on

10BASE-T receivers

Optional Attachment Unit Interface (AUI) for

non-10BASE-T transceivers

10BASE-T Extended Distance option

accommodate lines longer than 100 meters

Quad AMD Switching Interface (QuASI™)

interface reduces overall pin count

Half-Duplex and Full-Duplex operation

Auto-Negotiation compliant with IEEE 802.3u

Standard

Standard MII management interface and

protocol

Status Change Interrupt output pin for fast

response time to changed conditions

44-pin PLCC CMOS device

5 V supply with 3.3 V system interface

compatibility

GENERAL DESCRIPTION

The Am79C989 Quad Ethernet Switching Transceiver

(QuEST™) is a four-port physical layer (PHY) device

that provides all of the analog functions needed for a

10BASE-T switch, including four independent

Manchester Encode/Decode units (MENDECs) and

four independent 10BASE-T transceivers. If the AUI

port is used for a 10BASE-2, 10BASE-5, or

10BASE-FL transceiver, one of the four 10BASE-T

ports is disabled.

The QuEST device is designed for 10 Mbps Ethernet

switching hubs, port switching repeater hubs, routers,

bridges, and servers that require data encoding and

clock recovery on a per port basis and are limited by pin

constraints. Clock recovery is performed as par t of the

MENDEC function. The QuEST device supports every

physical layer function of a full-featured switch, including full-duplex operation with Auto-Negotiation and the

ability to use various media types.

A unique feature of the QuEST device is the Quad AMD

Switching Interface (QuASI) which multiplex es the data

for all four channels into one set of pins . This minimizes

the pin count and size of the QuEST device and substantially reduces overall system cost.

The QuEST device provides a 2-pin Media Independent Interface (MII) Management Interface which supports the protocols specified in the IEEE 802.3u

standard. Controlled by the switch system, this interface allows the QuEST de vice to be polled for status information and allows operating parameters of the

QuEST device, such as extended distance operation,

to be altered.

The Am79C989 device provides an Interrupt pin to indicate changes in the internal status of the device. The

interrupt function reduces CPU polling of status registers and allows fast response time to changes in physical layer conditions.

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed

product without notice.

Publication# 21173 Rev: B Amendment/+2

Issue Date: April 1997

PRELIMINARY

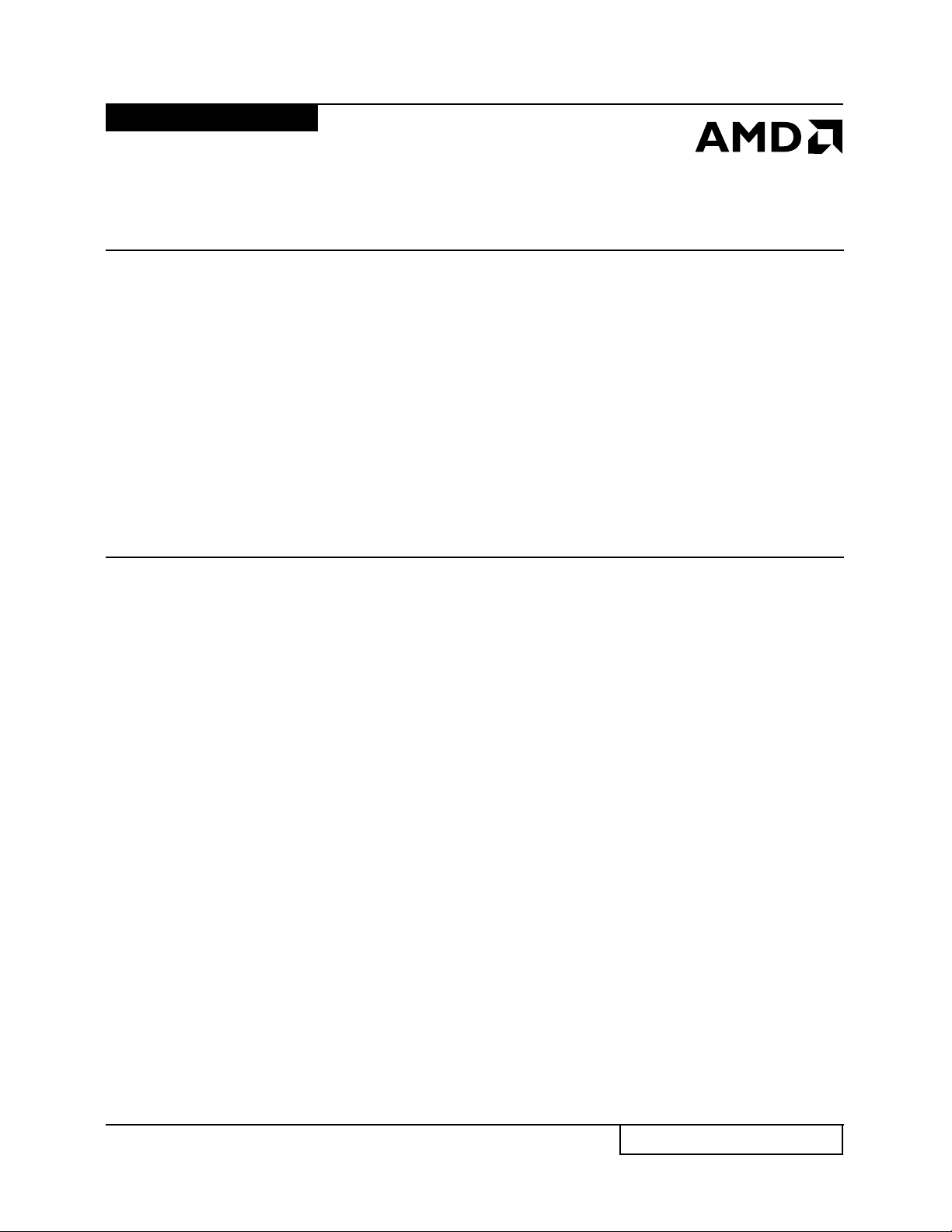

BLOCK DIAGRAM

System Interface Network Interface

QTX_EN

QTX_DATA

QRX_DATA

QRX_VALID

QRX_CRS

QCLSN

SCLK

QRST/STRB

QuASI Interface

Jabber

Timer

Collision

Detect

Elasticity FIFO

Manchester

Encoder

Manchester

Decode and

Carrier Detect

Link Detect

10BASE-T Transceiver 0

Polarity Detection/

Correction

Link/Auto Neg

State Machine

10BASE-T Transceiver 1

10BASE-T Transceiver 2

10BASE-T Transceiver 3

Collision

Attachment Unit Interface

Detect

Line Driver with

Wave Shaping

Line Receiver with

Smart Squelch

AUI Collision

Squelch

AUI Transmitter

AUI Receiver

with Squelch

TXD0+

TXD0-

RXD0+

RXD0-

REXT

TXD1+

TXD1-

RXD1+

RXD1-

TXD2+

TXD2-

RXD2+

RXD2-

TXD3+

TXD3-

RXD3+

RXD3-

PCI/CI+

QINT/CI-

DO+

DO-

DI+

DI-

Register Block

MDC

MDIO

v3

Management Interface

2 Am79C989

21173B-1

PRELIMINARY

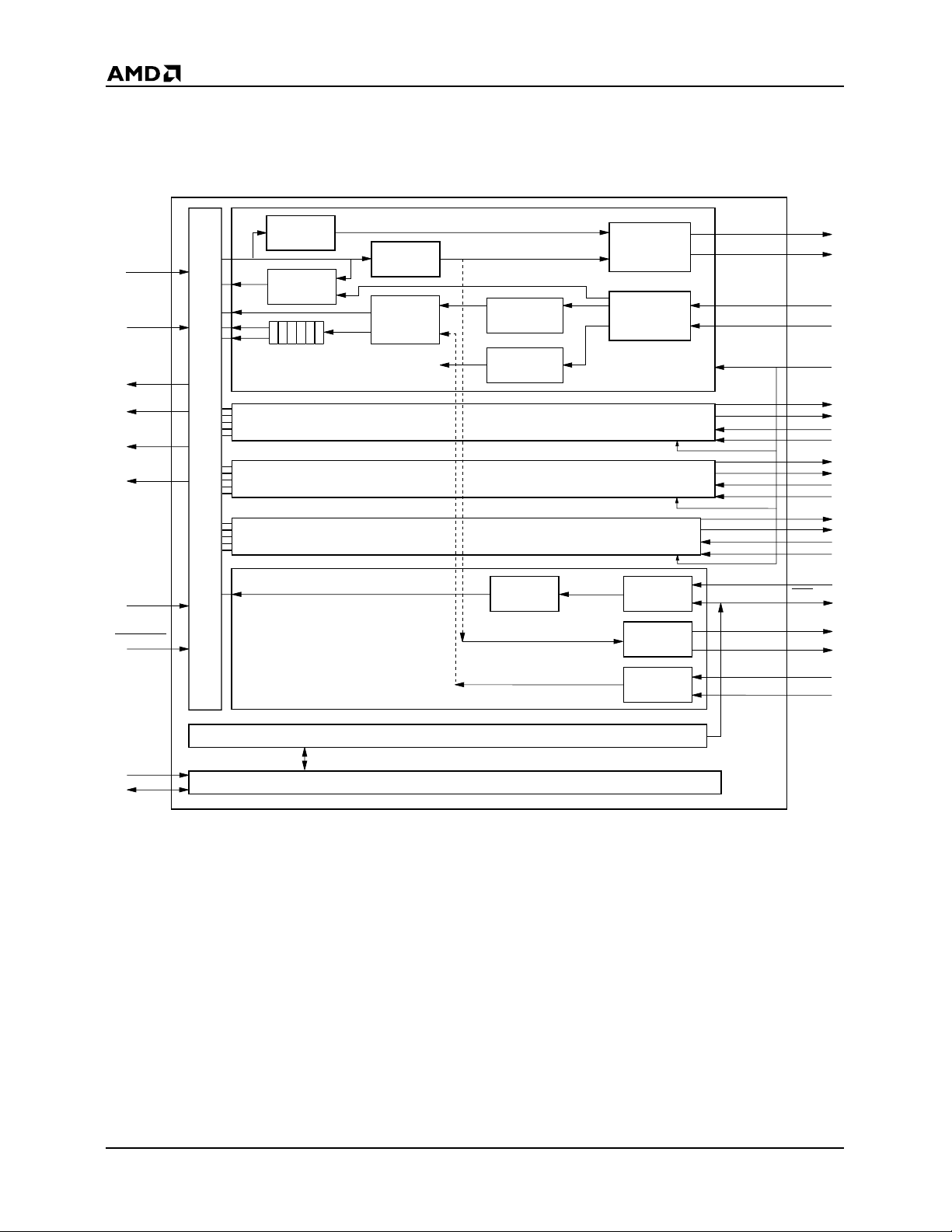

CONNECTION DIAGRAM

SCLK

QTX_EN

QTX_DATA

QRX_VALID

QRX_DATA

VDDIO

VSSIO

QRX_CRS

QCLSN

MDIO

MDC

QRST/STRB

REXT

VSS

QINT/CI-

PCI/CI+

DI-

DI+

VSSAUI

DO-

DO+

VDDTX

3

2

QuEST

Am79C989

44 PLCC

Version 2.0

23

22

TXD+

TXD1-

1

44

24

VDDTX

43

25

TXD2-

TXD2+

5

641

4

7

8

9

10

11

12

13

14

15

16

17

19

20

TXD0+

VSSTX

21

18 27

TXD0-

42

26

VSSTX

40

39

38

37

36

35

34

33

32

31

30

29

28

TXD3-

TXD3+

VDD

RXD3+

RXD3-

RXD2+

RXD2-

VSSRX

RXD1+

RXD1-

RXD0+

RXD0-

VDDTX

21173B-2

Am79C989 3

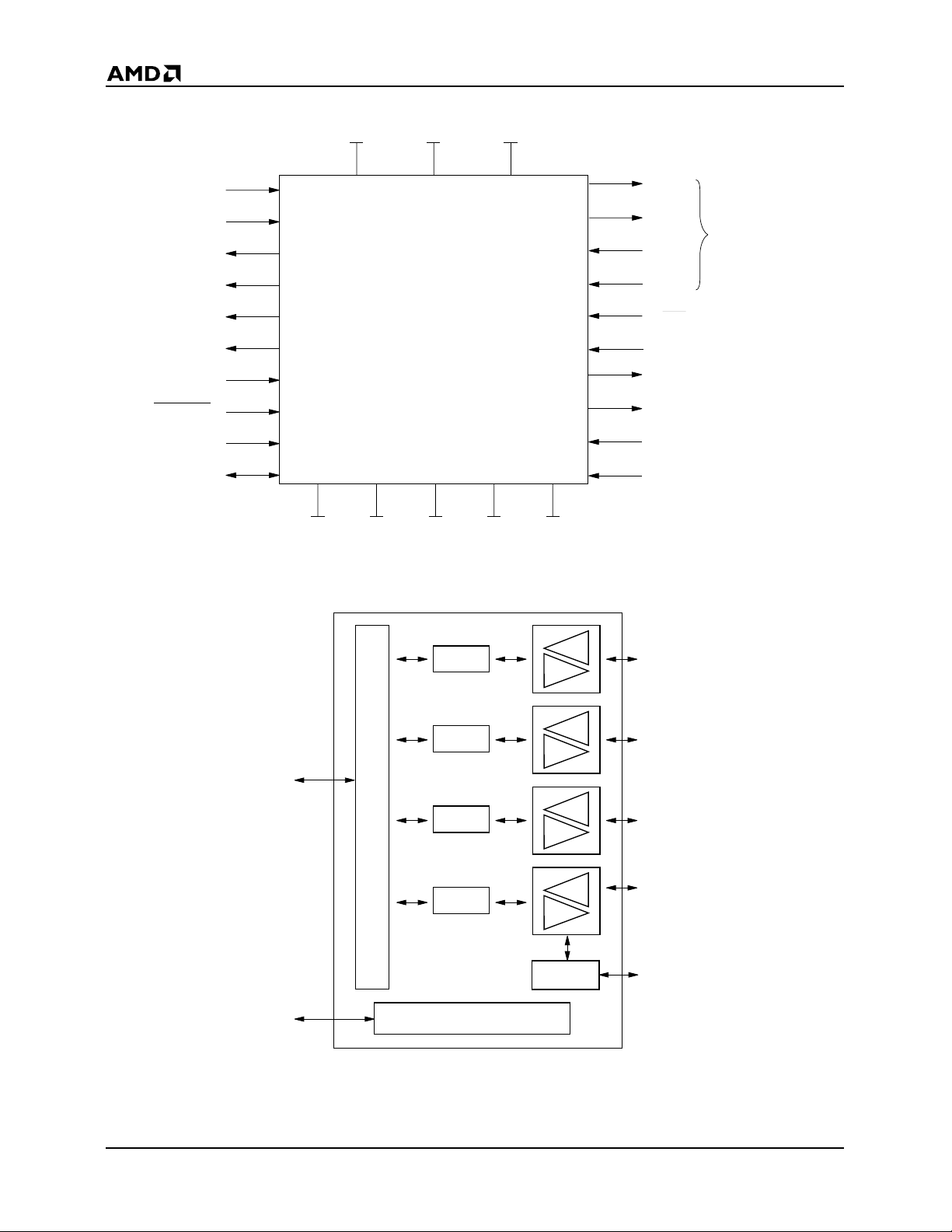

LOGIC DIAGRAM

PRELIMINARY

QTX_EN

QTX_DATA

QRX_DATA

QRX_VALID

QRX_CRS

QCLSN

SCLK

QRST/STRB

MDC

MDIO

LOGIC SYMBOL

V

DDIO

V

SS

V

SSAUI

V

DDTX(3)

V

SSTX(2)

V

SSRX

V

DD

V

SSIO

TXD+

TXD-

RXD+

RXD-

QINT/CI-

PCI/CI+

DO+

DO-

DI+

DI-

Twisted Pair Ports

(4 Ports)

21173B-3

QuASI

QuASI Interface

Management Interface

MENDEC

MENDEC

MENDEC

MENDEC

TP

TP

TP

TP

AUI

21173B-4

4 Am79C989

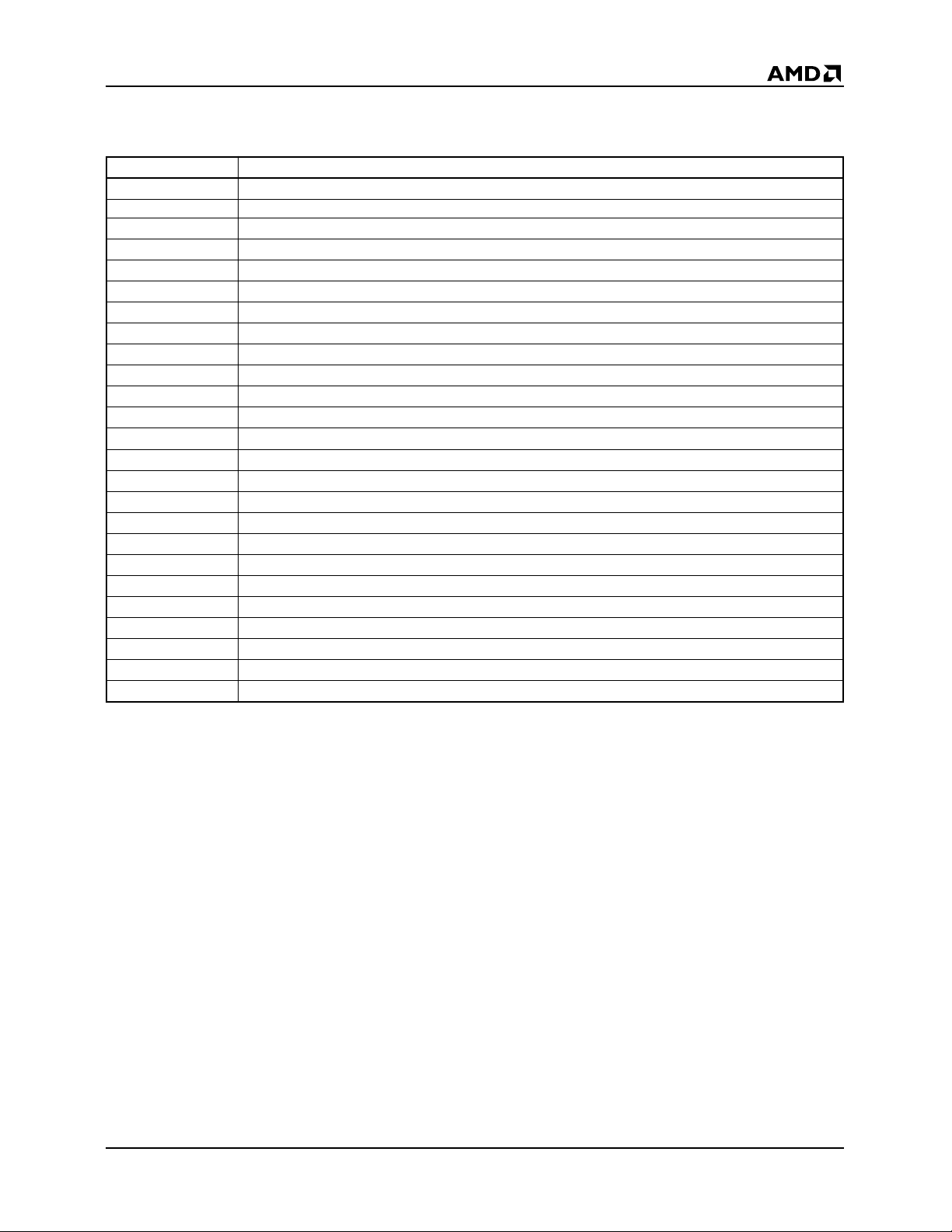

RELATED PRODUCTS

PRELIMINARY

Part No.

Am7990

Am7992B Serial Interface Adapter (SIA)

Am7996 IEEE 802.3/Ethernet/Cheapernet Transceiver

Am79C90 CMOS Local Area Network Controller for Ethernet (C-LANCE)

Am79C98 Twisted Pair Ethernet Transceiver (TPEX)

Am79C100 Twisted Pair Ethernet Transceiver Plus (TPEX+)

Am79C870 Quad Fast Ethernet Transceiver (QFEX™) for 100BASE-X

Am79C871 Quad Fast Ethernet Transceiver for 100BASE-X Repeater (QFEXr™)

Am79C981 Integrated Multiport Repeater Plus (IMR+™)

Am79C982 basic Integrated Multiport Repeater (bIMR™)

Am79C983 Integrated Multiport Repeater 2 (IMR2™)

Am79C984A enhanced Integrated Multiport Repeater (eIMR™)

Am79C985 enhanced Integrated Multiport Repeater Plus (eIMR+™)

Am79C987 Hardware Implemented Management Information Base (HIMIB™)

Am79C988 Quad Integrated Ethernet Transceiver (QuIET™)

Am79C900 Integrated Local Area Communications Controller (ILACC™)

Am79C940 Media Access Controller for Ethernet (MACE™)

Am79C960 PCnet™-ISA Single-Chip Ethernet Controller (for ISA bus)

Am79C961 PCnet™-ISA+ Single-Chip Ethernet Controller for ISA (with Microsoft® Plug n’ Play® Support)

Am79C961A PCnet™-ISA II Full Duplex Single-Chip Ethernet Controller for ISA

Am79C965 PCnet™-32 Single-Chip 32-Bit Ethernet Controller

Am79C970 PCnet™-PCI Single-Chip Ethernet Controller (for PCI bus)

Am79C970A PCnet™-PCI II Full Duplex Single-Chip Ethernet Controller (for PCI bus)

Am79C971B PCnet™Am79C974 PCnet™-SCSI Combination Ethernet and SCSI Controller for PCI Systems

Local Area Network Controller for Ethernet (LANCE)

FAST

Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus

Description

Am79C989 5

PRELIMINARY

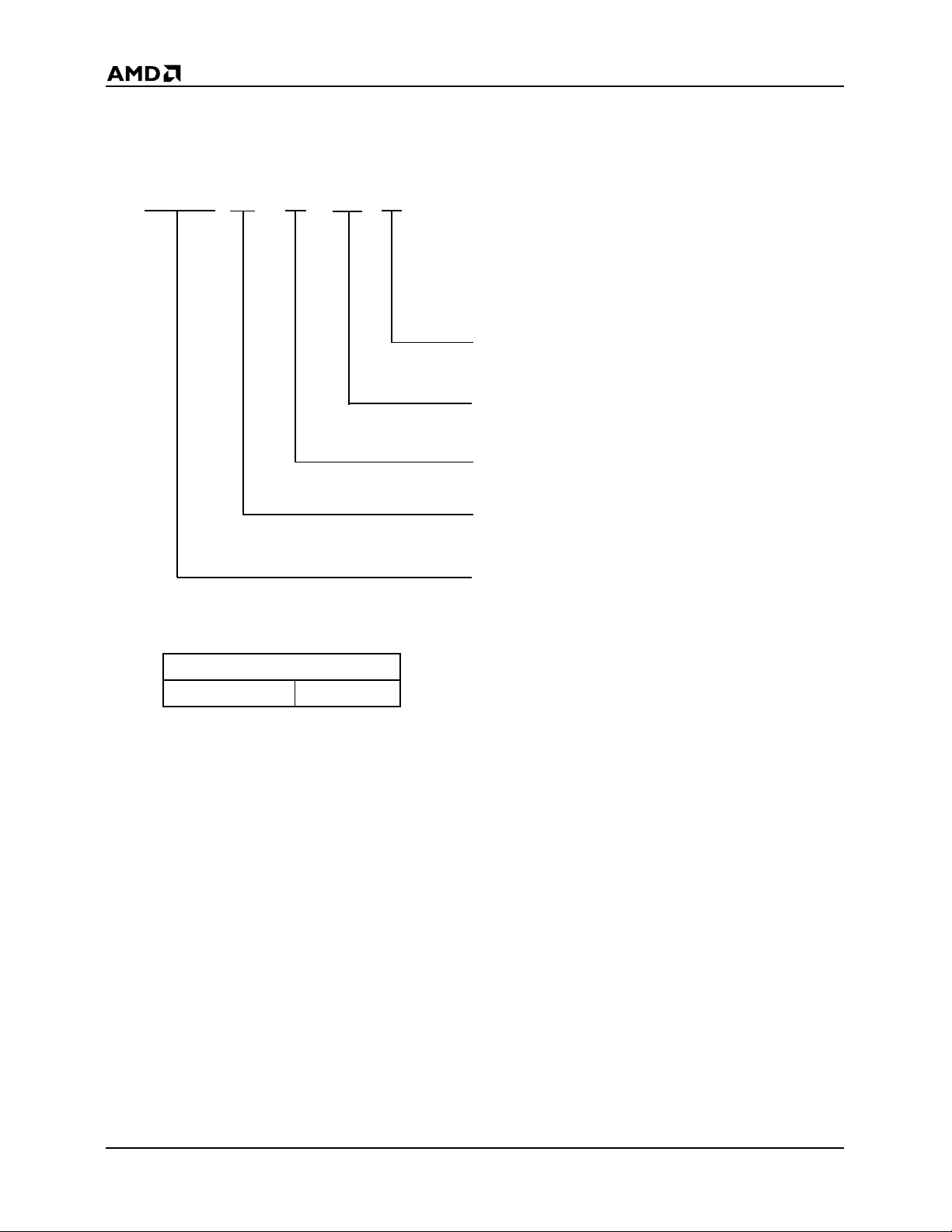

ORDERING INFORMATION

Standard Products

AMD standard products are available in se ver al packages and operating r anges. The order number (V alid Combination) is formed

by a combination of the elements below.

Am79C989

J

C

ALTERNATE PACKAGING OPTION

\T = Tape and reel

TEMPERATURE RANGE

C = Commercial (0˚C to +70˚C)

P ACKA GE TYPE

J = 44 PLCC

Valid Combinations

Am79C989 JC or JC\T

SPEED OPTION

Not Applicable

DEVICE NUMBER/DESCRIPTION

Am79C989

Quad Ethernet Switching Transceiver (QuEST)

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales

office to confirm availability of specific valid combinations and

to check on newly released combinations.

6 Am79C989

PRELIMINARY

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

CONNECTION DIAGRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

LOGIC DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

LOGIC SYMBOL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

RELATED PRODUCTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Standard Products. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

PIN DESIGNATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Listed by Pin Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Listed by Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

10BASE-T Signal Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

AUI Signal Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

QuASI Interface Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Management Interface Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Miscellaneous Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Power Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

10BASE-T Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

10BASE-T Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Jabber Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

10BASE-T Receiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Differential Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Receive Polarity Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Extended Distance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Collision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Link Integrity with Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

10BASE-T Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Auto-Negotiation Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Manchester Encoder. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Manchester Decoder. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Elasticity FIFO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Attachment Unit Interface (AUI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

AUI Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

AUI Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Collision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

QuASI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

The Management Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

PHY Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Interrupt Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.3 Volt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

REGISTER DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Shared Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Port Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Non-Implemented Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Auto-Negotiation Control Register (Reg 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Auto-Negotiation Status Register (Reg 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Auto-Negotiation Advertisement Register (Reg 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Auto-Negotiation Link Partner Ability Register (Reg 5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Am79C989 7

PRELIMINARY

Auto-Negotiation Next Page Register (Reg 7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Error Mask Register (Reg 20) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

SYSTEM APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

10 Mbps Ethernet Switch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

OPERATING RANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Commercial (C) Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

DC CHARACTERISTICS OVER OPERATING RANGES UNLESS OTHERWISE SPECIFIED. . . . 29

KEY TO SWITCHING WAVEFORMS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

PHYSICAL DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

8 Am79C989

PRELIMINARY

PIN DESIGNATIONS

Listed by Pin Number

Pin No. Pin Name Pin No. Pin Name Pin No. Pin Name Pin No. Pin Name

1 VDDIO 12 DI- 23 VDDTX 34 VSSRX

2 QRX_DATA 13 DI+ 24 TXD2- 35 RXD23 QRX_VALID 14 VSSAUI 25 TXD2+ 36 RXD2+

4 QTX_DATA 15 DO- 26 VSSTX 37 RXD35 QTX_EN 16 DO+ 27 TXD3- 38 RXD3+

6 SCLK 17 VDDTX 28 TXD3+ 39 VDD

7 QRST/STRB

8 REXT 19 TXD0+ 30 RXD0- 41 MDIO

9 VSS 20 VSSTX 31 RXD0+ 42 QCLSN

10 QINT/CI- 21 TXD1- 32 RXD1- 43 QRX_CRS

11 PCI/CI+ 22 TXD1+ 33 RXD1+ 44 VSSIO

18 TXD0- 29 VDDTX 40 MDC

Listed by Group

Pin Number Pin Name Pin Type Pin Description

10BASE-T Signal Pins

19 & 18 TXD0 ±

22 & 21 TXD1 ±

25 & 24 TXD2 ±

28 & 27 TXD3 ±

31 & 30 RXD0 ±

33 & 32 RXD1 ±

36 & 35 RXD2 ±

38 & 37 RXD3 ±

AUI Signal Pins

10 QINT

11 PCI/CI+ Input

13 & 12 DI ±

16 & 15 DO ±

QuASI Interface

2 QRX_DATA I/O

3 QRX_VALID I/O

4 QTX_DATA Input Multiplexed serial transmit data

5 QTX_EN Input Multiplexed transmit enable

/CI- I/O

Output Port 0 10BASE-T differential driver

Output Port 1 10BASE-T differential driver

Output Port 2 10BASE-T differential driver

Output Port 3 10BASE-T differential driver

Input Port 0 10BASE-T differential receiver

Input Port 1 10BASE-T differential receiver

Input Port 2 10BASE-T differential receiver

Input Port 3 10BASE-T differential receiver

AUI differential collision receiv er negative signal or Interrupt output

signal (open drain)

AUI differential collision receiver positive signal or single-ended

Pseudo AUI receiver

Input Attachment Unit Interface differential data receiver

Output Attachment Unit Interface differential output driver

Multiplexed serial receive data

PHYAD 4 internal address input upon reset

Multiplexed receive data valid enable

PHYAD 3 internal address input upon reset

Am79C989 9

PRELIMINARY

Pin Number Pin Name Pin Type Pin Description

QuASI Interface (Continued)

42 QCLSN I/O

43 QRX_CRS Output Multiplexed receive carrier sense

Management Interface

40 MDC Input Management Interface Clock

41 MDIO I/O Management Interface Data

Miscellaneous Pins

6 SCLK Input System Clock for QuASI Interface

7 QRST/STRB

8 REXT Input External resistor for determining TXD drive levels

Power Pins

1 VDDIO VDD1

44 VSSIO VSS 1 VSS pin for digital Inputs/Outputs

39 VDD VDD 1 VDD pin for internal digital logic

9 VSS VSS 1 VSS pin for internal digital logic

14 VSSAUI VSS 1 Analog VSS pin for AUI circuit

29, 23, 17 VDDTX VDD 3 Analog VDD pins for TXD driver

26, 20 VSSTX VSS 2 Analog VSS pins for TXD driver

34 VSSRX VSS 1 Analog VSS pin for 10BASE-T Receivers

Input Active Low -- Reset and QuASI Channel 0 strobe

Multiplexed collision error

PHYAD 2 internal address input upon reset

1 VDD pin for digital Outputs

(3.3 Volt Capable)

PIN DESCRIPTIONS

10BASE-T Signal Pins

TXD0 ±

10BASE-T Transmit Data Port 0

RXD ±

10BASE-T Receive Data Port 1

Input

RXD1 ± are the 10BASE-T differential data receivers f or

port 1.

Output

TXD0 ± are the 10BASE-T differential data drivers for

port 0.

RXD0 ±

10BASE-T Receive Data Port 0

TXD2 ±

10BASE-T Transmit Data Port 2

Output

TXD2 ± are the 10BASE-T differential data drivers for

port 2.

Input

RXD0 ± are the 10BASE-T differential data receivers f or

port 0.

TXD1 ±

10BASE-T Transmit Data Port 1

RXD2 ±

10BASE-T Receive Data Port 2

Input

RXD2 ± are the 10BASE-T differential data receivers f or

port 2.

Output

TXD1 ± are the 10BASE-T differential data drivers for

port 1.

TXD3 ±

10BASE-T Transmit Data Port 3

Output

TXD3 ± are the 10BASE-T differential data drivers for

port 3.

10 Am79C989

PRELIMINARY

DO ±

DI ±

RXD3 ±

10BASE-T Receive Data Port 3

Input

RXD3 ± are the 10BASE-T differential data receivers f or

port 3.

AUI Signal Pins

AUI Data Out

Output

When Port 0 is configured for A UI, DO ± are the AUI differential data out drivers. Data is transmitted with

Manchester encoded signaling compliant with IEEE

802.3 standards.

AUI Data In

Input

When Port 0 is configured for AUI (Control Register

Reg 18 bit 2), DI ± are the AUI diff erential data in receivers. Data is indicated by Manchester encoded signaling compliant with IEEE 802.3 standards.

PCI/CI+

Pseudo-AUI Collision, AUI Collision Int (-)

Input/Input

When Interrupt Enable is true (Control Register Reg 18

bit 5) and port 0 is configured for AUI (Control Register

Reg 18 bit 2), this pin is configured as PCI. PCI is a single-ended pseudo-AUI collision in signal. Collision is indicated by a 10 MHz pattern.

When Interrupt Enable is false (Control Register Reg

18 bit 5) and port 0 is configured for AUI (Control Register Reg 18 bit 2), this pin is configured as CI+. CI ± are

the AUI differential collision in signals. Collision is indicated by a 10 MHz pattern compliant with IEEE 802.3

standards.

/CI-

QINT

QuEST Interrupt, AUI Collision Int (-)

Output/Input

When Interrupt Enable is true (Control Register Reg.

18 bit 5), this pin is configured as QINT. QINT is an active-low signal which indicates that one of the follo wing

conditions has occurred: Link Status Change, Duplex

Mode Change, Auto-Negotiation Change, MAU Error.

Interrupt status flags and enables for individual conditions are reported in the Interrupt Status and Enable

Register (Reg 16).

When Interrupt Enable is false (Control Register Reg

18 bit 5) and port 0 is configured for AUI (Control Register Reg 18 bit 2), this pin is configured as CI-. CI ± are

the AUI differential collision in signals. Collision is indicated by a 10-MHz pattern compliant with IEEE 802.3

standards.

QuASI Interface

QTX_EN

Multiplexed T ransmit Enable

Input

QTX_EN indicates to QuEST that valid transmit data is

on QTX_DATA. QTX_EN for all 4 ports is time-division

multiplexed onto this signal and is sampled with respect to SCLK. The channel’s slot is synchronized to

the rising edge of QRST/STRB

QTX_DATA

Multiplexed T ransmit Data

Input

QTX_DATA indicates serial NRZ transmit data.

QTX_DATA for all 4 ports is time-division multiplexed

onto this signal and is sampled with respect to SCLK.

The channel’s slot is synchronized to the rising edge of

QRST/STRB

QRX_CRS

Multiplexed Receive Carrier Sense

Output

QRX_CRS indicates receive or transmit activity on the

network. QRX_CRS for all 4 ports is time-division multiplexed onto this signal and is sampled with respect to

SCLK. The channel’s slot is synchronized to the rising

edge of QRST/STRB.

QRX_VALID

Multiplexed Receive Data Valid

Output

QRX_VALID indicates that valid receive data is on

QRX_DATA. QRX_VALID for all 4 ports is time-division

multiplexed onto this signal and is sampled with respect to SCLK. The channel’s slot is synchronized to

the rising edge of QRST/STRB. At the rising edge of reset, QRX_VALID is sampled to determine PHYAD 3.

QRX_DATA

Multiplexed Receive Data

Output

QRX_DATA indicates serial NRZ receive data.

QRX_DATA for all 4 ports is time-division multiplexed

onto this signal and is sampled with respect to SCLK.

The channel’s slot is synchronized to the rising edge of

QRST/STRB. At the rising edge of reset, QRX_DATA is

sampled to determine PHYAD 4.

QCLSN

Multiplexed Collision

Output

QCLSN indicates a collision condition on the network.

QCLSN for all 4 ports is time-division multiplexed onto

this signal and is sampled with respect to SCLK. The

channel’s slot is synchronized to the rising edge of

QRST/STRB. At the r ising edge of reset, QCLSN is

sampled to determine PHYAD 2.

.

.

Am79C989 11

PRELIMINARY

Management Interface

MDC

Management Data Clock

Input

MDC provides the timing reference for data on the

MDIO pin. The Management Interface provides read

and write access to QuEST registers, similar to the MII

management interface of the IEEE 802.3u standard.

MDIO

Management Data I/O

Input/Output

MDIO is a bidirectional data signal between QuEST

and a management entity . MDIO timing is ref erenced to

MDC. The Management Interface provides read and

write access to QuEST registers, similar to the MII

management interface of the IEEE 802.3u standard.

Miscellaneous Pins

SCLK

System Clock

Input

SLCK is a 40-MHz (100 ppm) clock used for timing the

10BASE-T ports, the (optional) AUI port, the QuASI interface and core logic.

REXT

External Resistor

Input

REXT should be pulled to analog VDD via a 13 K Ω (1%

tolerance) external resistor. This signal is used to determine the 10BASE-T transmit current reference.

QRST/STRB

QuEST Reset and Channel 0 Strobe

Input

QRST/STRB is an active-low signal that will reset

QuEST if asserted for at least 1 µ s. QRST/STRB also

forces the channel slots of the QuASI interface to be

continuous aligned if strobed for a single clock period.

Power Pins

VDD

Digital Power

Power

There is a single power supply pin that is used for internal digital circuitry. The VDD pin must be connected to

a +5 V supply.

VSS

Digital Ground

Power

There is a single ground pin that is used for internal digital circuitry. The VSS pin must be connected to ground.

VDDIO

Digital I/O Power

Power

There is a single power supply pin that is used for digital I/O pins. The VDDIO pin can be connected to either

a +5 V or a +3.3 V supply.

VSSIO

Digital I/O Ground

Power

There is a single ground pin that is used for digital I/O

pins. The VSSIO pin must be connected to ground.

VDDTX

Analog 10BASE-T Power

Power

There are three power supply pins that are used for analog 10BASE-T transmit pins. The VDDTX pins must

be connected to a +5 V supply.

VSSTX

Analog 10BASE-T Ground

Power

There are two ground pins that are used for analog

10BASE-T transmit pins. The VSSTX pins must be

connected to ground.

VSSRX

Analog 10BASE-T Ground

Power

There is a single ground pin that is used for analog

10BASE-T receive pins. The VSSRX pin must be connected to ground.

VSSAUI

Analog I/O Ground

Power

There is a single ground pin that is used for analog A UI

circuitry. The VSSAUI pin must be connected to

ground.

12 Am79C989

Loading...

Loading...