T

w

■

■

■

■

■

■

■

■

■

■

■

■

PRELIMINARY

Am79C984A

enhanced Integrated Multiport Repeater (eIMR™)

DISTINCTIVE CHARACTERISTICS

Repeater functions comply with IEEE 802.3

Repeater Unit specifications

Four integral 10BASE-T transceivers with onchip filtering that eliminate the need for external

filter modules on the 10BASE-T transmit-data

(TXD) and receive-data (RXD) lines

One Reversible Attachment Unit Interface

(RAUI™) port that can be used either as a

standard IEEE-compliant AUI port for

connection to a Medium Attachment Unit (MAU),

or as a reversed port for direct connection to a

Media Access Controller (MAC)

Low cost suitable for non-managed multiport

repeater designs

Expandable to increase number of repeater

ports with support for up to seven eIMR devices

without the need for an external arbiter

All ports can be individually isolated

(partitioned) in response to excessive collision

conditions or fault conditions.

Full LED support for individual port status LEDs

and network utilization LEDs

Programmable extended distance mode on the

RXD lines, allowing connection to cables longer

than 100 meters

Twisted Pair Link Test capability conforming to

the 10BASE-T standard. The Link Test function

and the transmission of Link Test pulses can be

optionally disabled through the control port to

allow devices that do not implement the Link Test

function to work with the eIMR device.

Programmable option of automatic polarity

detection and correction permits automatic

recovery due to wiring errors

Full amplitude and timing regeneration for

retransmitted waveforms

CMOS device with a single +5-V supply

GENERAL DESCRIPTION

The enhanced Integrated Multiport Repeater (eIMR)

device is a VLSI integrated circuit that provides a system-level solution to designing non-managed multiport

repeaters. The device integr ates the repeater functions

specified in Section 9 of the IEEE 802.3 standard and

Twisted Pair Transceiver functions complying with the

10BASE-T standard.

his document contains information on a product under development at Advanced Micro Devices. The

information is intended to help you evaluate this product. AMD reserves the right to change or discontinue

ork on this proposed product without notice.

The eIMR device provides four Twisted Pair (TP) ports

and one RAUI port for direct connection to a MAC. The

total number of ports per repeater unit can be increased by connecting multiple eIMR devices through

their expansion ports, hence, minimizing the total cost

per repeater port.

The device is fabricated in CMOS technology and

requires a single +5-V supply.

Publication# 20650 Rev: B Amendment/0

Issue Date: January 1998

P R E L I M I N A R Y

ORDERING INFORMATION

Standard Products

AMD standard products are available in se v eral packages and oper ating ranges. The order number (Valid Combination) is f ormed

by a combination of the elements below.

Am79C984A

CJ

\W

ALTERNATE PACKAGING OPTION

\W = Trimmed and formed in a tray

TEMPERATURE RANGE

C = Commercial (0˚C to +70˚C)

P ACKA GE TYPE

J = 84-Pin Plastic Leaded Chip Carrier (PL 084)

K = 100-Pin Plastic Quad Flat Pack (PQR100)

SPEED OPTION

Not Applicable

DEVICE NUMBER/DESCRIPTION

Am79C984A

enhanced Integrated Multiport Repeater (eIMR)

Valid Combinations

Am79C984A JC, KC\W

2 Am79C984A

Valid Combinations

Valid Combinations list configurations planned to

be supported in volume for this device. Consult

the local AMD sales office to confirm availability

of specific valid combinations and to check on

newly released combinations.

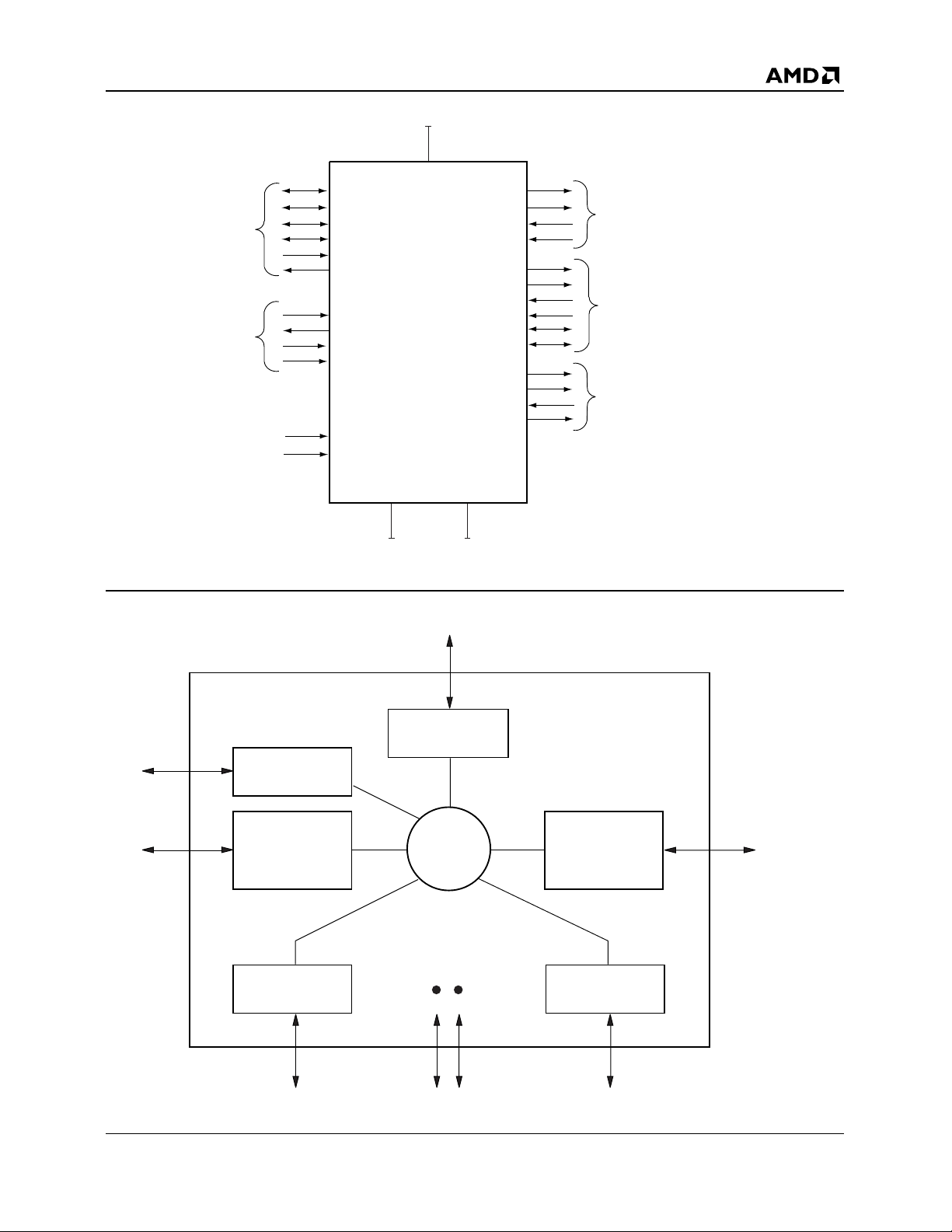

BLOCK DIAGRAM

P R E L I M I N A R Y

DAT

JAM

COL

ACK

SELI[1:0]

TX

MUX

Preamble

Jam Sequence

SELO

LDA[4:0], LDB[4:0]

LDGA, LDGB

LDC[2:0]

LED

Interface

Expansion Port

ACT[7:0]

SI

SO

SCLK

Test

and

AMODE

Port

Control

20650B-1

20650A-1

FIFO

Decoder

Manchester

RX

RX

AUI

Port

DI±

CI±

MUX

MUX

DO±

Lock

Phase

FIFO

CONTROL

Loop

TP

RXD±

0

Port

TXD±

Encoder

Manchester

Control

eIMR Chip

3

TP

Port

RXD±

TXD±

Link T est

Partitioning

Reset

RST

Clock

Timers

Gen

CLK

Am79C984A 3

RELATED AMD PRODUCTS

P R E L I M I N A R Y

Part No.

Am7990

Am7992B Serial Interface Adapter (SIA)

Am7996 IEEE 802.3/Ethernet/Cheapernet Transceiver

Am79C90 CMOS Local Area Network Controller for Ethernet (C-LANCE)

Am79C98 Twisted Pair Ethernet Transceiver (TPEX)

Am79C100 Twisted Pair Ethernet Transceiver Plus (TPEX+)

Am79C981 Integrated Multiport Repeater Plus (IMR+™)

Am79C982 basic Integrated Multiport Repeater (bIMR™)

Am79C987 Hardware Implemented Management Information Base (HIMIB™)

Am79C988 Quad Integrated Ethernet Transceiver (QuIET™)

Am79C900 Integrated Local Area Communications Controller (ILACC™)

Am79C940 Media Access Controller for Ethernet (MACE™)

Am79C960 PCnet™-ISA Single-Chip Ethernet Controller (for ISA bus)

Am79C961 PCnet™-ISA+ Single-Chip Ethernet Controller for ISA (with Microsoft® Plug n’ Play® Support)

Am79C961A PCnet™-ISA II Full Duplex Single-Chip Ethernet Controller for ISA

Am79C965 PCnet™-32 Single-Chip 32-Bit Ethernet Controller

Am79C970 PCnet™-PCI Single-Chip Ethernet Controller (for PCI bus)

Am79C970A PCnet™-PCI II Full Duplex Single-Chip Ethernet Controller (for PCI bus)

Am79C974 PCnet™-SCSI Combination Ethernet and SCSI Controller for PCI Systems

Am79C983 Integrated Multiport Repeater 2 (IMR2™)

Am79C985 enhanced Integrated Multiport Repeater Plus (eIMR+™)

Description

Local Area Network Controller for Ethernet (LANCE)

4 Am79C984A

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-29

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-29

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-30

STANDARD PRODUCTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30

BLOCK DIAGRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-31

RELATED AMD PRODUCTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-32

CONNECTION DIAGRAM (PL 084) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-35

CONNECTION DIAGRAM (PQR100) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-36

LOGIC SYMBOL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-37

LOGIC DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-37

PIN DESIGNATIONS (PL 084). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-38

Listed by Pin Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-38

PIN DESIGNATIONS (PQR100) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-39

Listed by Pin Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-39

PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-40

AUI Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-40

Twisted Pair Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-40

Expansion Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-40

Control Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-41

LED Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-41

Miscellaneous Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-41

FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-43

Basic Repeater Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-43

Repeater Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-43

Signal Regeneration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-43

Jabber Lockup Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-43

Collision Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-43

Fragment Extension. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-43

Auto Partitioning/Reconnection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-43

Detailed Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-44

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-44

AUI Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-44

TP Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-44

Twisted Pair Transmitters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-44

Twisted Pair Receivers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-44

Link Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-45

Polarity Reversal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-45

Visual Status Monitoring (LED) Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-45

Network Activity Display. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-46

Expansion Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-48

Internal Arbitration Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-48

IMR+ Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-48

Control Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-49

Command/Response Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-50

Control Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-50

SET (Write Commands) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-52

P R E L I M I N A R Y

Chip Programmable Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

Alternate AUI Partitioning Algorithm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

Alternate TP Partitioning Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

AUI Port Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

AUI Port Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

TP Port Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

TP Port Enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

Disable Link Test Function (Per TP port) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

Enable Link Test Function (Per TP port) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

Disable Link Pulse (Per TP Port) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

Am79C984A 5

P R E L I M I N A R Y

Enable Link Pulse (Per TP Port). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-52

Disable Automatic Receiver Polarity Reversal (Per TP Port). . . . . . . . . . . . . . . . .1-53

Enable Automatic Receiver Polarity Reversal (Per TP Port) . . . . . . . . . . . . . . . . .1-53

Disable Receiver Extended Distance Mode (Per TP Port). . . . . . . . . . . . . . . . . . .1-53

Enable Receiver Extended Distance Mode (Per TP Port) . . . . . . . . . . . . . . . . . . .1-53

Disable Software Override of LEDs 5

(Per Port - AUI and TP, Global) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-53

Enable Software Override of Bank A LEDs (Per Port - AUI and TP, Global). . . . .1-53

Enable Software Override of Bank B LEDs (Per Port - AUI and TP, Global). . . . .1-54

Software Override of LED Blink Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-54

GET (Read Commands). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-54

AUI Port(s) Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-54

Alternate AUI Port(s) Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-54

TP Port Partitioning Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-54

Bit Rate Error Status of TP Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-54

Link Test Status of TP ports. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-55

Receive Polarity Status of TP Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-55

MJLP Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-55

Version . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-55

SYSTEMS APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-55

eIMR to TP Port Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-55

Twisted Pair Transmitters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-55

Twisted Pair Receivers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-55

MAC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-57

Internal Arbitration Mode Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-57

IMR+ Mode External Arbitration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-57

Visual Status Display. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-59

ABSOLUTE MAXIMUM RATINGS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-60

OPERATING RANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-60

DC CHARACTERISTICS over operating ranges unless otherwise specified . . . . . . . . . . . . . . . . .1-60

SWITCHING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-62

KEY TO SWITCHING WAVEFORMS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-64

SWITCHING WAVEFORMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-64

SWITCHING TEST CIRCUIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-69

6 Am79C984A

P R E L I M I N A R Y

CONNECTION DIAGRAM (PL 084)

REXT

AVSS

DI+

DI–

VDD

CI+

CI–

AVSS

DO+

DO–

AMODE

VDD

DVSS

VDD

VDD

VDD

RST

CLK

DVSS

SELI_0

SELI_1

12

13

14

15

16

17

18

19

20

21

23

24

25

26

27

28

29

30

31

32

RXD3–

102211

33

34

SELO

RXD3+

RXD2–

8

9

35

36

COL

DVSS

RXD1–

RXD2+

7

6

38

37

DAT

ACK

RXD0–

RXD1+

5

39

JAM

VDD

TXD3–

VDD

RXD0+

3

4

2

eIMR

Am79C984A

41

42

40

SI

NC

DVSS

1

43

SO

AVSS

TXD3+

84

83

45

44

SCLK

TXD2+

TXD2–

81

82

46

47

VDD

ACT0

VDD

80

48

ACT1

TXD1–

TXD1+

78

79

50

49

ACT2

DVSS

TXD0–

AVSS

77

51

ACT4

ACT3

TXD0+

76

52

ACT5

75

53

VDD

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

ACT6

LDC2

LDC1

LDC0

VDD

LDGB

LDGA

LDB4

DVSS

LDA4

LDB3

LDA3

DVSS

LDB2

LDA2

VDD

LDB1

LDA1

DVSS

LDB0

LDA0

ACT7

20650A-2

20650B-2

Am79C984A 7

CONNECTION DIAGRAM (PQR100)

RXD3+

RXD2–NCRXD2+

RXD1–

RXD1+

99

98

97969594939291908988878685

RXD3–

NC

NC

NC

REXT

AVSS

DI+

DI–

VDD

CI+

CI–

AVSS

DO+

DO–

AMODE

VDD

DVSS

VDD

VDD

VDD

RST

NC

CLK

DVSS

SELI_0

SELI_1

NC

NC

NC

SELO

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31323334353637383940414243444546474849

P R E L I M I N A R Y

RXD0–

RXD0+

VDD

TXD3–

TXD3+

AVSS

TXD2–

TXD2+

VDD

TXD1–

TXD1+

848281

eIMR

Am79C984A

AVSS

TXD0–

83

TXD0+

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

VDD

NC

NC

NC

LDC2

LDC1

LDC0

VDD

LDGB

LDGA

LDB4

DVSS

LDA4

LDB3

LDA3

DVSS

LDB2

LDA2

VDD

LDB1

LDA1

NC

DVSS

LDB0

LDA0

ACT7

NC

NC

NC

ACT6

COL

NC

DVSS

ACK

DAT

VDD

JAM

NC

SI

DVSS

SO

VDD

SCLK

ACT0

ACT1

8 Am79C984A

ACT2

DVSS

ACT3

ACT4

ACT5

20650B-3

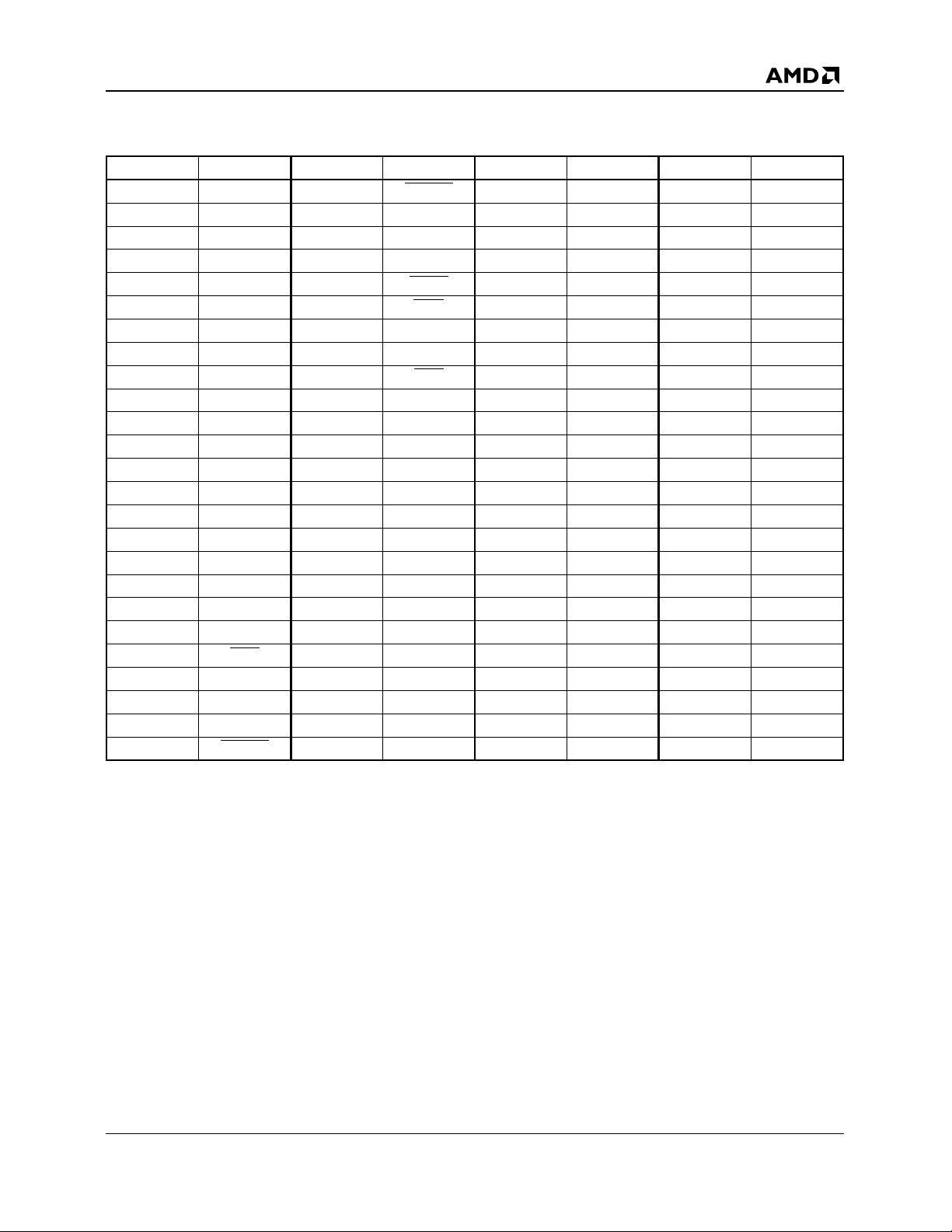

LOGIC SYMBOL

Expansion

Port

Test and

Control

Port

DAT

JAM

ACK

COL

SELO

SELI[1:0]

SI

SO

SCLK

AMODE

CLK

RST

P R E L I M I N A R Y

V

DD

Am79C984

LDA[4:0], LDB[4:0]

TXD+

TXD–

RXD+

RXD–

DO+

DO–

DI+

DI–

CI+

CI–

LDGA, LDGB

LDC[2:0]

ACT[7:0]

Twisted Pair

Ports

(4 Ports)

AUI

LED

Interface

LOGIC DIAGRAM

LED

Port

Control

Port

DV

SS

AV

AUI

Repeater

State

Machine

SS

20650A-4

20650B-4

Expansion

Port

Twisted Pair

Port 0

Twisted Pair

Port 3

20650A-5

20650B-5

Am79C984A 9

PIN DESIGNATIONS (PL 084)

Listed by Pin Number

P R E L I M I N A R Y

Pin No .

1

2 TXD3- 23 VDD 44 SCLK 65 LDB3

3 VDD 24 DVSS 45 VDD 66 LDA4

4 RXD0+ 25 VDD 46 ACT0 67 DVSS

5 RXD0- 26 VDD 47 ACT1 68 LDB4

6 RXD1+ 27 VDD 48 ACT2 69 LDGA

7 RXD1- 28 RST 49 DVSS 70 LDGB

8 RXD2+ 29 CLK 50 ACT3 71 VDD

9 RXD2- 30 DVSS 51 ACT4 72 LDC0

10 RXD3+ 31 SELI_0 52 ACT5 73 LDC1

11 RXD3- 32 SELI_1 53 ACT6 74 LDC2

12 REXT 33 SELO 54 ACT7 75 VDD

13 AVSS 34 COL 55 LDA0 76 TXD0+

14 DI+ 35 DVSS 56 LDB0 77 TXD015 DI- 36 ACK 57 DVSS 78 AVSS

16 VDD 37 DAT 58 LDA1 79 TXD1+

17 CI+ 38 VDD 59 LDB1 80 TXD118 CI- 39 JAM 60 VDD 81 VDD

19 AVSS 40 NC 61 LDA2 82 TXD2+

20 DO+ 41 DVSS 62 LDB2 83 TXD221 DO- 42 SI 63 DVSS 84 AVSS

Pin Name

TXD3+ 22 AMODE 43 SO 64 LDA3

Pin No .

Pin Name

Pin No .

Pin Name

Pin No. Pin Name

10 Am79C984A

PIN DESIGNATIONS (PQR100)

Listed by Pin Number

P R E L I M I N A R Y

Pin No .

1

2 NC 27 NC 52 NC 77 NC

3 NC 28 NC 53 NC 78 NC

4 NC 29 NC 54 NC 79 NC

5 REXT 30 SELO 55 ACT7 80 VDD

6 AVSS 31 COL 56 LDA0 81 TXD0+

7 DI+ 32 DVSS 57 LDB0 82 TXD0-

8 DI- 33 NC 58 DVSS 83 AVSS

9 VDD 34 ACK 59 NC 84 TXD1+

10 CI+ 35 DAT 60 LDA1 85 TXD111 CI- 36 VDD 61 LDB1 86 VDD

12 AVSS 37 JAM 62 VDD 87 TXD2+

13 DO+ 38 NC 63 LDA2 88 TXD214 DO- 39 DVSS 64 LDB2 89 AVSS

15 AMODE 40 SI 65 DVSS 90 TXD3+

16 VDD 41 SO 66 LDA3 91 TXD317 DVSS 42 SCLK 67 LDB3 92 VDD

18 VDD 43 VDD 68 LDA4 93 RXD0+

19 VDD 44 ACT0 69 DVSS 94 RXD020 VDD 45 ACT1 70 LDB4 95 RXD1+

21 RST 46 ACT2 71 LDGA 96 RXD122 NC 47 DVSS 72 LDGB 97 RXD2+

23 CLK 48 ACT3 73 VDD 98 NC

24 DVSS 49 ACT4 74 LDC0 99 RXD225 SELI_0 50 ACT5 75 LDC1 100 RXD3+

Pin Name

RXD3- 26 SELI_1 51 ACT6 76 LDC2

Pin No .

Pin Name

Pin No .

Pin Name

Pin No. Pin Name

Notes:

1. Pin 40 has a bonding option depending on internal device name.

2. NC = No Connection.

Am79C984A 11

P R E L I M I N A R Y

DI ±

DO ±

CI ±

PIN DESCRIPTION

AUI Port

DI+, DI–

Data In

Differential Input

are differential, Manchester receiver pins. The sig-

nals comply with IEEE 802.3, Section 7.

DO+, DO–

Data Out

Differential Output

are differential, Manchester output driver pins. The

signals comply with IEEE 802.3, Section 7.

CI+, CI–

Collision Input

Differential Input/Output

are differential, Manchester I/O signals. As an input,

CI is a collision-receive indicator . As an output, CI generates a 10-MHz signal if the eIMR device senses a

collision.

Twisted Pair Ports

TXD+

Transmit Data

Differential Output

TXD ± are 10BASE-T port differential drivers (4 ports).

RXD+

Receive Data

Differential Input

RXD ± are 10BASE-T port differential receive inputs

(4 ports).

0-3

0-3

, TXD–

, RXD–

0-3

0-3

Expansion Bus

DAT

Data

Input/Output/3-State

If the SELO

collision conditions, the eIMR device drives NRZ data

onto the DAT line, regenerating the preamble if necessary. During a collision, when JAM is HIGH, D A T is used

to differentiate between single-port (DAT=1) and multiport (DAT=0) collisions. DAT is an output when ACK is

asserted and the eIMR device’s ports are active; DAT

is an input when ACK is asserted and the ports are

inactive. If ACK is not asserted, DAT is in the high-impedance state. It is recommended that DAT be pulled

up or down via a high value resistor.

JAM

Jam

Input/Output/3-State

The active eIMR device drives JAM HIGH, if it detects

a collision condition on one or more of its ports. The

and ACK pins are asserted during non-

state of the DAT pin is used in conjunction with JAM to

indicate a single port (DA T =1) or multiport (DAT=0) collision. J AM is in the high-impedance state if neither the

SEL

nor ACK signal is asserted. It is recommended that

JAM be pulled up or down via a high value resistor.

SELI

0-1

Select In

Input, Active LOW

When the expansion bus is configured f or Internal Arbitration mode, these signals indicate that another eIMR

device is active; SELI

the upstream device. At reset, SELI

or SELI

0

is driven by SELO from

1

selects between

0

the Internal Arbitration mode and the IMR+ mode of the

expansion bus; a HIGH selects the Internal Arbitration

mode and a LOW selects the IMR+ mode.

SELI_1 SELI_0

X 1 Internal

X 0 IMR+

Arbitration

Mode

SELO

Select Out

Output, Active LOW

If the expansion bus is configured f or Internal Arbitration

mode, an eIMR device drives this pin LOW when it is

active or when either of its SELI

pins is LOW. An

0-1

active eIMR device is defined as having one or more

ports receiving or colliding and/or is still transmitting

data from the internal FIFO, or extending a pack et to the

minimum of 96 bit times. When the expansion bus is

configured for IMR+ mode, SELO

is active when the

eIMR device is active (acquiring the functionality of the

pin on the Am79C971 IMR+ device).

REQ

ACK

Acknowledge

Input/Output, Active LOW, Open Drain

This signal is asserted to indicate that an eIMR device

is active. It also signals to the other eIMR devices the

presence of a valid collision status on the JAM line and

valid data on the DAT line. When the eIMR device is

configured for Internal Arbitration mode, ACK is an I/O,

and must be pulled to VDD via a minimum equivalent

resistance of 1 k

for IMR+ mode, A

When the eIMR device is configured

Ω.

CK is an input driven by an external

arbiter.

COL

Collision

Input/Output, Active LOW, Open Drain

When asserted, COL indicates that more than one eIMR

device is active. Each eIMR device generates the Collision Jam sequence independently . When the eIMR device is configured for Internal Arbitration mode, COL is

12 Am79C984A

P R E L I M I N A R Y

an I/O and must be pulled to VDD via a minimum equivalent resistance of 1 k

sion port is configured for IMR+ mode, COL

Ω.

When the eIMR device expan-

is an input

driven by an external arbiter.

Control Port

AMODE

AUI Mode

Input

At reset, this pin sets the AUI port to either normal or

reversed mode. If AMODE is LOW at the rising edge of

, the AUI port is set to the normal mode; if AMODE

RST

is HIGH, the AUI port is set to the reversed mode.

SCLK

Serial Clock In

Input

Serial data (input or output) is clocked (in or out) on the

rising edge of the signal on this pin. SCLK is asynchronous to CLK and can operate at frequencies up to 10

MHz.

SI

Serial In

Input

The SI pin is used as a test/control serial input port.

Control commands are clocked in on this pin synchronous to SCLK input.

At reset, SI sets the state of the Automatic P olarity Reversal function. If SI is HIGH at the rising edge of RST

Automatic Polarity Reversal is disabled. If SI is LOW at

the rising edge of RST, Automatic Polar ity Reversal is

enabled.

SO

Serial Out

Output

The SO pin is used as a control command serial output

port. Responses to control commands are clocked out

on this pin synchronous to the SCLK input.

LED Interface

LDA

LED Drivers

Output, Open Drain

LDA

respectively. LDA

AUI port; LDA

four TP ports. The port attributes monitored by LDA

and LDB

LDGA

Global LED Driver, Bank A

Output, Open Drain

LDGA is the Global LED driver for LED Bank A. The

signal represents global CRS or COL conditions. In a

, LDB

0-4

0-4

0-4

and LDB

are programmed by three pins, LDC

0-4

drive LED Bank A and LED Bank B,

0-4

and LDB

0

and LDB

1-4

indicate the status of the

0

indicate the status of the

1-4

0-2

0-4

.

multiple-eIMR configuration, LDGA from each of the

eIMR devices can be tied together to drive a single global LED in Bank A.

LDGB

Global LED Driver, Bank B

Output, Open Drain

LDGB is the Global LED driver for LED Bank B. The

signal represents global CRS or JAB conditions. In a

multiple eIMR configuration, LDGB from each of the

eIMR devices can be tied together to drive a single global LED in Bank B.

LDC

0-2

LED Control

Input

These pins select the attributes that will be displayed

on LDA

0-4

, LDB

, LDGA, and LDGB. If an LED is pro-

0-4

grammed to display two attributes , the attribute associated with the periodic blink takes precedence.

ACT

0-7

Activity Display

Output

These signals drive the activity LEDs, which indicate

the percentage of network utilization. The displa y is updated every 250 ms.

Miscellaneous Pins

RST

,

Reset

Input, Active LOW

When RST is LOW , the eIMR device resets to its def ault

state. On the rising (trailing) edge of RST , the eIMR also

monitors the state of the SELI

to configure the operating mode of the device. In multiple eIMR systems, the falling (leading) edge of the RST

signal must be synchronized to CLK.

CLK

Master Clock In

Input

This pin is a 20-MHz clock input.

REXT

External Reference

Input

This pin is used for an internal current reference. It must

be tied to VDD via a 13-kΩ resistor with 1% tolerance.

VDD

Power

Power Pin

This pin supplies power to the device.

, SI, and AMODE pins,

0-1

Am79C984A 13

P R E L I M I N A R Y

AVSS

Analog Ground

Ground Pin

This pin is the ground reference for the differential

receivers and drivers.

DVSS

Digital Ground

Ground Pin

This pin is the ground reference for all the digital logic

in the eIMR device.

14 Am79C984A

Loading...

Loading...