PRELIMINARY

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed

product without notice.

Publication# 22206 Rev: B Amendment/0

Issue Date: November 1998

Refer to AMD’s Website (www.amd.com) for the latest information.

Am79C978

PCnet™- Home

Single-Chip 1/10 Mbps PCI Home Networking Controller

DISTINCTIVE CHARACTERISTICS

■

Fully integrated 1 Mbps HomePNA Physical

Layer (PHY) as defined by Home Phoneline

Networking Alliance (HomePNA) specification

1.0

— Optimized for home networking applications

over ordinary copper telephone wire

— In-band control features:

Adjustable power and speed levels

32 bits of reserved in-band messaging piggy-

backed on Ethernet packet

— Register programmable features:

Power control

Performance registers

Speed control

Major frame timing parameters programma-

ble: ISBI, AID ISBI, pulse width, inter-symbol

time

■

Fully integrated 10 Mbps PHY interface

— Comprehensive Auto-Negotiation

implementation

— Full-duplex capability

— Optimized for 10BASE-T applications

■

Integrated Fast Ethernet controller for the

Peripheral Component Interconnect (PCI) bus

— 32-bit glueless PCI host interface

— Supports PCI clock frequency from DC to

33 MHz independent of network clock

— Supports network operation with PCI clock

from 15 MHz to 33 MHz

— High performance bus mastering

architecture with integrated Direct Memory

Access (DMA) Buffer Management Unit for

low CPU and bus utilization

— PCI draft specification revision 2.2 compliant

— Supports PCI Subsystem/Subvendor ID/

Vendor ID pr ogramming through the

EEPROM interface

— Supports both PCI 5.0-V and 3.3-V signaling

environments

— Plug and Play compatible

— Supports an unlimited PCI burst length

— Big endian and little endian byte alignments

supported

— Implements optional PCI power management

event (PME) pin

■

Dual-speed CSMA/CD (10 Mbps and 100 Mbps)

Media Access Controller (MAC) compliant with

IEEE/ANSI 802.3 Ethernet standard

■

Compliant with HomePNA specification 1.0

■

Media Independent Interface (MII) for

connecting external 10/100 Mbps transceivers

— IEEE 802.3u compliant MII

— Intelligent Auto-Poll™ external PHY status

monitor and interrupt

— Supports both auto-negotiable and non-

auto-negotiable external PHYs

— Supports 10BASE-T, 100BASETX/FX,

100BASET4, and 100BASET2 IEEE 802.3

compliant MII PHYs at full-duplex or halfduplex

■

Full-duplex operation supported on the MII port

with independent Transmit (TX) and Receive

(RX) channels

■

Supports PC98/PC99 and Net PC specifications

— Implements full OnNow features including

pattern matching and link status wake-up

events

— Implements Magic Packet™ mode

— Magic Packet mode and the physical address

loaded from EEPROM at power up without

requiring PCI clock

— Supports PCI Bus Power Management

Interface specification revision 1.1

— Supports Advanced Configuration and

Power Interface (ACPI) specification version

1.0

— Supports Network Device Class Power

Management specification version 1.0a

2 Am79C978

PRELIMINARY

■

Independent internal TX and RX FIFOs

— Programmable FIFO watermarks for both TX

and RX operations

— RX frame queuing for high latency PCI bus

host operation

— Programmable allocation of buffer space

between RX and TX queues

■

Extensive programmable internal/external

loopback capabilities

■

EEPROM interface supports jumperless design

and provides through-chip programming

— Supports full programmability of half-/full-

duplex operation through EEPROM mapping

— Programmable PHY reset output pin capable

of resetting external PHY without the need

for buffering

■

Extensive programmable LED status support

■

Look-Ahead Packet Processing (LAPP) data

handling technique reduces system overhead

by allowing protocol analysis to begin before

the end of a receive frame

■

Includes Programmable Inter Packet Gap (IPG)

to address less network aggressive MAC

controllers

■

Offers the Modified Back-Off algorithm to

address the

Ethernet Capture Effect

■

IEEE 1149.1-compliant JTAG Boundary Scan

test access port interface and NAND tree test

mode for board-level production connectivity

test

■

Software compatible with AMD’s PCnet™

Family and LANCE/C-LANCE register and

descriptor architecture

■

Very low power consumption

■

+3.3 V power supply along with 5 V tolerant I/Os

enable broad system compatibility

■

Available in 144-pin TQFP and 160-pin PQFP

packages

GENERAL DESCRIPTION

The Am79C978 controller is the first in a series of

home networking products from AMD. The Am79C978

controller is fabricated in an advanced low po wer 3.3 V

CMOS process to provide low operating current for

power sensitive applications.

The Am79C978 controller contains an Ethernet Controller based on the Am79C971 Fast Ethernet controller, a physical layer device for supporting the 802.3

standard for 10BASE-T, and a physical layer device f or

data networking at speeds up to 1 Mbps over ordinary

residential telephone wiring.

The integrated PCI Ethernet controller is a highly integrated 32-bit full-duplex, 10/100 Mbps Ethernet controller solution designed to address high-performance

system application requirements. It is a flexible busmastering device that can be used in any application,

including network ready PCs. The bus master architecture provides high data throughput and low CPU and

system bus utilization.

The integrated Ethernet transceiver is a physical layer

device supporting the IEEE 802.3 standards for

10BASE-T. It provides all of the PHY la yer functions required to support 10 Mbps data transfer speeds.

The integrated HomePNA transceiver is a physical

layer de vice that enables data netw orking at speeds up

to 1 Mbps over common residential phone wiring regardless of topology and without disrupting telephone

(POTS) service.

The 32-bit multiplexed bus interface unit provides a direct interface to the PCI local bus, simplifying the design of an Ethernet or home network node in a PC

system. The device has built-in support for both little

and big endian byte alignment. The integrated home

networking controller’s adv anced CMOS design allo ws

the bus interface to be connected to either a +5.0 V or

a +3.3 V signaling environment. A compliant IEEE

1149.1 JT A G test interface f or board level testing is also

provided, as well as a NAND tree test structure for

those systems that do not support the JTAG interface.

The integrated Am79C978 home networking controller

is also compliant with the PC98, PC99, and Net PC

specifications. It includes the full implementation of the

Microsoft OnNow and ACPI specifications, which are

backward compatible with Magic Packet technology,

and is compliant with the PCI Bus Pow er Management

Interface specification by supporting the four power

management states (D0, D1, D2, and D3), the optional

PME

pin, and the necessary configuration and data

registers.

The integrated Am79C978 home networking controller

is a complete Ethernet or home network node integrated into a single VLSI de vice. It contains a bus interface unit, a Direct Memory Access (DMA) Buffer

Management Unit, an ISO/IEC 88023 (IEEE 802.3)

compliant Media Access Controller (MAC), a Transmit

FIFO and a large Receive FIFO, and an IEEE 802.3u

compliant MII. Both IEEE 802.3 compliant full-duplex

and half-duplex operations are supported on the MII interface. 10/100 Mbps operation is suppor ted through

the MII interface.

The integrated Am79C978 home networking controller

is register compatible with the LANCE (Am7990) and

C-LANCE (Am79C90) Ethernet controllers and all

Am79C978 3

PRELIMINARY

Ethernet controllers in the PCnet Family (

except

ILACC™ (Am79C900)), including PCnet-ISA

(Am79C960), PCnet-ISA+ (Am79C961), PCnet-ISA II

(Am79C961A), PCnet-32 (Am79C965A), PCnet-PCI

(Am79C970), PCnet-PCI II (Am79C970A), PCnet-

FAST

(Am79C971), and PCnet-

FAST+

(Am79C972).

The Buffer Management Unit supports the LANCE and

PCnet descriptor software models.

The integrated Am79C978 controller supports autoconfiguration in the PCI configuration space. Additional

integrated controller configuration parameters, includ-

ing the unique IEEE physical address, can be read

from an external non-volatile memory (EEPROM) immediately following system reset.

In addition, the Am79C978 controller provides programmable on-chip LED drivers for transmit, receive,

collision, link integrity, Magic Packet status, speed, activity, power output, address match, full-duplex, or 100

Mbps status.

4 Am79C978

PRELIMINARY

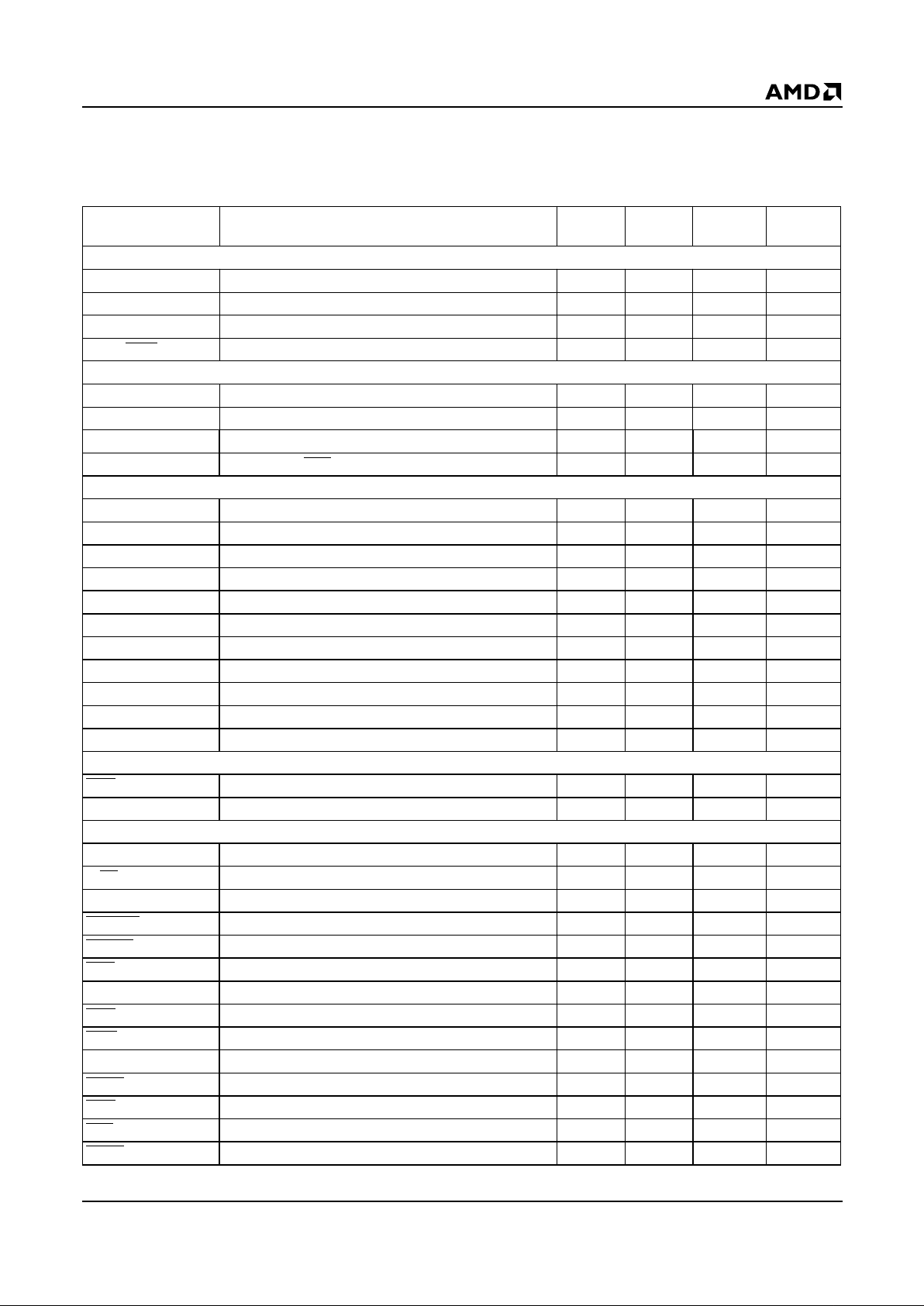

BLOCK DIAGRAM

CLK

RST

AD[31:0]

C/BE[3:0]

PAR

FRAME

TRDY

IRDY

STOP

IDSEL

DEVSEL

REQ

GNT

PERR

SERR

INTA

PCI Bus

Interface

Unit

Buffer

Management

Unit

Bus

Rcv

FIFO

Bus

Xmt

FIFO

FIFO

Control

Network

Port

Manager

MAC

Rcv

FIFO

12K

SRAM

MAC

Xmt

FIFO

JTAG

Port

Control

OnNow

Power

Management

Unit

802.3

MAC

Core

93C46

EEPROM

Interface

LED

Control

PME

PG

TCK

TMS

TDI

TDO

Transmit

State

Machine

MII

Interface

MII

Management

MDIO

Receive

State

Machine

PHY Control

Link

Monitor

Auto

Negotiation

10 Mbps PHY

Transmit

State

Machine

MII

Interface

Receive

State

Machine

Drive

Control

Analog

Front

End

10 BASE-T

TX±

RX±

LED0

LED1

LED2

LED3

LED4

EECS

EESK

EEDI

EEDO

MII

Management

MDIO

RXD(3:0)/TXD(3:0)

PHY

Control

Link

Monitor

HRTXRXP/N

MDC

1Mbps HomePNA PHY

MDC

Clock

Reference

XTAL2

XTAL1

22206B-1

Am79C978 5

PRELIMINARY

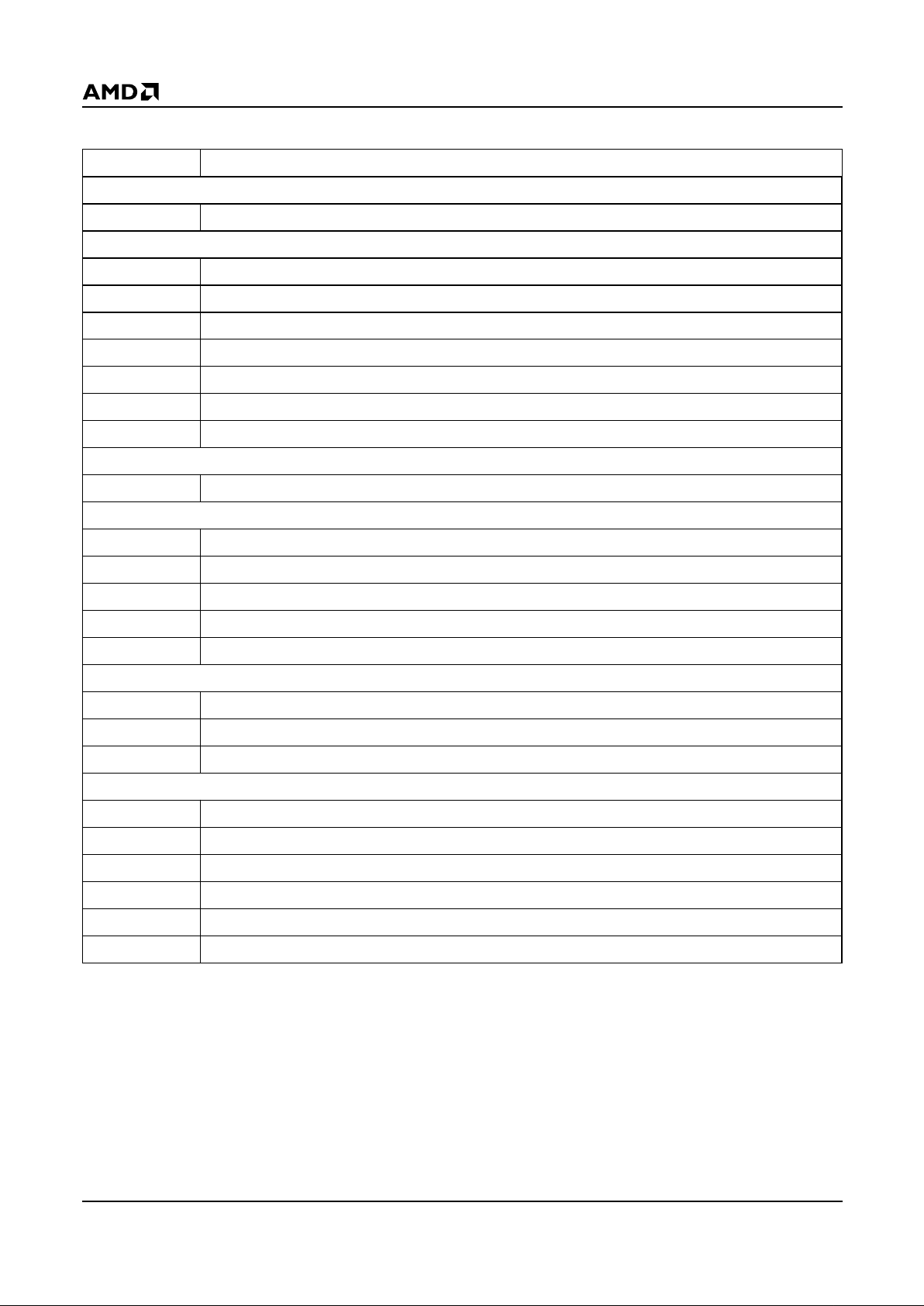

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

BLOCK DIAGRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

RELATED AMD PRODUCTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

CONNECTION DIAGRAM (144 TQFP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

CONNECTION DIAGRAM (160 PQFP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

PIN DESIGNATIONS (PQL144) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Listed By Pin Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

PIN DESIGNATIONS (PQR160) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Listed By Pin Number. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

PIN DESIGNATIONS (PQL144) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Listed By Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

PIN DESIGNATIONS (PQR160) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Listed By Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

PIN DESIGNATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Listed By Driver Type. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Standard Products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Magic Packet Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Board Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

EEPROM Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

MII Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

IEEE 1149.1 (1990) Test Access Port Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Ethernet Network Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

HomePNA PHY Network Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Power Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

BASIC FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

System Bus Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Software Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Network Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Media Independent Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

MII Transmit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

MII Receive Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

MII Network Status Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

MII Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

MII Management Frames. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Auto-Poll External PHY Status Polling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Network Port Manager . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

10BASE-T PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

PCI and JTAG Configuration Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Slave Bus Interface Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Slave Configuration Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Slave I/O Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Expansion ROM Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Slave Cycle Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Disconnect When Busy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Disconnect Of Burst Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Master Bus Interface Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Bus Acquisition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Bus Master DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Basic Non-Burst Read Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Basic Burst Read Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

6 Am79C978

PRELIMINARY

Basic Non-Burst Write Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Basic Burst Write Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Target Initiated Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Disconnect With Data Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Disconnect Without Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Target Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Master Initiated Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Preemption During Non-Burst Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Preemption During Burst Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Master Abort. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Advanced Parity Error Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Initialization Block DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Descriptor DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

FIFO DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Non-Burst FIFO DMA Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Burst FIFO DMA Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Buffer Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Re-Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Suspend. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Buffer Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Descriptor Rings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Polling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Transmit Descriptor Table Entry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Receive Descriptor Table Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Receive Frame Queuing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Software Interrupt Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

10/100 Media Access Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Transmit and Receive Message Data Encapsulation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Framing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Destination Address Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Error Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Media Access Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Medium Allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Collision Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Transmit Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Transmit Function Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Automatic Pad Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Transmit FCS Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Transmit Exception Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Loss of Carrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Late Collision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

SQE Test Error. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Receive Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Receive Function Programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Address Matching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Automatic Pad Stripping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Receive FCS Checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Receive Exception Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Loopback Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Miscellaneous Loopback Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Full-Duplex Link Status LED Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

PHY/MAC Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

10BASE-T Physical Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Twisted Pair Transmit Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Twisted Pair Receive Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Am79C978 7

PRELIMINARY

Twisted Pair Interface Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Collision Detect Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Jabber Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Reverse Polarity Detect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Soft Reset Function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

DETAILED FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

1 Mbps HomePNA PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

HomePNA PHY Medium Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Framing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

HomePNA Symbol Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Time Interval Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

ACCESS ID Intervals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Symbol 0 (SYNC interval) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

SYNC Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

SYNC Receive Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

AID Symbols 1 through 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

AID Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

AID Receive Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Collisions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

JAM Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

ACCESS ID Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Silence Interval (AID symbol 7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Data Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Data Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Data Receive Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Data Symbol RLL25 Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Management Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Header AID Remote Control Word Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

PHY Control and Management Block (PCM Block) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Register Administration for 10BASE-T PHY Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Description of the Methodology. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

No SRAM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Low Latency Receive Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Direct SRAM Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Automatic EEPROM Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

EEPROM Auto-Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Direct Access to the Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

EEPROM-Programmable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

EEPROM MAP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

LED Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Power Savings Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Power Management Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

OnNow Wake-Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Link Change Detect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

OnNow Pattern Match Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Pattern Match RAM (PMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Magic Packet Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

IEEE 1149.1 (1990) Test Access Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Boundary Scan Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

TAP Finite State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Supported Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Instruction Register and Decoding Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Other Data Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

NAND Tree Testing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

8 Am79C978

PRELIMINARY

H_RESET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

S_RESET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

Power on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

Software Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

PCI Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

I/O Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

I/O Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Address PROM Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Reset Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Word I/O Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Double Word I/O Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

USER ACCESSIBLE REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

PCI Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

PCI Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

PCI Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

PCI Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

PCI Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

PCI Revision ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

PCI Programming Interface Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

PCI Sub-Class Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

PCI Base-Class Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

PCI Latency Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

PCI Header Type Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

PCI I/O Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

PCI Memory Mapped I/O Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

PCI Subsystem Vendor ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

PCI Subsystem ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

PCI Expansion ROM Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

PCI Capabilities Pointer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

PCI Interrupt Line Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

PCI Interrupt Pin Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI MIN_GNT Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI MAX_LAT Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Capability Identifier Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Next Item Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Power Management Capabilities Register (PMC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Power Management Control/Status Register (PMCSR) . . . . . . . . . . . . . . . . . . . . . . . . . .112

PCI PMCSR Bridge Support Extensions Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

PCI Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

RAP Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

RAP: Register Address Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

Control and Status Registers (CSRs). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

CSR0: Controller Status and Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

CSR1: Initialization Block Address 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

CSR2: Initialization Block Address 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

CSR3: Interrupt Masks and Deferral Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

CSR4: Test and Features Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

CSR5: Extended Control and Interrupt 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

CSR6: RX/TX Descriptor Table Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

CSR7: Extended Control and Interrupt 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

CSR8: Logical Address Filter 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

CSR9: Logical Address Filter 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

CSR10: Logical Address Filter 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

CSR11: Logical Address Filter 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

CSR12: Physical Address Register 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

CSR13: Physical Address Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

CSR14: Physical Address Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

Am79C978 9

PRELIMINARY

CSR15: Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

CSR16: Initialization Block Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

CSR17: Initialization Block Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

CSR18: Current Receive Buffer Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

CSR19: Current Receive Buffer Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CSR20: Current Transmit Buffer Address Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CSR21: Current Transmit Buffer Address Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CSR22: Next Receive Buffer Address Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CSR23: Next Receive Buffer Address Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CSR24: Base Address of Receive Ring Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CSR25: Base Address of Receive Ring Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CSR26: Next Receive Descriptor Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

CSR27: Next Receive Descriptor Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

CSR28: Current Receive Descriptor Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

CSR29: Current Receive Descriptor Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

CSR30: Base Address of Transmit Ring Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

CSR31: Base Address of Transmit Ring Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

CSR32: Next Transmit Descriptor Address Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

CSR33: Next Transmit Descriptor Address Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

CSR34: Current Transmit Descriptor Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

CSR35: Current Transmit Descriptor Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

CSR36: Next Next Receive Descriptor Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

CSR37: Next Next Receive Descriptor Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

CSR38: Next Next Transmit Descriptor Address Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

CSR39: Next Next Transmit Descriptor Address Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

CSR40: Current Receive Byte Count. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

CSR41: Current Receive Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

CSR42: Current Transmit Byte Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

CSR43: Current Transmit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

CSR44: Next Receive Byte Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

CSR45: Next Receive Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

CSR46: Transmit Poll Time Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

CSR47: Transmit Polling Interval. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

CSR48: Receive Poll Time Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

CSR49: Receive Polling Interval . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

CSR58: Software Style. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

CSR60: Previous Transmit Descriptor Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CSR61: Previous Transmit Descriptor Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CSR62: Previous Transmit Byte Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CSR63: Previous Transmit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CSR64: Next Transmit Buffer Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CSR65: Next Transmit Buffer Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CSR66: Next Transmit Byte Count. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CSR67: Next Transmit Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CSR72: Receive Ring Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CSR74: Transmit Ring Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CSR76: Receive Ring Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CSR78: Transmit Ring Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

CSR80: DMA Transfer Counter and FIFO Threshold Control . . . . . . . . . . . . . . . . . . . . . . . . .140

CSR82: Transmit Descriptor Address Pointer Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CSR84: DMA Address Register Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CSR85: DMA Address Register Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CSR86: Buffer Byte Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142

CSR88: Chip ID Register Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

CSR89: Chip ID Register Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

CSR92: Ring Length Conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

CSR100: Bus Timeout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

CSR112: Missed Frame Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

10 Am79C978

PRELIMINARY

CSR114: Receive Collision Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

CSR116: OnNow Power Mode Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

CSR122: Advanced Feature Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

CSR124: Test Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

CSR125: MAC Enhanced Configuration Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

Bus Configuration Registers (BCRs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

BCR0: Master Mode Read Active . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

BCR1: Master Mode Write Active. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

BCR2: Miscellaneous Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .149

BCR4: LED 0 Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

BCR5: LED1 Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

BCR6: LED2 Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153

BCR7: LED3 Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

BCR9: Full-Duplex Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

BCR16: I/O Base Address Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

BCR17: I/O Base Address Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

BCR18: Burst and Bus Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

BCR19: EEPROM Control and Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

BCR20: Software Style. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164

BCR22: PCI Latency Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .165

BCR23: PCI Subsystem Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

BCR24: PCI Subsystem ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

BCR25: SRAM Size Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

BCR26: SRAM Boundary Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

BCR27: SRAM Interface Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

BCR28: Expansion Bus Port Address Lower (Used for Flash/EPROM and SRAM Accesses)169

BCR29: Expansion Port Address Upper (Used for Flash/EPROM Accesses). . . . . . . . . . . . .169

BCR30: Expansion Bus Data Port Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

BCR31: Software Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

BCR32: PHY Control and Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

BCR33: PHY Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

BCR34: PHY Management Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

BCR35: PCI Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

BCR36: PCI Power Management Capabilities (PMC) Alias Register . . . . . . . . . . . . . . . . . . .174

BCR37: PCI DATA Register 0 (DATA0) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

BCR38: PCI DATA Register 1 (DATA1) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

BCR39: PCI DATA Register 2 (DATA2) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

BCR40: PCI DATA Register 3 (DATA3) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

BCR41: PCI DATA Register 4 (DATA4) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

BCR42: PCI DATA Register 5 (DATA5) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

BCR43: PCI DATA Register 6 (DATA6) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

BCR44: PCI DATA Register 7 (DATA7) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176

BCR45: OnNow Pattern Matching Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

BCR46: OnNow Pattern Matching Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

BCR47: OnNow Pattern Matching Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

BCR48: LED4 Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

BCR49: PHY Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

BCR50-BCR55: Reserved Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

10BASE-T PHY Management Registers (TBRs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

TBR0: 10BASE-T PHY Control Register (Register 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

TBR1: 10BASE-T Status Register (Register 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183

TBR2 and TBR3: 10BASE-T PHY Identifier (Registers 2 and 3). . . . . . . . . . . . . . . . . . . . . . .184

TBR4: 10BASE-T Auto-Negotiation Advertisement Register (Register 4). . . . . . . . . . . . . . . .185

TBR5: 10BASE-T Auto-Negotiation Link Partner Ability Register (Register 5) . . . . . . . . . . . .186

TBR6: 10BASE-T Auto-Negotiation Expansion Register (Register 6) . . . . . . . . . . . . . . . . . . .187

TBR7: 10BASE-T Auto-Negotiation Next Page Register (Register 7) . . . . . . . . . . . . . . . . . . .187

Reserved Registers (Registers 8-15, 18, 20-23, and 25-31) . . . . . . . . . . . . . . . . . . . . . . . . . .187

TBR16: 10BASE-T INTERRUPT Status and Enable Register (Register 16). . . . . . . . . . . . . .188

Am79C978 11

PRELIMINARY

TBR17: 10BASE-T PHY Control/Status Register (Register 17). . . . . . . . . . . . . . . . . . . . . . . .189

TBR19: 10BASE-T PHY Management Extension Register (Register 19) . . . . . . . . . . . . . . . .190

Reserved Register: 10BASE-T Configuration Register (Register 22) . . . . . . . . . . . . . . . . . . .190

Reserved Register: 10BASE-T Carrier Status Register (Register 23). . . . . . . . . . . . . . . . . . .190

TBR24: 10BASE-T Summary Status Register (Register 24) . . . . . . . . . . . . . . . . . . . . . . . . . .190

1 Mbps HomePNA PHY Internal Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

HPR0: HomePNA PHY MII Control (Register 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

HPR1: HomePNA PHY MII Status (Register 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

HPR2 and HPR3: HomePNA PHY MII PHY ID (Registers 2 and 3) . . . . . . . . . . . . . . . . . . . .193

HPR4-HPR7: HomePNA PHY Auto-Negotiation (Registers 4 - 7). . . . . . . . . . . . . . . . . . . . . .193

Reserved Registers: HPR8 - HPR15, HPR17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

HPR16: HomePNA PHY Control (Register 16) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194

HPR18 and HPR19: HomePNA PHY TxCOMM (Registers 18 and 19). . . . . . . . . . . . . . . . . .194

HPR20 and HPR21: HomePNA PHY RxCOMM (Registers 20 and 21) . . . . . . . . . . . . . . . . .195

HPR22: HomePNA PHY AID (Register 22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

HPR23: HomePNA PHY Noise Control (Register 23) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

HPR24: HomePNA PHY Noise Control 2 (Register 24). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

HPR25: HomePNA PHY Noise Statistics (Register 25). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

HPR26: HomePNA PHY Event Status (Register 26). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .197

HPR27: HomePNA PHY Event Status (Register 27). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .197

HPR28: HomePNA PHY ISBI Control (Register 28) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .198

HPR29: HomePNA PHY Tx Control (Register 29). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .198

Initialization Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .199

RLEN and TLEN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .199

RDRA and TDRA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

LADRF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

PADR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

Receive Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .201

RMD0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .202

RMD1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .202

RMD2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

RMD3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204

Transmit Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .204

TMD0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205

TMD1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205

TMD2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206

TMD3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

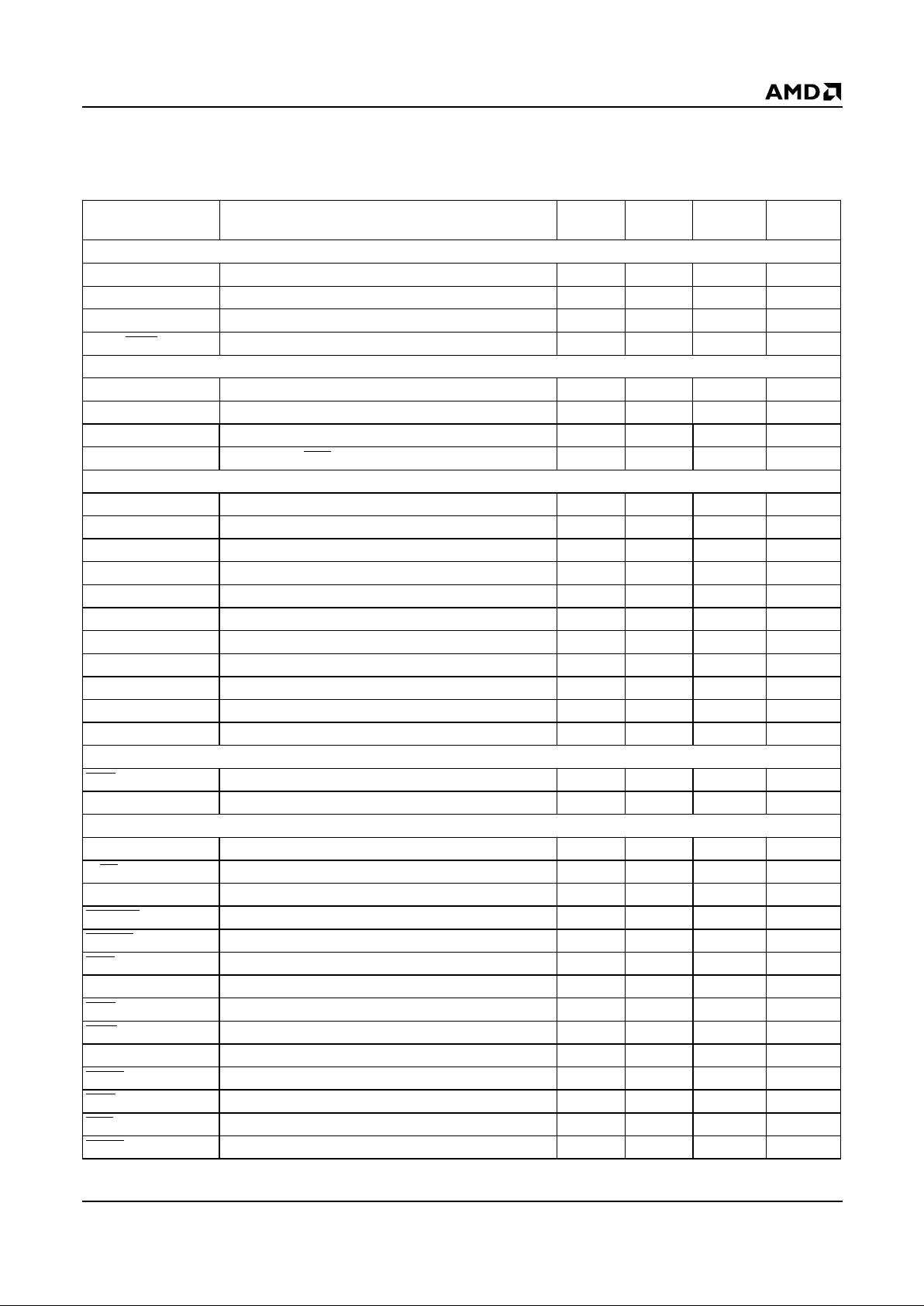

REGISTER SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

PCI Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

Bus Configuration Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

10BASE-T PHY Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214

1 Mbps HomePNA PHY Management Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215

REGISTER PROGRAMMING SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216

Am79C978 Programmable Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

OPERATING RANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

DC CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES . . . . . . . . . . . . . . . . . . . .221

SWITCHING CHARACTERISTICS: BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

Analog I/O - PECL Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

10BASE-T Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

Power Supply Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

External Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

PMD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

PECL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

10BASE-T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .227

SWITCHING CHARACTERISTICS: MEDIA INDEPENDENT INTERFACE. . . . . . . . . . . . . . . . . . .228

12 Am79C978

PRELIMINARY

SWITCHING WAVEFORMS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

Key to Switching Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

SWITCHING TEST CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229

SWITCHING WAVEFORMS: SYSTEM BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .230

SWITCHING WAVEFORMS: MEDIA INDEPENDENT INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . .234

PHYSICAL DIMENSIONS* . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236

PQL144 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .236

PQR160 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237

APPENDIX A - ALTERNATIVE METHOD FOR INITIALIZATION. . . . . . . . . . . . . . . . . . . . . . . . . . A-1

APPENDIX B - LOOK-AHEAD PACKET PROCESSING (LAPP) CONCEPT . . . . . . . . . . . . . . . . B-1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Outline of LAPP Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

LAPP Software Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-5

LAPP Rules for Parsing Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-5

Some Examples of LAPP Descriptor Interaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-6

Buffer Size Tuning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-7

An Alternative LAPP Flow: Two-Interrupt Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-8

LIST OF FIGURES

Figure 1. Media Independent Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 2. Frame Format at the MII Interface Connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 3. Slave Configuration Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 4. Slave Configuration Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 5. Slave Read Using I/O Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 6. Slave Write Using Memory Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 7. Expansion ROM Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 8. Disconnect of Slave Cycle When Busy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 9. Disconnect of Slave Burst Transfer - No Host Wait States. . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 10. Disconnect of Slave Burst Transfer - Host Inserts Wait States. . . . . . . . . . . . . . . . . . . . . 42

Figure 11. Address Parity Error Response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 12. Slave Cycle Data Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 13. Bus Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 14. Non-Burst Read Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 15. Burst Read Transfer (EXTREQ = 0, MEMCMD = 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 16. Non-Burst Write Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 17. Burst Write Transfer (EXTREQ = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 18. Disconnect With Data Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 19. Disconnect Without Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 20. Target Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 21. Preemption During Non-Burst Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 22. Preemption During Burst Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 23. Master Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 24. Master Cycle Data Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 25. Initialization Block Read In Non-Burst Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 26. Initialization Block Read In Burst Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 27. Descriptor Ring Read In Non-Burst Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 28. Descriptor Ring Read In Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 29. Descriptor Ring Write In Non-Burst Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 30. Descriptor Ring Write In Burst Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 31. FIFO Burst Write at Start of Unaligned Buffer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 32. FIFO Burst Write at End of Unaligned Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 33. 16-Bit Software Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 34. 32-Bit Software Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 35. ISO 8802-3 (IEEE/ANSI 802.3) Data Frame. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 36. IEEE 802.3 Frame and Length Field Transmission Order . . . . . . . . . . . . . . . . . . . . . . . . 75

Am79C978 13

PRELIMINARY

Figure 37. 10BASE-T Transmit and Receive Data Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 38. HomePNA PHY Framing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 39. AID Symbol Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 40. AID Symbol Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 41. Transmit Data Symbol Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 42. Receive Symbol Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 43. RLL 25 Coding Tree . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 44. Block Diagram No SRAM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 45. Block Diagram Low Latency Receive Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 46. LED Control Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 47. OnNow Functional Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 48. Pattern Match RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 49. NAND Tree Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 50. NAND Tree Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 51. Address Match Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Figure 52. Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Figure 56. Normal and Tri-State Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Figure 57. CLK Waveform for 5 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Figure 58. CLK Waveform for 3.3 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Figure 59. Input Setup and Hold Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Figure 60. Output Valid Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Figure 61. Output Tri-State Delay Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Figure 62. EEPROM Read Functional Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Figure 63. Automatic PREAD EEPROM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

Figure 64. JTAG (IEEE 1149.1) TCK Waveform for 5 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . . 232

Figure 65. JTAG (IEEE 1149.1) Test Signal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Figure 66. Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Figure 67. Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Figure 68. MDC Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Figure 69. Management Data Setup and Hold Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

Figure 70. Management Data Output Valid Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

Figure B-1. LAPP Timeline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-4

Figure B-2. LAPP 3 Buffer Grouping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-5

Figure B-3. LAPP Timeline for Two-Interrupt Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-9

Figure B-4. LAPP 3 Buffer Grouping for Two-Interrupt Methods . . . . . . . . . . . . . . . . . . . . . . . . . . .B-10

LIST OF TABLES

Table 1. Interrupt Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 2. External Clock/Crystal Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 3. PCI Device ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 4. PCI Software Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 5. Slave Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 6. Slave Configuration Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 7. Master Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 8. Descriptor Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 9. Descriptor Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 10. Receive Address Match. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74