Page 1

PRELIMINARY

Am79C976

PCnet-PRO™

10/100 Mbps PCI Ethernet Controller

DISTINCTIVE CHARACTERISTICS

■ Integrated Fast Ethernet controller for the

Peripheral Component Interconnect (PCI) bus

— 32-bit gluele ss PCI hos t interf ace

— Supports PCI clock frequency from DC to

33 MHz independent of network clock

— Supports network operation with PCI clock

from 15 MHz to 33 MHz

— High performance bus mastering

architecture with integrated Direct Memory

Access (DMA) Buffer Management Unit for

low CPU and bus utilization

— PCI specification revision 2.2 compliant

— Supports PCI Subsystem/Subvendor

ID/Vendor ID programming through the

EEPROM interface

— Supports both PCI 3.3-V and 5.0-V signaling

environments

— Plug and Play compatible

— Uses advanced PCI commands (MWI, MRL,

MRM)

— Optionally supports PCI bursts aligned to

cache line boundaries

— Supports big endian and little endian byte

alignments

— Implements optional PCI power management

event (PME

— Supports 40-bit addressing (using PCI Dual

Address Cycles)

■ Media Independent Interface (MII) for

connecting external 10/100 megabit per second

(Mbps) transceivers

— IEEE 802.3-compliant MII

— Intelligent Auto-Poll™ external PHY status

monitor and interrupt

— Supports both auto-negotiable and non auto-

negotiable external PHYs

— Supports 10BASE-T, 100BASE-TX/FX,

100BASE-T4, and 100BASE-T2 IEEE 802.3compliant MII PHYs at full- or half-duplex

) pin

■ Full-duplex operation supported with

independent Transmit (TX) and Receive (RX)

channels

■ Includes support for IEEE 802.1Q VLANs

— Automatically inserts, deletes, or modifies

VLAN tag

— Optionally filters untagged frames

■ Provides optional flow control features

— Recognizes and transmits IEEE 802.3x MAC

flow control frames

— Asserts collision-based back pressure in

half-duplex mode

■ Provides internal Management Information

Base (MIB) counters for net work statistics

■ Supports PC97, PC98, PC99, and Net PC

requirements

— Implements full OnNow features including

pattern matching and link status wake-up

— Implements Magic Packet™ mode

— Magic Packet mode and the physical address

loaded from EEPROM at power up without

requiring PCI clock

— Supports PCI Bus Power Management

Interface Specification Version 1.1

— Supports Advanced Configuration and

Power Interface (ACPI) Specification Version

1.0

— Supports Network Device Class Power

Management Specification Version 1.0

■ Large independent external TX and RX FIFOs

— Supports up to 4 megabytes (Mbytes)

external SSRAM for RX and TX frame storage

— Programmable FIFO watermarks for both

transmit and receive operations

— Receive frame queuing for high latency PCI

bus host operation

— Programmable allocation of buffer space

between transmit and receive queues

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you ev aluate this pr oduct. AMD reserves the right to chang e or discontinu e work on this proposed

product without notice.

Refer to AMD’s Website (www.amd.com) for the latest information.

Publication# 22929 Rev: C Amendment/0

Issue Date: August 2000

Page 2

PRELIMINARY

■ Dual-speed CSMA/CD (10 Mbps and 100 Mbps)

Media Access Controller (MAC) compliant with

IEEE/ANSI 802.3 and Blue Book Ethernet

standards

■ Programmable internal/external loopback

capabilities

■ Supports patented External Address Detection

Interface (EADI) with receive frame tagging

support for internetworking applications

■ EEPROM interface supports jumperless design

and provides through-chip programming

— Supports full programmability of all internal

registers through EEPROM mapping

■ Programmable PHY rese t output pin capab le of

resetting external PHY without needing

buffering

■ Integrated oscillator circuit is controlled by

external crystal

■ Extensive programmable LED status support

■ Supports up to 16 Mbyte optional Boot PR OM or

Flash for diskless node application

■ Look-Ahead Packet Processing (LAPP) data

handling technique reduces system overhead

by allowing protocol analysis to begin before

the end of a receive frame

■ Optional delayed interrupt feature reduces CPU

overhead

■ Programmable Inter Packet Gap (IPG) to

address less aggressive network MAC

controllers

■ Offers the Modified Back-Off algorithm to

address the Ethernet Capture Effect

■ Optionally sends and receives non-standard

frames of up to 64K octets in length

■ IEEE 1149.1-compliant JTAG Boundary Scan

test access port interface for board-level

production connectivity test

■ Provides built-in self test (MBIST) for the

external SSRAM

■ Software compatible with AMD PCnet Family

and LANCE/C-LANCE register and descriptor

architecture

■ Compatible with the existing PCnet Family

driver and diagnostic software (except for

statistics)

■ Available in 208-pin PQFP package

■ +3.3-V power supply with 5 -V tolerant I/Os

enables broad system compatibility

■ Support for operation in Industrial temperature

range (-40° C to +85

C) available.

2 Am79C976 8/01/00

Page 3

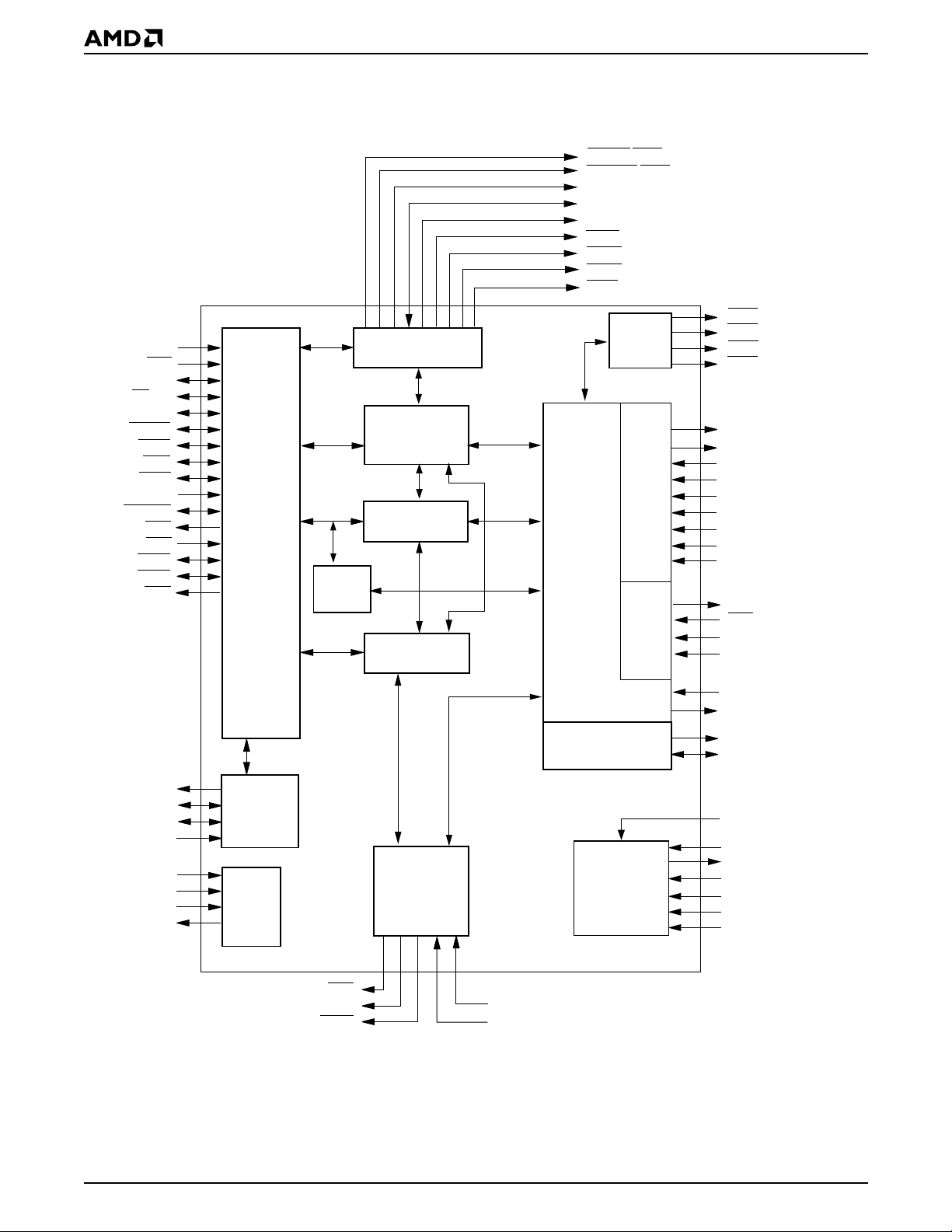

GENERAL DESCRIPTION

PRELIMINARY

The Am79C976 controll er is a highly-integrated 32- bit

full-duplex, 10/100-Mega bit per second (Mbp s) Ethernet controller solution, designed to address highperformance system application requirements. It is a

flexible bus mastering device that ca n be used in any

application, including network-ready PCs and bridge/

router designs. The bus master architecture provides

high data throughput and low CPU and system bus utilization. The Am79C976 controller is fabricated with

advanced low-power 3.3-V CMO S process to provid e

low operating current for power sensitive applications.

The Am79C976 controller also has several enhancements over its predecessor, the Am79C971

PCnet-FAST d evice. In addi tion t o providing acc ess t o

a larger SSRAM, it fur ther reduc es system impleme ntation cost by the addition of a new EEPROM programmable pin (PHY_RST) and the integration of the PAL

function needed for Magic Packet application. The

PHY_RST pin is i mplemented to reset the external

PHY without increasing the load to the PCI bus an d to

block RST

The 32-bit multiplexed bus interface unit provides a d irect interface to the P CI local bus, simplif ying the design of an Ethernet node in a PC system. The

Am79C976 co ntroller provides the complet e interface

to an Expansion ROM or Flash device allowing add-on

card designs with onl y a single lo ad per PCI bus interface pin. With its built-in suppor t for both little and big

endian byte alignment, this controller also addresses

non-PC applications. The A m79C976 controller’s

advanced CMOS design allows the bus interface to be

connected to eithe r a +5-V o r a +3.3-V signalin g environment. An IEEE 1149.1-compliant JTAG test interface for board-level testing is also provided.

The Am79C976 controller is also compliant with the

PC97, PC98, PC99, and Network PC (Net PC) specifications. It includes the full implementation of the Microsoft OnNow and ACPI specifications, which are

backward compatible with the Magic Packet technology, and it is com pliant with the PCI Bus Power Management Interface Specifica tio n by sup porting the four

power management states ( D0, D1, D2, and D3), th e

optional PME

data registers.

The Am79C976 control ler is ideal ly suited for Net PC,

motherboard, net work interface card (N IC), and embedded designs. It is available in a 208-pin Plastic

Quad Flat Pack (PQFP) package.

to the PHY when PG input is LOW.

pin, and the necessary configuration and

The Am79C976 controller contains a bus interface unit,

a DMA Buffer Management Unit, an ISO/IEC 8802-3

(IEEE 802.3)-compliant Media Access Controller

(MAC), and an IEEE 802.3-compliant MI I. An inter face

to an external RAM of up to 4 Mbytes is provided for

frame storage. The MII supports IEEE 802.3-compliant

full-duplex and half-duplex operations at 10 Mbps or

100 Mbps. The MII TX an d RX clock signals can be

stopped independently for home networking applications.

The Am79C976 controller is register compatible with

the LANCE™ (Am7990) and C-LANCE™ (Am79C 90)

Ethernet c on tro ll ers, and al l Et hernet contro ll er s in th e

PCnet Family except ILACC™ (Am79C900), including

the PCnet™-ISA controller (Am79C960),

PCnet™-ISA+ (Am79C961), PCnet™-ISA II

(Am79C961A), P Cnet™-32 (Am79C965) , PCnet™PCI (Am79C970), PCn et™-PCI II (Am79C970A) , and

the PCnet™-FAST (Am79C971).

The Buffer Management Unit supports the LANCE and

PCnet descriptor software models.

The Am79C976 controll er suppor ts au to-configuratio n

in the PCI configu ration space. Additional Am79C976

controller configuration parameters, including the

unique IEEE physical address, can be read from an external nonvolatile memory (EEPROM) immediately following system reset.

In addition, the device provides programmable on-chip

LED drivers f or tr ansmit, re ceiv e, coll ision, lin k integrit y,

Magic Packet status, activit y, addres s match, fullduplex, or 100 Mbps status. The Am 79C9 76 c on tro ller

also provides an EADI to al low external hardware address filtering in interne tworking applications and a

receive frame tagging feature.

With the rise of embedded networking applications operating in harsh environments where temperatures

may exceed the normal commercial temperature (0

C) window, an industrial temperature (-40 C to

to +70

C) version is available. This industrial temperature

+85

version of the PCnet-PRO Ethernet co ntroller is characterized across the industrial temperature range (-40

C to +85 C) within the published power supply specification (4.75V to 5.25V;

of the PCnet-PRO performance over this temperature

range is guaranteed by a design and character i zatio n

monitor.

±5% Vcc). Thus, conformance

C

8/01/00 Am79C976 3

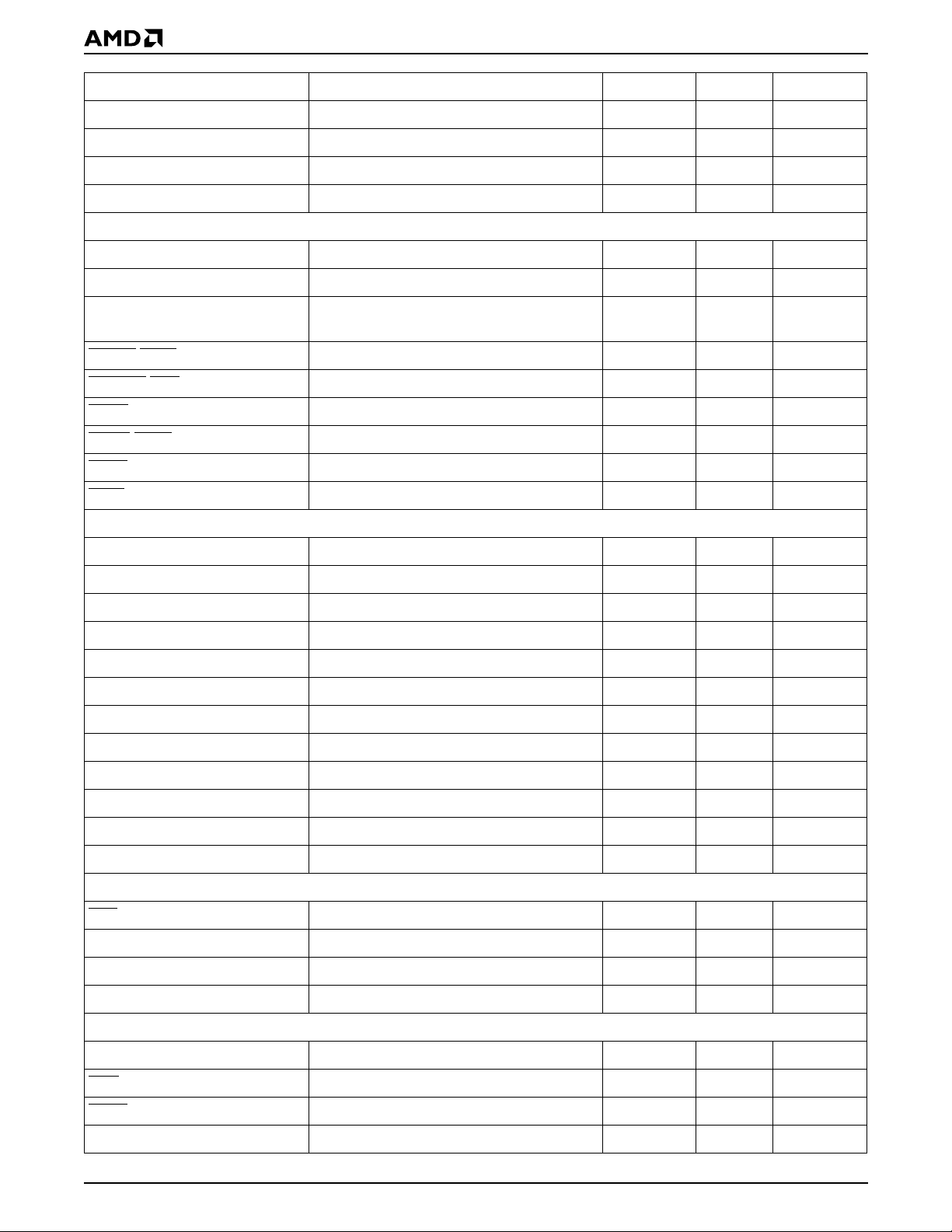

Page 4

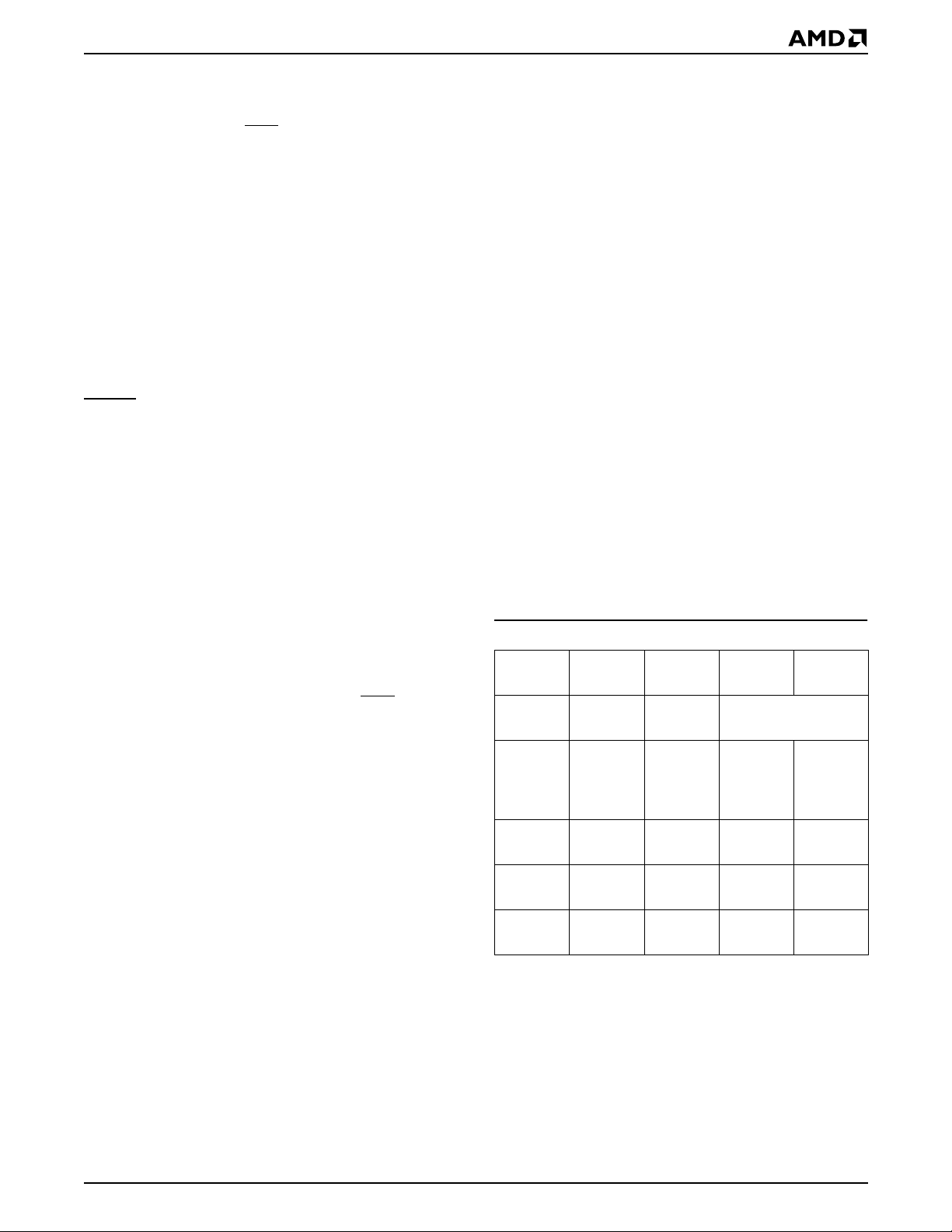

BLOCK DIAGRAM

CLK

RST

AD[31:0]

C/BE[3:0]

PAR

FRAME

TRDY

IRDY

STOP

IDSEL

DEVSEL

REQ

GNT

PERR

SERR

INTA

PCI Bus

Interface

Unit

MIB

Counters

PRELIMINARY

Expansion Bus

Interface

Memory Control

Unit

Register Control

and Status Unit

Descriptor

Management Unit

ERADV/FLOE

ERADSP/ICEN

ERCLK

ERD[31:0]/FLD[7:0]/FLA[23.20]

ERA[19:0]/FLA[19:0]

ERCE

EROE

ERWE

FLCS

LED

Control

802.3

MAC

Core

MII

Port

EADI

Port

LED0

LED1

LED2

LED3

TXD[3:0]

TX_EN

TX_CLK

COL

RXD[3:0]

RX_ER

RX_CLK

RX_DV

CRS

SFBD

EAR

RXFRTGD

RXFRTGE

EECS

EESK

EEDI

EEDO

TCK

TMS

TDI

TDO

93CXX

EEPROM

Interface

JTAG

Port

Control

PME

RWU

WUMI

OnNow

Power

Management

Unit

PG

VAUX_SENSE

Network Port

Manager

Clock

Generator

FC

PHY_RST

MDC

MDIO

TEST

XTAL1

XTAL2

XCLK

CLKSEL0

CLKSEL1

CLKSEL2

22929B1

4 Am79C976 8/01/00

Page 5

PRELIMINARY

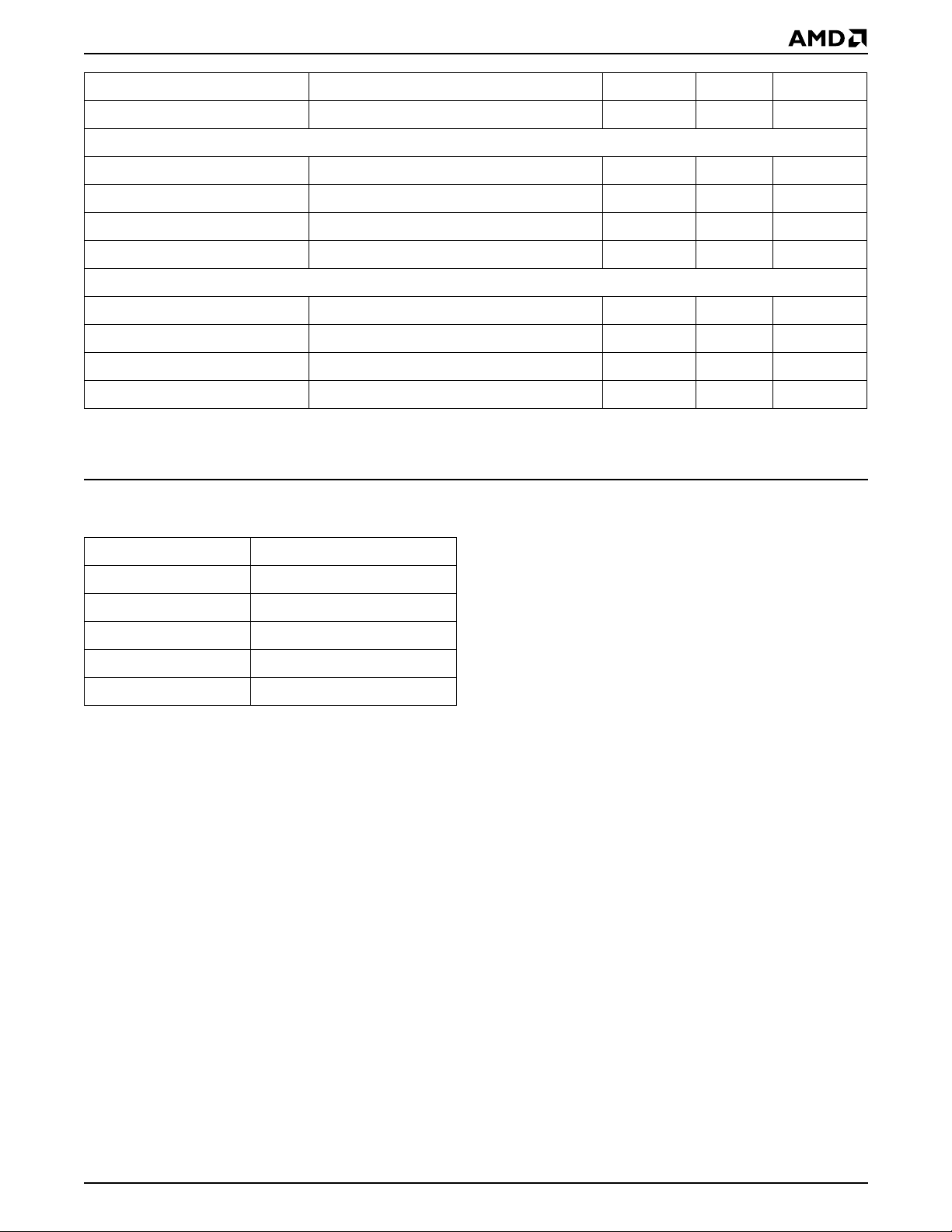

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

BLOCK DIAGRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

TABLE OF CONTENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

LIST OF FIGURES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

LIST OF TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

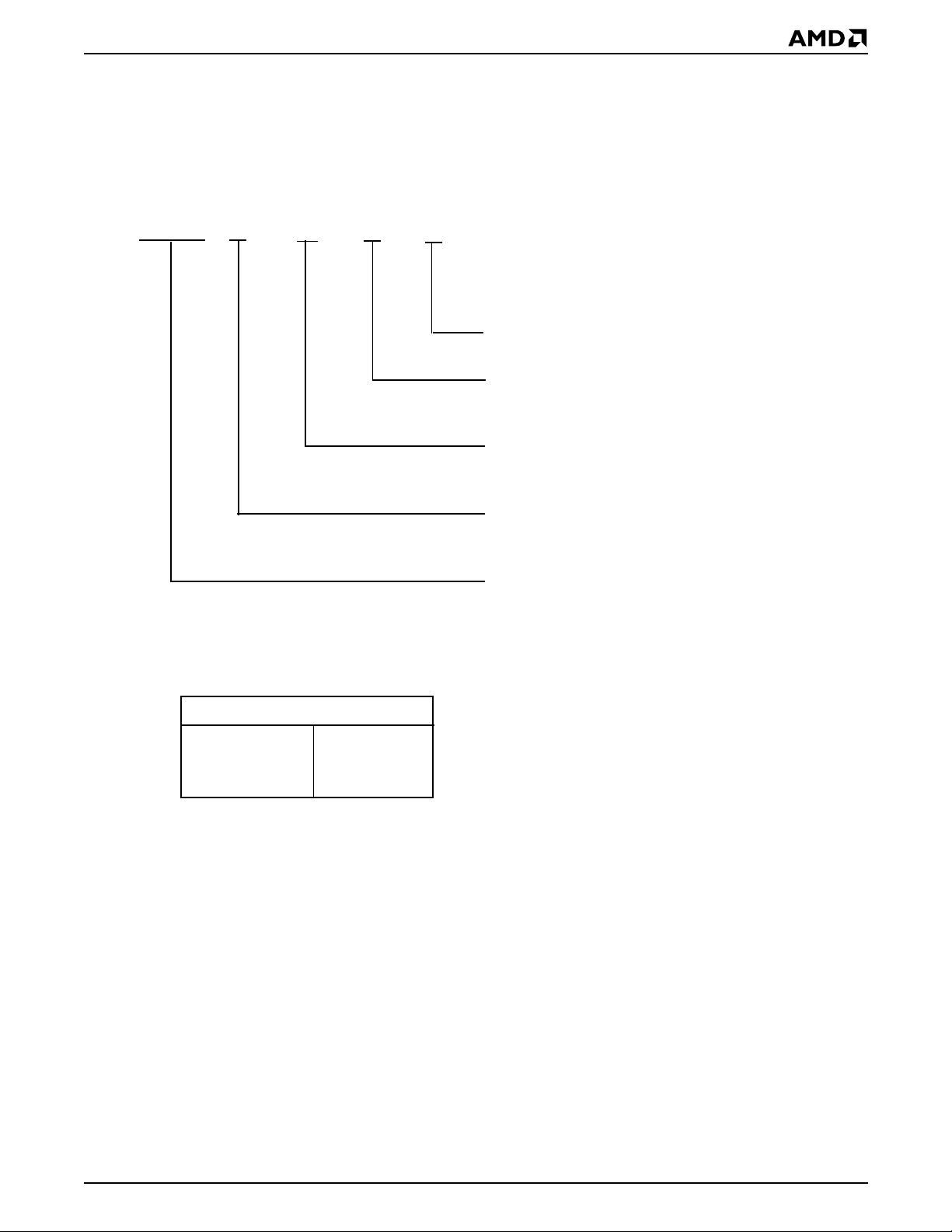

ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Standard Products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

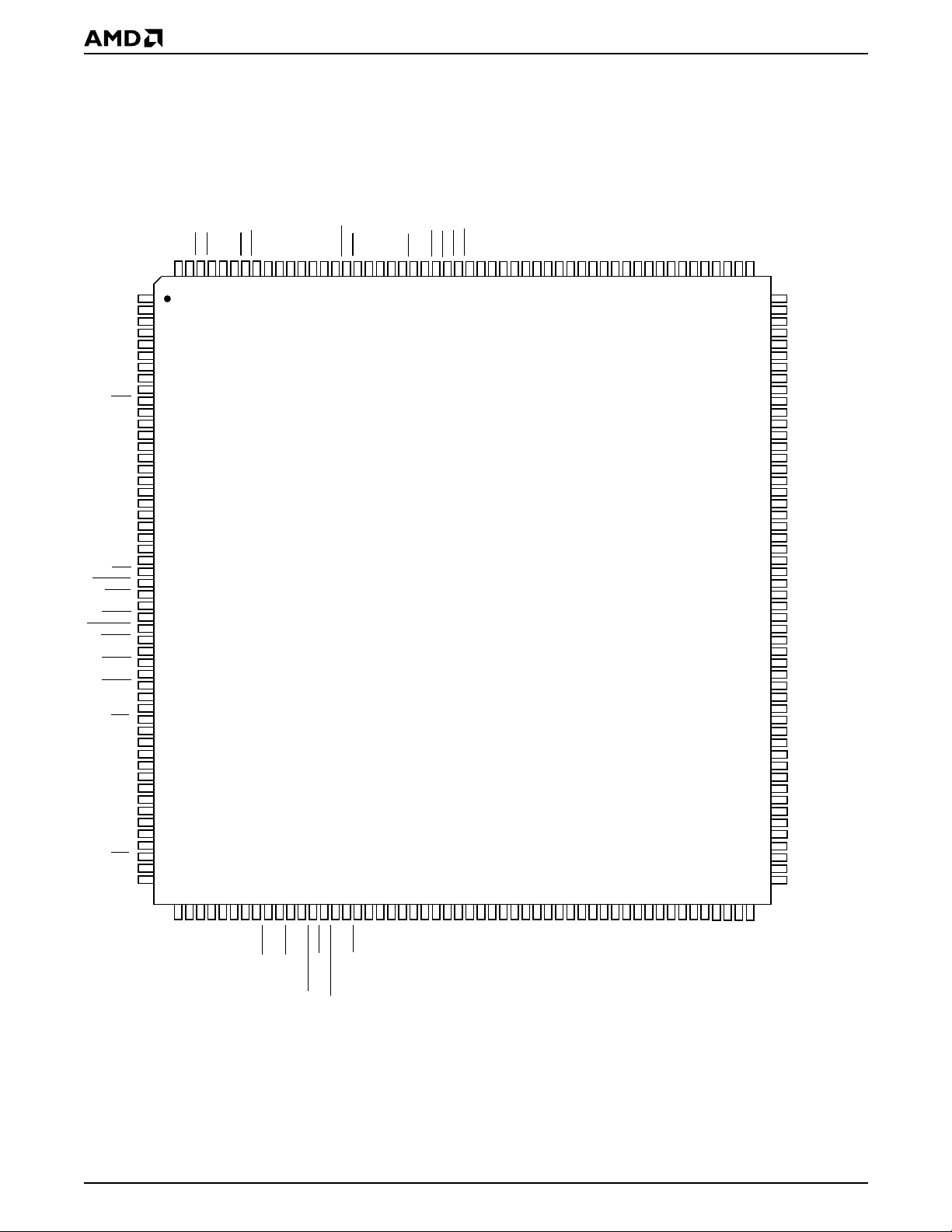

CONNECTION DIAGRAM (PQR208) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

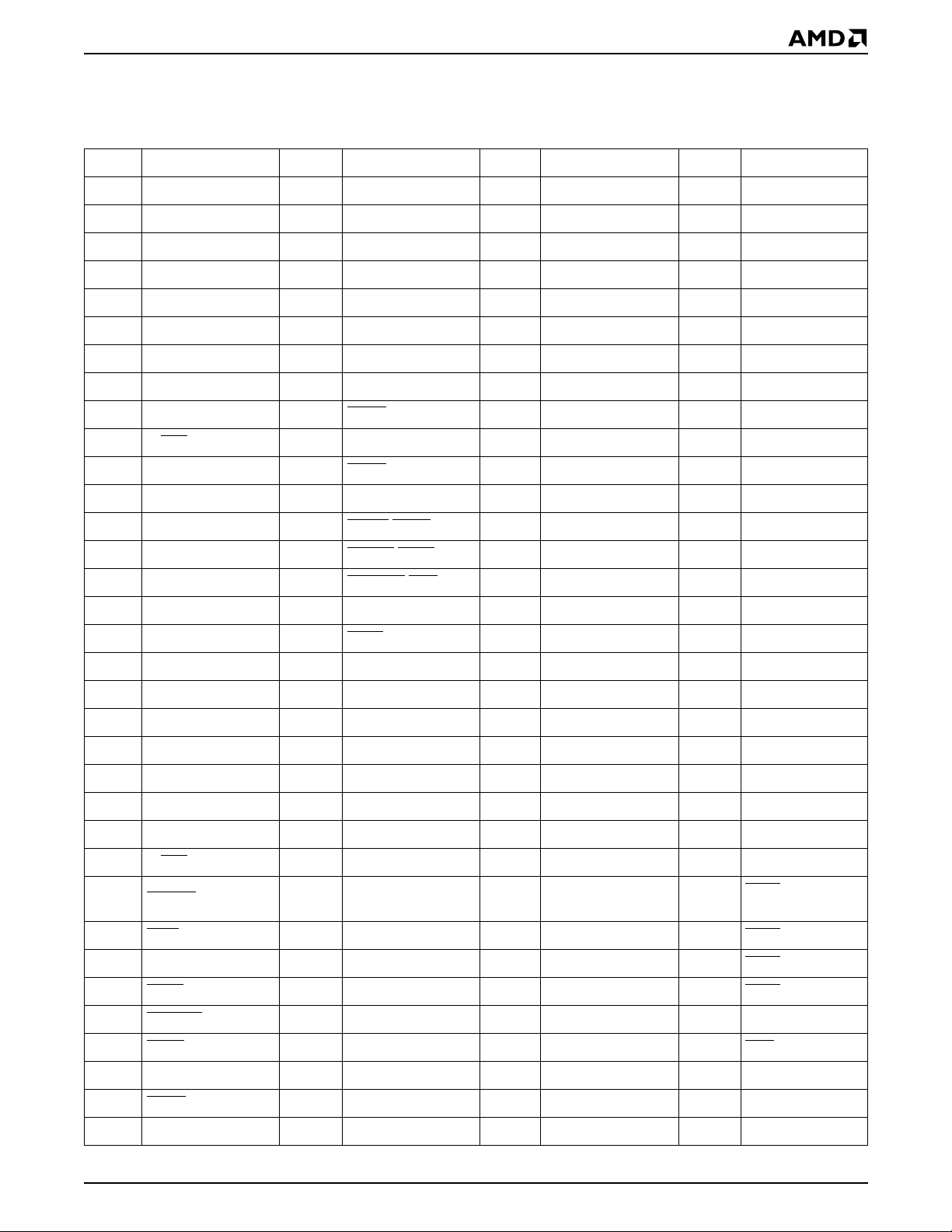

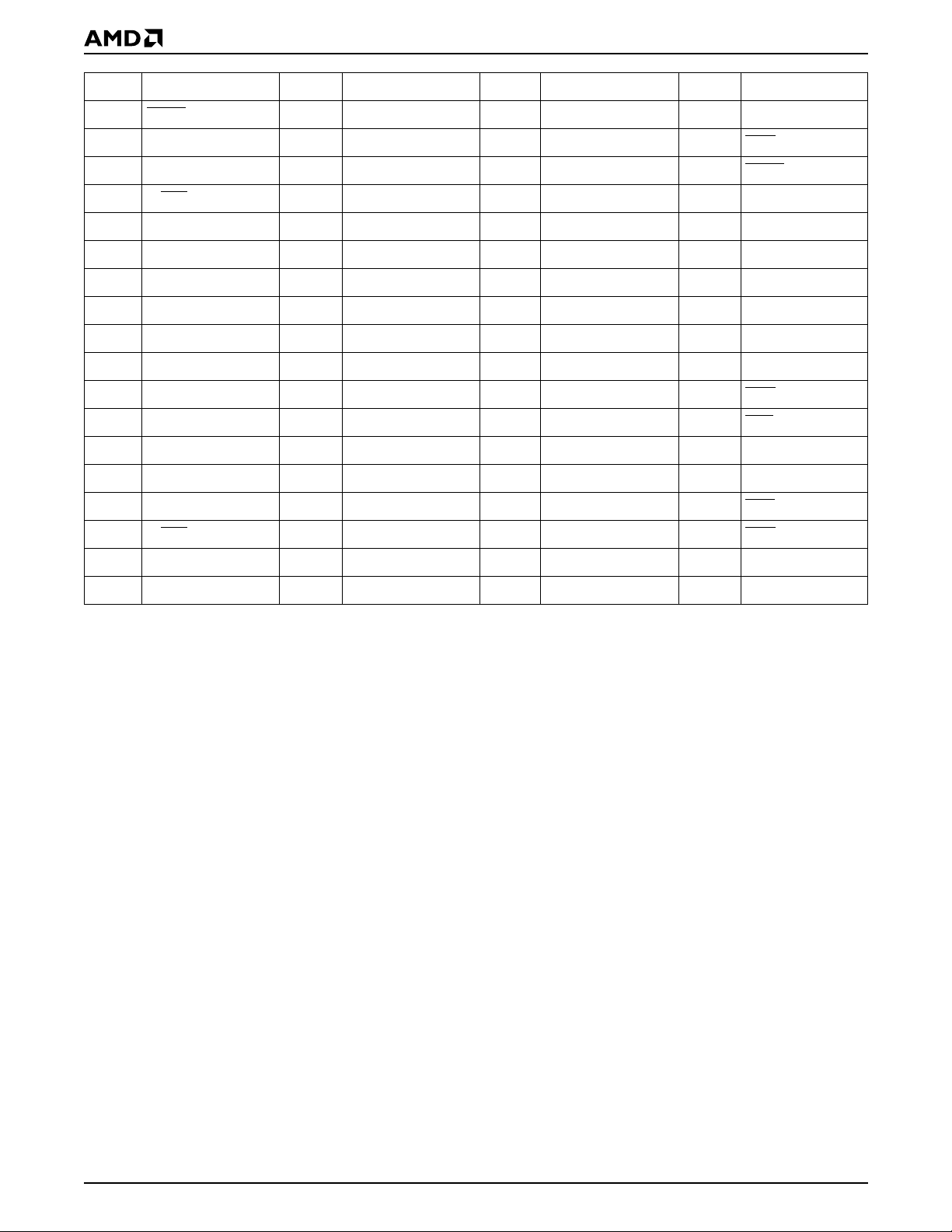

PIN DESIGNATIONS (PQR208) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Listed By Pin Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Listed By Group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Board Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

External Memory Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Media Independent Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

External Address Detection Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

IEEE 1149.1 (1990) Test Access Port Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Power Supply Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

BASIC FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

System Bus Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Software Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Network Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

DETAILED FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Slave Bus Interface Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Slave Configuration Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Slave I/O Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Expansion ROM Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Slave Cycle Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Disconnect When Busy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Disconnect Of Burst Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Parity Error Response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Master Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Bus Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Bus Master DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Basic Non-Burst Read Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Basic Burst Read Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Basic Non-Burst Write Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Basic Burst Write Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

DMA Burst Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Target Initiated Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Disconnect With Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Disconnect Without Data Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Target Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Master Initiated Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Preemption During Non-Burst Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Preemption During Burst Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Master Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Parity Error Response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Initialization Block DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Descriptor DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

FIFO DMA Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Descriptor Management Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

8/01/00 Am79C976 5

Page 6

PRELIMINARY

Re-Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Run and Suspend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Descriptor Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Descriptor Rings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Polling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Transmit Polling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Receive Polling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Look Ahead Packet Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Software Interrupt Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Media Access Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Transmit and Receive Message Data Encapsulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

Framing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Destination Address Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Error Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Media Access Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Medium Allocation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Signal Quality Error (SQE) Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Collision Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Transmit Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Transmit Function Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Automatic Pad Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Transmit FCS Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Transmit Error Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Loss of Carrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Late Collision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Transmit FIFO Underflow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Receive Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Receive Function Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Address Matching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Automatic Pad Stripping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Receive FCS Checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Receive Exception Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Statistics Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Receive Statistics Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Transmit Statistics Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

VLAN Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

VLAN Frame Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Admit Only VLAN Frames Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

VLAN Tags in Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Loopback Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Miscellaneous Loopback Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80

Full-Duplex Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Full-Duplex Link Status LED Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

Media Independent Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

MII Transmit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

MII Receive Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

MII Network Status Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

MII Management Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

MII Management Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

Host CPU Access to External PHY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Auto-Poll State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

Network Port Manager . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Auto-Negotiation With Multiple PHY Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Operation Without MMI Management Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

Regulating Network Traffic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

MAC Control Pause Frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Back Pressure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

6 Am79C976 8/01/00

Page 7

PRELIMINARY

Enabling Traffic Regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Hardware Control of Traffic Regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

Software Control of Traffic Regulation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

Programming the Pause Length Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

PAUSE Frame Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Delayed Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

External Address Detection Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

External Address Detection Interface: Receive Frame Tagging . . . . . . . . . . . . . . . . . . . . . . . . . .91

External Memory Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Expansion ROM - Boot Device Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

Direct Flash Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

Flash/EPROM Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

SRAM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Automatic EEPROM Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

EEPROM Auto-Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Direct Access to the Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

EEPROM CRC Calculation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

LED Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

Power Savings Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

Power Management Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

OnNow Wake-Up Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

RWU Wake-Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

Link Change Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

Magic Packet Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

OnNow Pattern Match Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

Pattern Match RAM (PMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

IEEE 1149.1 (1990) Test Access Port Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

Boundary Scan Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

TAP Finite State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Supported Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

Other Data Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

H_RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

EE_RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

S_RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

STOP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

Power on Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

External PHY Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

Software Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

I/O Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

I/O Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Address PROM Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Reset Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

Word I/O Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Double Word I/O Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

USER ACCESSIBLE REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Vendor ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

PCI Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

PCI Revision ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

PCI Programming Interface Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

PCI Sub-Class Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

PCI Base-Class Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

8/01/00 Am79C976 7

Page 8

PRELIMINARY

PCI Cache Line Size Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

PCI Latency Timer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

PCI Header Type Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

PCI I/O Base Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

PCI Memory Mapped I/O Base Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

PCI Subsystem Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

PCI Subsystem ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

PCI Expansion ROM Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

PCI Capabilities Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

PCI Interrupt Line Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

PCI Interrupt Pin Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

PCI MIN_GNT Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

PCI MAX_LAT Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

PCI Capability Identifier Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

PCI Next Item Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

PCI Power Management Capabilities Register (PMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

PCI Power Management Control/Status Register (PMCSR). . . . . . . . . . . . . . . . . . . . . . . . . . . .120

PCI PMCSR Bridge Support Extensions Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

PCI Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

Memory-Mapped Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

MIB Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

AP_VALUE0: Auto-Poll Value0 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

AP_VALUE1: Auto-Poll Value1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

AP_VALUE2: Auto-Poll Value2 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

AP_VALUE3: Auto-Poll Value3 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

AP_VALUE4: Auto-Poll Value4 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

AP_VALUE5: Auto-Poll Value5 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

AUTOPOLL0: Auto-Poll0 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

AUTOPOLL1: Auto-Poll1 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

AUTOPOLL2: Auto-Poll2 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

AUTOPOLL3: Auto-Poll3 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

AUTOPOLL4: Auto-Poll4 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

AUTOPOLL5: Auto-Poll5 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

BADR: Receive Ring Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

BADX: Transmit Ring Base Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

CHIPID: Chip ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

CHPOLLTIME: Chain Poll Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

CMD0: Command0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

CMD2: Command2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131

CMD3: Command3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

CMD7: Command7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

CTRL0: Control0 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

CTRL1: Control1 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

CTRL2: Control2 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

CTRL3: Control3 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

DATAMBIST: Memory Built-in Self-Test Access Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

DELAYED_INT: Delayed Interrupts Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

EEPROM_ACC: EEPROM Access Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

FLASH_ADDR: Flash Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

FLASH_DATA: Flash Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

FLOW: Flow Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

IFS1: Inter-Frame Spacing Part 1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

INT0: Interrupt0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153

INTEN0: Interrupt0 Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

IPG: Inter-Packet Gap Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

LADRF: Logical Address Filter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

LED0 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

LED1 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

8 Am79C976 8/01/00

Page 9

PRELIMINARY

LED2 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

LED3 Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

MAX_LAT_A: PCI Maximum Latency Alias Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .160

MIN_GNT_A: PCI Minimum Grant Alias Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .160

PADR: Physical Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Pause Count Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

PCIDATA0: PCI DATA Register Zero Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

PCIDATA1: PCI DATA Register One Alias Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

PCIDATA2: PCI DATA Register Two Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

PCIDATA3: PCI DATA Register Three Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

PCIDATA4: PCI DATA Register Four Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

PCIDATA5: PCI DATA Register Five Alias Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

PCIDATA6: PCI DATA Register Six Alias Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

PCIDATA7: PCI DATA Register Seven Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

PHY Access Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163

PMAT0: OnNow Pattern Register 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

PMAT1: OnNow Pattern Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

PMC_A: PCI Power Management Capabilities Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Receive Protect Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .165

RCV_RING_LEN: Receive Ring Length Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

ROM_CFG: ROM Base Address Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

SID_A: PCI Subsystem ID Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166

SRAM Boundary Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

SRAM Size Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

STAT0: Status0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168

Software Timer Value Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .169

SVID_A: PCI Subsystem Vendor ID Alias Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

VID_A: PCI Vendor ID Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

XMT_RING_LEN: Transmit Ring Length Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

XMTPOLLTIME: Transmit Poll Timer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171

RAP Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

RAP: Register Address Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172

Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

CSR0: Am79C976 Controller Status and Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

CSR1: Initialization Block Address 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

CSR2: Initialization Block Address 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

CSR3: Interrupt Masks and Deferral Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

CSR4: Test and Features Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

CSR5: Extended Control and Interrupt 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

CSR6: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

CSR7: Extended Control and Interrupt 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

CSR8: Logical Address Filter 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

CSR9: Logical Address Filter 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

CSR10: Logical Address Filter 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

CSR11: Logical Address Filter 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

CSR12: Physical Address Register 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184

CSR13: Physical Address Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

CSR14: Physical Address Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

CSR15: Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

CSR16-23: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

CSR24: Base Address of Receive Ring Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

CSR25: Base Address of Receive Ring Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

CSR26-29: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

CSR30: Base Address of Transmit Ring Lower. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

CSR31: Base Address of Transmit Ring Upper. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

CSR32-46: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .188

CSR47: Transmit Polling Interval. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .188

CSR48: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .188

8/01/00 Am79C976 9

Page 10

PRELIMINARY

CSR49: Chain Polling Interval. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .188

CSR50-57: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

CSR58: Software Style . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189

CSR59-75: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

CSR76: Receive Ring Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

CSR77: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

CSR78: Transmit Ring Length. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

CSR79: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191

CSR80: DMA Transfer Counter and FIFO Threshold Control . . . . . . . . . . . . . . . . . . . . . . . . . . .191

CSR81-87: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR88: Chip ID Register Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR89: Chip ID Register Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR90-99: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR100: Bus Timeout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR101-111: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR112: Missed Frame Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR113: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR114: Receive Collision Count. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR115: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193

CSR116: OnNow Power Mode Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .194

CSR117-121: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

CSR122: Advanced Feature Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

CSR123: Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195

CSR124: Test Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

CSR125: MAC Enhanced Configuration Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196

Bus Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

BCR0: Master Mode Read Active . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .198

BCR1: Master Mode Write Active . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .198

BCR2: Miscellaneous Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .199

BCR4: LED0 Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .199

BCR5: LED1 Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .201

BCR6: LED2 Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .203

BCR7: LED3 Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205

BCR9: Full-Duplex Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

BCR16: I/O Base Address Lower . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

BCR17: I/O Base Address Upper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

BCR18: Burst and Bus Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208

BCR19: EEPROM Control and Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209

BCR20: Software Style . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212

BCR22: PCI Latency Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214

BCR23: PCI Subsystem Vendor ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

BCR24: PCI Subsystem ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215

BCR25: SRAM Size Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215

BCR26: SRAM Boundary Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215

BCR27: SRAM Interface Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216

BCR28: Expansion Bus Port Address Lower (Used for Flash/EPROM and SRAM Accesses). .216

BCR29: Expansion Port Address Upper (Used for Flash/EPROM Accesses) . . . . . . . . . . . . . .216

BCR30: Expansion Bus Data Port Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

BCR31: Software Timer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

BCR32: MII Control and Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217

BCR33: MII Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .219

BCR34: MII Management Data Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .220

BCR35: PCI Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

BCR36: PCI Power Management Capabilities (PMC) Alias Register . . . . . . . . . . . . . . . . . . . . .220

BCR37: PCI DATA Register Zero (DATA0) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

BCR38: PCI DATA Register One (DATA1) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

BCR39: PCI DATA Register Two (DATA2) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221

BCR40: PCI DATA Register Three (DATA3) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

10 Am79C976 8/01/00

Page 11

PRELIMINARY

BCR41: PCI DATA Register Four (DATA4) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .222

BCR42: PCI DATA Register Five (DATA5) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .222

BCR43: PCI DATA Register Six (DATA6) Alias Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

BCR44: PCI DATA Register Seven (DATA7) Alias Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

BCR45: OnNow Pattern Matching Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

BCR46: OnNow Pattern Matching Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224

BCR47: OnNow Pattern Matching Register 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224

Initialization Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

RLEN and TLEN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .225

RDRA and TDRA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

LADRF. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

PADR. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

Receive Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Transmit Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .238

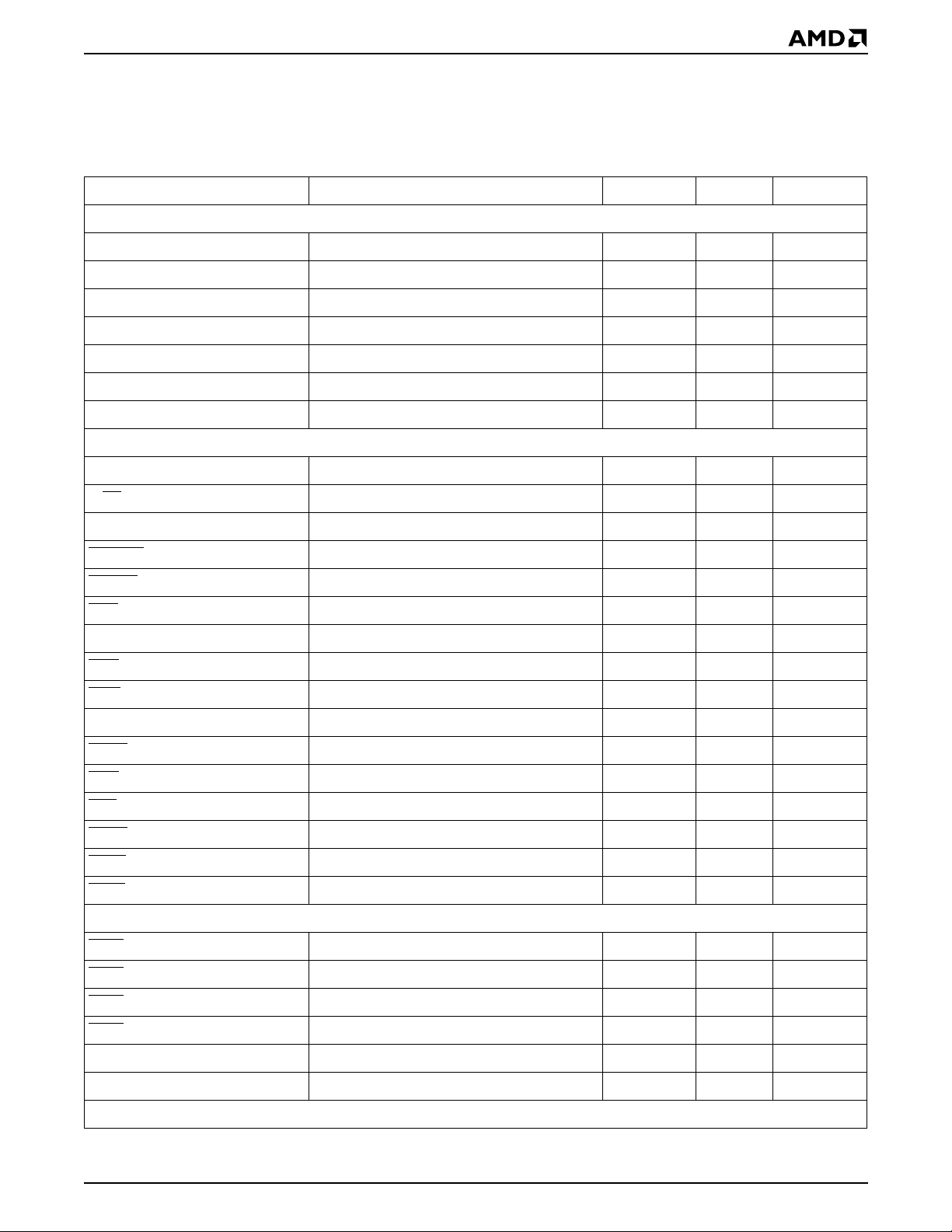

REGISTER SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .245

PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .245

Memory-Mapped Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Control and Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .248

Bus Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

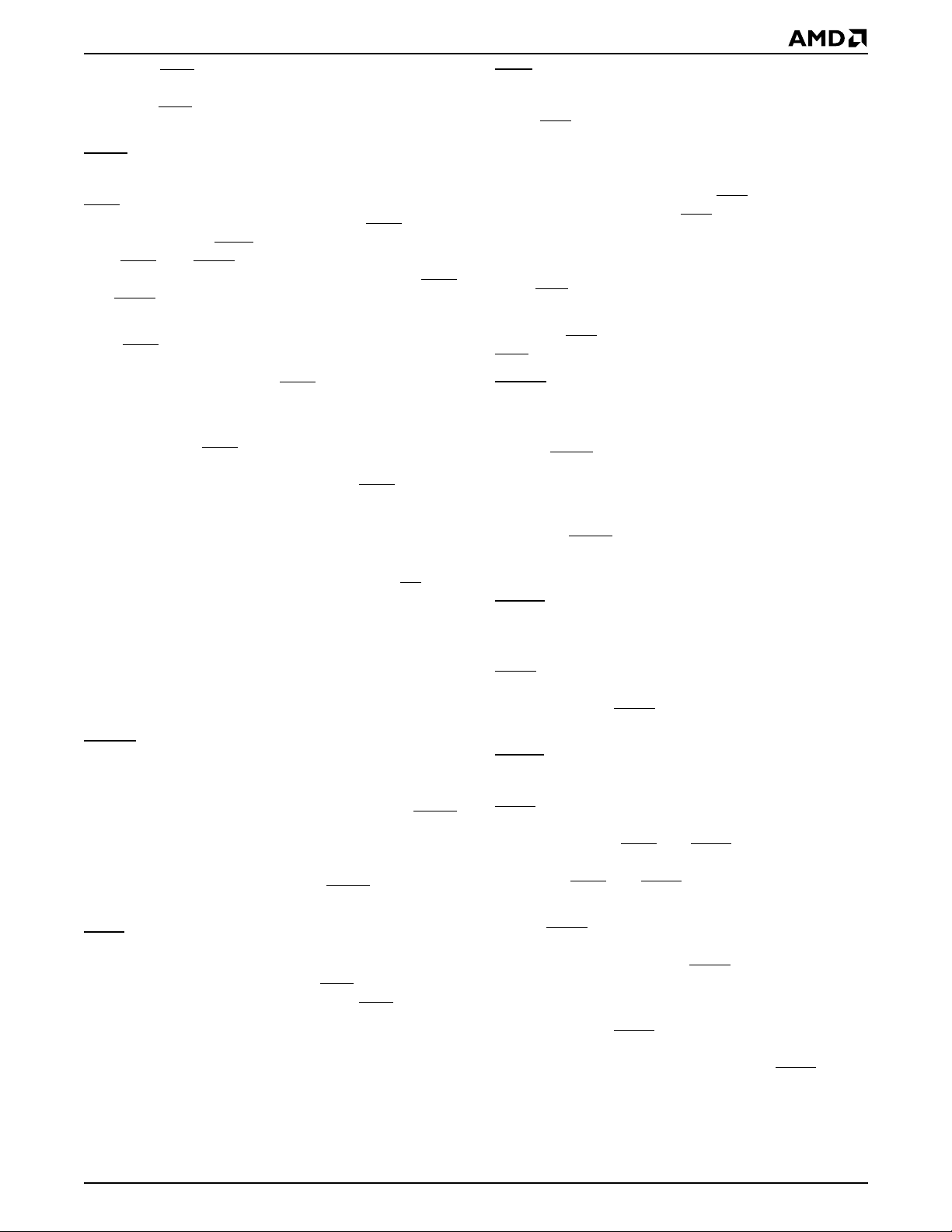

REGISTER BIT CROSS REFERENCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .253

REGISTER PROGRAMMING SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .262

Programmable Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .266

OPERATING RANGES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .266

DC CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES . . . . . . . . . . . . . . . . . . . . . . . 267

SWITCHING CHARACTERISTICS: BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .269

SWITCHING WAVEFORMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

Key to Switching Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .270

SWITCHING TEST CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .271

SWITCHING WAVEFORMS: SYSTEM BUS INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .272

SWITCHING CHARACTERISTICS: EEPROM INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .274

SWITCHING CHARACTERISTICS: JTAG TIMING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .276

SWITCHING CHARACTERISTICS: MEDIA INDEPENDENT INTERFACE . . . . . . . . . . . . . . . . . . . . . . 278

SWITCHING CHARACTERISTICS: EXTERNAL ADDRESS DETECTION INTERFACE . . . . . . . . . . .281

SWITCHING WAVEFORMS: RECEIVE FRAME TAG. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

SWITCHING WAVEFORMS: EXTERNAL MEMORY INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

PHYSICAL DIMENSIONS* . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .285

PQFP208. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

Plastic Quad Flat Pack Trimmed and Formed. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .285

APPENDIX A: LOOK-AHEAD PACKET PROCESSING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Outline of LAPP Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

Flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

LAPP Software Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

LAPP Rules for Parsing Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Some Examples of LAPP Descriptor Interaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

Buffer Size Tuning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

An Alternative LAPP Flow: Two-Interrupt Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

APPENDIX B: MII MANAGEMENT REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Control Register (Register 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Status Register (Register 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-2

Auto-Negotiation Advertisement Register (Register 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

Technology Ability Field Bit Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

Auto-Negotiation Link Partner Ability Register (Register 5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-4

INDEX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .INDEX-1

8/01/00 Am79C976 11

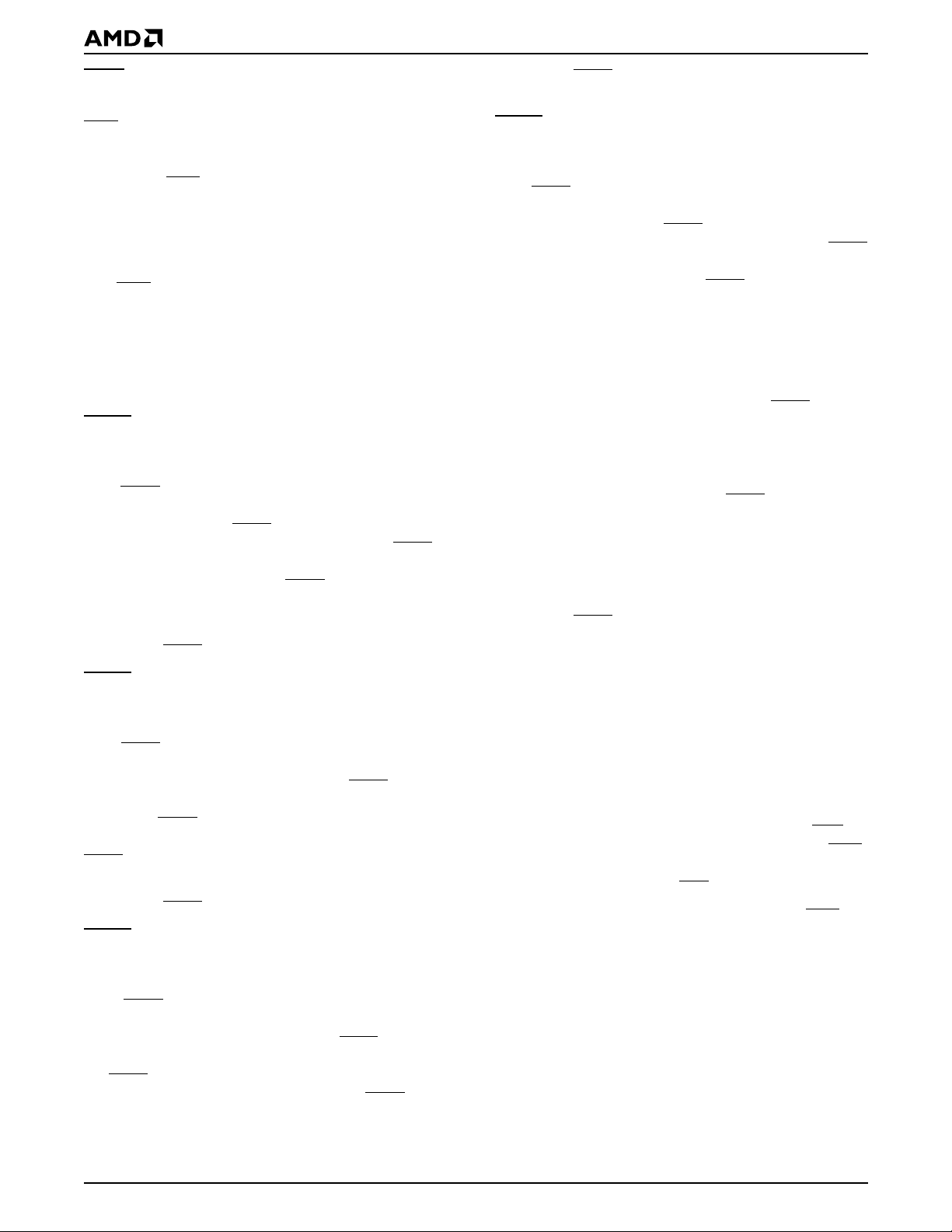

Page 12

PRELIMINARY

LIST OF FIGURES

Figure 1: Slave Configuration Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 2: Slave Configuration Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 3: Slave Read Using I/O Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 4: Slave Write Using Memory Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 5: Disconnect Of Slave Cycle When Busy . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 6: Disconnect Of Slave Burst Transfer - No Host Wait States . . . . . . . . . . . . 38

Figure 7: Disconnect Of Slave Burst Transfer - Host Inserts Wait States . . . . . . . . . 39

Figure 8: Address Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 9: Slave Cycle Data Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 10: Bus Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 11: Non-Burst Read Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 12: Burst Read Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 13: Non-Burst Write Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 14: Burst Write Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 15: Disconnect With Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 16: Disconnect Without Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 17: Target Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 18: Preemption During Non-Burst Transaction . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 19: Preemption During Burst Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 20: Master Abor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 21: Master Cycle Data Parity Error Response . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 22: Descriptor Ring Read In Non-Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 23: Descriptor Ring Read In Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 24: Descriptor Ring Write In Non-Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 25: Descriptor Ring Write In Burst Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 26: FIFO Burst Write At Start Of Unaligned Buffer . . . . . . . . . . . . . . . . . . . . . 58

Figure 27: FIFO Burst Write At End Of Unaligned Buffer . . . . . . . . . . . . . . . . . . . . . . 59

Figure 28: 16-Bit Software Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 29: 32-Bit Software Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 30: ISO 8802-3 (IEEE/ANSI 802.3) Data Frame . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 31: IEEE 802.3 Frame and Length Field Transmission Order . . . . . . . . . . . . . 73

Figure 32: VLAN-Tagged Frame Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 33: Media Independent Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 34: Frame Format at the MII Interface Connection . . . . . . . . . . . . . . . . . . . . . 83

Figure 35: MII Receive Frame Tagging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 36: External SSRAM and Flash Configuration . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 37: Expansion ROM Bus Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Figure 38: Flash Read from Expansion Bus Data Port . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 39: Flash Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 40: EEPROM Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 41: EEPROM Entry Positions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 42: CRC Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 43: LED Control Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 44: OnNow Functional Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Figure 45: Pattern Match RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 46: PCI Expansion ROM Base Address Register . . . . . . . . . . . . . . . . . . . . . 117

Figure 47: Address Match Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .227

Figure 48: Normal and Tri-State Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

12 Am79C976 7/25/00

Page 13

PRELIMINARY

Figure 49: CLK Waveform for 5 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

Figure 50: CLK Waveform for 3.3 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

Figure 51: Input Setup and Hold Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

Figure 52: Output Valid Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Figure 53: Output Tri-State Delay Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Figure 54: EEPROM Read Functional Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Figure 55: Automatic PREAD EEPROM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

Figure 56: JTAG (IEEE 1149.1) TCK Waveform for 5 V Signaling . . . . . . . . . . . . . . 276

Figure 57: JTAG (IEEE 1149.1) Test Signal Timing . . . . . . . . . . . . . . . . . . . . . . . . . 277

Figure 58: Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Figure 59: Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Figure 60: MDC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .279

Figure 61: Management Data Setup and Hold Timing . . . . . . . . . . . . . . . . . . . . . . .280

Figure 62: Management Data Output Valid Delay Timing . . . . . . . . . . . . . . . . . . . . . 280

Figure 63: Reject Timing - External PHY MII @ 25 MHz . . . . . . . . . . . . . . . . . . . . . 281

Figure 64: Reject Timing - External PHY MII @ 2.5 MHz . . . . . . . . . . . . . . . . . . . . . 282

Figure 65: Receive Frame Tag Timing with Media Independent Interface . . . . . . . .283

Figure 66: External Memory Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Figure A-1: LAPP Timeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Figure A-2: LAPP 3 Buffer Grouping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Figure A-3: LAPP Timeline for Two-Interrupt Method . . . . . . . . . . . . . . . . . . . . . . . . . A-9

Figure A-4: LAPP 3 Buffer Grouping for Two-Interrupt Method . . . . . . . . . . . . . . . . A-10

7/25/00 Am79C976 13

Page 14

PRELIMINARY

LIST OF TABLES

Table 1: System Clock Selections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2: Slave Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 3: PCI Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 4: Descriptor Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 5: Descriptor Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 6: Receive Address Match . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 7: Receive Statistics Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 8: Transmit Statistics Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 9: VLAN Tag Control Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 10: VLAN Tag Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 11: Auto-Negotiation Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 12: MAC Control Pause Frame Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 13: FC Pin Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 14: FCCMD Bit Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 15: SRAM_TYPE Field Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 16: LED Default Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 17: IEEE 1149.1 Supported Instruction Summary . . . . . . . . . . . . . . . . . . . . . 104

Table 18: BSR Mode Of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 19: Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 20: PCI Configuration Space Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 21: Address PROM Space Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 22: I/O Map In Word I/O Mode (DWIO = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 23: Legal I/O Accesses in Word I/O Mode (DWIO = 0) . . . . . . . . . . . . . . . . . 109

Table 24: I/O Map In DWord I/O Mode (DWIO = 1) . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 25: Legal I/O Accesses in Double Word I/O Mode (DWIO =1) . . . . . . . . . . . . 109