AMD Advanced Micro Devices AM79C940VCW, AM79C940VC, AM79C940KCW, AM79C940KC, AM79C940JC Datasheet

Publication#16235 Rev. C Amendment/0

Issue Date: June 1994

Advanced

Micro

Devices

Am79C940

Media Access Controller for Ethernet (MACETM)

FINAL

DISTINCTIVE CHARACTERISTICS

■ Integrated Controller with 10BASE-T

transceiver and AUI port

■ Supports IEEE 802.3/ANSI 8802-3 and Ethernet

standards

■ 84-pin PLCC and 100-pin PQFP Packages

■ 80-pin Thin Quad Flat Pack (TQFP) package

available for space critical applications such

as PCMCIA

■ Modular architecture allows easy tuning to

specific applications

■ High speed, 16-bit synchronous host system

interface with 2 or 3 cycles/transfer

■ Individual transmit (136 byte) and receive (128

byte) FlFOs provide increase of system

latency and support the following features:

– Automatic retransmission with no FIFO

reload

– Automatic receive stripping and transmit

padding (individually programmable)

– Automatic runt packet rejection

– Automatic deletion of collision frames

– Automatic retransmission with no FIFO

reload

■ Direct slave access to all on board

configuration/status registers and transmit/

receive FlFOs

■ Direct FIFO read/write access for simple

interface to DMA controllers or l/O processors

■ Arbitrary byte alignment and little/big endian

memory interface supported

■ Internal/external loopback capabilities

■ External Address Detection Interface (EADI)

for external hardware address filtering in

bridge/router applications

■ JTAG Boundary Scan (IEEE 1149.1 ) test

access port interface for board level

production test

■ Integrated Manchester Encoder/Decoder

■ Digital Attachment Interface (DAI) allows

by-passing of differential Attachment Unit

Interface (AUI)

■ Supports the following types of network

interface:

– AUI to external 10BASE2, 10BASE5 or

10BASE-F MAU

– DAI port to external 10BASE2, 10BASE5,

10BASE-T, 10BASE-F MAU

– General Purpose Serial Interface (GPSI) to

external encoding/decoding scheme

– Internal 10BASE-T transceiver with

automatic selection of 10BASE-T or AUI port

■ Sleep mode allows reduced power consump-

tion for critical battery powered applications

■ 1 MHz – 25 MHz system clock speed

GENERAL DESCRIPTION

The Media Access Controller for Ethernet (MACE) chip

is a CMOS VLSI device designed to provide flexibility in

customized LAN design. The MACE device is specifically designed to address applications where multiple

I/O peripherals are present, and a centralized or system

specific DMA is required. The high speed, 16-bit synchronous system interface is optimized for an external

DMA or I/O processor system, and is similar to many existing peripheral devices, such as SCSI and serial

link controllers.

The MACE device is a slave register based peripheral.

All transfers to and from the system are performed using

simple memory or I/O read and write commands. In conjunction with a user defined DMA engine, the MACE

chip provides an IEEE 802.3 interface tailored to a

specific application. Its superior modular architecture

and versatile system interface allow the MACE device to

be configured as a stand-alone device or as a connectivity cell incorporated into a larger, integrated system.

The MACE device provides a complete Ethernet node

solution with an integrated 10BASE-T transceiver, and

supports up to 25-MHz system clocks. The MACE device embodies the Media Access Control (MAC) and

Physical Signaling (PLS) sub-layers of the IEEE 802.3

standard, and provides an IEEE defined Attachment

Unit Interface (AUI) for coupling to an external Medium

Attachment Unit (MAU). The MACE device is

compliant with 10BASE2, 10BASE5, 10BASE-T, and

10BASE-F transceivers.

AMD

2 Am79C940

Additional features also enhance over-all system

design. The individual transmit and receive FIFOs

optimize system overhead, providing substantial

latency during packet transmission and reception, and

minimizing intervention during normal network error

recovery. The integrated Manchester encoder/decoder

eliminates the need for an external Serial Interface

Adapter (SIA) in the node system. If support for an

external encoding/decoding scheme is desired, the

General Purpose Serial Interface (GPSI) allows direct

access to/from the MAC. In addition, the Digital Attachment Interface (DAI), which is a simplified electrical

attachment specification, allows implementation of

MAUs that do not require DC isolation between the MAU

and DTE. The DAI port can also be used to indicate

transmit, receive, or collision status by connecting LEDs

to the port. The MACE device also provides an External

Address Detection Interface (EADI) to allow external

hardware address filtering in internetworking

applications.

The Am79C940 MACE chip is offered in a Plastic Leadless Chip Carrier (84-pin PLCC), a Plastic Quad Flat

Package (100-pin PQFP), and a Thin Quad Flat Package (TQFP 80-pin). There are several small functional

and physical differences between the 80-pin TQFP and

the 84-pin PLCC and 100-pin PQFP configurations.

Because of the smaller number of pins in the TQFP configuration versus the PLCC configuration, four pins are

not bonded out. Though the die is identical in all three

package configurations, the removal of these four pins

does cause some functionality differences between the

TQFP and the PLCC and PQFP configurations. Depending on the application, the removal of these pins will

or will not have an effect.

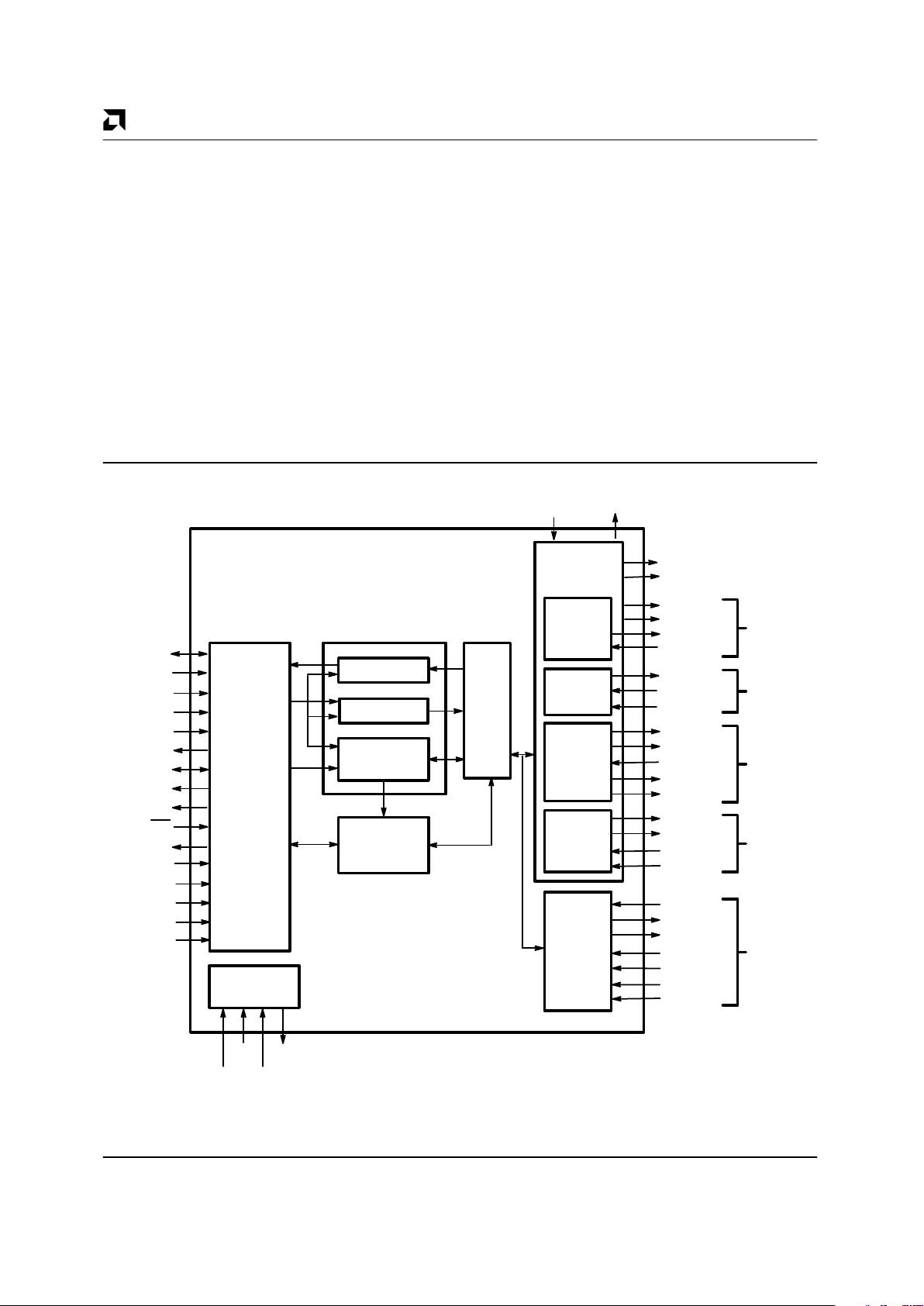

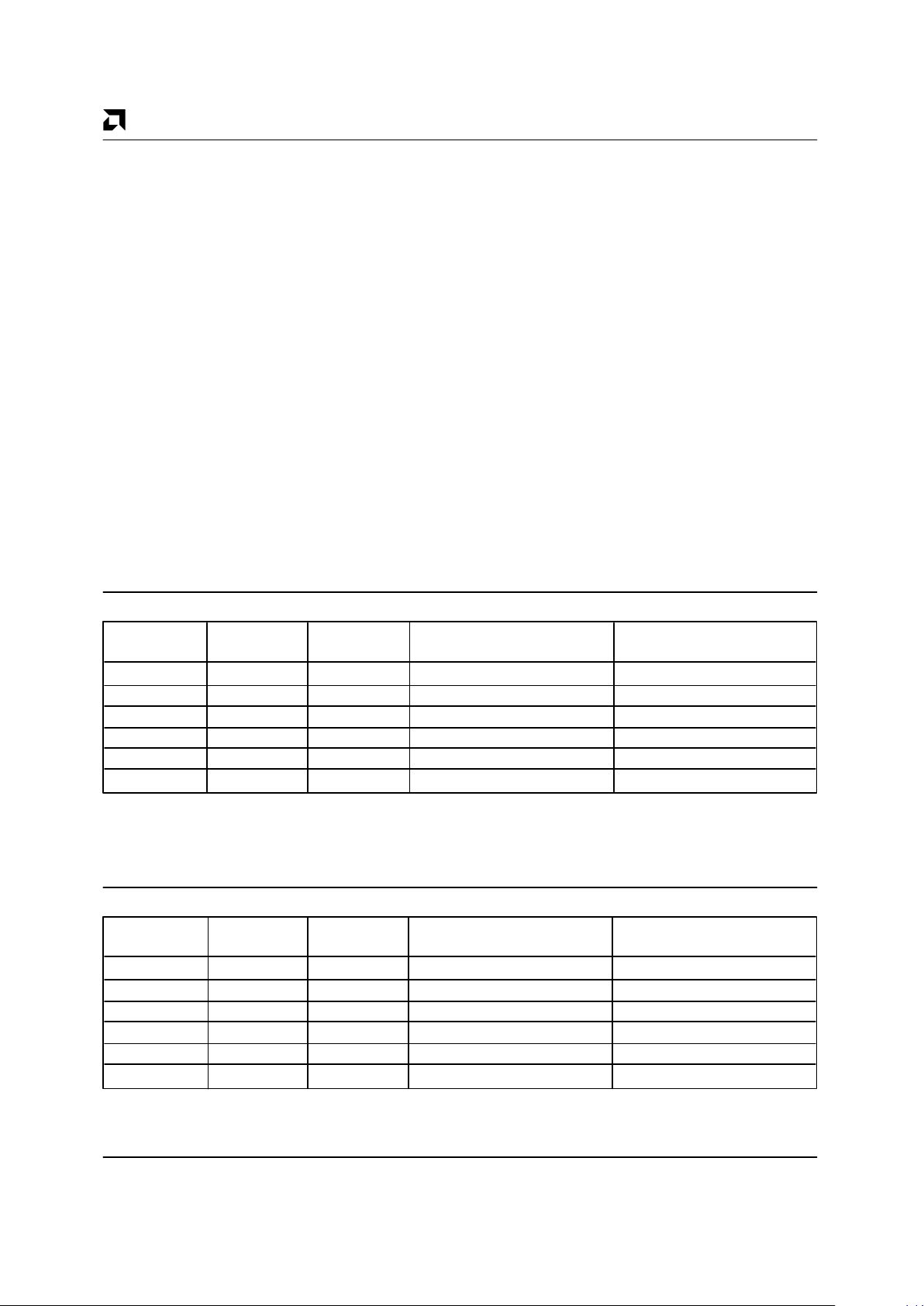

BLOCK DIAGRAM

DBUS 15-0

ADD 4-0

R/W

CS

FDS

DTV

EOF

RDTREQ

TDTREQ

BE 1–0

INTR

SCLK

EDSEL

TC

SLEEP

RESET

16235C-1

XTAL1

FIFO

Control

EADI Port

Bus

Interface

Unit

802.3

MAC

Core

ENCODER/

DECODER

(PLS)

XMT FIFO

RCV FIFO

Command

& Status

Registers

JTAG

PORT CNTRL

TCK

TDI

TMS

TDO

XTAL2

EADI

Port

Control

AUI

Port

10BASE-T

MAU

DAI

Port

GPSI

Port

DXCVR

CLSN

SRDCLK

SRD

SF/BD

EAM/R

DO±

DI±

CI±

TXD±

TXP±

RXD±

LNKST

RXPOL

TXDAT±

TXEN

RXDAT

RXCRS

STDCLK

TXDAT+

TXEN

SRDCLK

RXDAT

RXCRS

CLSN

AUI

10BASE-T

DAI Port

GPSI

Notes:

1. Only one of the network ports AUI, 10BASE-T, DAI port or GPSI can be active at any time. Some shared signals are active

regardless of which network port is active, and some are reconfigured.

2. The EADI port is active at all times.

AMD

3Am79C940

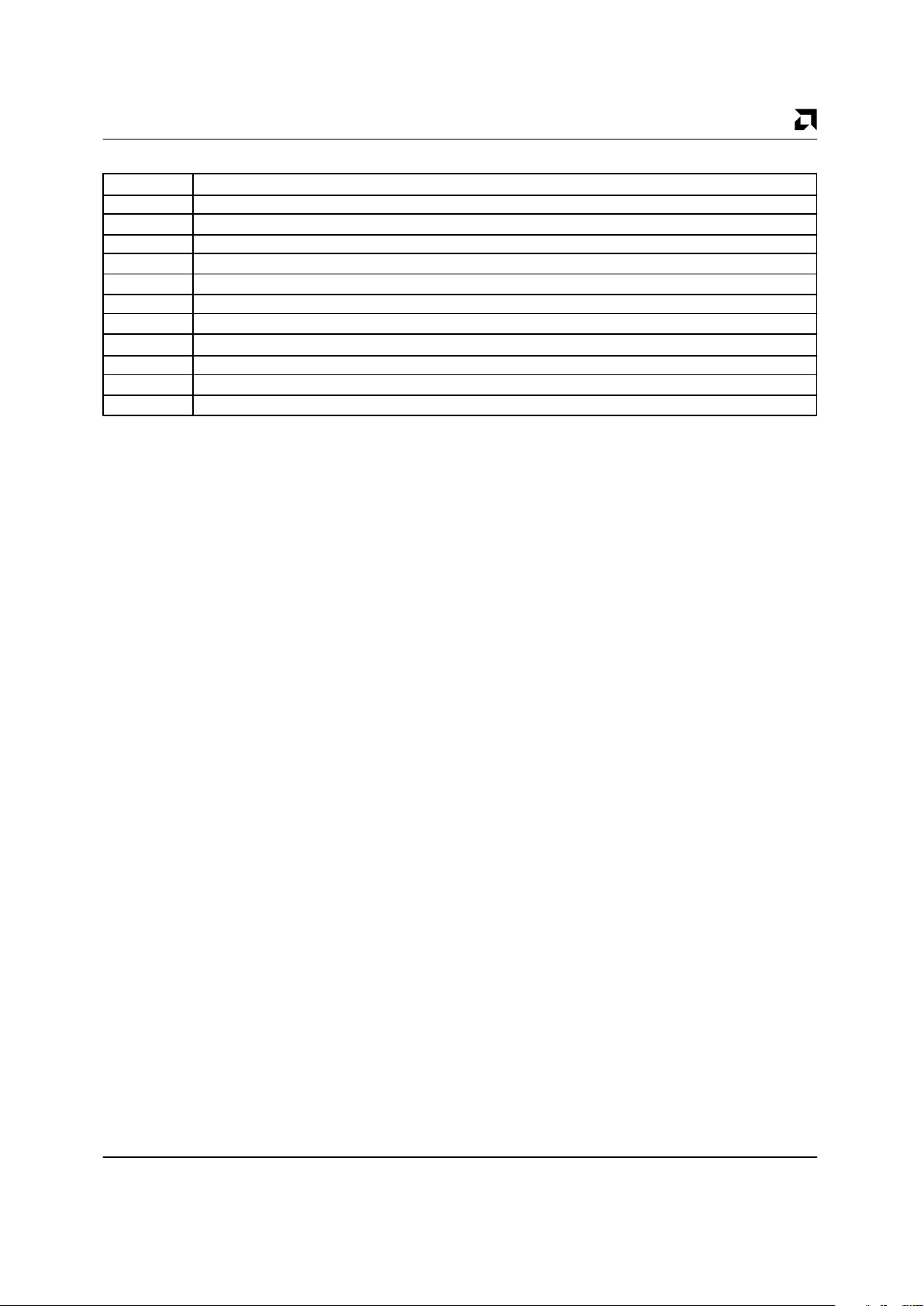

RELATED PRODUCTS

Part No. Description

Am7996 IEEE 802.3/Ethernet/Cheapernet Transceiver

Am79C90 CMOS Local Area Network Controller for Ethernet (C-LANCE)

Am79C98 Twisted Pair Ethernet Transceiver (TPEX)

Am79C100 Twisted Pair Ethernet Transceiver Plus (TPEX+)

Am79C981 Integrated Multiport Repeater Plus (IMR+)

Am79C987 Hardware Implemented Management Information Base (HIMIB)

Am79C900 Integrated Local Area Communications Controller (ILACC)

Am79C961 PCnet-ISA

+

Single-Chip Ethernet Controller for ISA (with Microsoft Plug n’ Play Support)

Am79C965 PCnet-32 Single-Chip 32-Bit Ethernet Controller

Am79C970 PCnet-PCI Single-Chip Ethernet Controller (for PCI bus)

Am79C974 PCnet-SCSI Combination Ethernet and SCSI Controller for PCI Systems

AMD

4 Am79C940

TABLE OF CONTENTS

DISTINCTIVE CHARACTERISTICS 1-64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

GENERAL DESCRIPTION 1-64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BLOCK DIAGRAM 1-65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RELATED PRODUCTS 1-66. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CONNECTION DIAGRAMS 1-70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLCC 1-70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PQR 1-71. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PQT 1-72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ORDERING 1-73. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PIN/PACKAGE SUMMARY 1-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PIN DESCRIPTION 1-82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Network Interfaces 1-82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Attachment Unit Interface (AUI) 1-82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital Attachment Interface (DAI) 1-82. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10BASE-T Interface 1-85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

General Purpose Serial Interface (GPSI) 1-85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Address Detection Interface (EADI) 1-86. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Host System Interface 1-88. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IEEE 1149.1 Test Access Port (TAP) Interface 1-89. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

General Interface 1-89. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply 1-90. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FUNCTIONAL DESCRIPTION 1-92. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Network Interfaces 1-92. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Interface 1-92. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DETAILED FUNCTIONS 1-93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Block Level Description 1-93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bus Interface Unit (BIU) 1-93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BIU to FIFO Data Path 1-93. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BIU to Control and Status Register Data Path 1-94. . . . . . . . . . . . . . . . . . . . . . . . .

FIFO Sub-System 1-94. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Media Access Control (MAC) 1-96. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Manchester Encoder/Decoder (MENDEC) 1-100. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Attachment Unit Interface (AUI) 1-103. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital Attachment Interface (DAI) 1-103. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10BASE-T Interface 1-104. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Twisted Pair Transmit Function 1-104. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Twisted Pair Receive Function 1-104. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Link Test Function 1-105. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Polarity Detection and Reversal 1-105. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Twisted Pair Interface Status 1-106. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Collision Detect Function 1-106. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Quality Error (SQE) Test (Heartbeat) Function 1-106. . . . . . . . . . . . . . . . . .

Jabber Function 1-106. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AMD

5Am79C940

External Address Detection Interface (EADI) 1-107. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

General Purpose Serial Interface (GPSI) 1-108. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IEEE 1149.1 Test Access Port Interface 1-108. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Slave Access Operation 1-109. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Read Access 1-109. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Write Access 1-110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Initialization 1-110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reinitialization 1-110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Operation 1-110. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit FIFO Write 1-111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Function Programming 1-111. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Automatic Pad Generation 1-112. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit FCS Generation 1-113. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Status Information 1-113. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Exception Conditions 1-113. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Operation 1-115. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive FIFO Read 1-115. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Function Programming 1-116. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Automatic Pad Stripping 1-116. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive FCS Checking 1-117. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Status Information 1-117. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Exception Conditions 1-117. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Loopback Operation 1-118. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

USER ACCESSIBLE REGISTERS 1-120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive FIFO (RCVFIFO) 1-120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit FIFO (XMTFIFO) 1-120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Frame Control (XMTFC) 1-120. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Frame Status (XMTFS) 1-121. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmit Retry Count (XMTRC) 1-122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Frame Control (RCVFC) 1-122. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Frame Status (RCVFS) 1-123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RFS0—Receive Message Byte Count (RCVCNT) 1-123. . . . . . . . . . . . . . . . . . . . . . . . .

RFS1—Receive Status (RCVSTS) 1-123. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RFS2—Runt Packet Count (RNTPC) 1-124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RFS3—Receive Collision Count (RCVCC) 1-124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FIFO Frame Count (FIFOFC) 1-124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Register (IR) 1-124. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Mask Register (IMR) 1-126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Poll Register (PR) 1-126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BIU Configuration Control (BIUCC) 1-127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

FIFO Configuration Control (FIFOCC) 1-127. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MAC Configuration Control (MACCC) 1-129. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLS Configuration Control (PLSCC) 1-130. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PHY Configuration Control (PHYCC) 1-130. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chip Identification Register (CHIPID [15–00]) 1-131. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Address Configuration (IAC) 1-131. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Logical Address Filter (LADRF [63–00]) 1-132. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AMD

6 Am79C940

Physical Address (PADR [47–00]) 1-134. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Missed Packet Count (MPC) 1-134. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Runt Packet Count (RNTPC) 1-134. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Collision Count (RCVCC) 1-135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Test Register (UTR) 1-135. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reserved Test Register 1 (RTR1) 1-136. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reserved Test Register 2 (RTR2) 1-136. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Register Table Summary 1-137. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Register Bit Summary 1-138. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16-Bit Registers 1-138. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

8-Bit Registers 1-138. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receive Frame Status 1-138. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Programmer’s Register Model 1-139. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SYSTEM APPLICATIONS 1-142. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HOST SYSTEM EXAMPLES 1-142. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Motherboard DMA Controller 1-142. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Interface-Motherboard DMA Example 1-143. . . . . . . . . . . . . . . . . . . . . . . .

PC/AT Ethernet Adapter Card 1-144. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Interface-Simple PC/AT Ethernet Hypercard Example 1-145. . . . . . . . . . .

NETWORK INTERFACES 1-145. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Address Detection Interface (EADI) 1-145. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Attachment Unit Interface (AUI) 1-146. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10BASE-T Interface 1-147. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

10BASE-T and 10BASE2 Configuration of Am79C940 1-148. . . . . . . . . . . . . . . . . . . . .

10BASE-T and AUI Implementation of Am79C940 1-149. . . . . . . . . . . . . . . . . . . . . . . .

MACE Device Compatible AUI Isolation Transformers 1-150. . . . . . . . . . . . . . . . . . . . .

MACE Device Compatible 10BASE-T Media Interface Modules 1-150. . . . . . . . . . . . . .

ABSOLUTE MAXIMUM RATINGS 1-152. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

OPERATING RANGES 1-152. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DC CHARACTERISTICS 1-152. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AC CHARACTERISTICS 1-155. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BIU Output Valid Delay vs. Load Chart 1-159. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

KEY TO SWITCHING WAVEFORMS 1-159. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SWITCHING TEST CIRCUITS 1-160. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AC WAVEFORMS 1-161. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

APPENDIX A 1-179. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LOGICAL ADDRESS FILTERING FOR ETHERNET 1-179. . . . . . . . . . . . . . . . . . . . . . . . . .

MAPPING OF LOGICAL ADDRESS TO FILTER MASK 1-180. . . . . . . . . . . . . . . . . . . . . . .

APPENDIX B 1-181. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BSDL DESCRIPTION OF Am79C940 MACE JTAG STRUCTURE 1-181. . . . . . . . . . . . . . .

AMD

7Am79C940

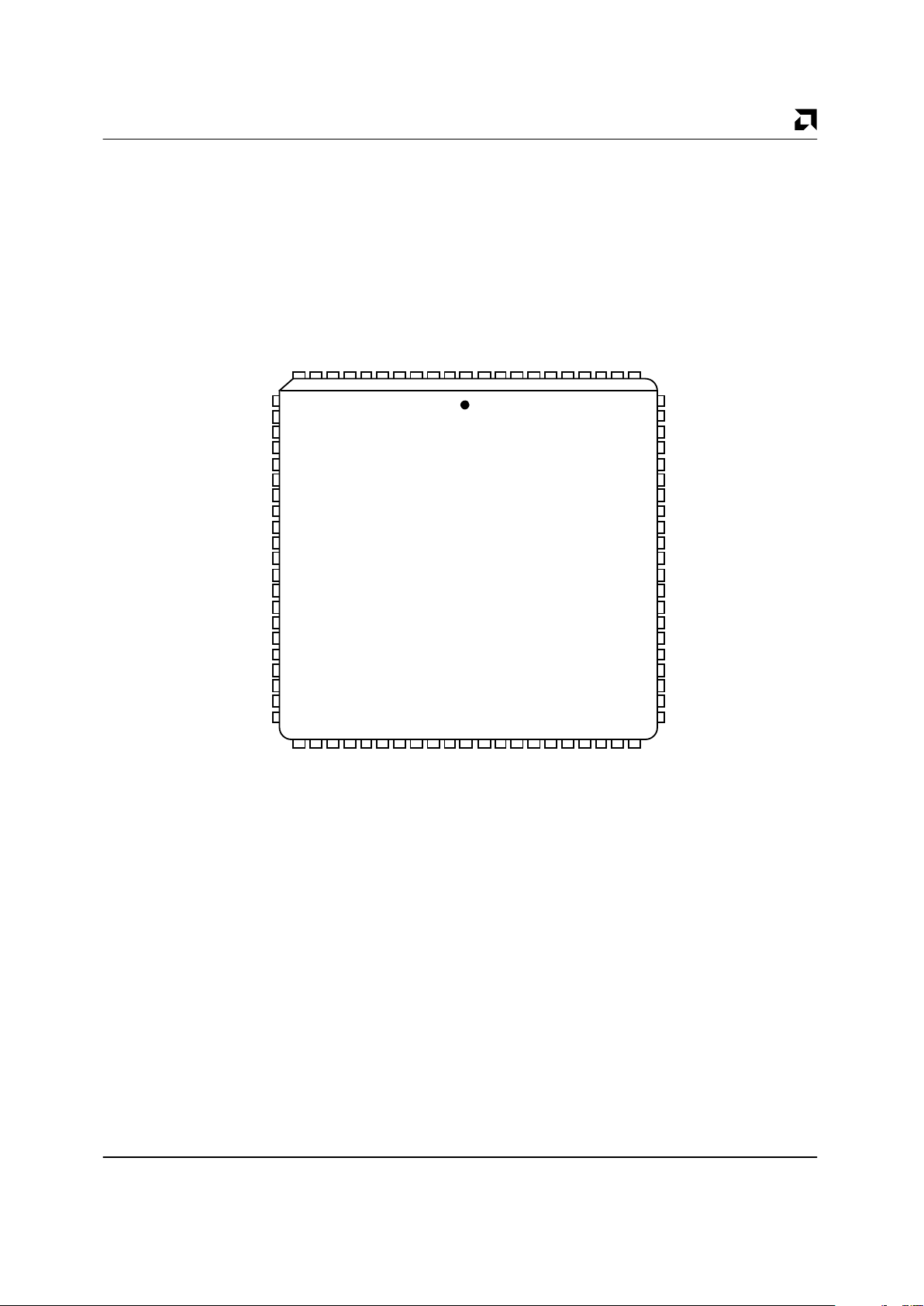

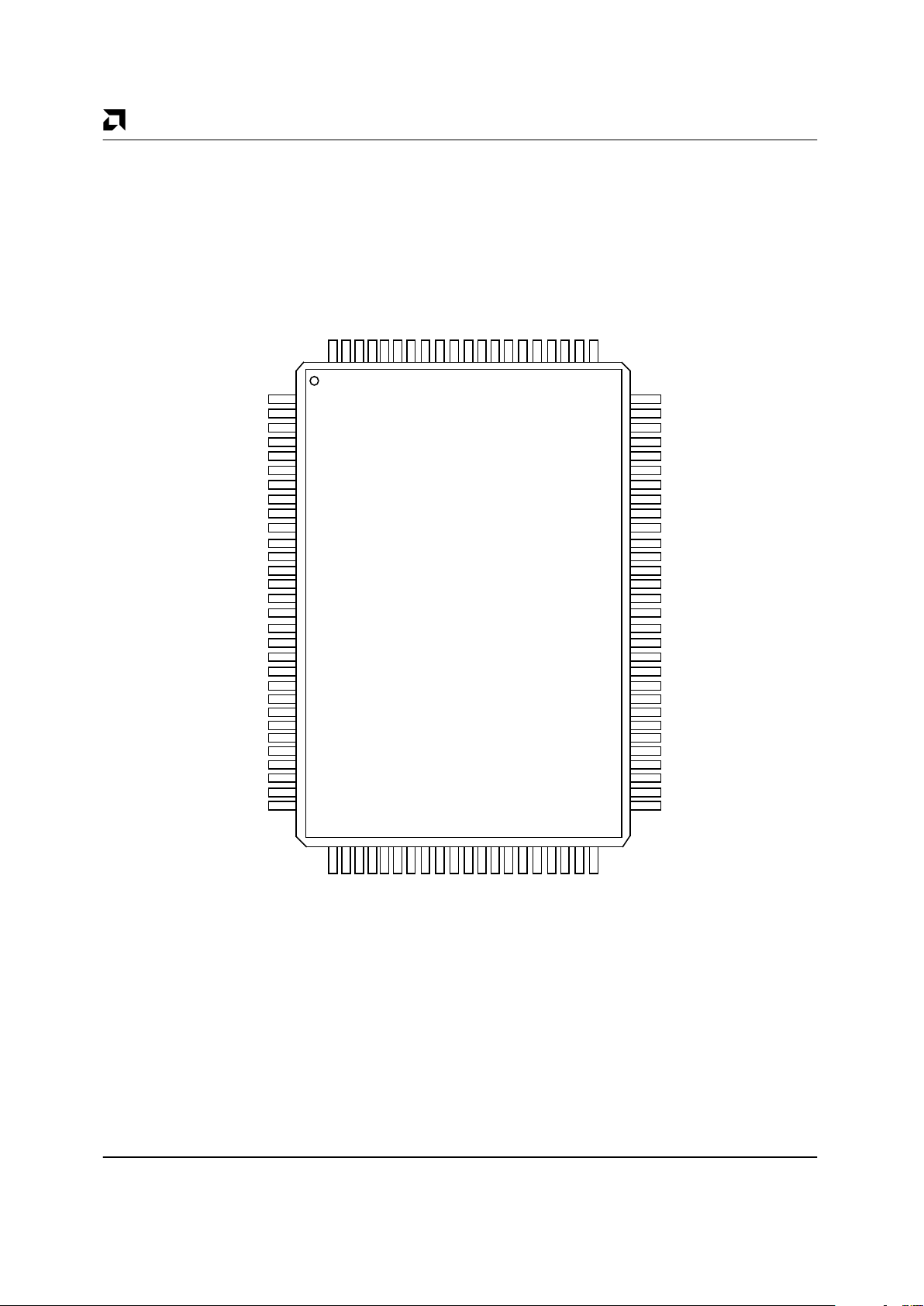

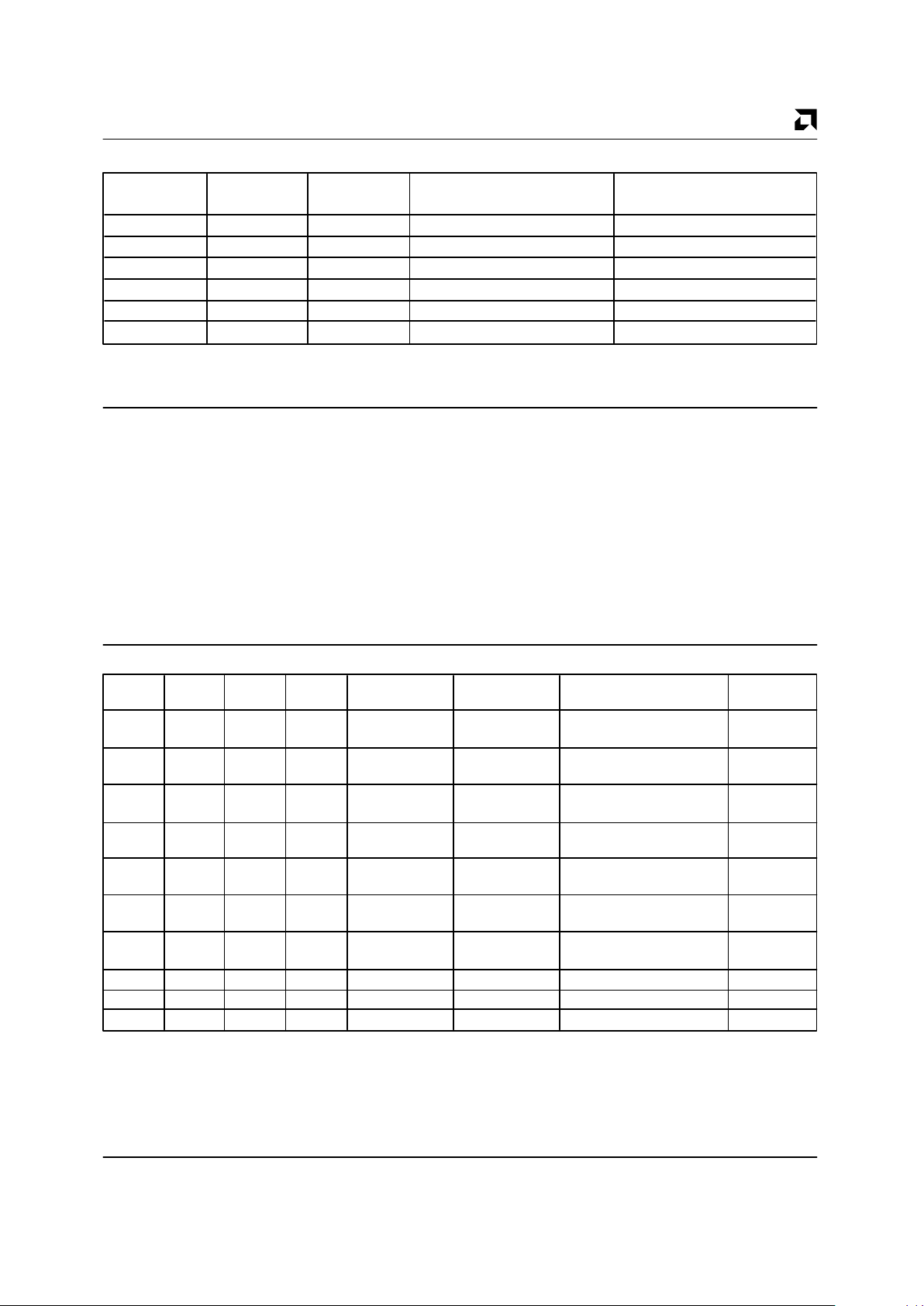

CONNECTION DIAGRAMS

PL 084

PLCC Package

16235C-2

1

2

3

81

82

83

84

6

7

8

9

4

5

80

76

77

78

79

75

12

13

14

15

16

17

18

19

20

21

23

24

25

26

27

28

29

30

31

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

43

42

41

40

47

46

45

44

37

36

35

34

39

38

33

48

52

51

50

49

10

22

11

32

53

74

SRDCLK

EAM/R

SRD

SF/BD

RESET

SLEEP

DV

DD

INTR

TC

DBUS0

DV

SS

DBUS1

DBUS2

DBUS3

DBUS4

DV

SS

DBUS5

DBUS6

DBUS7

DBUS8

DBUS9

XTAL2

AV

SS

XTAL1

AV

DD

TXD+

TXP+

TXD-

TXP-

AV

DD

RXD+

RXD-

DV

DD

TDI

DV

SS

TCK

TMS

TDO

LNKST

RXPOL

CS

R/W

RXCRS

RXDAT

CLSN

TXEN/TXEN

STDCLK

DV

SS

TXDAT-

TXDAT+

DV

SS

EDSEL

DXCVR

DV

DD

AV

DD

CI+

CI-

DI+

DI-

AV

DD

DO+

DO-

AV

SS

DBUS10

DBUS11

DBUS12

DBUS13

DV

DD

DBUS14

DBUS15

DV

SS

EOF

DTV

FDS

BE0

BE1

SCLK

TDTREQ

RDTREQ

ADD0

ADD1

ADD2

ADD3

ADD4

Am79C940

MACE

MACE

Am79C940JC

AMD

8 Am79C940

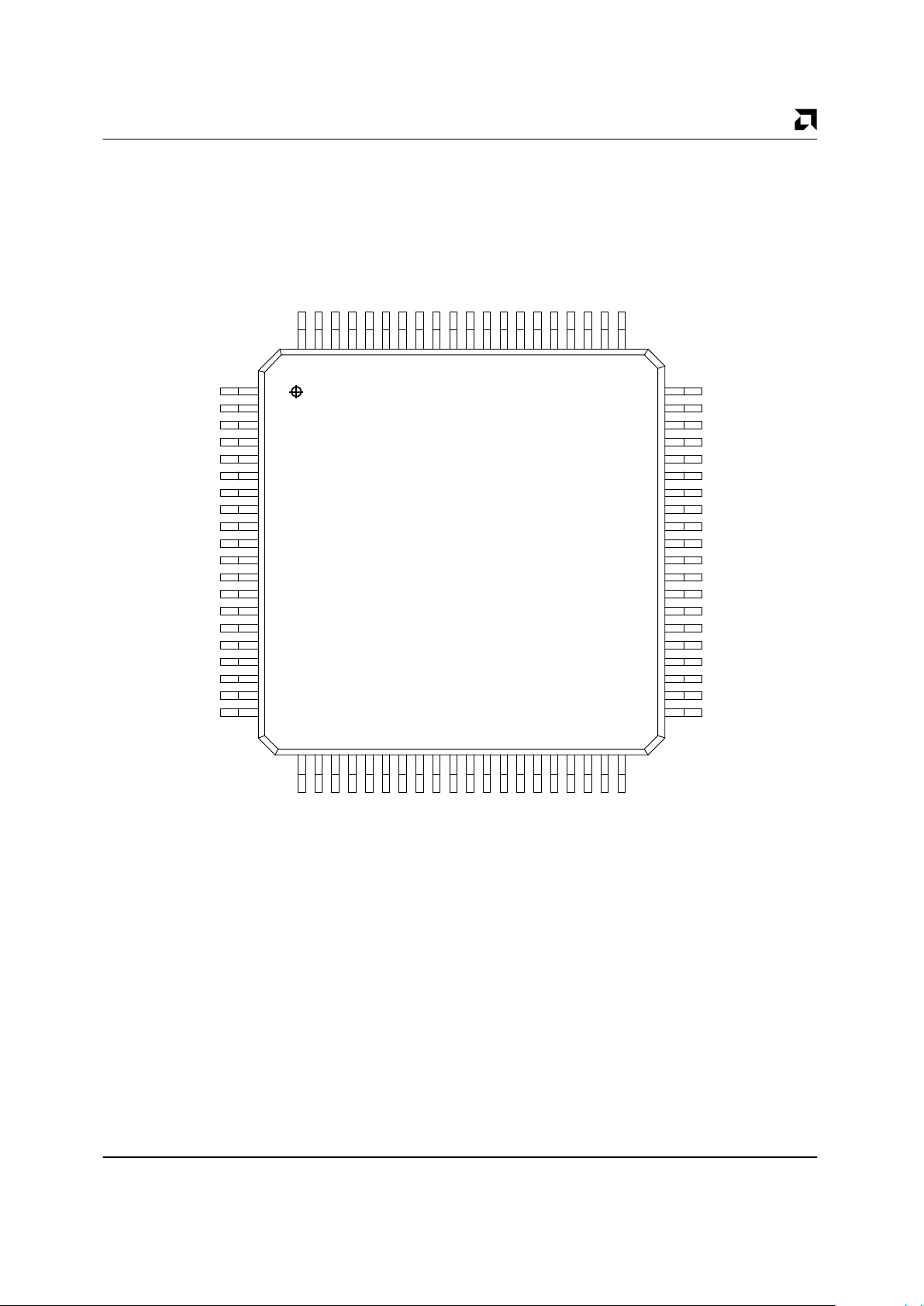

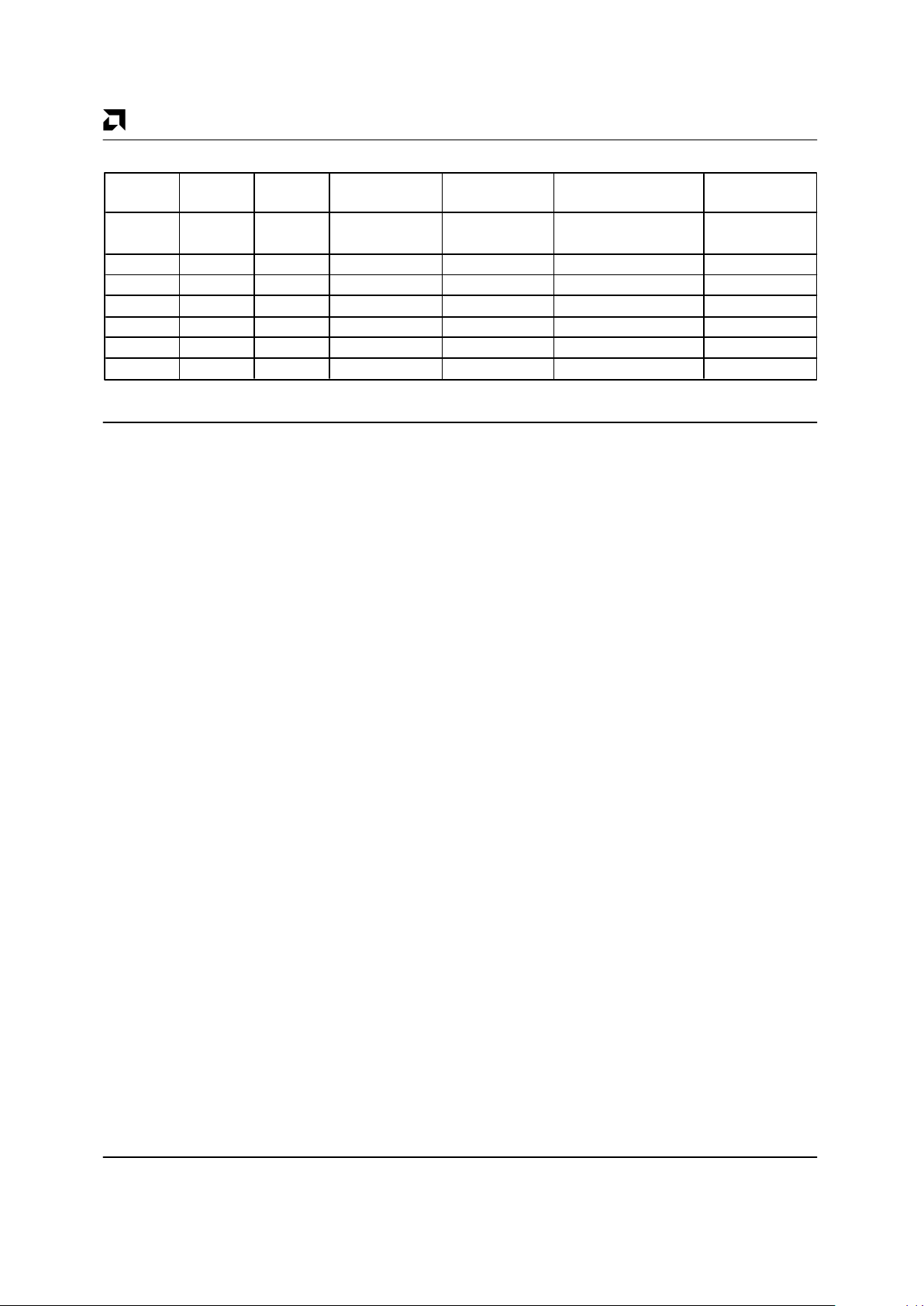

CONNECTION DIAGRAMS

PQR 100

PQFP Package

RXCRS

RXDAT

CLSN

TXEN/TXEN

STDCLK

DVSSTXDAT-

TXDAT+

DVSSEDSEL

DXCVR

DVDDAVDDCI+

CI-

DI+

DI-

AVDDDO+

DO-

28

29

30

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

1

2

3

99

98

100

31323334353637383940414243444546474849

50

9796959493929190898887868584828183

TCK

TMS

TDO

LNKST

RXPOL

CS

R/W

NC

NC

NC

NC

AV

SS

NC

NC

NC

XTAL2

AV

SS

XTAL1

AV

DD

TXD+

TXP+

TXDTXPAV

DD

RXD+

RXDDV

DD

TDI

DV

SS

NC

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

80

79

78

NC

NC

NC

NC

SRDCLK

EAM/R

SRD

SF/BD

RESET

SLEEP

DV

DD

INTR

TC

DBUS0

DV

SS

DBUS1

DBUS2

DBUS3

DBUS4

DV

SS

DBUS5

DBUS6

DBUS7

DBUS8

DBUS9

NC

NC

NC

DBUS10

NC

DBUS11

DBUS12

DBUS13

DV

DD

DBUS14

DBUS15

DV

SS

EOF

DTV

FDS

BE0

BE1

SCLK

TDTREQ

RDTREQ

ADD0

ADD1

ADD2

ADD3

ADD4

MACE

Am79C940KC

16235C-3

MACE

Am79C940KC

AMD

9Am79C940

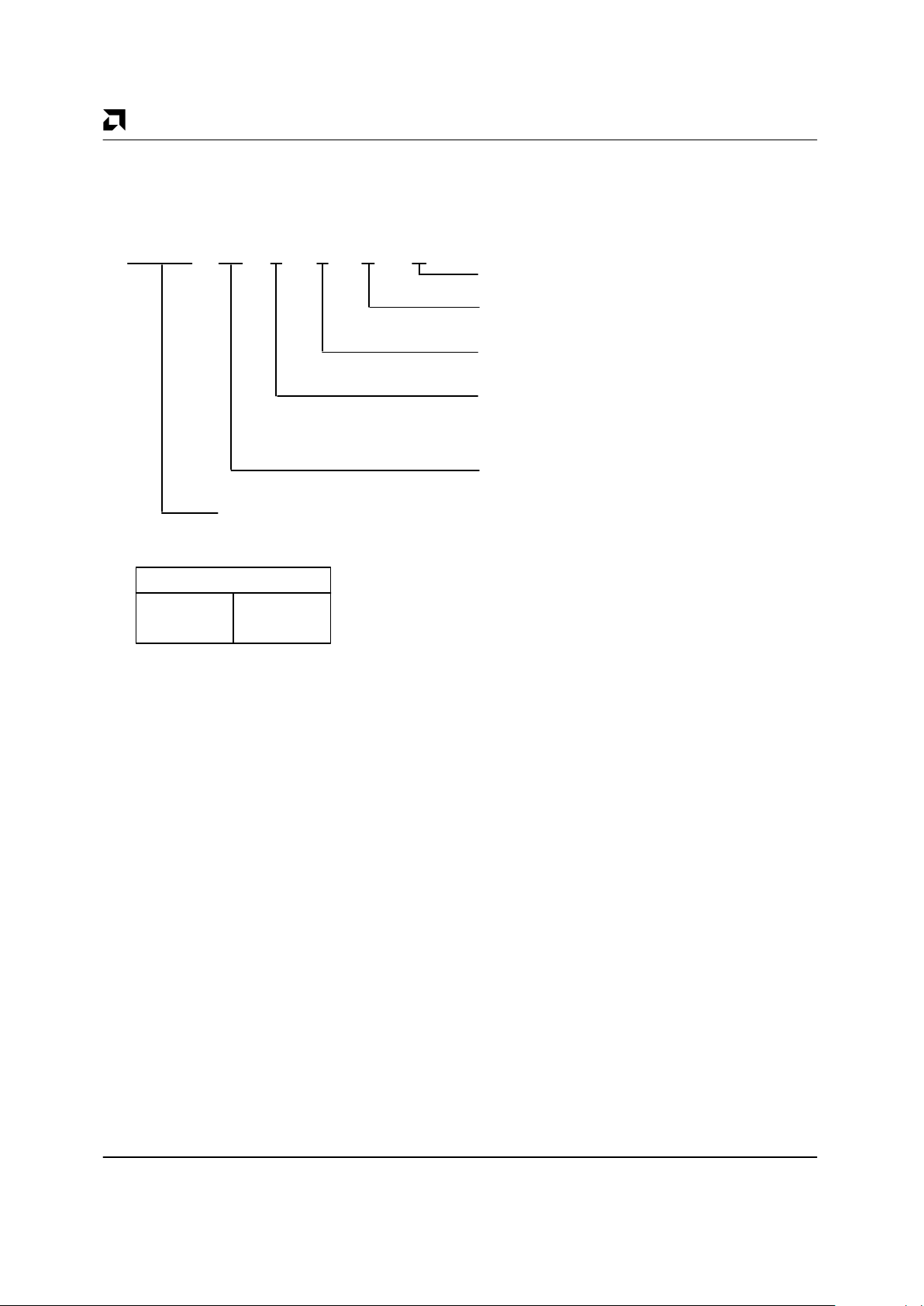

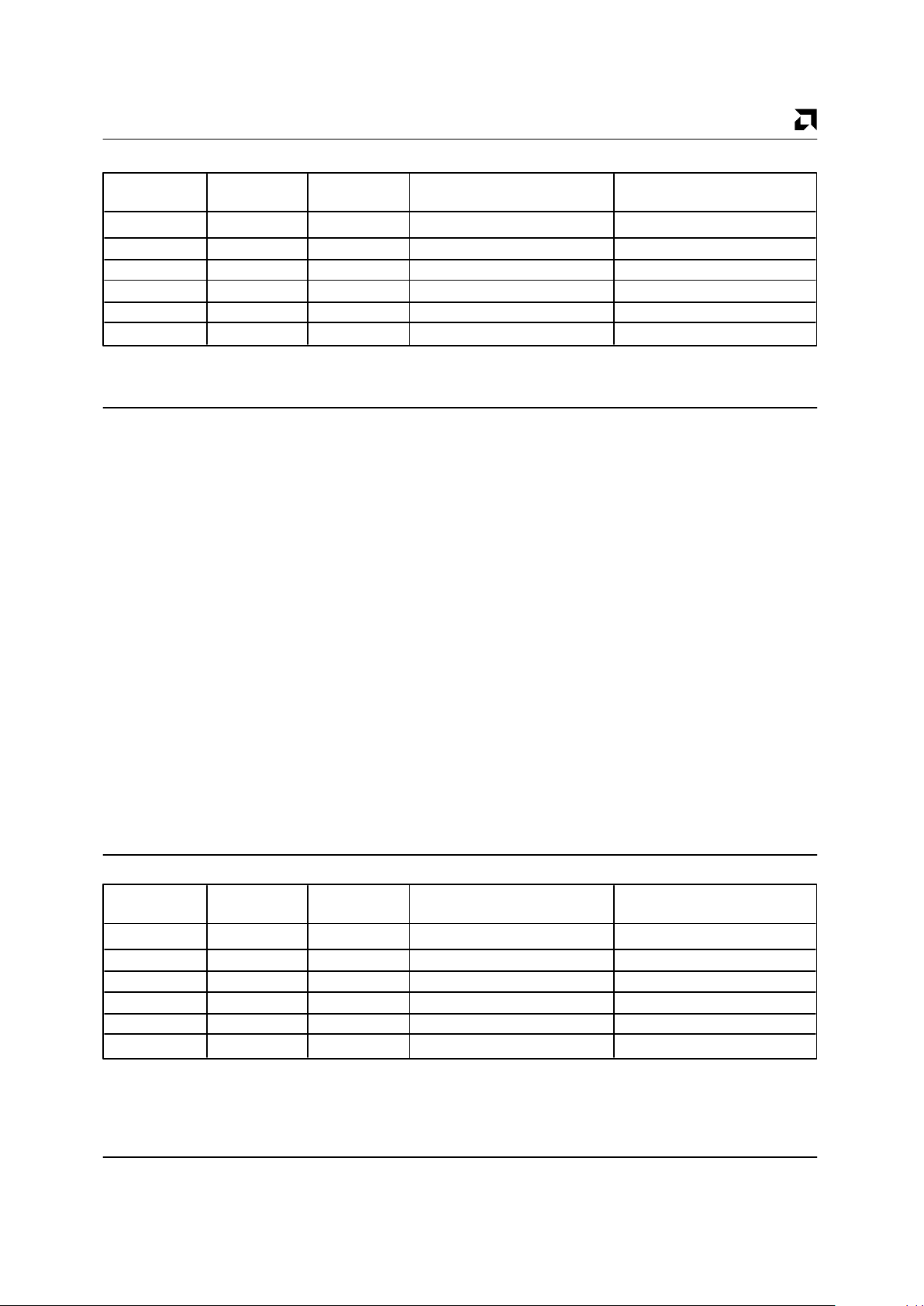

CONNECTION DIAGRAMS

PQT 080

TQFP Package

16235C-4

Note: Four pin functions available on the PLCC and PQFP packages are not available with the TQFP package.

(See page 27 “Pin Functions not available with the 80-pin TQFP Package”).

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

80 79 78 77 76 757473 72 71 7069 68 676665 64 63 62 61

21 22 23 24 25 262728 29 30 3132 33 343536 37 38 39 40

SRDCLK

EAM/R

SF/BD

RESET

SLEEP

DVDD

INTR

TC

DBUS0

DVSS

DBUS1

DBUS2

DBUS3

DBUS4

DVSS

DBUS5

DBUS6

DBUS7

DBUS8

DBUS9

XTAL2

AVSS

XTAL1

AVDD

TXD+

TXP+

TXDTXPAVDD

RXD+

RXDDVDD

TDI

DVSS

TCK

TMS

TD0

LNKST

CS

R/W

DBUS10

DBUS11

DBUS12

DBUS13

DVDD

DBUS14

DBUS15

DVSS

EOF

FDS

BE0

BE1

SCLK

TDTREQ

RDTREQ

ADD0

ADD1

ADD2

ADD3

ADD4

RXCRS

RXDAT

CLSN

TXEN/TXEN

STDCLK

DVSS

TXDAT+

DVSS

EDSEL

DXCVR

DVDD

AVDD

CI+

CI-

DI+

DI-

AVDD

DO+

DO-

AVSS

MACE

Am79C940VC

AMD

10 Am79C940

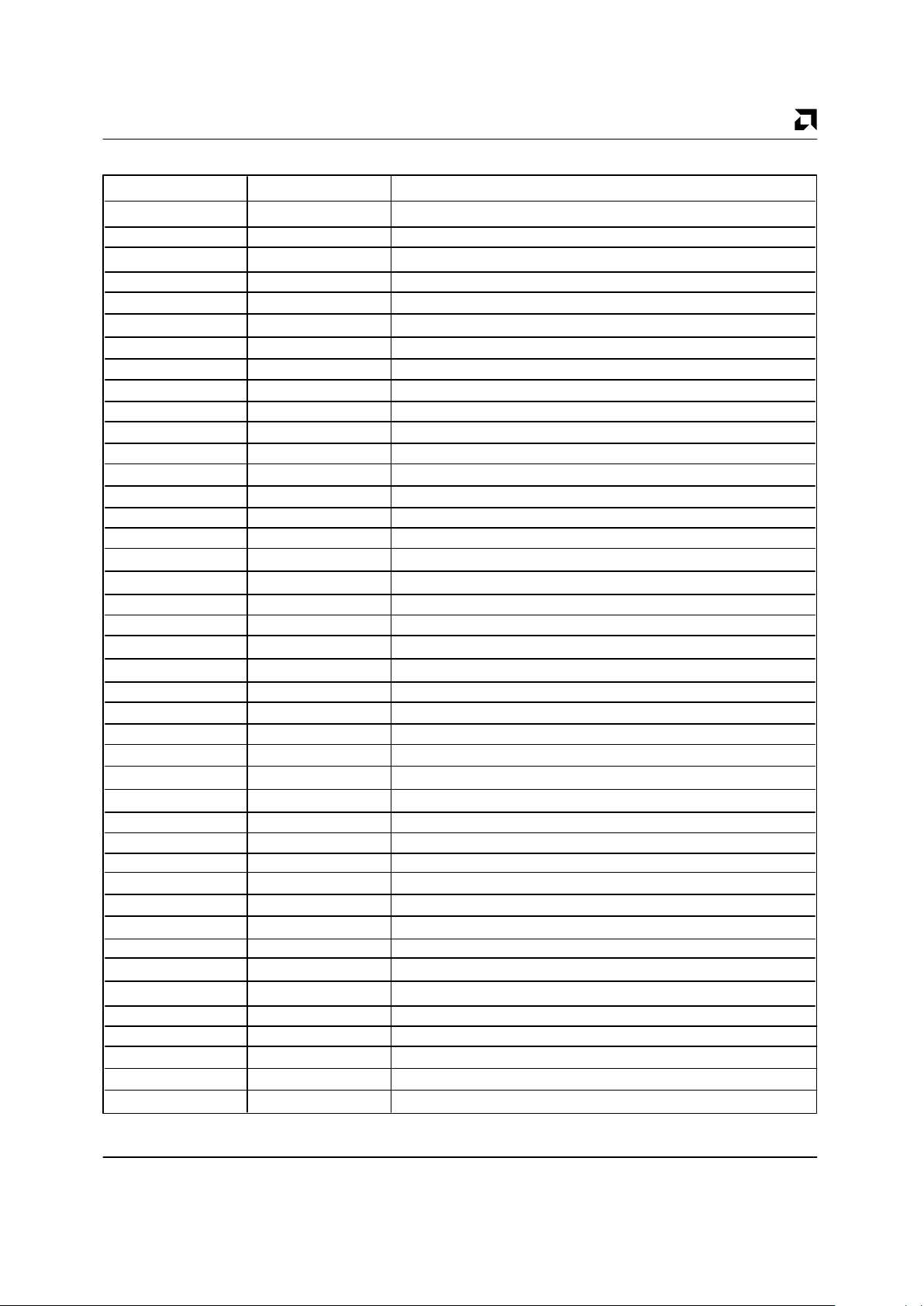

ORDERING INFORMATION

Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is

formed by a combination of:

AM79C940

JC, KC,

Valid Combinations

Valid Combinations

The Valid Combinations table lists configurations

planned to be supported in volume for this device.

Consult the local AMD sales office to confirm

availability of specific valid combinations and to

check on newly released combinations.

AM79C940

OPTIONAL PROCESSING

Blank = Standard Processing

TEMPERATURE RANGE

C = Commercial (0

° to +70°C)

PACKAGE TYPE (per Prod. Nomenclature/16-038)

J = 84-Pin Plastic Leaded Chip Carrier (PL 084)

K = 100-Pin Plastic Quad Flat Pack (PQR100)

V = 80-Pin Thin Quad Flat Package (PQT080)

SPEED

Not Applicable

DEVICE NUMBER/DESCRIPTION (include revision letter)

Am79C940

Media Access Controller for Ethernet

VC

ALTERNATE PACKAGING OPTION

/W = Trimmed and Formed in a Tray

KC/W, VC,

/W

VC/W

AMD

11Am79C940

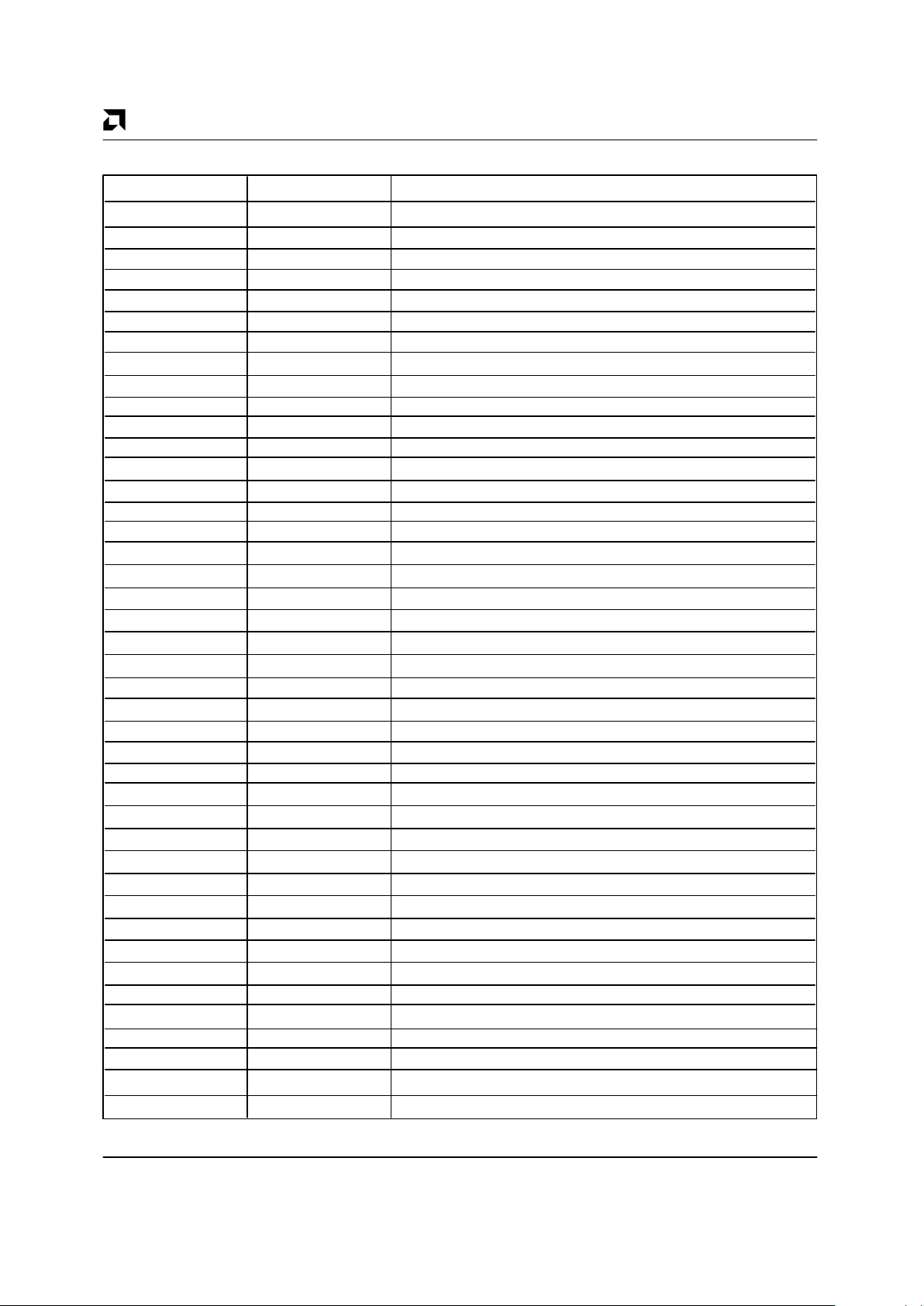

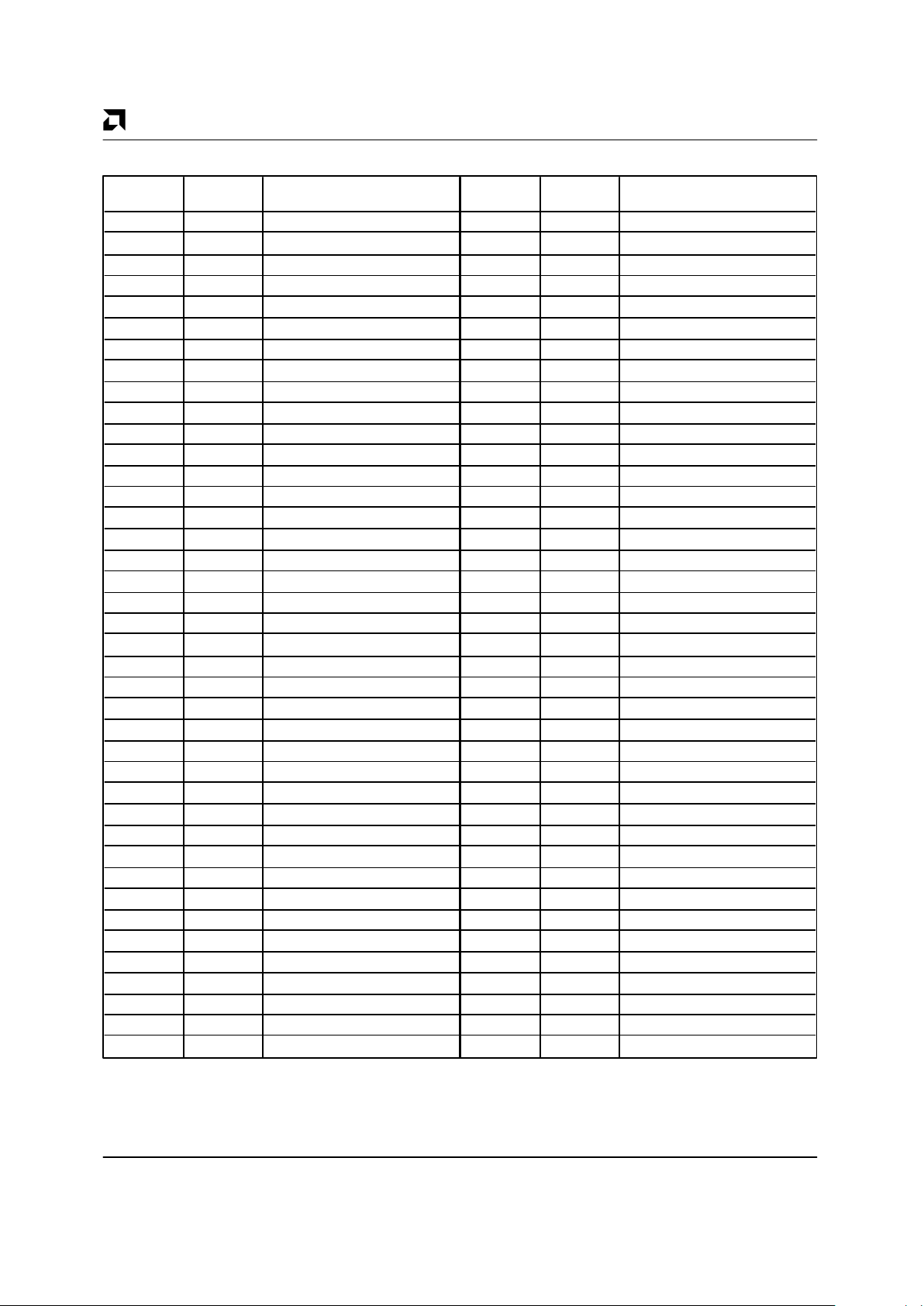

PIN/PACKAGE SUMMARY

PLCC Pin # Pin Name Pin Function

1 DXCVR Disable Transceiver

2 EDSEL Edge Select

3DV

SS

Digital Ground

4 TXDAT+ Transmit Data +

5 TXDAT– Transmit Data –

6DV

SS

Digital Ground

7 STDCLK Serial Transmit Data Clock

8 TXEN/TXEN Transmit Enable

9 CLSN Collision

10 RXDAT Receive Data

11 RXCRS Receive Carrier Sense

12 SRDCLK Serial Receive Data Clock

13 EAM/R External Address Match/Reject

14 SRD Serial Receive Data

15 SF/BD Start Frame/Byte Delimiter

16 RESET Reset

17 SLEEP Sleep Mode

18 DV

DD

Digital Power

19 INTR Interrupt

20 TC Timing Control

21 DBUS0 Data Bus0

22 DV

SS

Digital Ground

23 DBUS1 Data Bus1

24 DBUS2 Data Bus2

25 DBUS3 Data Bus3

26 DBUS4 Data Bus4

27 DV

SS

Digital Ground

28 DBUS5 Data Bus5

29 DBUS6 Data Bus6

30 DBUS7 Data Bus7

31 DBUS8 Data Bus8

32 DBUS9 Data Bus9

33 DBUS10 Data Bus10

34 DBUS11 Data Bus11

35 DBUS12 Data Bus12

36 DBUS13 Data Bus13

37 DV

DD

Digital Power

38 DBUS14 Data Bus14

39 DBUS15 Data Bus15

40 DV

SS

Digital Ground

41 EOF End Of Frame

42 DTV Data Transfer Valid

AMD

12 Am79C940

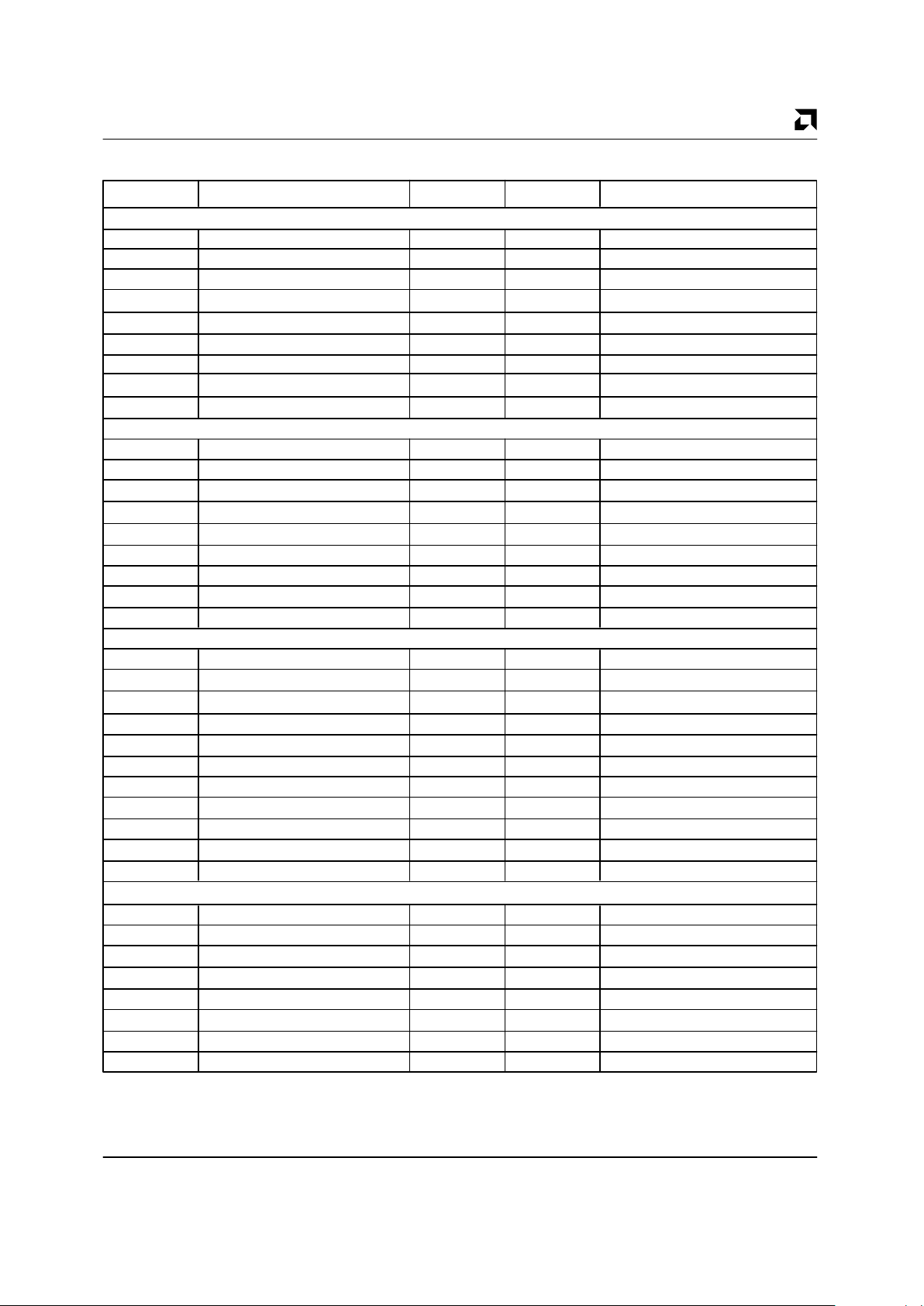

PIN/PACKAGE SUMMARY (continued)

PLCC Pin # Pin Name Pin Function

43 FDS FIFO Data Strobe

44 BE0 Byte Enable0

45 BE1 Byte Enable1

46 SCLK System Clock

47 TDTREQ Transmit Data Transfer Request

48 RDTREQ Receive Data Transfer Request

49 ADD0 Address0

50 ADD1 Address1

51 ADD2 Address2

52 ADD3 Address3

53 ADD4 Address4

54 R/W Read/Write

55 CS Chip Select

56 RXPOL Receive Polarity

57 LNKST Link Status

58 TDO Test Data Out

59 TMS Test Mode Select

60 TCK Test Clock

61 DV

SS

Digital Ground

62 TDI Test Data Input

63 DV

DD

Digital Power

64 RXD– Receive Data–

65 RXD+ Receive Data+

66 AV

DD

Analog Power

67 TXP– Transmit Pre-distortion

68 TXD– Transmit Data–

69 TXP+ Transmit Pre–distortion+

70 TXD+ Transmit Data+

71 AV

DD

Analog Power

72 XTAL1 Crystal Input

73 AV

SS

Analog Ground

74 XTAL2 Crystal Output

75 AV

SS

Analog Ground

76 DO– Data Out–

77 DO+ Data Out+

78 AV

DD

Analog Power

79 DI– Data In–

80 DI+ Data In+

81 CI– Control In–

82 CI+ Control In+

83 AV

DD

Analog Power

84 DV

DD

Digital Power

AMD

13Am79C940

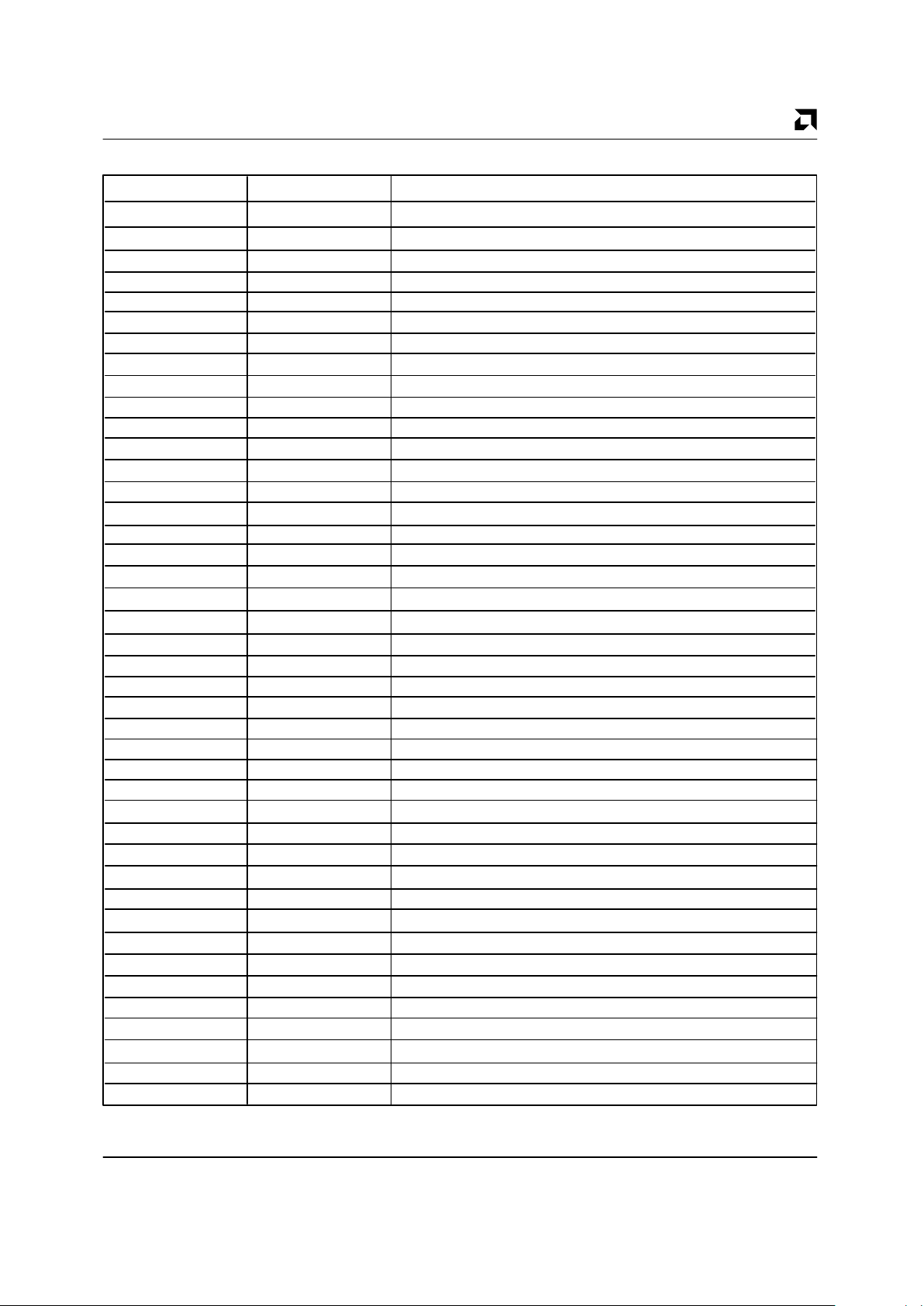

PIN/PACKAGE SUMMARY (continued)

PQFP Pin # Pin Name Pin Function

1 NC No Connect

2 NC No Connect

3 NC No Connect

4 NC No Connect

5 SRDCLK Serial Receive Data Clock

6 EAM/R External Address Match/Reject

7 SRD Serial Receive Data

8 SF/BD Start Frame/Byte Delimiter

9 RESET Reset

10 SLEEP Sleep Mode

11 DVDD Digital Power

12 INTR Interrupt

13 TC Timing Control

14 DBUS0 Data Bus0

15 DV

SS

Digital Ground

16 DBUS1 Data Bus1

17 DBUS2 Data Bus2

18 DBUS3 Data Bus3

19 DBUS4 Data Bus4

20 DV

SS

Digital Ground

21 DBUS5 Data Bus5

22 DBUS6 Data Bus6

23 DBUS7 Data Bus7

24 DBUS8 Data Bus8

25 DBUS9 Data Bus9

26 NC No Connect

27 NC No Connect

28 NC No Connect

29 DBUS10 Data Bus10

30 NC No Connect

31 DBUS11 Data Bus11

32 DBUS12 Data Bus12

33 DBUS13 Data Bus13

34 DV

DD

Digital Power

35 DBUS14 Data Bus14

36 DBUS15 Data Bus15

37 DV

SS

Digital Ground

38 EOF End Of Frame

39 DTV Data Transfer Valid

40 FDS FIFO Data Strobe

41 BE0 Byte Enable0

42 BE1 Byte Enable1

AMD

14 Am79C940

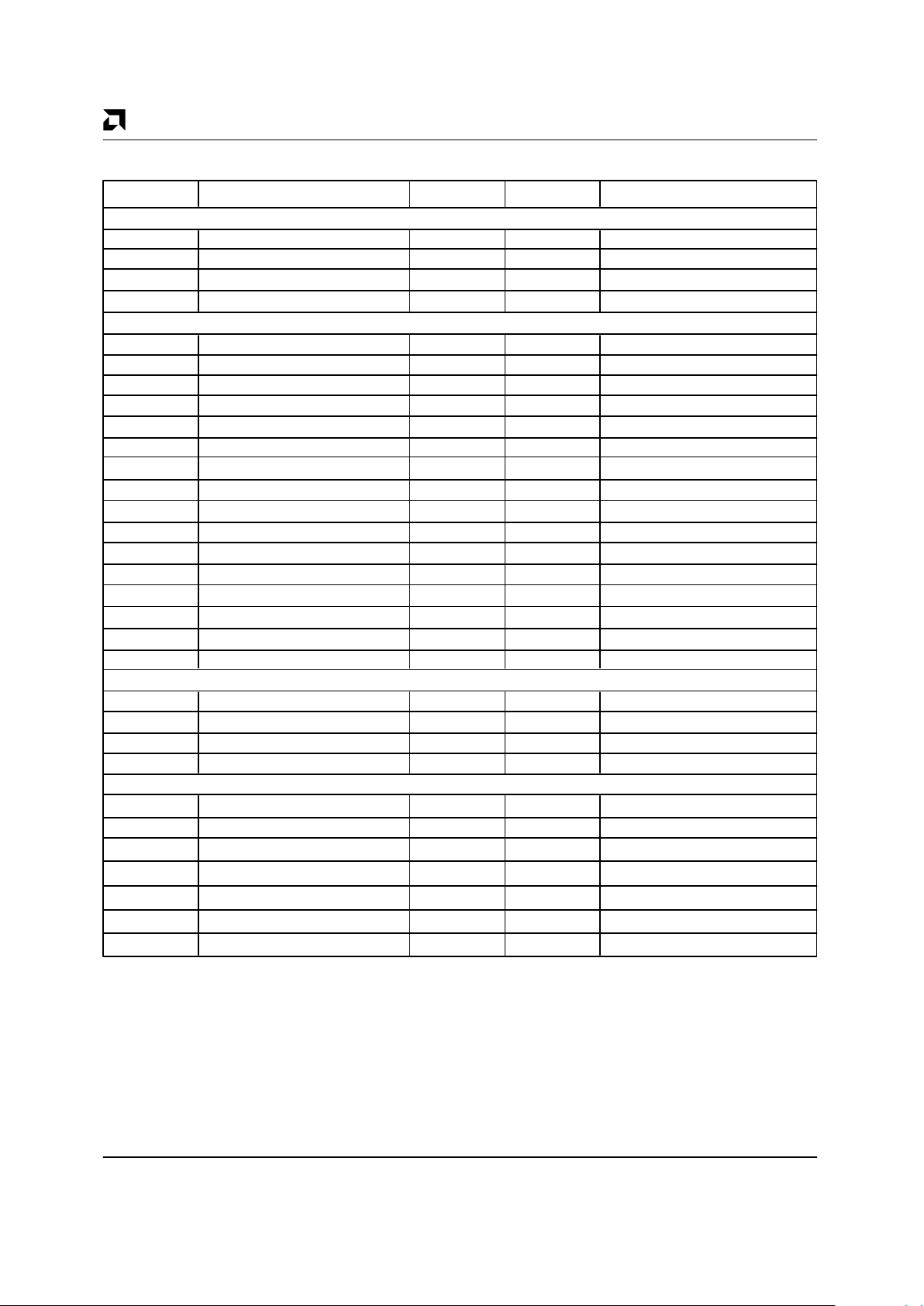

PIN/PACKAGE SUMMARY (continued)

PQFP Pin # Pin Name Pin Function

43 SCLK System Clock

44 TDTREQ Transmit Data Transfer Request

45 RDTREQ Receive Data Transfer Request

46 ADD0 Address0

47 ADD1 Address1

48 ADD2 Address2

49 ADD3 Address3

50 ADD4 Address4

51 NC No Connect

52 NC No Connect

53 NC No Connect

54 NC No Connect

55 R/W Read/Write

56 CS Chip Select

57 RXPOL Receive Polarity

58 LNKST Link Status

59 TDO Test Data Out

60 TMS Test Mode Select

61 TCK Test Clock

62 DV

SS

Digital Ground

63 TDI Test Data Input

64 DV

DD

Digital Power

65 RXD– Receive Data–

66 RXD+ Receive Data+

67 AV

DD

Analog Power

68 TXP– Transmit Pre-distortion–

69 TXD– Transmit Data–

70 TXP+ Transmit Pre-distortion+

71 TXD+ Transmit Data+

72 AV

DD

Analog Power

73 XTAL1 Crystal Input

74 AV

SS

Analog Ground

75 XTAL2 Crystal Output

76 NC No Connect

77 NC No Connect

78 NC No Connect

79 AV

SS

Analog Ground

80 NC No Connect

81 DO– Data Out–

82 DO+ Data Out+

83 AV

DD

Analog Power

84 DI– Data In–

85 DI+ Data In+

AMD

15Am79C940

PIN/PACKAGE SUMMARY (continued)

PQFP Pin # Pin Name Pin Function

86 CI– Control In–

87 CI+ Control In+

88 AV

DD

Analog Power

89 DV

DD

Digital Power

90 DXCVR Disable Transceiver

91 EDSEL Edge Select

92 DV

SS

Digital Ground

93 TXDAT+ Transmit Data +

94 TXDAT– Transmit Data –

95 DV

SS

Digital Ground

96 STDCLK Serial Transmit Data Clock

97 TXEN/TXEN Transmit Enable

98 CLSN Collision

99 RXDAT Receive Data

100 RXCRS Receive Carrier Sense

AMD

16 Am79C940

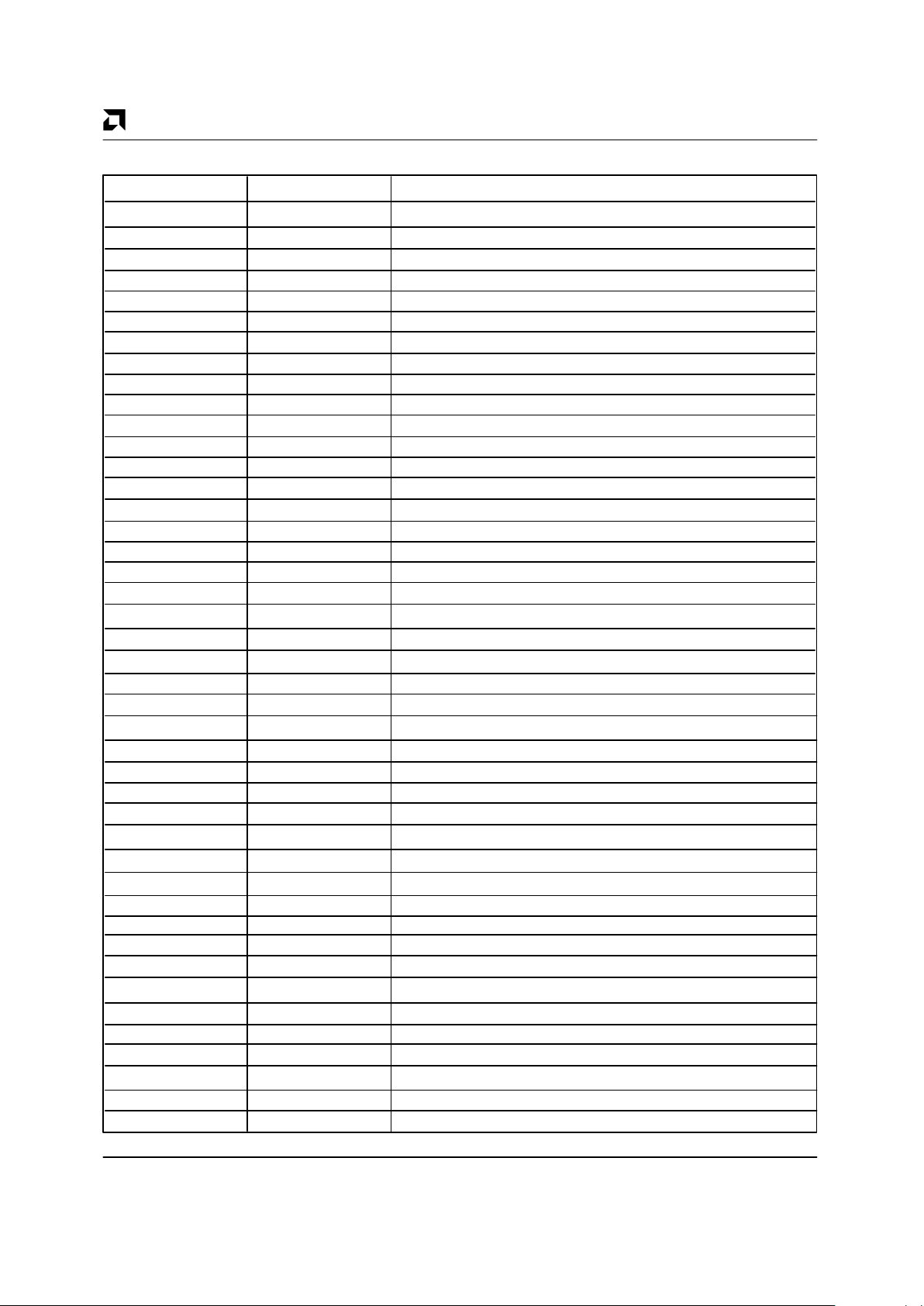

PIN/PACKAGE SUMMARY (continued)

TQFP TQFP

Pin Number Pin Name Pin Function Pin Number Pin Name Pin Function

1 SRDCLK Serial Receive Data Clock 41 R/W Read/Write

2 EAM/R External Address Match/Reject 42 CS Chip/Select

3 SF/BD Start Frame/Byte Delimiter 43 LNKST Link Status

4 RESET Reset 44 TDO Test Data Out

5 SLEEP Sleep Mode 45 TMS Test Mode Select

6 DVDD Digital Power 46 TCK Test Clock

7 INTR Interrupt 47 DVSS Digital Ground

8 TC Timing Control 48 TDI Test Data Input

9 DBUS0 Data Bus0 49 DVDD Digital Power

10 DVSS Digital Ground 50 RXD– Receive Data–

11 DBUS1 Data Bus1 51 RXD+ Receive Data+

12 DBUS2 Data Bus2 52 AVDD Analog Power

13 DBUS3 Data Bus3 53 TXP– Transmit Pre-distortion–

14 DBUS4 Data Bus4 54 TXD– Transmit Data–

15 DVSS Digital Ground 55 TXP+ Transmit Pre-distortion+

16 DBUS5 Data Bus5 56 TXD+ Transmit Data+

17 DBUS6 Data Bus6 57 AVDD Analog Power

18 DBUS7 Data Bus7 58 XTAL1 Crystal Output

19 DBUS8 Data Bus8 59 AVSS Analog Ground

20 DBUS9 Data Bus9 60 XTAL2 Crystal Output

21 DBUS10 Data Bus10 61 AVSS Analog Ground

22 DBUS11 Data Bus11 62 DO– Data Out–

23 DBUS12 Data Bus12 63 DO+ Data Out+

24 DBUS13 Data Bus13 64 AVDD Analog Power

25 DVDD Digital Power 65 DI– Data In–

26 DBUS14 Data Bus14 66 DI+ Data Out+

27 DBUS15 Data Bus15 67 CI– Control In–

28 DVSS Digital Ground 68 CI+ Control In+

29 EOF End of Frame 69 AVDD Analog Power

30 FDS FIFO Data Strobe 70 DVDD Digital Power

31 BE0 Byte Enable0 71 DXCVR Disable Transceiver

32 BE1 Byte Enable1 72 EDSEL Edge Select

33 SCLK System Clock 73 DVSS Digital Ground

34 TDTREQ Transmit Data Transfer Request 74 TXDAT+ Transmit Data+

35 RDTREQ Receive Data Transfer Request 75 DVSS Digital Ground

36 ADD0 Address0 76 STDCLK Serial Transmit Data Clock

37 ADD1 Address1 77 TXEN/TXEN Transmit Enable

38 ADD2 Address2 78 CLSN Collision

39 ADD3 Address3 79 RXDAT Receive Data

40 ADD4 Address4 80 RXCRS Receive Carrier Sense

AMD

17Am79C940

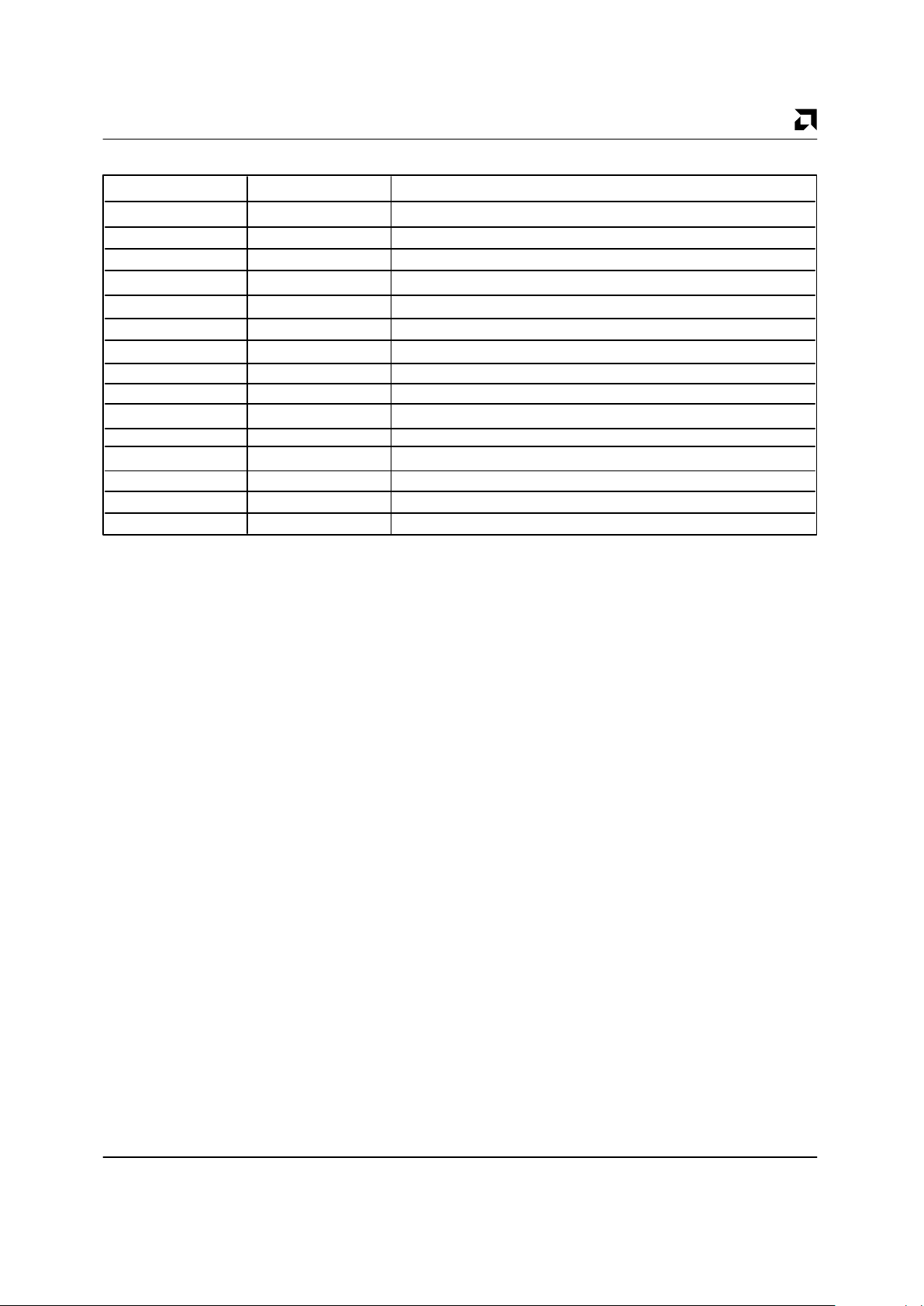

PIN SUMMARY

Pin Name Pin Function Type Active Comment

Attachment Unit Interface (AUI)

DO+/DO– Data Out O Pseudo-ECL

DI+/DI– Data In I Pseudo-ECL

CI+/CI– Control In I Pseudo-ECL

RXCRS Receive Carrier Sense I/O High TTL output. Input in DAI, GPSI port

TXEN Transmit Enable O High TTL. TXEN in DAI port

CLSN Collision I/O High TTL output. Input in GPSI

DXCVR Disable Transceiver O Low TTL low

STDCLK Serial Transmit Data Clock I/O Output. Input in GPSI

SRDCLK Serial Receive Data Clock I/O Output. Input in GPSI

Digital Attachment Interface (DAI)

TXDAT+ Transmit Data + O High TTL. See also GPSI

TXDAT– Transmit Data – O Low TTL

TXEN Transmit Enable O Low TTL. See TXEN in GPSI

RXDAT Receive Data I TTL. See also GPSI

RXCRS Receive Carrier Sense I/O High TTL input. Output in AUI

CLSN Collision I/O High TTL output. Input in GPSI

DXCVR Disable Transceiver O High TTL high

STDCLK Serial Transmit Data Clock I/O Output. Input in GPSI

SRDCLK Serial Receive Data Clock I/O Output. Input in GPSI

10BASE–T Interface

TXD+/TXD– Transmit Data O

TXP+/TXP– Transmit Pre-distortion O

RXD+/RXD– Receive Data I

LNKST Link Status O Low Open Drain

RXPOL Receive Polarity O Low Open Drain

TXEN Transmit Enable O High TTL. TXEN in DAI port

RXCRS Receive Carrier Sense I/O High TTL output. Input in DAI, GPSI port

CLSN Collision I/O High TTL output. Input in GPSI

DXCVR Disable Transceiver O High TTL high

STDCLK Serial Transmit Data Clock I/O Output. Input in GPSI

SRDCLK Serial Receive Data Clock I/O Output. Input in GPSI

General Purpose Serial Interface (GPSI)

STDCLK Serial Transmit Data Clock I/O Input

TXDAT+ Transmit Data + O High TTL. See also DAI port

TXEN Transmit Enable O High TTL. TXEN in DAI port

SRDCLK Serial Receive Data Clock I/O Input. See also EADI port

RXDAT Receive Data I TTL. See also DAI port

RXCRS Receive Carrier Sense I/O High TTL input. Output in AUI

CLSN Collision I/O High TTL input

DXCVR Disable Transceiver O Low TTL low

AMD

18 Am79C940

PIN SUMMARY (continued)

Pin Name Pin Function Type Active Comment

External Address Detection Interface (EADI)

SF/BD Start Frame/Byte Delimiter O High

SRD Serial Receive Data O High

EAM/R External Address Match/Reject I Low

SRDCLK Serial Receive Data Clock I/O Output except in GPSI

Host System Interface

DBUS15–0 Data Bus I/O High

ADD4–0 Address I High

R/W Read/Write I High/Low

RDTREQ Receive Data Transfer Request O Low

TDTREQ Transmit Data Transfer Request O Low

DTV Data Transfer Valid O Low Tristate

EOF End Of Frame I/O Low

BE0 Byte Enable 0 I Low

BE1 Byte Enable 1 I Low

CS Chip Select I Low

FDS FIFO Data Strobe I Low

INTR Interrupt O Low Open Drain

EDSEL Edge Select I High

TC Timing Control I Low Internal pull-up

SCLK System Clock I High

RESET Reset I Low

IEEE 1149.1 Test Access Port (TAP) Interface

TCK Test Clock I Internal pull-up

TMS Test Mode Select I Internal pull-up

TDI Test Data Input I Internal pull-up

TDO Test Data Out O

General Interface

XTAL1 Crystal Input I CMOS

XTAL2 Crystal Output O CMOS

SLEEP Sleep Mode I Low TTL

DV

DD

Digital Power (4 pins) P

DV

SS

Digital Ground (6 pins) P

AV

DD

Analog Power (4 pins) P

AV

SS

Analog Ground (2 pins) P

AMD

19Am79C940

PIN DESCRIPTION

Network Interfaces

The MACE device has five potential network interfaces.

Only one of the interfaces that provides physical network attachment can be used (active) at any time. Selection between the AUI, 10BASE-T, DAI or GPSI ports

is provided by programming the PHY Configuration

Control register. The EADI port is effectively active at all

times. Some signals, primarily used for status reporting,

are active for more than one single interface (the CLSN

pin for instance). Under each of the descriptions for the

network interfaces, the primary signals which are

unique to that interface are described. Where signals

are active for multiple interfaces, they are described

once under the interface most appropriate.

Attachment Unit Interface (AUI)

CI+/CI

Control In

(Input)

A differential input pair, signalling the MACE device that

a collision has been detected on the network media, indicated by the CI± inputs being exercised with 10 MHz

pattern of sufficient amplitude and duration. Operates at

pseudo-ECL levels.

DI+/DI

Data In

(Input)

A differential input pair to the MACE device for receiving

Manchester encoded data from the network. Operates

at pseudo-ECL levels.

DO+/DO

Data Out

(Output)

A differential output pair from the MACE device for

transmitting Manchester encoded data to the network.

Operates at pseudo-ECL levels.

Digital Attachment Interface (DAI)

TXDAT+/TXDAT–

Transmit Data

(Output)

When the DAI port is selected, TXDAT± are configured

as a complementary pair for Manchester encoded data

output from the MACE device, used to transmit data to a

local external network transceiver. During valid transmission (indicated by TXEN low), a logical

1

is indicated

by the TXDAT+ pin being in the high state and TXDAT–

in the low state; and a logical

0

is indicated by the

TXDAT+ pin being in the low state and TXDAT– in the

high state. During idle (TXEN high), TXDAT+ will be in

the high state, and TXDAT– in the low state. When the

GPSI port is selected, TXDAT+ will provide NRZ data

output from the MAC core, and TXDAT– will be held in

the LOW state. Operates at TTL levels. The operations

of TXDAT+ and TXDAT– are defined in the following

tables:

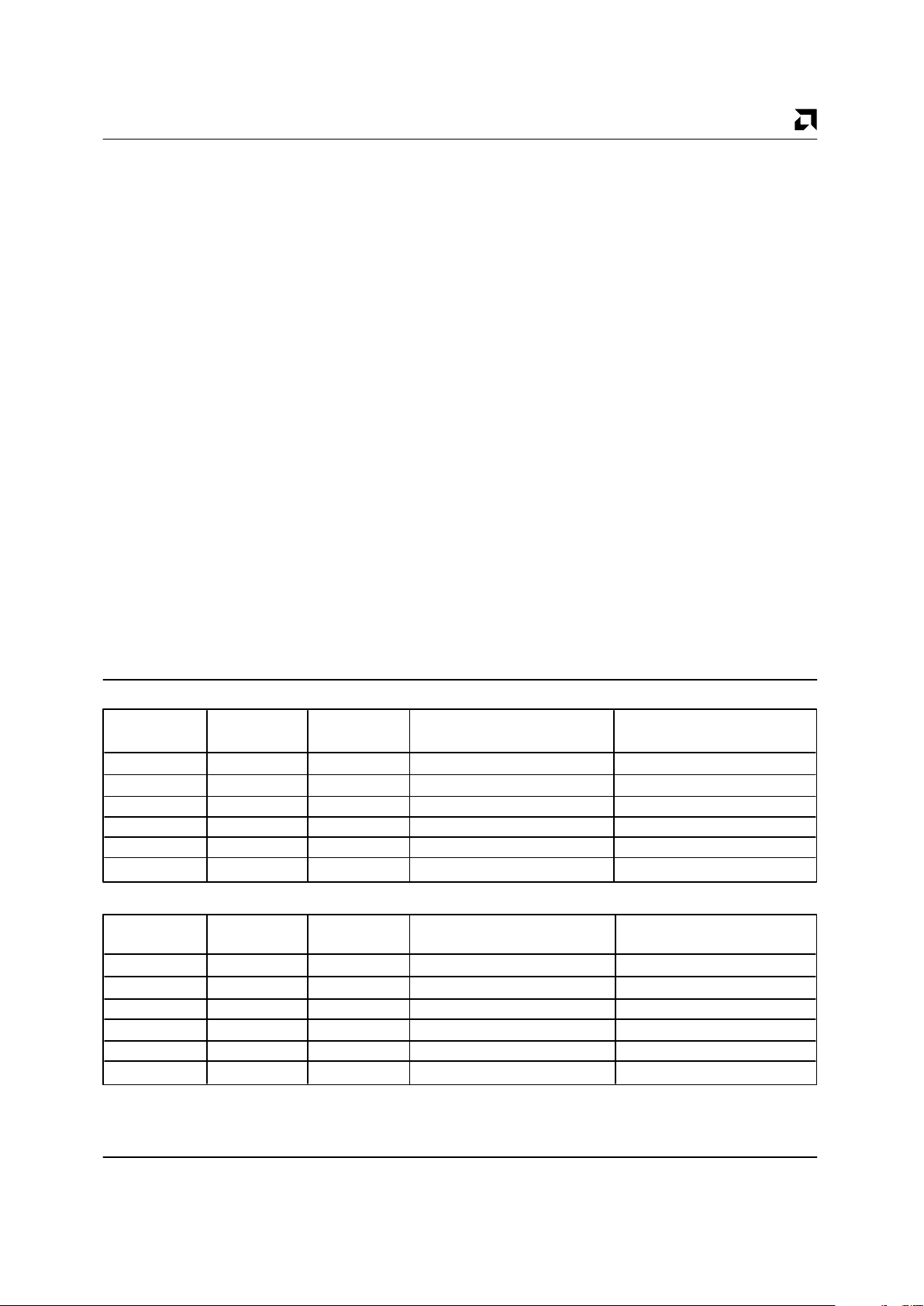

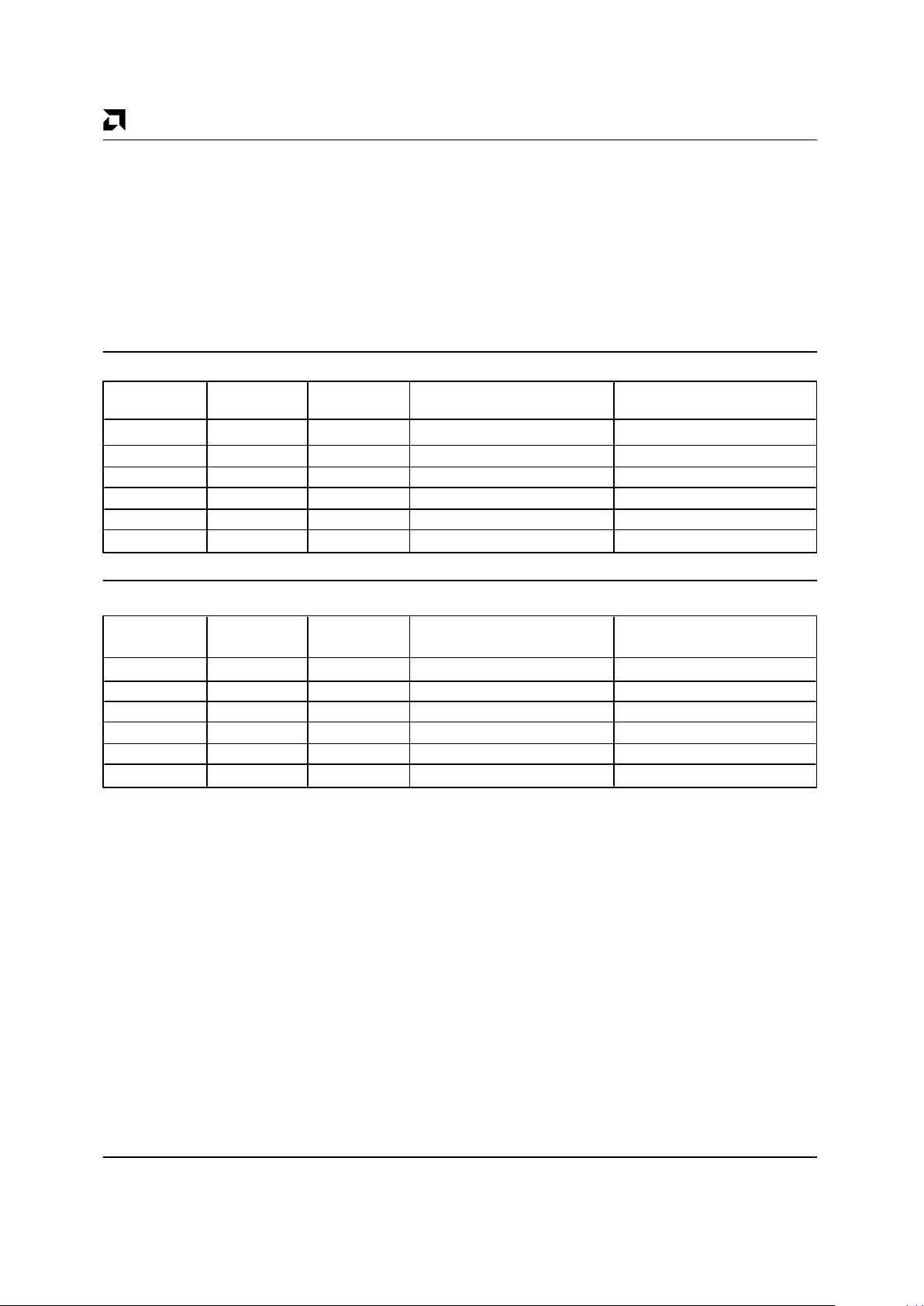

TXDAT+ Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI High Impedance (Note 2)

1 01 1 10BASE-T High Impedance (Note 2)

1 10 1 DAI Port TXDAT+ Output

1 11 1 GPSI TXDAT+ Output

1 XX 0 Status Disabled High Impedance (Note 2)

TXDAT– Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI High Impedance

1 01 1 10BASE-T High Impedance

1 10 1 DAI Port TXDAT– Output

1 11 1 GPSI LOW

1 XX 0 Status Disabled High Impedance

Notes:

1. PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

2. This pin should be externally terminated, if unused, to reduce power consumption.

AMD

20 Am79C940

TXEN/TXEN

Transmit Enable

(Output)

When the AUI port is selected (PORTSEL [1–0] = 00),

an output indicating that the AUI DO± differential output

has valid Manchester encoded data is presented. When

the 10BASE-T port is selected (PORTSEL [1–0] = 01),

indicates that Manchester data is being output on the

TXD±/TXP± complementary outputs. When the DAI

port is selected (PORTSEL [1–0] = 10), indicates that

Manchester data is being output on the DAI port

TXDAT± complementary outputs. When the GPSI port

is selected (PORTSEL [1–0] =11), indicates that NRZ

data is being output from the MAC core of the MACE device, to an external Manchester encoder/decoder, on

the TXDAT+ output. Active low when the DAI port is selected, active high when the AUI, 10 BASE-T or GPSI is

selected. Operates at TTL levels.

RXDAT

Receive Data

(Input)

When the DAI port is selected (PORTSEL [1–0] = 10),

the Manchester encoded data input to the integrated

clock recovery and Manchester decoder of the MACE

device, from an external network transceiver. When the

GPSI port is selected (PORTSEL [1–0] =11), the NRZ

decoded data input to the MAC core of the MACE device, from an external Manchester encoder/decoder.

Operates at TTL levels.

RXCRS

Receive Carrier Sense

(Input/Output)

When the AUI port is selected (PORTSEL [1–0] = 00),

an output indicating that the DI± input pair is receiving

valid Manchester encoded data from the external transceiver which meets the signal amplitude and pulse width

requirements. When the 10BASE-T port is selected

(PORTSEL [1–0] = 01), an output indicating that the

RXD± input pair is receiving valid Manchester encoded

data from the twisted pair cable which meets the signal

amplitude and pulse width requirements. RXCRS will be

asserted high for the entire duration of the receive message. When the DAI port is selected (PORTSEL [1–0] =

10), an input signaling the MACE device that a receive

carrier condition has been detected on the network, and

valid Manchester encoded data is being presented to

the MACE device on the RXDAT line. When the GPSI

port is selected (PORTSEL [1–0] = 11), an input signalling the internal MAC core that valid NRZ data is being

presented on the RXDAT input. Operates at TTL levels.

TXEN/TXEN Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI TXEN Output

1 01 1 10BASE-T TXEN Output

1 10 1 DAI Port TXEN Output

1 11 1 GPSI TXEN Output

1 XX 0 Status Disabled High Impedance (Note 3)

Notes:

1. PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

2. When the GPSI port is selected, TXEN should have an external pull-down attached (e.g. 3.3k

Ω

) to ensure the output is held

inactivebefore ENPLSIO is set.

3. This pin should be externally terminated, if unused, to reduce power consumption.

RXDAT Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI High Impedance (Note 2)

1 01 1 10BASE-T High Impedance (Note 2)

1 10 1 DAI Port RXDAT Input

1 11 1 GPSI RXDAT Input

1 XX 0 Status Disabled High Impedance (Note 2)

Notes:

1. PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

2. This pin should be externally terminated, if unused, to reduce power consumption.

AMD

21Am79C940

RXCRS Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI RXCRS Output

1 01 1 10BASE-T RXCRS Output

1 10 1 DAI Port RXCRS Input

1 11 1 GPSI RXCRS Input

1 XX 0 Status Disabled High Impedance (Note 2)

Notes:

1. PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

2. This pin should be externally terminated, if unused, to reduce power consumption.

DXCVR

Disable Transceiver

(Output)

An output from the MACE device to indicate the network

port in use, as programmed by the ASEL bit or the

PORTSEL [1–0] bits. The output is provided to allow

power down of an external DC-to-DC converter, typically used to provide the voltage requirements for an external 10BASE2 transceiver.

When the Auto Select (ASEL) feature is enabled, the

state of the PORTSEL [1–0] bits is overridden, and the

network interface will be selected by the MACE device,

dependent only on the status of the 10BASE-T link. If the

link is active (LNKST pin driven LOW) the 10BASE-T

port will be used as the active network interface. If the

link is inactive (LNKST pin pulled HIGH) the AUI port will

be used as the active network interface. Auto Select will

continue to operate even when the SLEEP pin is asserted if the RWAKE bit has been set. The AWAKE bit

does not allow the Auto Select function, and only the receive section of 10BASE-T port will be active (DXCVR =

HIGH).

Active (HIGH) when either the 10BASE-T or DAI port is

selected. Inactive (LOW) when the AUI or GPSI port is

selected.

DXCVR Configuration—SLEEP Operation

SLEEP RWAKE AWAKE ASEL LNKST PORTSEL Interface Pin

Pin Bit Bit Bit Pin [1–0] Bits Description Function

0 0 0 X High XX Sleep High

Impedance Mode Impedance

0 1 0 0 High 00 AUI with EADI port LOW

Impedance

0 1 0 0 High 01 10BASE-T with EADI port HIGH

Impedance

0 1 0 0 High 10 Invalid HIGH

Impedance

0 1 0 0 High 11 Invalid LOW

Impedance

0 1 0 1 High 0X AUI with EADI port LOW

Impedance

0 1 0 1 High 0X 10BASE-T with EADI port HIGH

Impedance

0 1 1 1 HIGH 0X AUI with EADI port LOW

0 1 1 1 LOW 0X 10BASE-T with EADI port HIGH

0 0 1 X X 0X 10BASE-T HIGH

Note: RWAKE and ASEL are located in the PHY Configuration Control register (REG ADDR 15). PORTSEL [1–0] and

ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14). All bits must be programmed prior to the

assertion of the

SLEEP

pin.

AMD

22 Am79C940

DXCVR Configuration—Normal Operation

SLEEP ASEL LNKST PORTSEL ENPLSIO Interface Pin

Pin Bit Pin [1–0] Bits Bit Description Function

1 X X XX X SIA Test Mode High

Impedance

1 0 X 00 X AUI LOW

1 0 X 01 X 10BASE-T HIGH

1 0 X 10 X DAI Port HIGH

1 0 X 11 X GPSI LOW

1 1 HIGH 0X X AUI LOW

1 1 LOW 0X X 10BASE-T HIGH

Note: RWAKE and ASEL are located in the PHY Configuration Control register (REG ADDR 15). PORTSEL [1–0] and

ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

10BASE-T Interface

TXD+, TXD–

Transmit Data

(Output)

10BASE-T port differential drivers.

TXP+, TXP–

Transmit Pre-Distortion

(Output)

Transmit wave form differential driver for pre-distortion.

RXD+, RXD–

Receive Data

(Input)

10BASE-T port differential receiver. These pins should

be externally terminated to reduce power consumption if

the 10BASE-T interface is not used.

LNKST

Link Status

(OutputOpen Drain)

This pin is driven LOW if the link is identified as functional. If the link is determined to be nonfunctional, due

to missing idle link pulses or data packets, then this pin

is not driven (requires external pull-up). In the LOW output state, the pin is capable of sinking a maximum of

12 mA and can be used to drive an LED.

This feature can be disabled by setting the Disable Link

Test (DLNKTST) bit in the PHY Configuration Control

register. In this case the internal Link Test Receive function is disabled, the LNKST pin will be driven LOW, and

the Transmit and Receive functions will remain active

regardless of arriving idle link pulses and data. The internal 10BASE-T MAU will continue to generate idle link

pulses irrespective of the status of the DLNKTST bit.

RXPOL

Receive Polarity

(Output, Open Drain)

The twisted pair receiver is capable of detecting a receive signal with reversed polarity (wiring error). The

RXPOL pin is normally in the LOW state, indicating correct polarity of the received signal. If the receiver detects

a received packet with reversed polarity, then this pin is

not driven (requires external pull–up) and the polarity of

subsequent packets are inverted. In the LOW output

state, this pin is capable of sinking a maximum of 12mA

and can be used to drive an LED.

The polarity correction feature can be disabled by setting the Disable Auto Polarity Correction (DAPC) bit in

the PHY Configuration Control register. In this case, the

Receive Polarity correction circuit is disabled and the internal receive signal remains non-inverted, irrespective

of the received signal. Note that RXPOL will continue to

reflect the polarity detected by the receiver.

General Purpose Serial Interface (GPSI)

STDCLK

Serial Transmit Data Clock

(Input/Output)

When either the AUI, 10BASE-T or DAI port is selected,

STDCLK is an output operating at one half the crystal or

XTAL1 frequency. STDCLK is the encoding clock for

Manchester data transferred to the output of either the

AUI DO± pair, the 10BASE-T TXD±/TXP± pairs, or the

DAI port TXDAT± pair. When using the GPSI port,

STDCLK is an input at the network data rate, provided

by the external Manchester encode/decoder, to strobe

out the NRZ data presented on the TXDAT+ output.

AMD

23Am79C940

STDCLK Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI STDCLK Output

1 01 1 10BASE-T STDCLK Output

1 10 1 DAI Port STDCLK Output

1 11 1 GPSI STDCLK Input

1 XX 0 Status Disabled High Impedance (Note 2)

Notes:

1. PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

2. This pin should be externally terminated, if unused, to reduce power consumption.

CLSN

Collision

(Input/Output)

An external indication that a collision condition has been

detected by the (internal or external) Medium Attachment Unit (MAU), and that signals from two or more

nodes are present on the network. When the AUI port is

selected (PORTSEL [1–0] = 00), CLSN will be activated

when the CI± input pair is receiving a collision indication

from the external transceiver. CLSN will be asserted

high for the entire duration of the collision detection, but

will not be asserted during the SQE Test message following a transmit message on the AUI. When the

10BASE-T port is selected (PORTSEL [1–0] = 01),

CLSN will be asserted high when simultaneous transmit

and receive activity is detected (logically detected when

TXD±/TXP± and RXD± are both active). When the DAI

port is selected (PORTSEL [1–0] = 10), CLSN will be asserted high when simultaneous transmit and receive activity is detected (logically detected when RXCRS and

TXEN are both active). When the GPSI port is selected

(PORTSEL [1–0] = 11), an input from the external

Manchester encoder/decoder signaling the MACE device that a collision condition has been detected on the

network, and any receive frame in progress should be

aborted.

External Address Detection Interface

(EADI )

SF/BD

Start Frame/Byte Delimiter

(Output)

The external indication that a start of frame delimiter has

been received. The serial bit stream will follow on the

Serial Receive Data pin (SRD), commencing with the

destination address field. SF/BD will go high for 4 bit

times (400 ns) after detecting the second 1 in the SFD of

a received frame. SF/BD will subsequently toggle every

400 ns (1.25 MHz frequency) with the rising edge indicating the start (first bit) in each subsequent byte of the

received serial bit stream. SF/BD will be inactive during

frame transmission.

SRD

Serial Receive Data

(Output)

SRD is the decoded NRZ data from the network. It is

available for external address detection. Note that when

the 10BASE-T port is selected, transition on SRD will

only occur during receive activity. When the AUI or DAI

port is selected, transition on SRD will occur during both

transmit and receive activity.

CLSN Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI CLSN Output

1 01 1 10BASE-T CLSN Output

1 10 1 DAI Port CLSN Output

1 11 1 GPSI CLSN Input

1 XX 0 Status Disabled High Impedance (Note 2)

Notes:

1. PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

2. This pin should be externally terminated, if unused, to reduce power consumption.

AMD

24 Am79C940

EAM/R

External Address Match/Reject

(Input)

The incoming frame will be received dependent on the

receive operational mode of the MACE device, and the

polarity of the EAM/R pin. The EAM/R pin function is

programmed by use of the M/R bit in the Receive Frame

Control register. If the bit is set, the pin is configured as

EAM. If the bit is reset, the pin is configured as EAR.

EAM/R can be asserted during packet reception to ac-

cept or reject packets based on an external address

comparison.

SRDCLK

Serial Receive Data Clock

(Input/Output)

The Serial Receive Data (SRD) output is synchronous

to SRDCLK running at the 10MHz receive data clock frequency. The pin is configured as an input, only when the

GPSI port is selected. Note that when the 10BASE-T

port is selected, transition on SRDCLK will only occur

during receive activity. When the AUI or DAI port is selected, transition on SRDCLK will occur during both

transmit and receive activity.

SRD Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI SRD Output

1 01 1 10BASE-T SRD Output

1 10 1 DAI Port SRD Output

1 11 1 GPSI SRD Output

1 XX 0 Status Disabled High Impedance

Note: PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

SRDCLK Configuration

PORTSEL

SLEEP [1–0] ENPLSIO Interface Description Pin Function

0 XX X Sleep Mode High Impedance

1 00 1 AUI SRDCLK Output

1 01 1 10BASE-T SRDCLK Output

1 10 1 DAI Port SRDCLK Output

1 11 1 GPSI SRDCLK Input

1 XX 0 Status Disabled High Impedance (Note 2)

Notes:

1. PORTSEL [1–0] and ENPLSIO are located in the PLS Configuration Control register (REG ADDR 14).

2. This pin should be externally terminated, if unused, to reduce power consumption.

AMD

25Am79C940

HOST SYSTEM INTERFACE

DBUS15–0

Data Bus (

Input/Output/3-state)

DBUS contains read and write data to and from internal

registers and the Transmit and Receive FIFOs.

ADD4–0

Address Bus

(Input)

ADD is used to access the internal registers and FIFOs

to be read or written.

R/W

Read/Write

(Input)

Indicates the direction of data flow during the MACE device register, Transmit FIFO, or Receive FIFO

accesses.

RDTREQ

Receive Data Transfer Request

(Output)

Receive Data Transfer Request indicates that there is

data in the Receive FIFO to be read. When RDTREQ is

asserted there will be a minimum of 16 bytes to be read

except at the completion of the frame, in which case

EOF will be asserted. RDTREQ can be programmed to

request receive data transfer when 16, 32 or 64 bytes

are available in the Receive FIFO, by programming the

Receive FIFO Watermark (RCVFW bits) in the FIFO

Configuration Control register. The first assertion of

RDTREQ will not occur until at least 64 bytes have been

received, and the frame has been verified as non runt.

Runt packets will normally be deleted from the Receive

FIFO with no external activity on RDTREQ. When Runt

Packet Accept is enabled (RPA bit) in the User Test

Register, RDTREQ will be asserted when the runt pack-

et completes, and the entire frame resides in the

Receive FIFO. RDTREQ will be asserted only when Enable Receive (ENRCV) is set in the MAC Configuration

Control register.

The RCVFW can be overridden by enabling the Low Latency Receive function (setting LLRCV bit) in the Receive Frame Control register, which allows RDTREQ to

be asserted after only 12 bytes have been received.

Note that use of this function exposes the system interface to premature termination of the receive frame, due

to network events such as collisions or runt packets. It is

the responsibility of the system designer to provide adequate recovery mechanisms for these conditions.

TDTREQ

Transmit Data Transfer Request

(Output)

Transmit Data Transfer Request indicates there is room

in the Transmit FIFO for more data. TDTREQ is asserted when there are a minimum of 16 empty bytes in

the Transmit FIFO. TDTREQ can be programmed to request transmit data transfer when 16, 32 or 64 bytes are

available in the Transmit FIFO, by programming the

Transmit FIFO Watermark (XMTFW bits) in the FIFO

Configuration Control register. TDTREQ will be

asserted only when Enable Transmit (ENXMT) is set in

the MAC Configuration Control register.

FDS

FIFO Data Select

(Input)

FIFO Data Select allows direct access to the transmit or

Receive FIFO without use of the ADD address bus. FDS

must be activated in conjunction with R/W. When the

MACE device samples R/W as high and FDS low, a read

cycle from the Receive FIFO will be initiated. When the

MACE chip samples R/W and FDS low, a write cycle to

the Transmit FIFO will be initiated. The CS line should

be inactive (high) when FIFO access is requested using

the FDS pin. If the MACE device samples both CS and

FDS as active simultaneously, no cycle will be executed, and DTV will remain inactive.

DTV

Data Transfer Valid

(Output/3-state)

When asserted, indicates that the read or write operation has completed successfully. The absence of DTV at

the termination of a host access cycle on the MACE device indicates that the data transfer was unsuccessful.

DTV need not be used if the system interface can guarantee that the latency to TDTREQ and RDTREQ assertion and de-assertion will not cause the Transmit FIFO

to be over-written or the Receive FIFO to be over-read.

In this case, the latching or strobing of read or write data

can be synchronized to the SCLK input rather than to the

DTV output.

EOF

End Of Frame

(Input/Output/3–state)

End Of Frame will be asserted by the MACE device

when the last byte/word of frame data is read from the

Receive FIFO, indicating the completion of the frame

data field for the receive message. End Of Frame must

be asserted low to the MACE device when the last byte/

word of the frame is written into the Transmit FIFO.

BE1–0

Byte Enable

(Input)

Used to indicate the active portion of the data transfer to

or from the internal FIFOs. For word (16-bit) transfers,

both BE0 and BE1 should be activated by the external

host/controller. Single byte transfers are performed by

identifying the active data bus byte and activating only

one of the two signals. The function of the BE1–0 pins is

programmed using the BSWP bit (BIU Configuration

Control register, bit 6). BE1–0 are not required for accesses to MACE device registers.

CS

Chip Select

(Input)

Used to access the MACE device FIFOs and internal

registers locations using the ADD address bus. The

FIFOs may alternatively be directly accessed without

supplying the FIFO address, by using the FDS and

R/W pins.

AMD

26 Am79C940

INTR

Interrupt

(Output, Open Drain)

An attention signal indicating that one or more of the following status flags are set: XMTINT, RCVINT, MPCO,

RPCO, RCVCCO, CERR, BABL or JAB. Each interrupt

source can be individually masked. No interrupt condition can take place in the MACE device immediately after a hardware or software reset.

RESET

Reset

(Input)

Reset clears the internal logic. Reset can be asynchronous to SCLK, but must be asserted for a minimum

duration of 15 SCLK cycles.

SCLK

System Clock

(Input)

The system clock input controls the operational frequency of the slave interface to the MACE device and

the internal processing of frames. SCLK is unrelated to

the 20 MHz clock frequency required for the

802.3/Ethernet interface. The SCLK frequency range is

1 MHz–25 MHz.

EDSEL

System Clock Edge Select

(Input)

EDSEL is a static input that allows System Clock

(SCLK) edge selection. If EDSEL is tied high, the bus interface unit will assume falling edge timing. If EDSEL is

tied low, the bus interface unit will assume rising edge

timing, which will effectively invert the SCLK as it enters

the MACE device, i.e., the address, control lines (CS,

R/W, FDS, etc) and data are all latched on the rising

edge of SCLK, and data out is driven off the rising edge

of SCLK.

TC

Timing Control

(Input)

The Timing Control input conditions the minimum number of System Clocks (SCLK) cycles taken to read or

write the internal registers and FIFOs. TC can be used

as a wait state generator, to allow additional time for

data to be presented by the host during a write cycle, or

allow additional time for the data to be latched during a

read cycle. TC has an internal (SLEEP disabled) pull up.

Timing Control

Number of

TC Clocks

12

03

IEEE 1149.1 TEST ACCESS PORT (TAP)

INTERFACE

TCK

Test Clock

(Input)

The clock input for the boundary scan test mode

operation. TCK can operate up to 10 MHz. TCK has an

internal (not SLEEP disabled) pull up.

TMS

Test Mode Select

(Input)

A serial input bit stream used to define the specific

boundary scan test to be executed. TMS has an internal

(not SLEEP disabled) pull up.

TDI

Test Data Input

(Input)

The test data input path to the MACE device. TDI has an

internal (not SLEEP disabled) pull up.

TDO

Test Data Out

(Output)

The test data output path from the MACE device.

GENERAL INTERFACE

XTAL1

Crystal Connection

(Input)

The internal clock generator uses a 20 MHz crystal that

is attached to pins XTAL1 and XTAL2. Internally, the

20 MHz crystal frequency is divided by two which determines the network data rate. Alternatively, an external

20 MHz CMOS-compatible clock signal can be used to

drive this pin. The MACE device supports the use of 50

pF crystals to generate a 20 MHz frequency which is

compatible with the IEEE 802.3 network frequency

tolerance and jitter specifications.

XTAL2

Crystal Connection

(Output)

The internal clock generator uses a 20 MHz crystal that

is attached to pins XTAL1 and XTAL2. If an external

clock generator is used on XTAL1, then XTAL2 should

be left unconnected.

SLEEP

Sleep Mode

(Input)

The optimal power savings made is extracted by asserting the SLEEP pin with both the Auto Wake (AWAKE bit)

and Remote Wake (RWAKE bit) functions disabled. In

this “deep sleep” mode, all outputs will be forced into

their inactive or high impedance state, and all inputs will

be ignored except for the SLEEP, RESET, SCLK, TCK,

AMD

27Am79C940

TMS, and TDI pins. SCLK must run for 5 cycles after the

assertion of SLEEP. During the “Deep Sleep”, the SCLK

input can be optionally suspended for maximum power

savings. Upon exiting “Deep Sleep”, the hardware

RESET pin must be asserted and the SCLK restored.

The system must delay the setting of the bits in the MAC

configuration Control Register of the internal analog

circuits by 1 ns to allow for stabilization.

If the AWAKE bit is set prior to the activation of SLEEP,

the 10BASE-T receiver and the LNKST output pin remain operational.

If the RWAKE bit is set prior to SLEEP being asserted,

the Manchester encoder/decoder, AUI and 10BASE-T

cells remain operational, as do the SRD, SRDCLK and

SF/BD outputs.

The input on XTAL1 must remain active for the AWAKE

or RWAKE features to operate. After exit from the Auto

Wake or Remote Wake modes, activation of hardware

RESET is not required when SLEEP is reasserted.

On deassertion of SLEEP, the MACE device will go

through an internally generated hardware reset sequence, requiring re-initialization of MACE registers.

Power Supply

DV

DD

Digital Power

There are four Digital V

DD

pins.

DV

SS

Digital Ground

There are six Digital V

SS

pins.

AV

DD

Analog Power

There are four analog VDD pins. Special attention

should be paid to the printed circuit board layout to avoid

excessive noise on the supply to the PLL in the

Manchester encoder/decoder (pins 66 and 83 in PLCC,

pins 67 and 88 in PQFP). These supply lines should be

kept separate from the DV

DD

lines as far back to the

power supply as is practically possible.

AV

SS

Analog Ground

There are two analog VSS pins. Special attention

should be paid to the printed circuit board layout to avoid

excessive noise on the PLL supply in Manchester encoder/decoder (pin 73 in PLCC, pin 74 in PQFP). These

supply lines should be kept separate from the DV

SS

lines

as far back to the power supply as is practically possible.

PIN FUNCTIONS NOT AVAILABLE WITH

THE 80-PIN TQFP PACKAGE

In the 84-pin PLCC configuration,

ALL

the pins are used

while in the 100-pin PQFP version, 16 pins are specified

as No Connects. Moving to the 80-pin TQFP configuration requires the removal of 4 pins. Since Ethernet controllers with integrated 10BASE-T have analog portions

which are very sensitive to noise, power and ground

pins are not deleted. The MACE device does have

several sets of media interfaces which typically go unused in most designs, however. Pins from some of

these interfaces are deleted instead. Removed are

the following:

■ TXDAT– (previously used for the DAI interface)

■ SRD (previously used for the EADI interface)

■ DTV (previously used for the host interface)

■ RXPOL (previously used as a receive frame

polarity LED driver)

Note that pins from four separate interfaces are removed rather than removing all the pins from a single interface. Each of these pins comes from one of the four

sides of the device. This is done to maintain symmetry,

thus avoiding bond out problems.

In general, the most critical of the four removed pins are

TXDAT– and SRD. Depending on the application, either

the DAI or the EADI interface may be important. In most

designs, however, this will not be the case.

PINS REMOVED AND THEIR EFFECTS

TXDAT–

The removal of TXDAT– means that the DAI interface is

no longer usable. The DAI interface was designed to be

used with media types that do not require DC isolation

between the MAU and the DTE. Media which do not

require DC isolation can be implemented more simply

using the DAI interface, rather than the AUI interface. In

most designs this is not a problem because most

media requires DC isolation (10BASE-T, 10BASE2,

10BASE5) and will use the AUI port. About the only media which does not require DC isolation is 10BASE-F.

SRD

The SRD pin is an output pin used by the MACE device

to transfer a receive data stream to external address

detection logic. It is part of the EADI interface. This pin is

used to help interface the MACE device to an external

CAM device. Use of an external CAM is typically required when an application will operate in promiscuous

mode and will need perfect filtering (i.e., the internal

hash filter will not suffice). Example applications for this

AMD

28 Am79C940

sort of operation are bridges and routers. Lack of

perfect filtering in these applications forces the CPU to

be more involved in filtering and thus either slows the

forwarding rates achieved or forces the use of a more

powerful CPU.

DTV

The DTV pin is part of the host interface to the MACE

device. It is used to indicate that a read or write cycle to

the MACE device was successful. If DTV is not asserted

at the end of a cycle, the data transfer was not successful. Basically, this will happen on a write to a full transmit

FIFO or a read from an empty receive FIFO. In general,

there are ways to ensure that a transfer is always valid

and so this pin is not required in many designs. For instance, the TDTREQ and RDTREQ pins can be used to

monitor the state of the FIFOs to ensure that data transfer only occurs at the correct times.

RXPOL

RXPOL is typically used to drive an LED indicating the

polarity of receive frames. This function is not necessary for correct operation of the Ethernet and serves

strictly as a status indication to a user. The status of the

receive polarity is still available through the PHYCC

register.

AMD

29Am79C940

FUNCTIONAL DESCRIPTION

The Media Access Controller for Ethernet (MACE) chip

embodies the Media Access Control (MAC) and Physical Signaling (PLS) sub-layers of the 802.3 Standard.

The MACE device provides the IEEE defined Attachment Unit Interface (AUI) for coupling to remote Media

Attachment Units (MAUs) or on-board transceivers.

The MACE device also provides a Digital Attachment Interface (DAI), by-passing the differential AUI interface.

The system interface provides a fundamental data conduit to and from an 802.3 network. The MACE device in

conjunction with a user defined DMA engine, provides

an 802.3 interface tailored to a specific application.

In addition, the MACE device can be combined with

similarly architected peripheral devices and a multichannel DMA controller, thereby providing the system

with access to multiple peripheral devices with a single

master interface to memory.

Network Interfaces

The MACE device can be connected to an 802.3 network using any one of the AUI, 10 BASE-T, DAI and

GPSI network interfaces. The Attachment Unit Interface (AUI) provides an IEEE compliant differential interface to a remote MAU or an on-board transceiver. An