AMD Advanced Micro Devices AM27C1024-90DI, AM27C1024-90DCB, AM27C1024-90DC, AM27C1024-70PI, AM27C1024-70PC Datasheet

...

FINAL

Publication# 06780 Rev: J Amendment/0

Issue Date: May 1998

Am27C1024

1 Megabit (65 K x 16-Bit) CMOS EPROM

DISTINCTIVE CHARACTERISTICS

■ Fast access time

— Speed options as fast as 55 ns

■ Low power consumption

— 20 µA typical CMOS standby current

■ JEDEC-approved pinout

— 40-Pin DIP/PDIP

— 44-Pin PLCC

■ Single +5 V power supply

■ ±10% power supply tolerance standard

■ 100% Flashrite™ programming

— Typical programming time of 8 seconds

■ Latch-up protected to 100 mA from –1 V to

V

CC

+ 1 V

■ High noise immunity

■ Versatile features for simple interfacing

— Both CMOS and TTL input/output compatibility

— Two line control functions

GENERAL DESCRIPTION

The Am27C1024 is a 1 Megabit, ultraviolet erasable

programmable read-only memory. It is orga nize d as 64

Kwords by 16 bits per word, operates fro m a single

+5 V supply, has a static standby mode, and features

fast single address location programming. Products are

available in windowed ceramic DIP packages, as well

as plastic one time programmable (OTP) PDIP and

PLCC packages.

Data can be typically accessed in less than 55 ns, allowing high-p erformance m icroproces sors to ope rate

without any WAIT states. The device offers separate

Output Enable (OE#) and Chip Enable (CE#) controls,

thus eliminating bus contention in a mul tiple bus microprocessor system.

AMD’s CMOS process technology provides high

speed, low power, and high noise immunity. Typical

power consumption is only 125 mW in active mode,

and 100 µW in standby mode.

All signals are TTL levels, including programming signals. Bit locations may be programmed singly, in

blocks, or at random. The device supports AMD’s

Flashrite programming alg orithm (100 µs pulses), resulting in a typical programming time of 8 seconds.

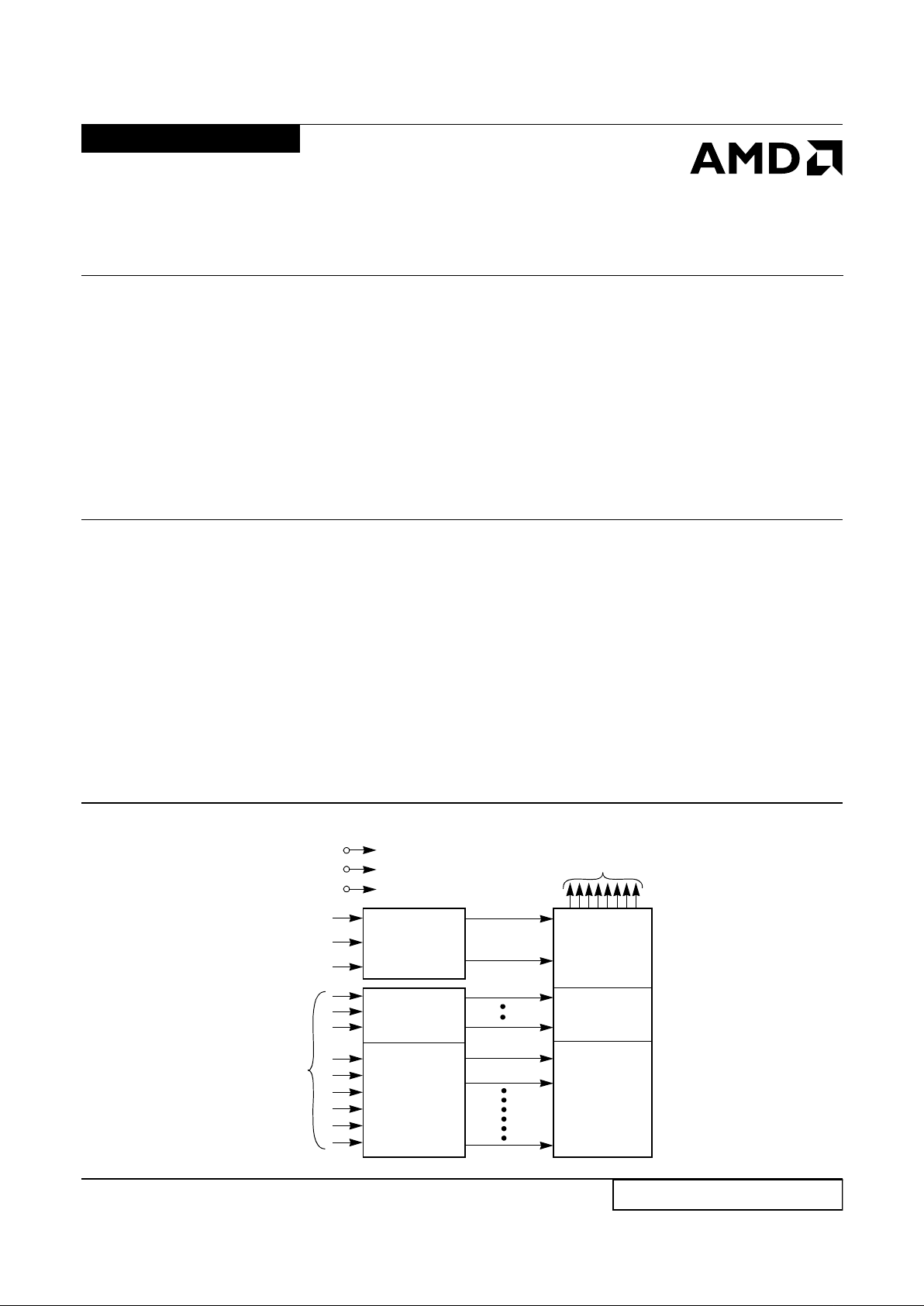

BLOCK DIAGRAM

06780J-1

A0–A15

Address

Inputs

PGM#

CE#

OE#

V

CC

V

SS

V

PP

Data Outputs

DQ0–DQ15

Output

Buffers

Y

Gating

1,048,576

Bit Cell

Matrix

X

Decoder

Y

Decoder

Output Enable

Chip Enable

and

Prog Logic

2 Am27C1024

PRODUCT SELECTOR GUIDE

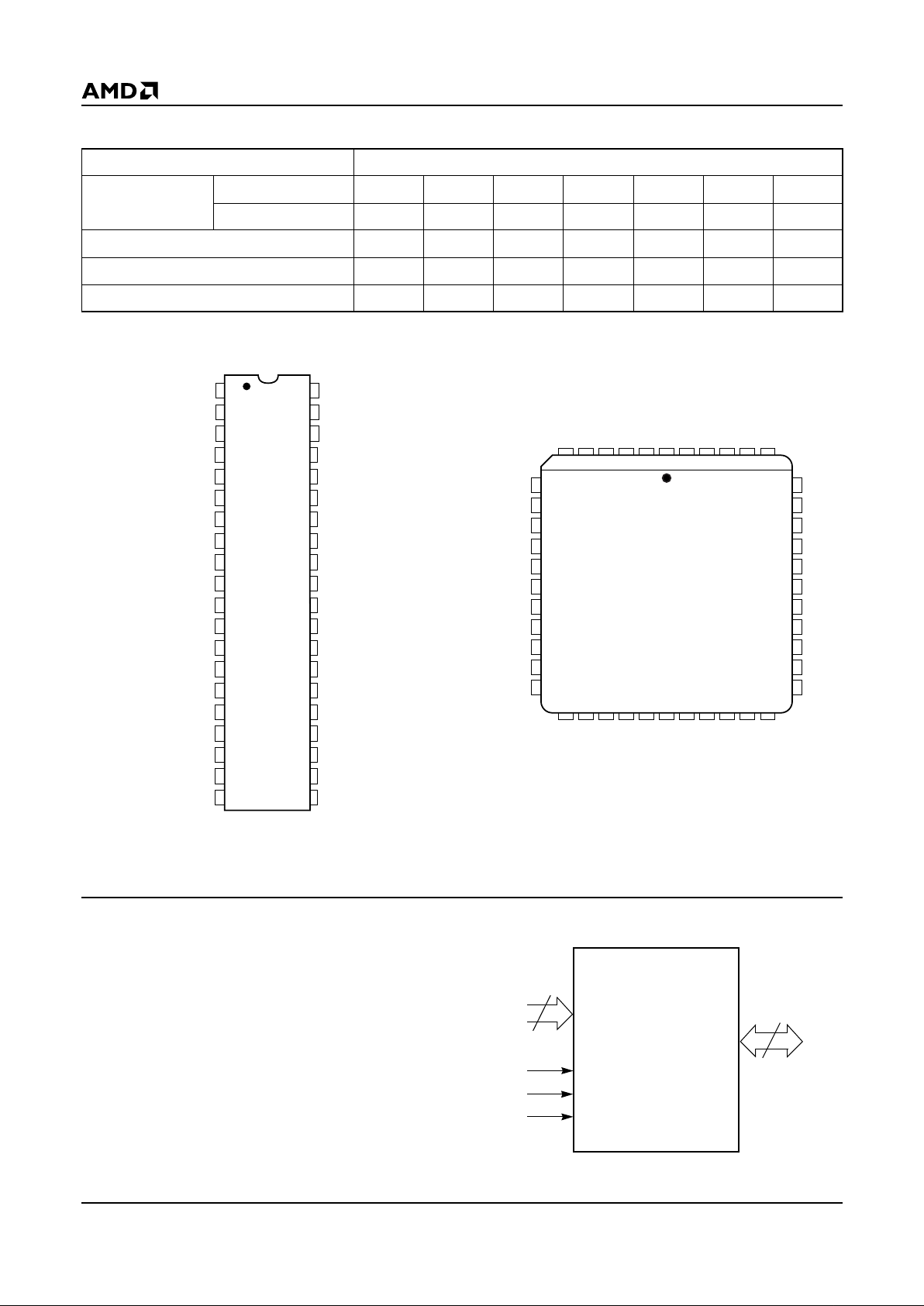

CONNECTION DIAGRAMS

DIP PLCC

Notes:

1. JEDEC nomenclature is in parenthesis.

2. Don’t use (DU) for PLCC.

PIN DESIGNATIONS

A0–A15 = Address Inputs

CE# (E#) = Chip Enable Input

DQ0–DQ15 = Data Input/Outputs

OE# (G#) = Output Enable Input

PGM# (P#) = Program Enable Input

V

CC

=VCC Supply Voltage

V

PP

= Program Voltage Input

V

SS

= Ground

NC = No Internal Connection

LOGIC SYMBOL

Family Part Number Am27C1024

Speed Options

V

CC

= 5.0 V ± 5% -55 -255

V

CC

= 5.0 V ± 10% -55 -70 -90 -120 -150 -200

Max Access Time (ns) 55 70 90 120 150 200 250

CE# (E#) Access (ns) 55 70 90 120 150 200 250

OE# (G#) Access (ns) 40 40 45 50 65 75 75

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

V

CC

PGM# (P#)

NC

A15

A14

A13

A12

A11

A10

A9

V

SS

A8

A7

A6

A5

A4

A3

A2

A1

A0

V

PP

CE# (E#)

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

V

SS

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

OE# (G#)

06780J-2

1 444342543264140

7

8

9

10

11

12

13

14

15

16

17

A13

A12

A11

A10

A9

V

SS

NC

A8

A7

A6

A5

DQ13

DQ14

DQ15

CE (E)

VPPDU (Note 2)

VCCPGM# (P#)NCA15

A14

39

38

37

36

35

34

33

32

31

30

29

DQ12

DQ11

DQ10

DQ9

DQ8

V

SS

NC

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

OE# (G#)

DU (Note 2)

A0A1A2A3A4

23 24 25 2619 20 21 2218 27 28

06780J-3

16

16

DQ0–DQ15

A0–A15

CE# (E#)

OE# (G#)

06780J-4

PGM# (P#)

Am27C1024 3

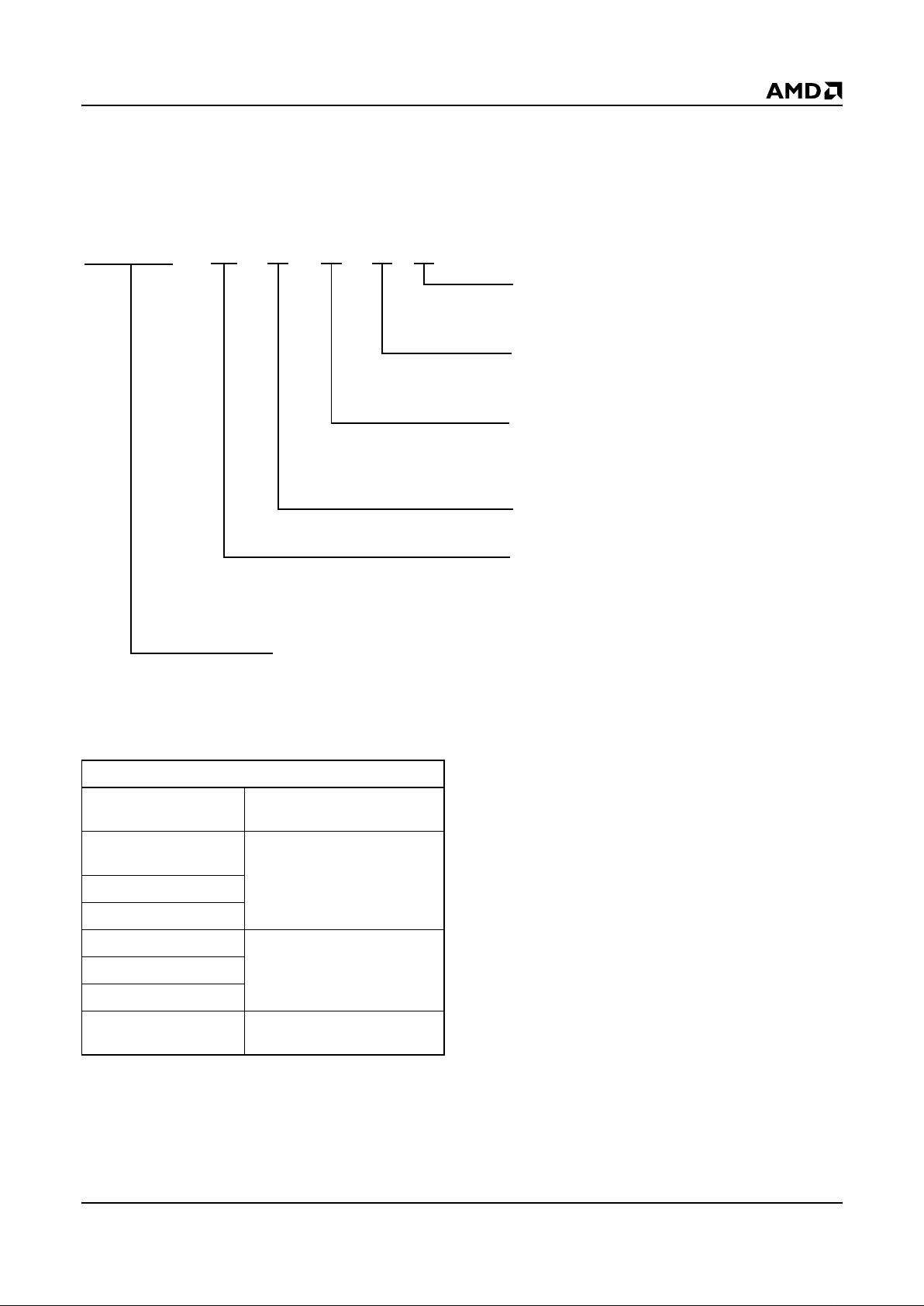

ORDERING INFORMATION

UV EPROM Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed

by a combination of the following:

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales

office to confirm availability of specific valid combinations and

to check on newly released combinations.

DEVICE NUMBER/DESCRIPTION

Am27C1024

1 Megabit (64 K x 16-Bit) CMOS UV EPROM

AM27C1024 -55 D C

OPTIONAL PROCESSING

Blank = Standard Processing

B = Burn-In

VOLTAGE TOLERANCE

5=V

CC

± 5%, 55 ns only

See Product Selector Guide and Valid Combinations

TEMPERATURE RANGE

C = Commercial (0°C to +70

°C)

I=Industrial (–40

°C to +85°C)

E = Extended (–55°C to +125°C)

PACKAGE TYPE

D = 40-Pin Ceramic DIP (CDV040)

SPEED OPTION

See Product Selector Guide and Valid Combinations

5

B

Valid Combinations

AM27C1024-55

V

CC

= 5.0 V ± 5%

DC5, DC5B, DI5, DI5B

AM27C1024-55

V

CC

= 5.0 V ± 10%

DC, DCB, DI, DIB

AM27C1024-70

AM27C1024-90

AM27C1024-120

DC, DCB, DI, DIB, DE, DEBAM27C1024-150

AM27C1024-200

AM27C1024-255

V

CC

= 5.0 V ± 5%

DC, DCB, DI, DIB

4 Am27C1024

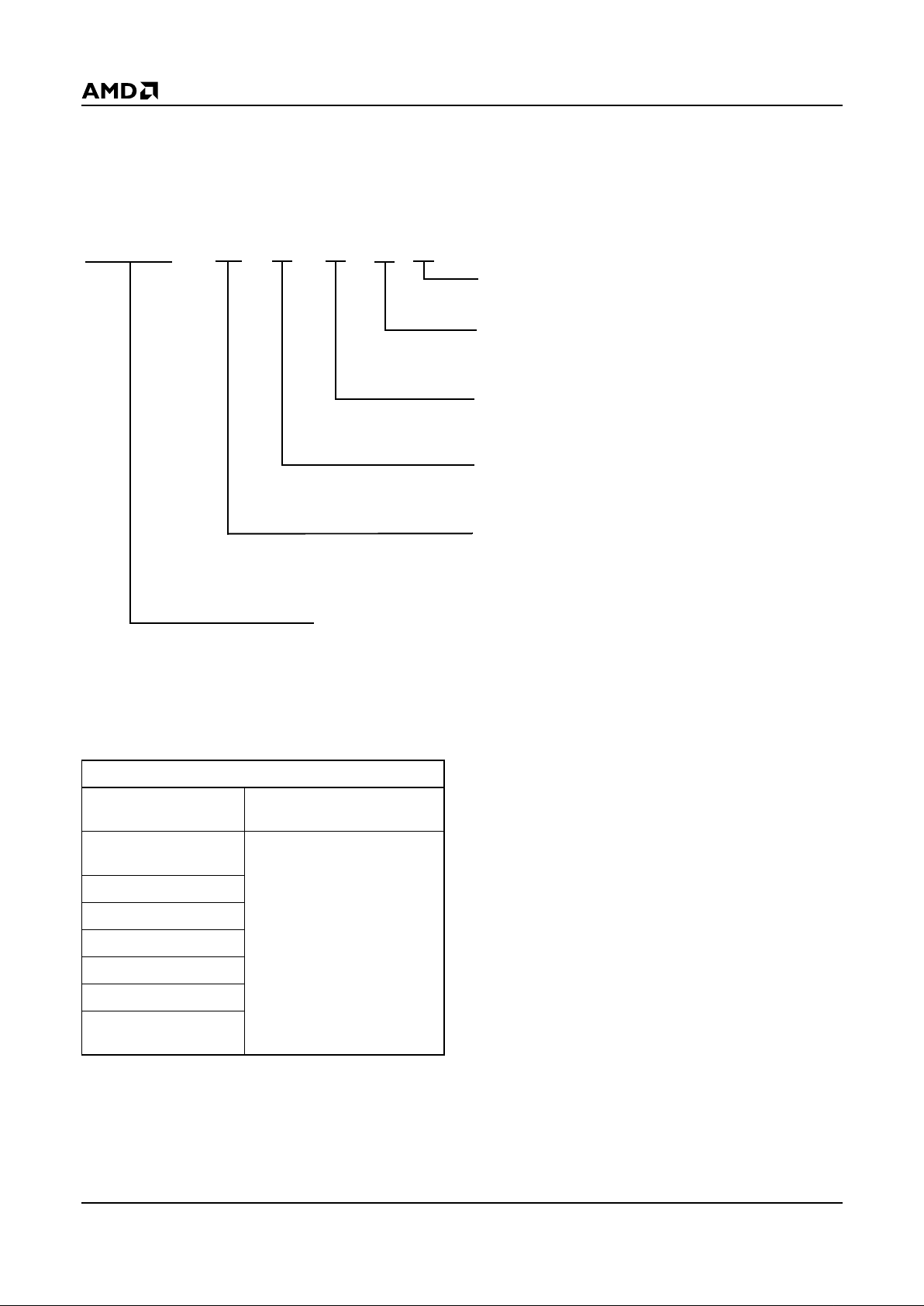

ORDERING INFORMATION

OTP EPROM Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed

by a combination of the following:

Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales

office to confirm availability of specific valid combinations and

to check on newly released combinations.

DEVICE NUMBER/DES CR IP TIO N

Am27C1024

1 Megabit (64 K x 16-Bit) CMOS OTP EPROM

AM27C1024 -55 J C

OPTIONAL PROCESSING

Blank = Standard Processing

VOLTAGE TOLERANCE

5=V

CC

± 5%, 55 ns only

See Product Selector Guide and Valid Combinations

TEMPERATURE RANGE

C = Commercial (0

°C to +70°C)

I=Industrial (–40

°C to +85°C)

PACKAGE TYPE

P = 40-Pin Plastic DIP (PD 040)

J = 44-Pin Plastic Leaded Chip Carrier (PL 044)

SPEED OPTION

See Product Selector Guide and Valid Combinations

5

Valid Combinations

AM27C1024-55

V

CC

= 5.0 V ± 5%

PC5, PI5, JC5, JI5

AM27C1024-55

V

CC

= 5.0 V ± 10%

JC, PC, JI, PI

AM27C1024-70

AM27C1024-90

AM27C1024-120

AM27C1024-150

AM27C1024-200

AM27C1024-255

V

CC

= 5.0 V ± 5%

Loading...

Loading...