Page 1

V-Series Avalon-MM DMA Interface for PCIe Solutions

User Guide

Last updated for Altera Complete Design Suite: 14.1

Subscribe

Send Feedback

UG-01154

2014.12.18

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

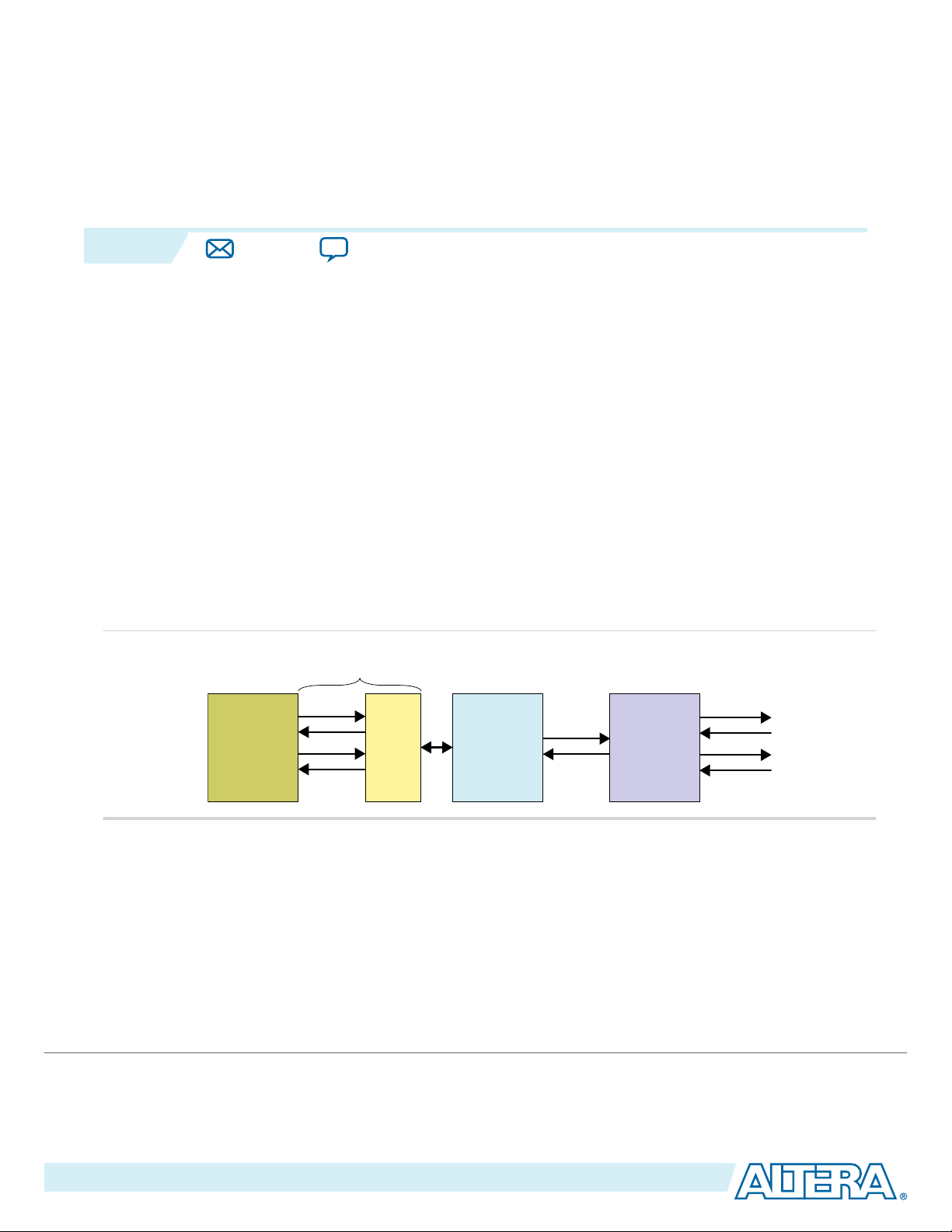

2014.12.18

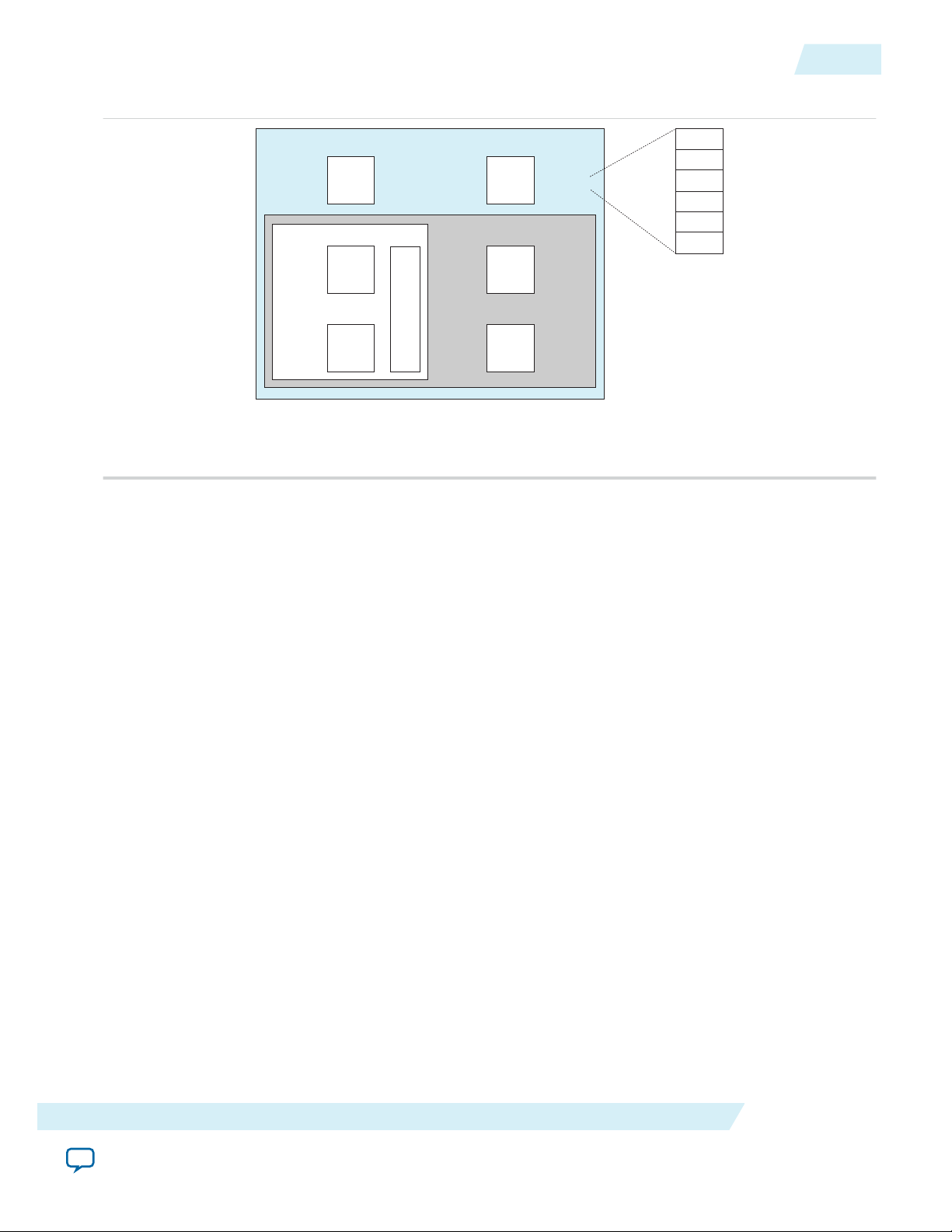

Bridge

and DMA

Engine

PCIe Hard IP

Block

PIPE

Interface

PHY IP Core

for PCIe

(PCS/PMA)

Serial Data

Transmission

Application

Layer

(User Logic)

Avalon-MM with

DMA Interface

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Datasheet

1

UG-01154

Subscribe

Send Feedback

V-Series Avalon-MM DMA Interface for PCIe Datasheet

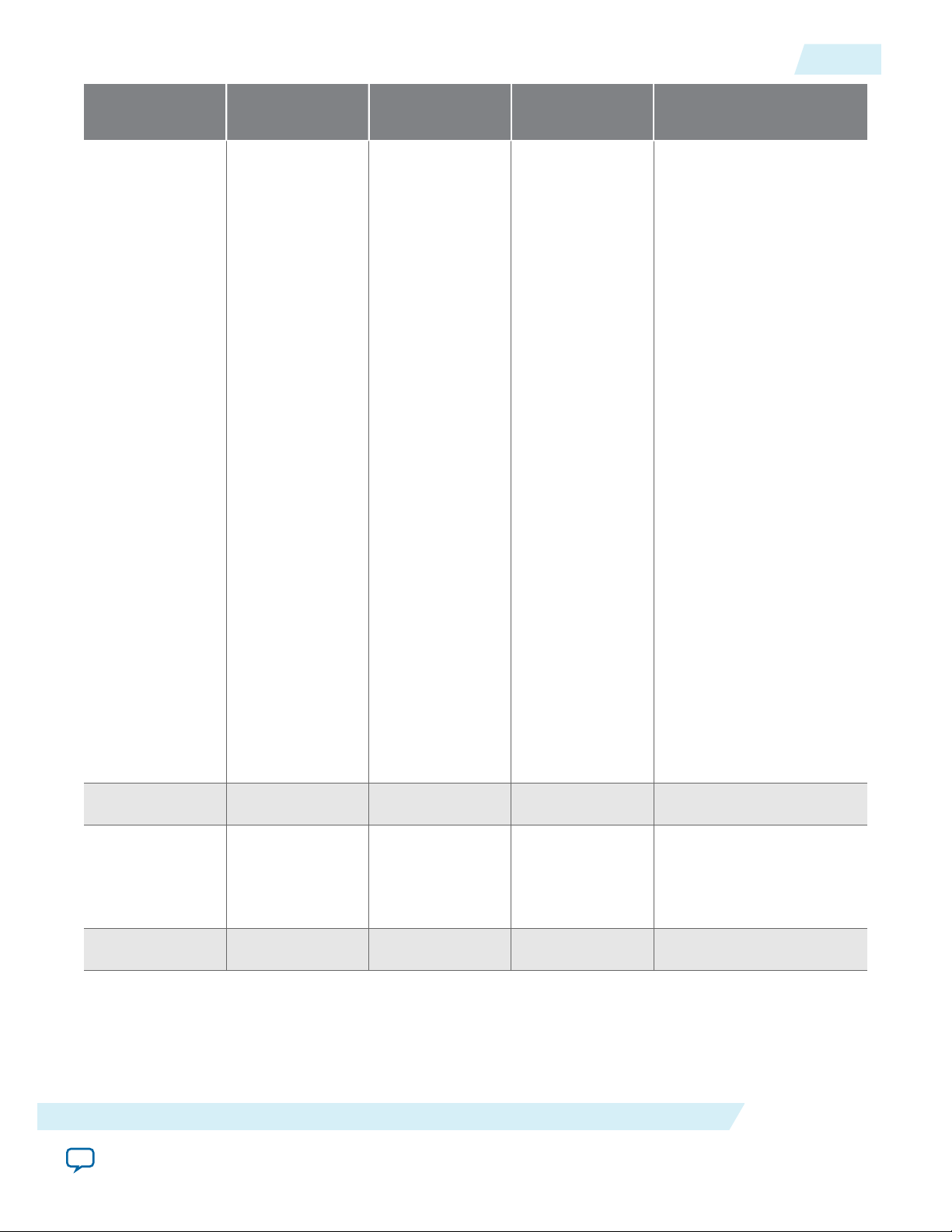

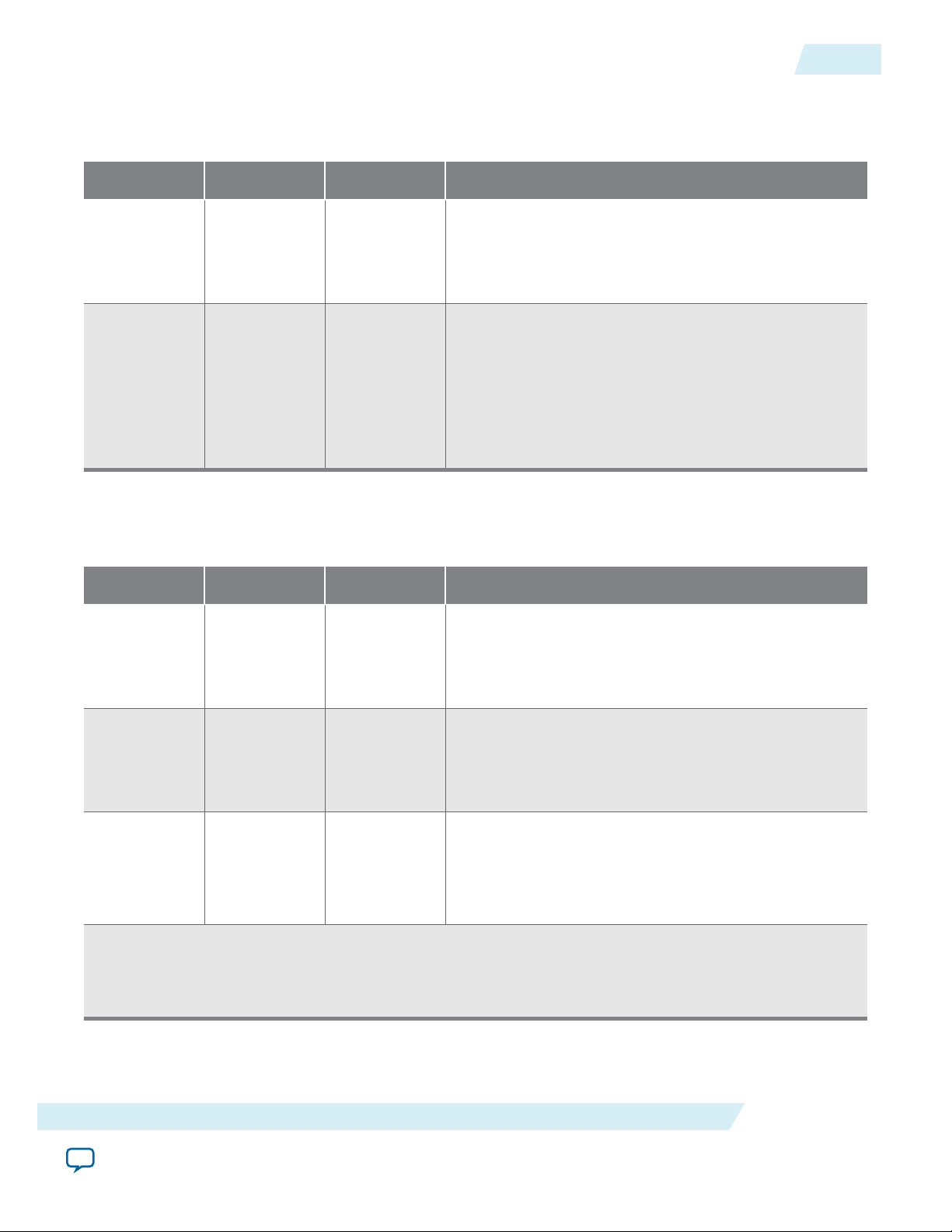

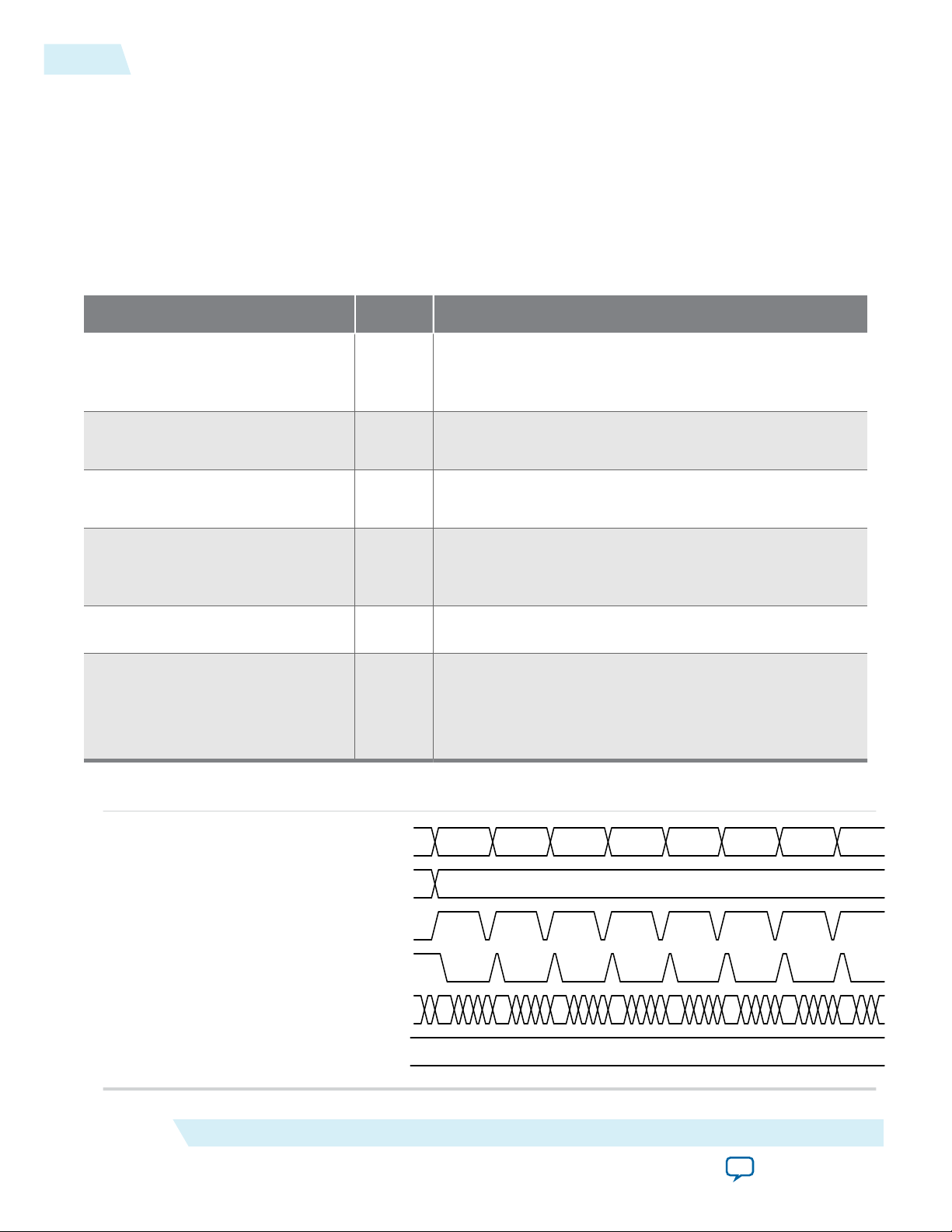

Altera® V-Series FPGAs include a configurable, hardened protocol stack for PCI Express

compliant with PCI Express Base Specification 2.1 or 3.0.

The V-Series Avalon ® Memory-Mapped (Avalon-MM) DMA for PCI Express removes some of the

complexities associated with the PCIe protocol. For example, the IP core handles TLP encoding and

decoding. In addition, it includes Read DMA and Write DMA engines. If you have already architected

your own DMA system with the Avalon-MM interface, you may want to continue to use it. However, you

will probably benefit from the simplicity of having the DMA engines already implemented. Altera

recommends this variant for new users. Depending of the device you select, this variant is available in

Qsys for 128- and 256-bit interfaces to the Application Layer. The Avalon-MM interface and DMA

engines are implemented in FPGA soft logic.

Figure 1-1: V-Series PCIe Variant with Avalon-MM DMA Interface

The following figure shows the high-level modules and connecting interfaces for this variant.

®

that is

Note:

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

This variant was renamed in the Quartus® II 14.0 release. The name in the Quartus II 13.1 release

was Avalon-MM 256-bit Hard IP for PCI Express IP Core.

ISO

9001:2008

Registered

Page 3

1-2

Features

UG-01154

2014.12.18

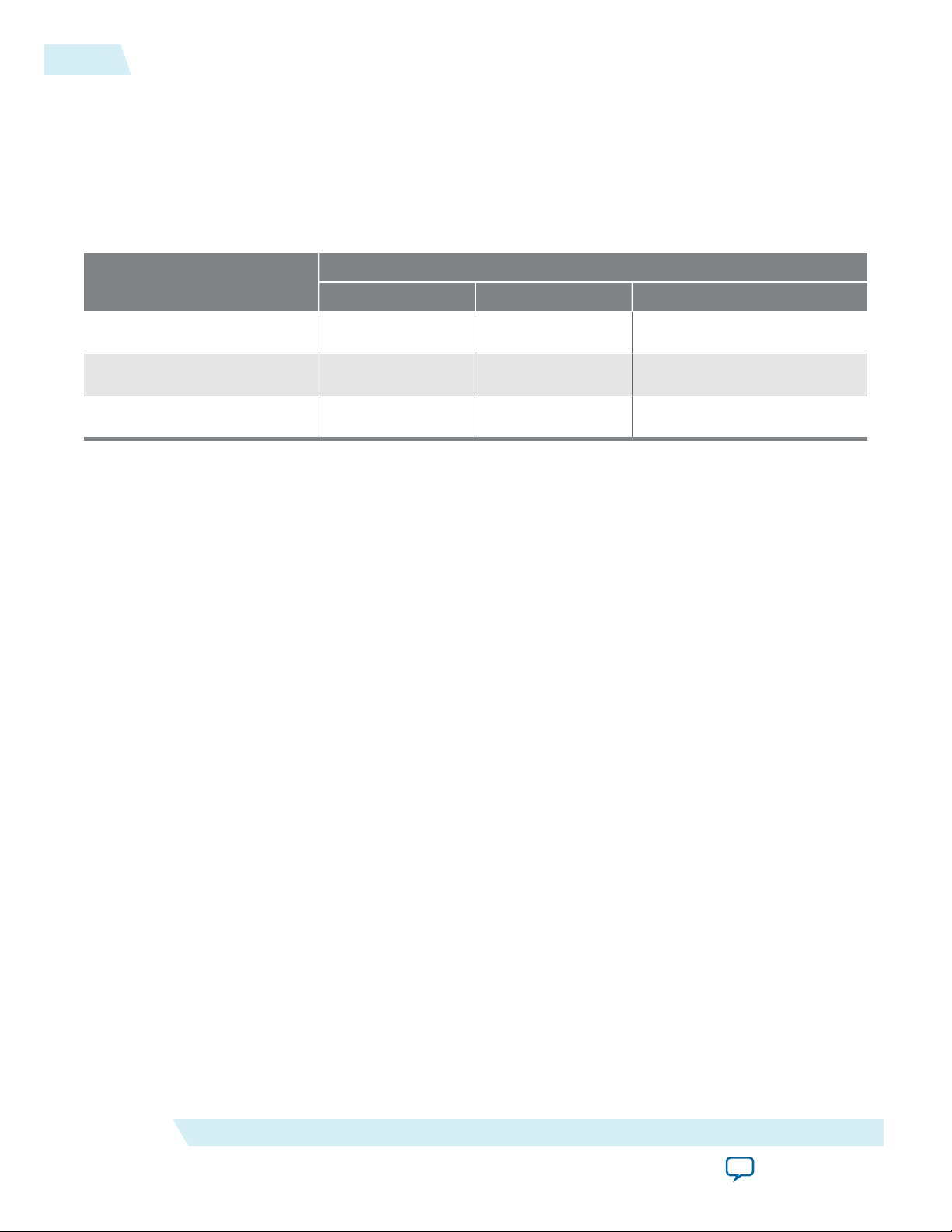

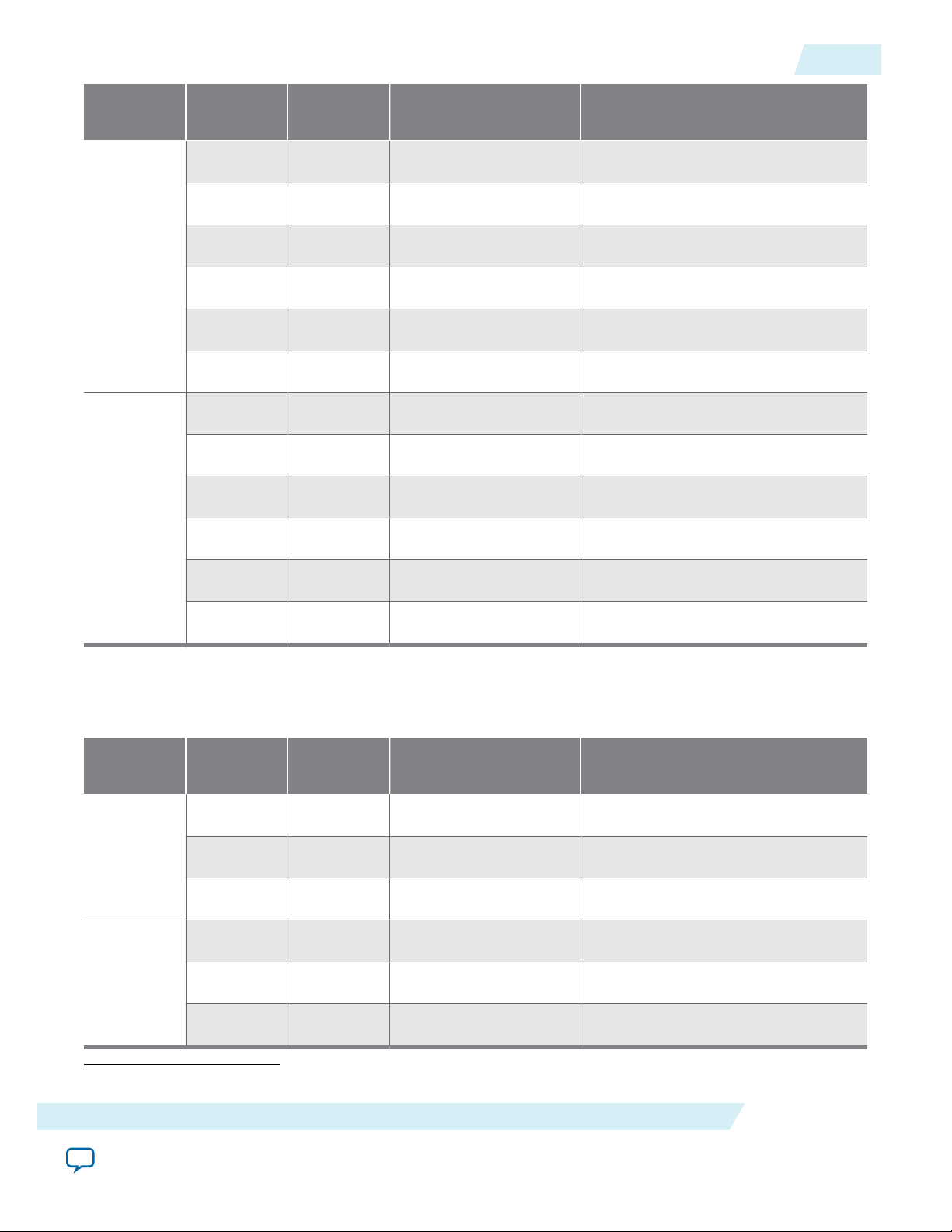

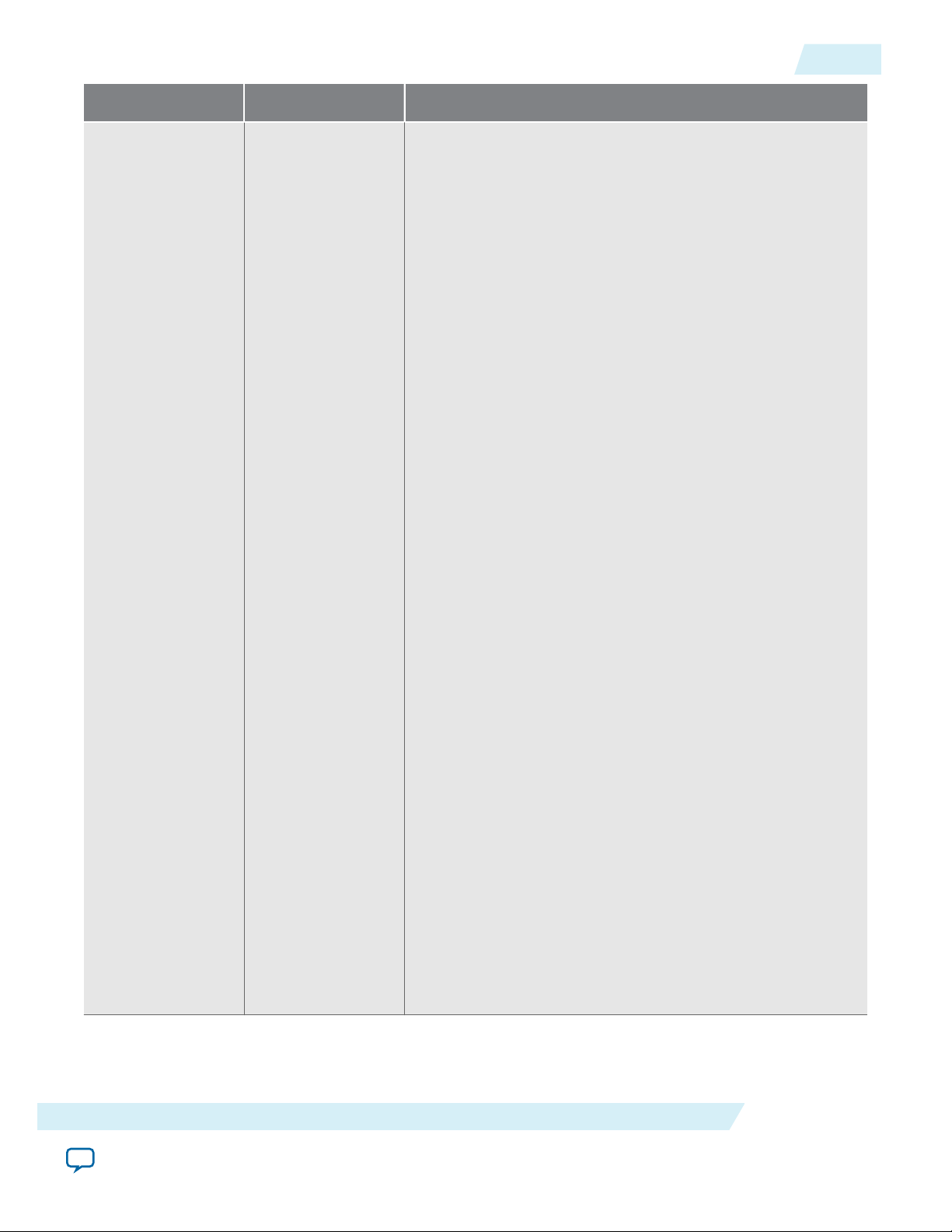

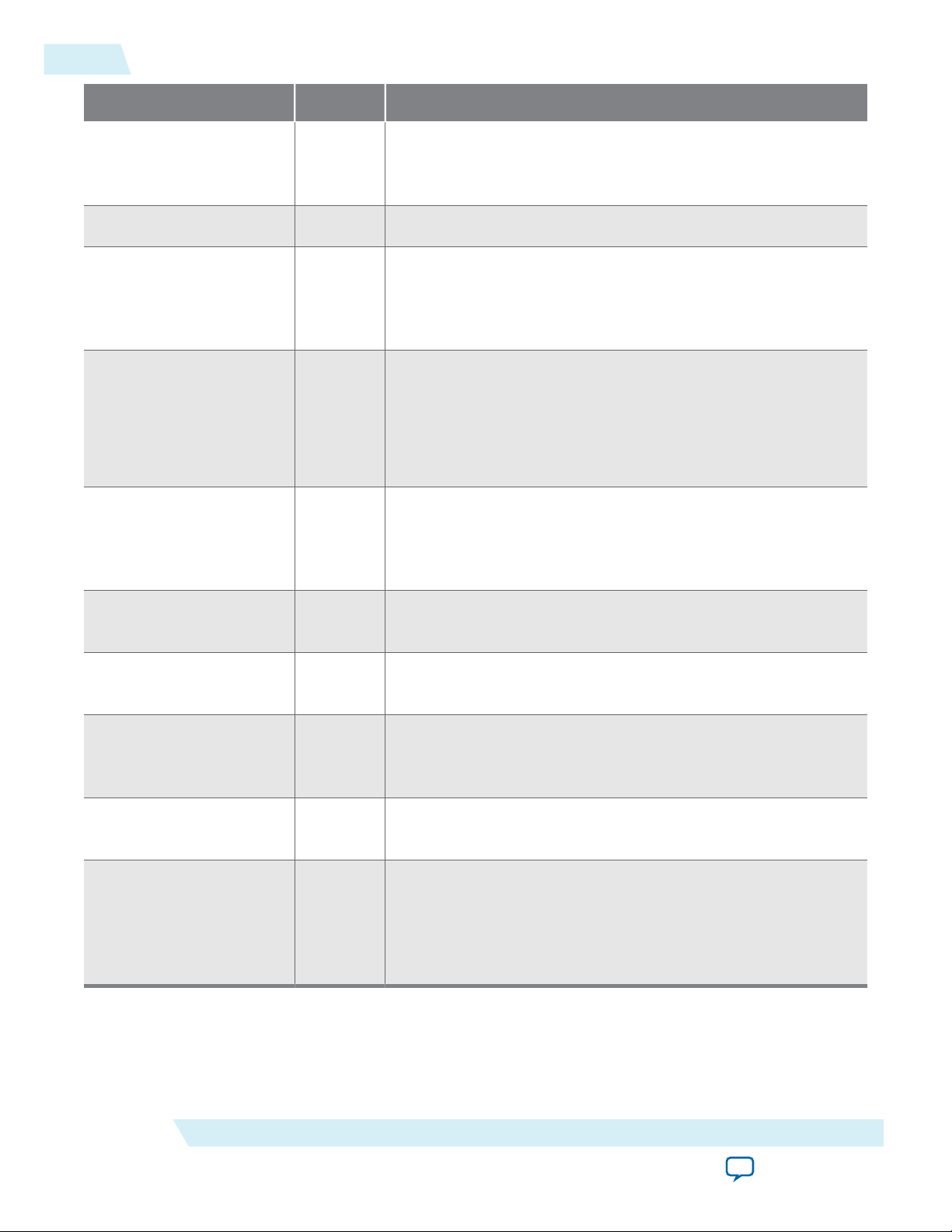

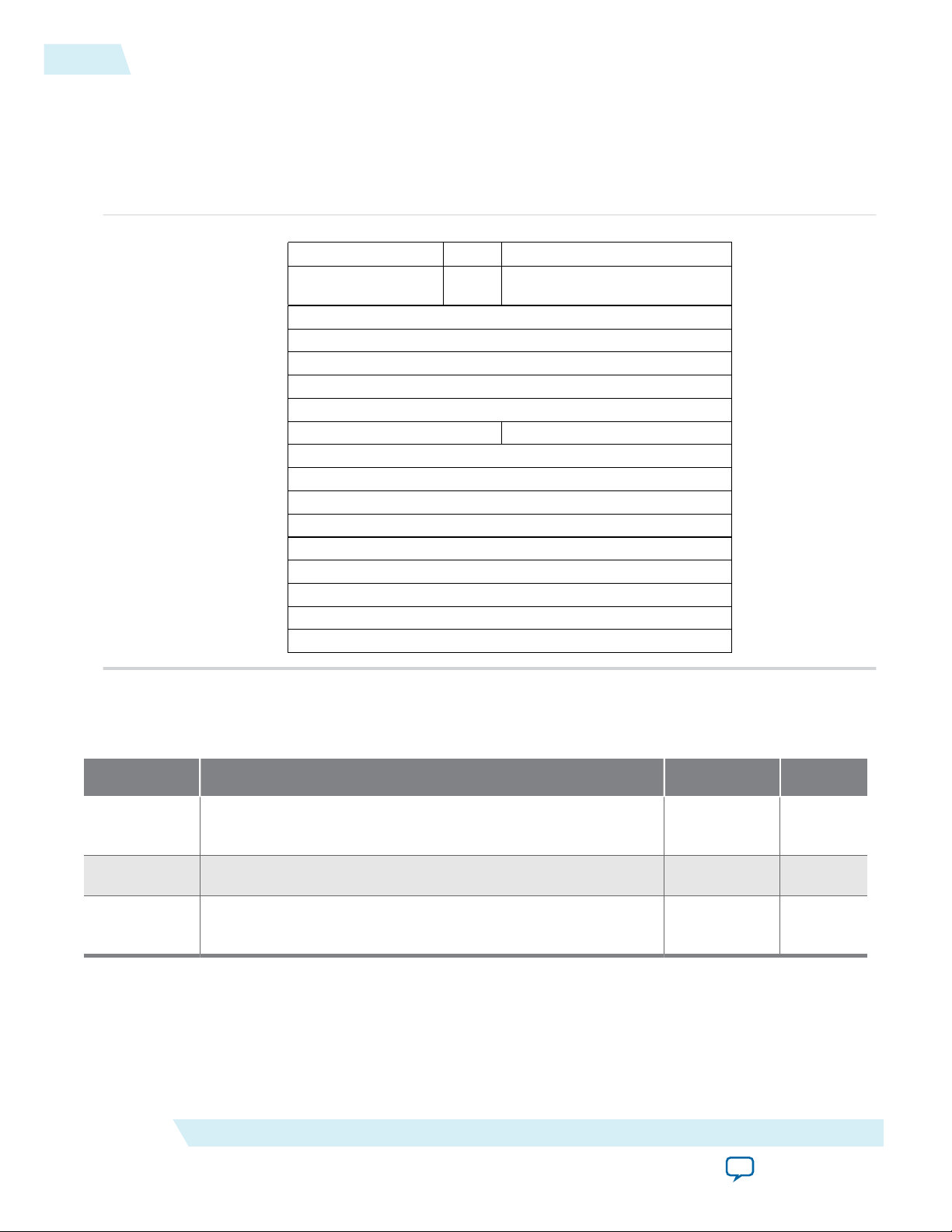

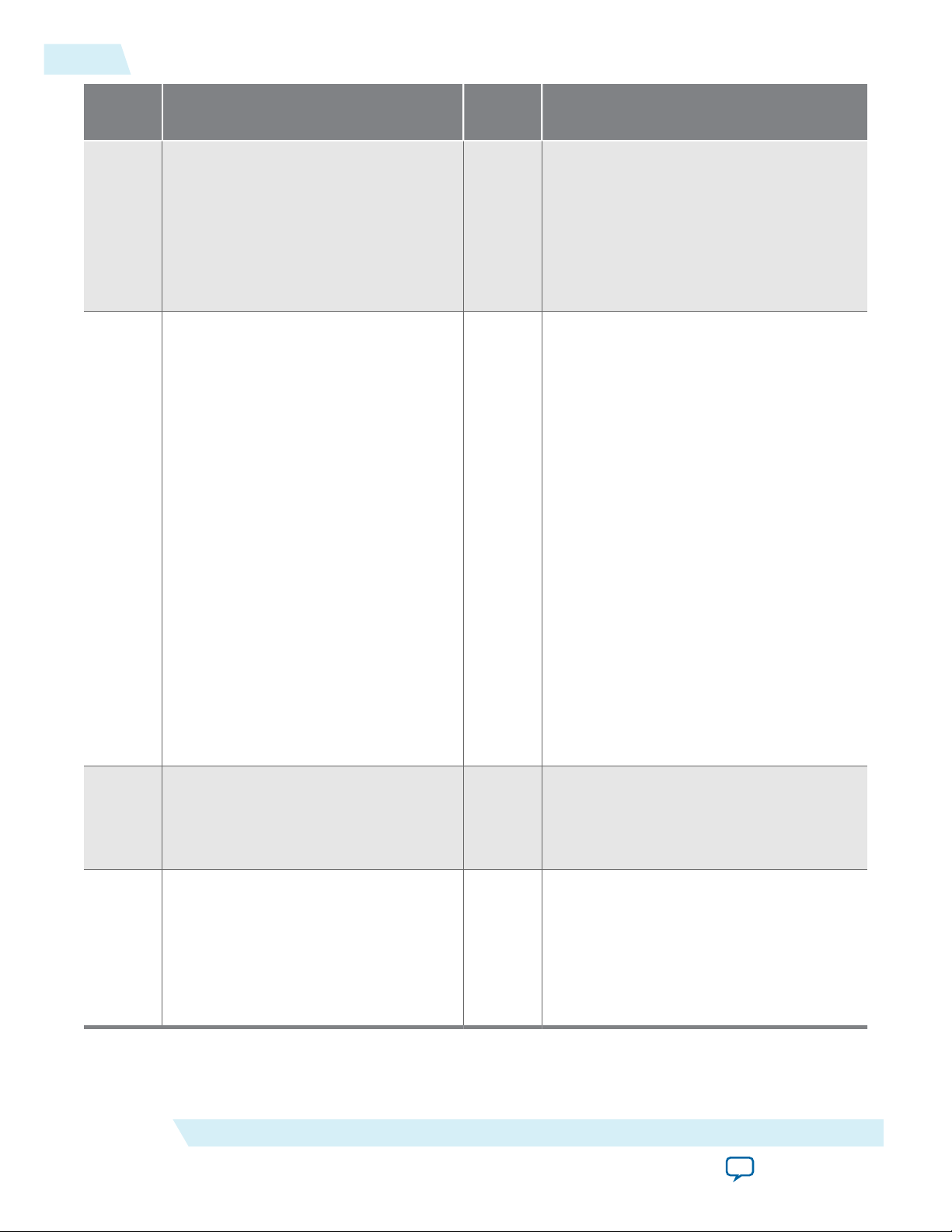

Table 1-1: PCI Express Data Throughput

The following table shows the aggregate bandwidth of a PCI Express link for Gen1, Gen2, and Gen3 for 2, 4, and 8

lanes. The protocol specifies 2.5 giga-transfers per second for Gen1, 5.0 giga-transfers per second for Gen2, and

8.0 giga-transfers per second for Gen3. This table provides bandwidths for a single transmit (TX) or receive (RX)

channel. The numbers double for duplex operation. Gen1 and Gen2 use 8B/10B encoding which introduces a 20%

overhead. In contrast, Gen3 uses 128b/130b encoding which reduces the data throughput lost to encoding to less

than 1%.

Link Width in Gigabits Per Second (Gbps)

×2 ×4 ×8

PCI Express Gen1 (2.5 Gbps)

N/A N/A

PCI Express Gen2 (5.0 Gbps) 8 16 32

PCI Express Gen3 (8.0 Gbps) 15.75 31.51 63

Related Information

• PCI Express Base Specification 2.1 or 3.0

• PCI Express DMA Reference Design for Stratix V Devices

• Creating a System with Qsys

Features

New features in the Quartus® II 14.1 software release:

• New PCI Express Multi-Channel DMA Interface IP Core to demonstrate multi-channel operation.

This component is available in the Qsys IP Catalog under Interface Protocols > PCI Express > Qsys

Example Designs

• New Avalon-MM DMA FIFO Mode IP Core for PCI Express to provide a FIFO interface to the Data

Mover included in the Avalon-MM bridge. This component is available in the Qsys IP Catalog under

Interface Protocols > PCI Express > Qsys Example Designs

• Support for 128-Bit Avalon-MM RX master.

• Reduced Quartus II compilation warnings by 50%.

16

The V-Series Avalon-MM DMA for PCI Express supports the following features:

• Complete protocol stack including the Transaction, Data Link, and Physical Layers implemented as

• Native support for Gen1 x8, Gen2 x4, Gen2 x8, Gen3 x4, Gen3 x8 for Endpoints. The variant

• Dedicated 16 KByte receive buffer.

• Optional hard reset controller for Gen2.

• Support for 128- or 256-bit Avalon-MM interface to Application Layer with embedded DMA up to

• Support for 32- or 64-bit addressing for the Avalon-MM interface to the Application Layer.

• Qsys example designs demonstrating parameterization, design modules, and connectivity.

Altera Corporation

hard IP.

downtrains when plugged into a lesser link width or changes to a different maximum link rate.

Gen3 ×8 data rate.

Datasheet

Send Feedback

Page 4

UG-01154

2014.12.18

Features

• Extended credit allocation settings to better optimize the RX buffer space based on application type.

• Optional end-to-end cyclic redundancy code (ECRC) generation and checking and advanced error

reporting (AER) for high reliability applications.

• Support for Configuration Space Bypass Mode, allowing you to design a custom Configuration Space

and support multiple functions.

• Support for Gen3 PIPE simulation.

• Support for V-Series Avalon-MM DMA for PCI Express with either a 128- or 256-bit interface to the

Application Layer. This variant includes an embedded DMA controller for data transfers. The

following table shows the available configurations.

Configuration Available Devices Interface

Width

Application Layer

Clock Frequency

Gen1 x8 Arria® V, Arria V GZ, Stratix® V 128 bits 125 MHz

Gen2 x4 Arria V, Arria V GZ, Cyclone, ® V Stratix V 128 bits 125 MHz

Gen2 x8 Arria V GZ, Stratix V 128 bits 250 MHz

Gen2 x8 Arria V GZ, Stratix V 256 bits 125 MHz

Gen3 x4 Arria V GZ, Stratix V 128 bits 250 MHz

Gen3 x4 Arria V GZ, Stratix V 256 bits 125 MHz

1-3

Gen3 x8 Arria V GZ, Stratix V 256 bits 250 MHz

• Easy to use:

• Flexible configuration.

• No license requirement.

• Example designs to get started.

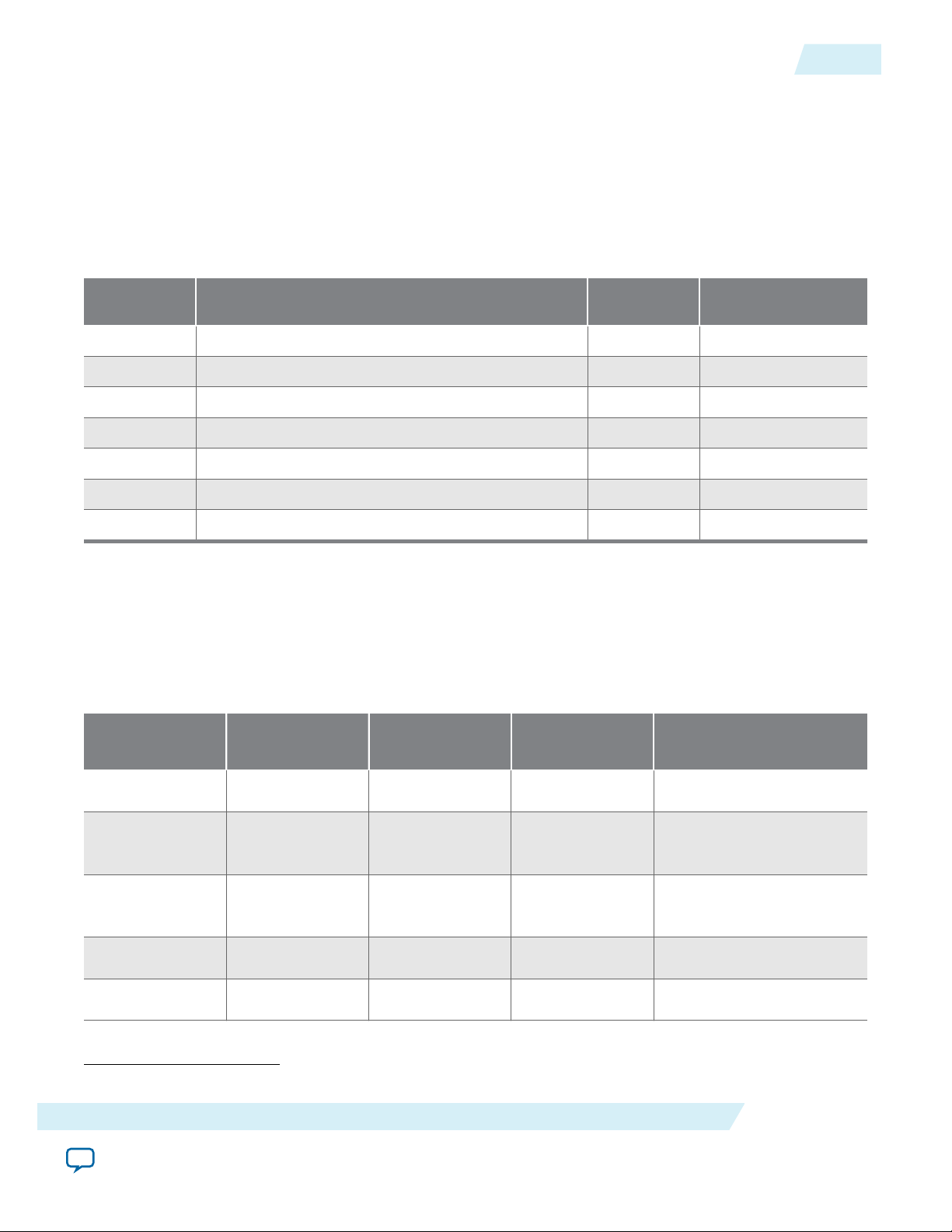

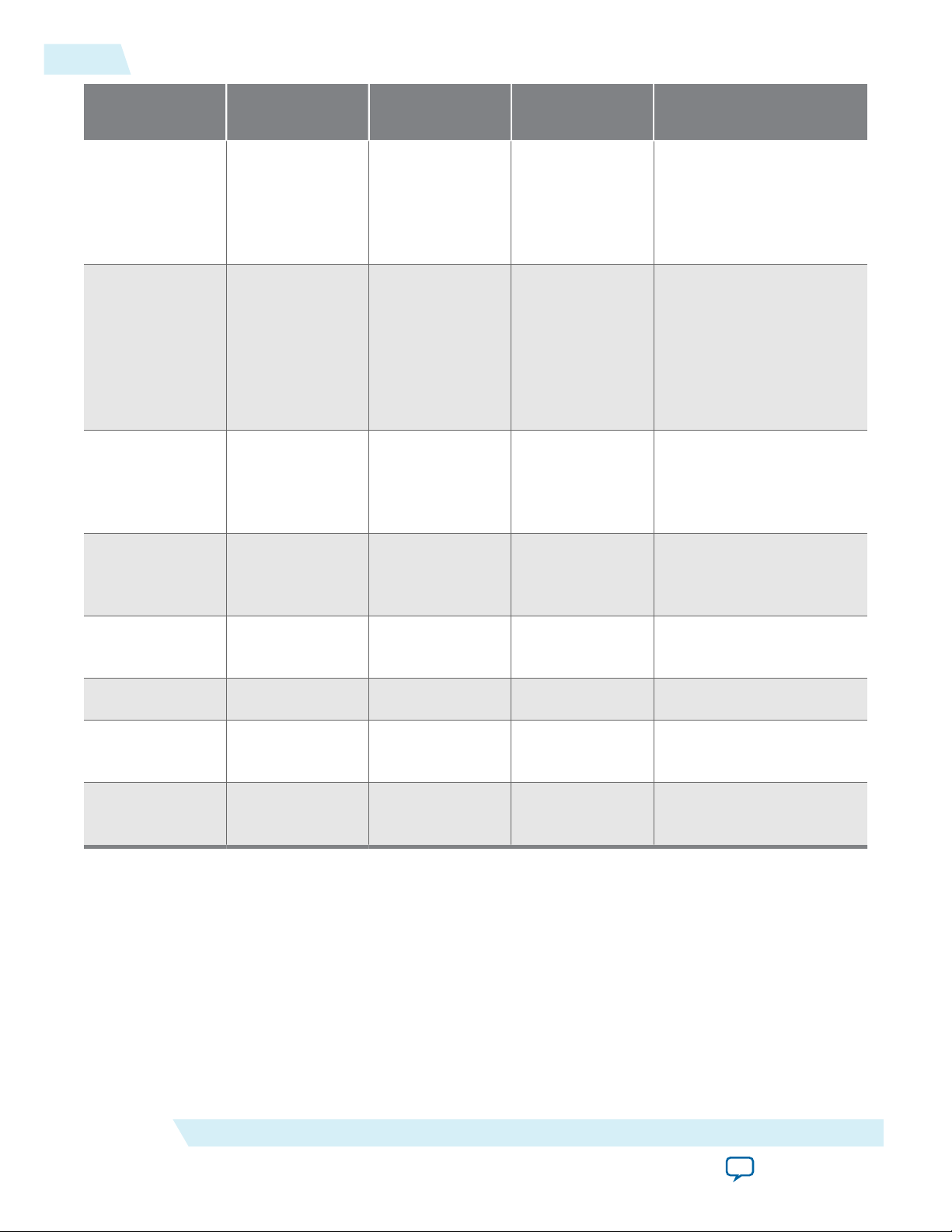

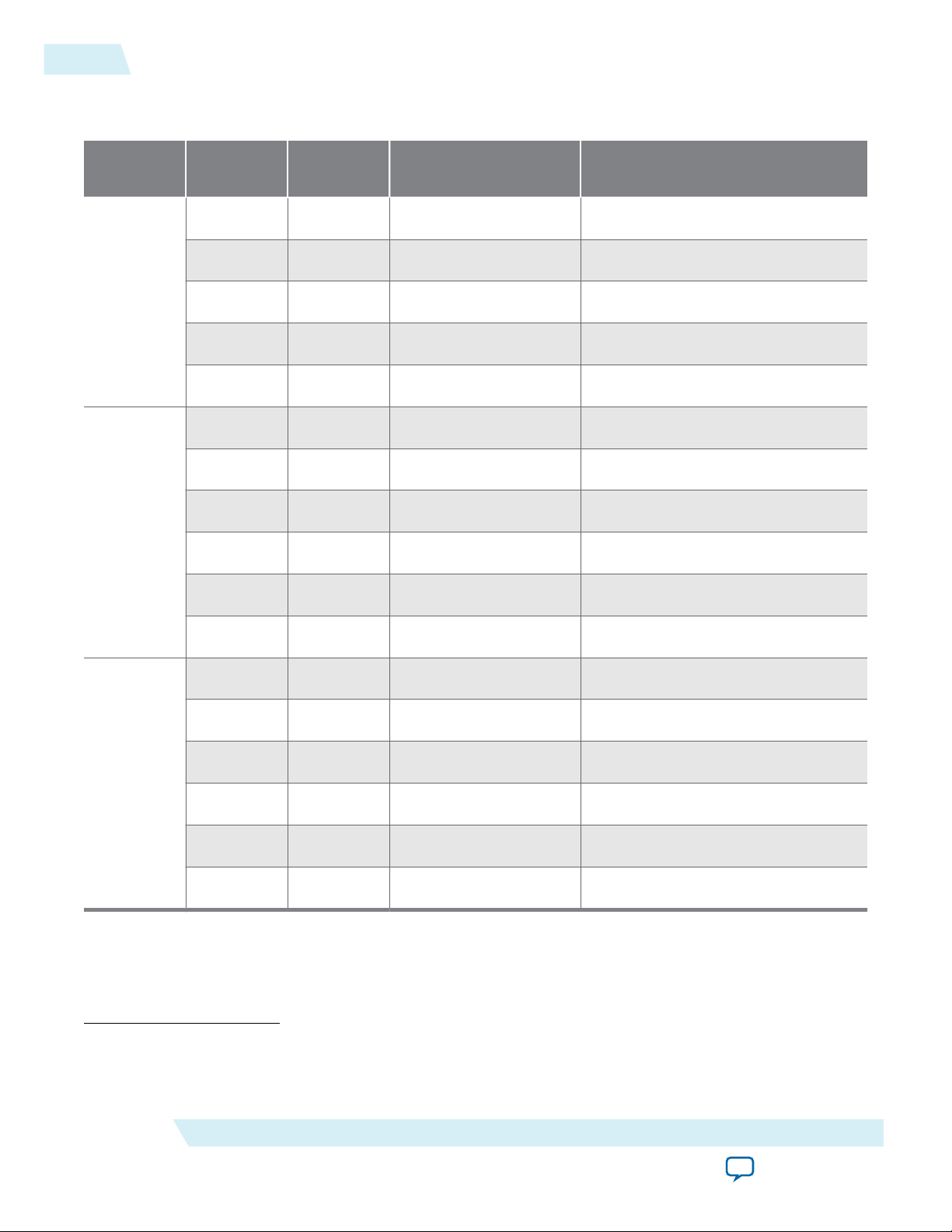

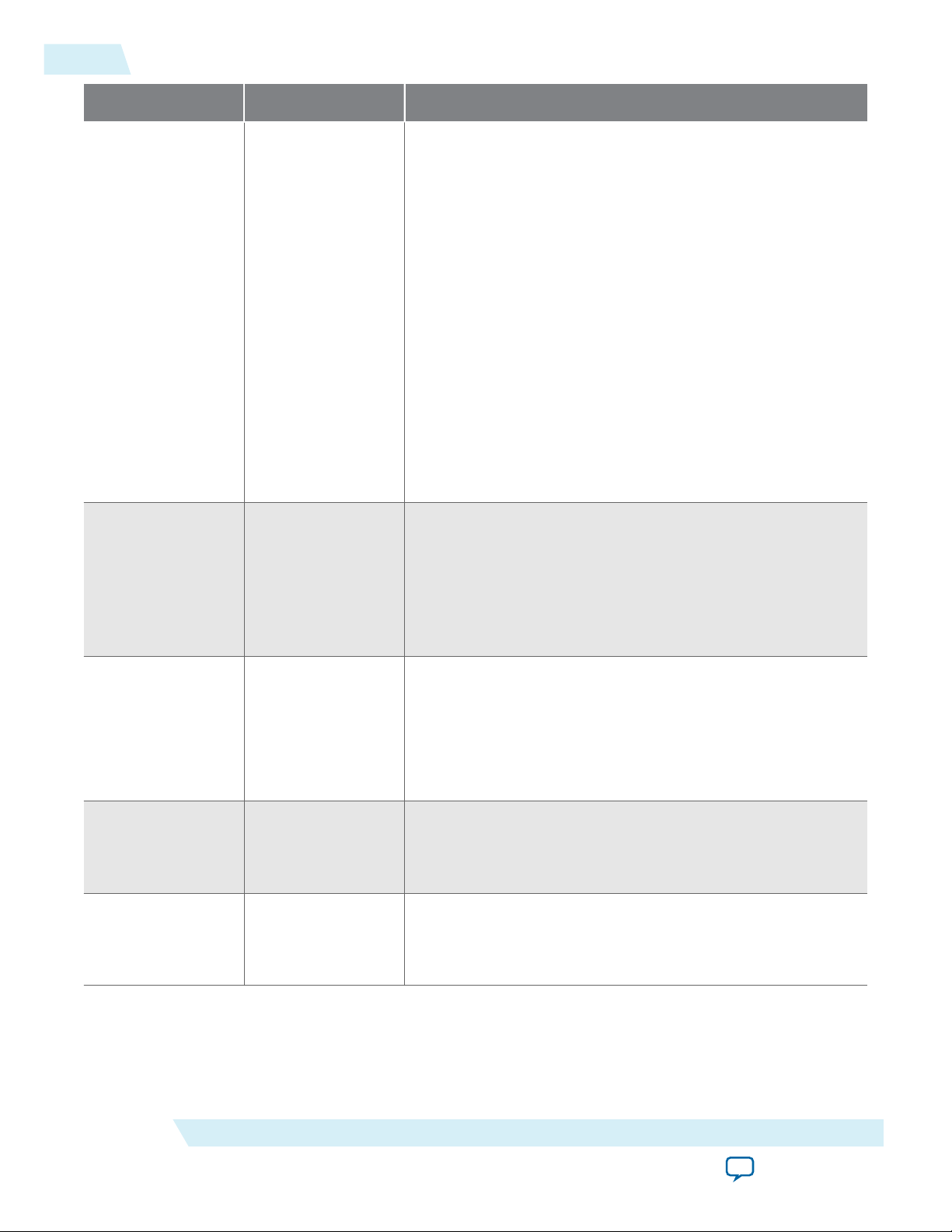

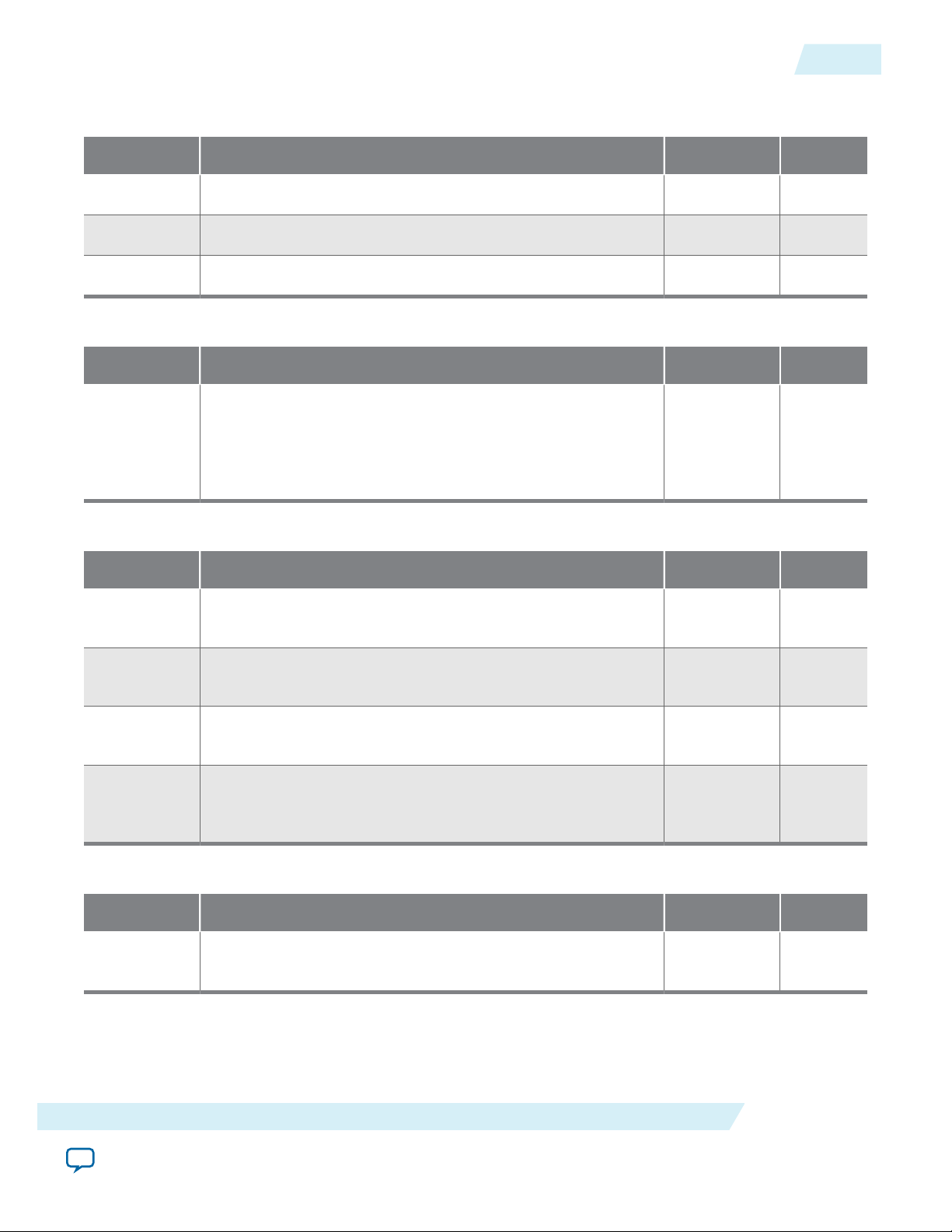

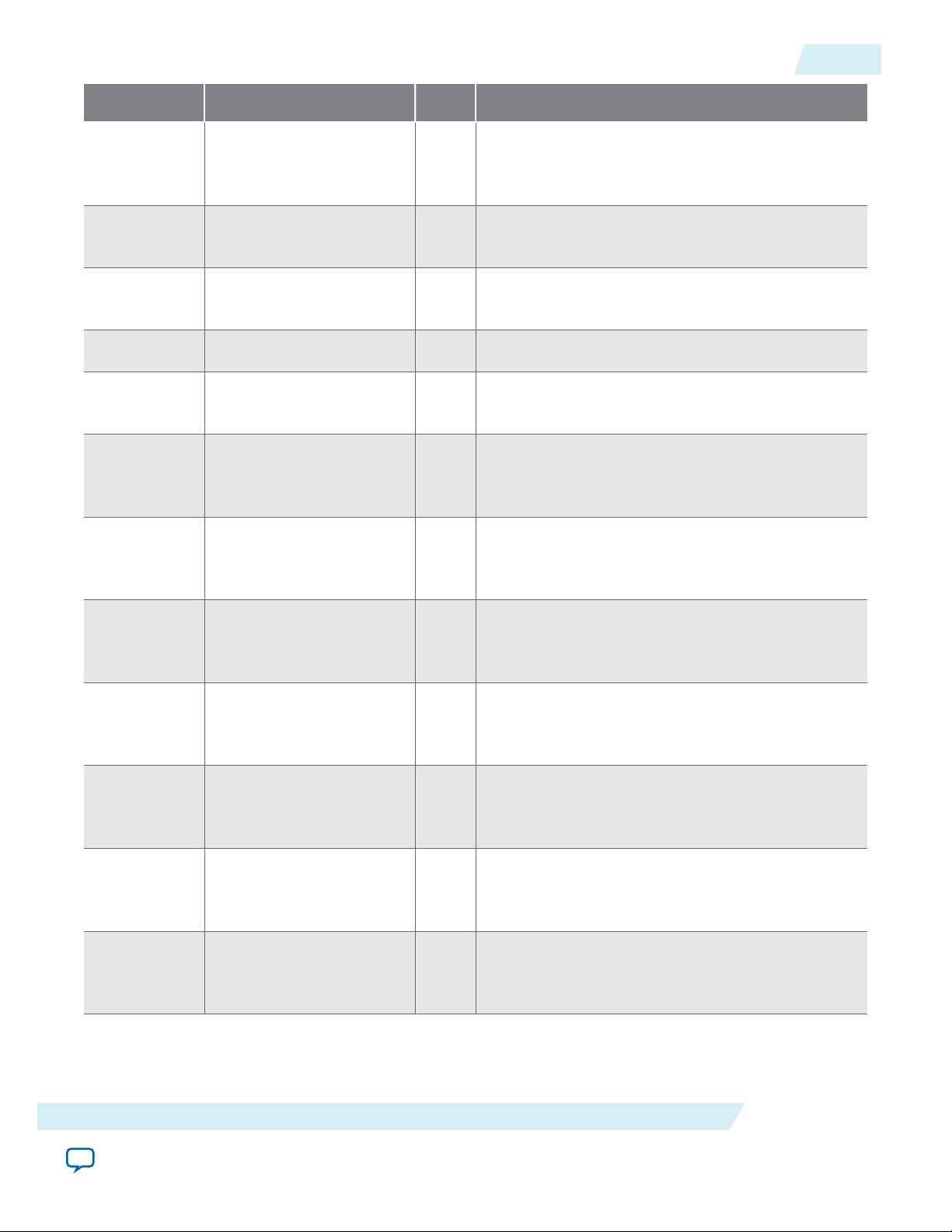

Table 1-2: Feature Comparison for all Hard IP for PCI Express IP Cores

The table compares the features of the four Hard IP for PCI Express IP Cores.

Feature Avalon‑ST Interface Avalon‑MM

Interface

Avalon‑MM DMA Avalon‑ST Interface with SR-

IOV

IP Core License Free Free Free Free

Native

Supported Supported Supported Supported

Endpoint

Legacy

Endpoint

(1)

Supported Not Supported Not Supported Not Supported

Root port Supported Supported Not Supported Not Supported

(1)

Datasheet

Gen1 ×1, ×2, ×4, ×8 ×1, ×2, ×4, ×8 Not Supported

Not recommended for new designs.

Send Feedback

×8

Altera Corporation

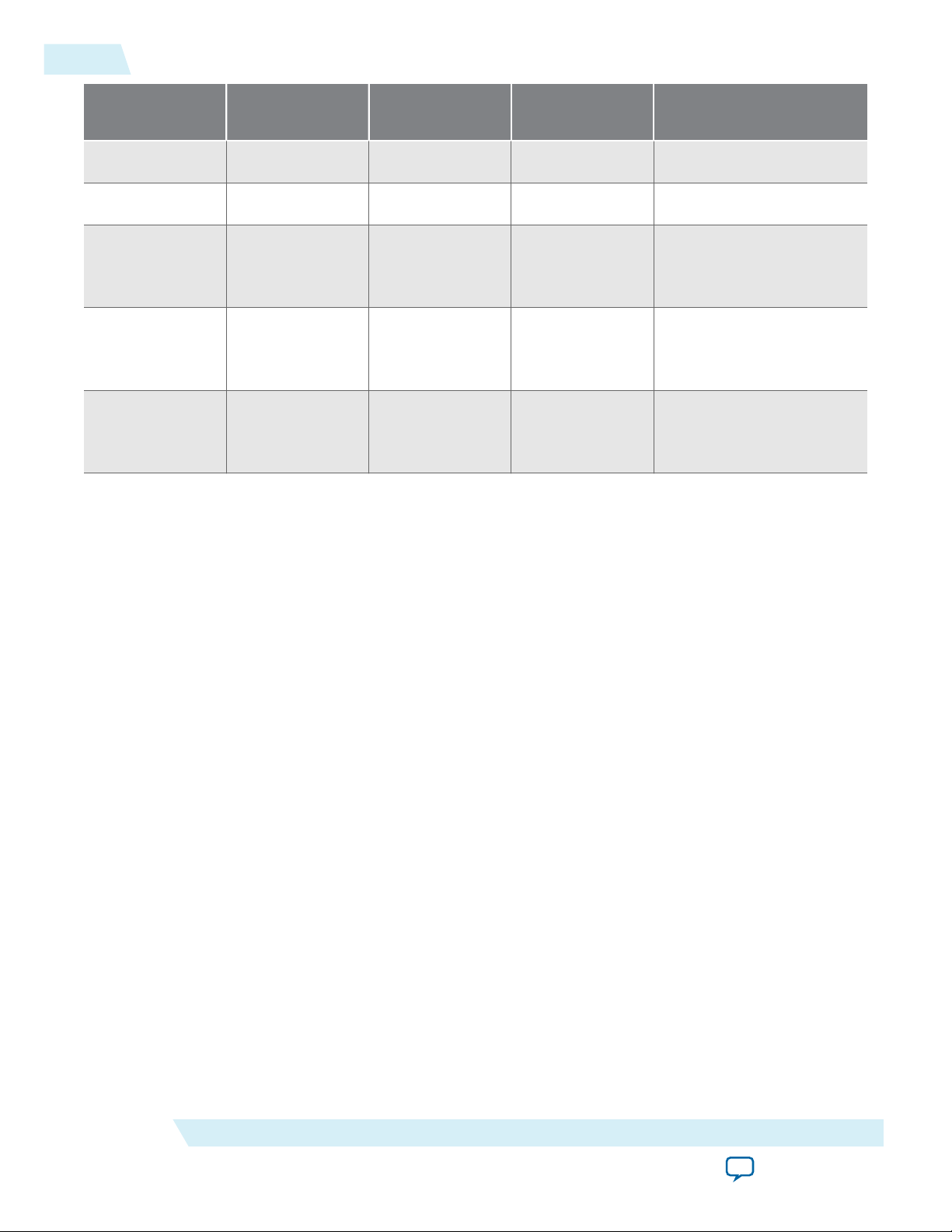

Page 5

1-4

Features

UG-01154

2014.12.18

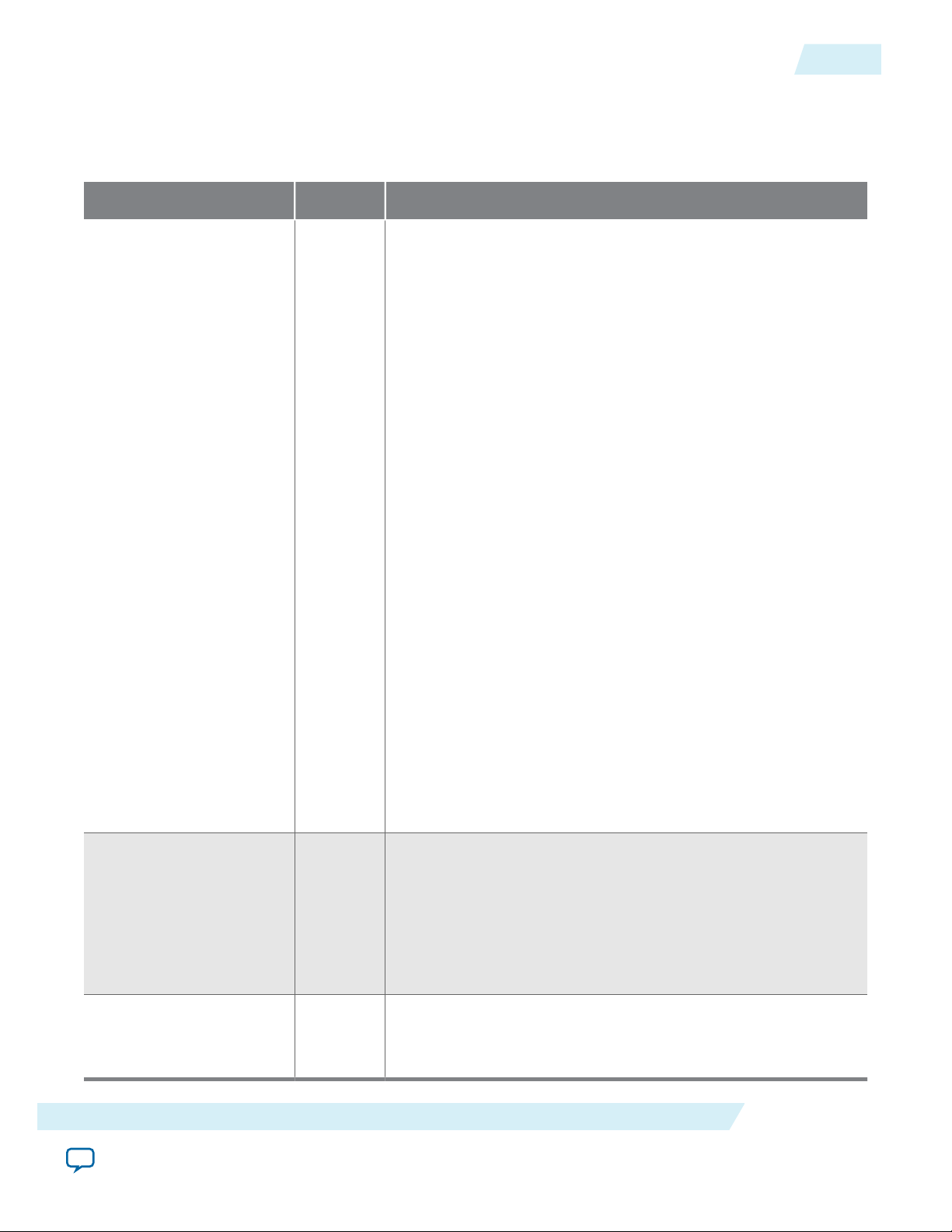

Feature Avalon‑ST Interface Avalon‑MM

Interface

Avalon‑MM DMA Avalon‑ST Interface with SR-

Gen2 ×1, ×2, ×4, ×8 ×1, ×2, ×4, ×8 ×4, ×8

Gen3 ×1, ×2, ×4, ×8 ×1, ×2, ×4 ×4, ×8

64-bit Applica‐

Supported Supported Not supported Not supported

tion Layer

interface

128-bit

Supported Supported Supported Supported

Application

Layer interface

256-bit

Supported Not Supported Supported Supported

Application

Layer interface

IOV

×4, ×8

×2, ×4, ×8

Altera Corporation

Datasheet

Send Feedback

Page 6

UG-01154

2014.12.18

Features

1-5

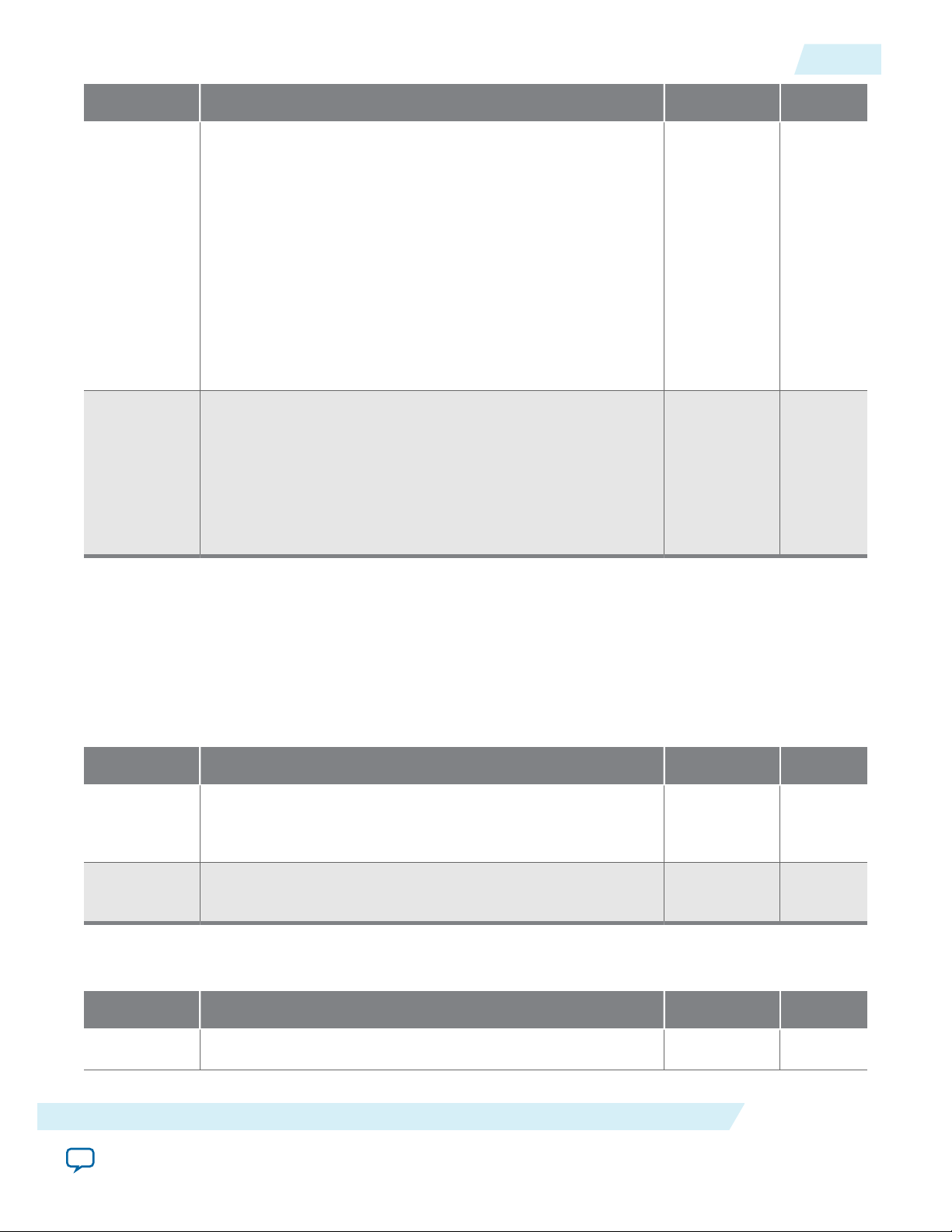

Feature Avalon‑ST Interface Avalon‑MM

Interface

Transaction

Layer Packet

type (TLP)

• Memory Read

Request

• Memory Read

RequestLocked

• Memory Write

Request

• I/O Read

Request

• I/O Write

Request

• Configuration

Read Request

(Root Port)

• Configuration

Write Request

(Root Port)

• Message

Request

• Message

Request with

Data Payload

• Completion

Message

• Completion

with Data

• Memory Read

Request

• Memory Write

Request

• I/O Read

Request—Root

Port only

• I/O Write

Request—Root

Port only

• Configuration

Read Request

(Root Port)

• Configuration

Write Request

(Root Port)

• Completion

Message

• Completion

with Data

• Memory Read

Request (single

dword)

• Memory Write

Request (single

dword)

• Completion for

Locked Read

without Data

Avalon‑MM DMA Avalon‑ST Interface with SR-

IOV

• Memory Read

Request

• Memory Write

Request

• Completion

Message

• Completion

with Data

• Memory Read Request

• Memory Write

Request

• Configuration Read

Request (from Root

Port)

• Configuration Write

Request (from Root

Port)

• Message Request

• Completion Message

• Completion with Data

Datasheet

Payload size

Number of tags

128–2048 bytes 128–256 bytes 128, 256, 512 bytes 128–256 bytes

256 8 16 256

supported for

non-posted

requests

62.5 MHz clock Supported Supported Not Supported Not Supported

Send Feedback

Altera Corporation

Page 7

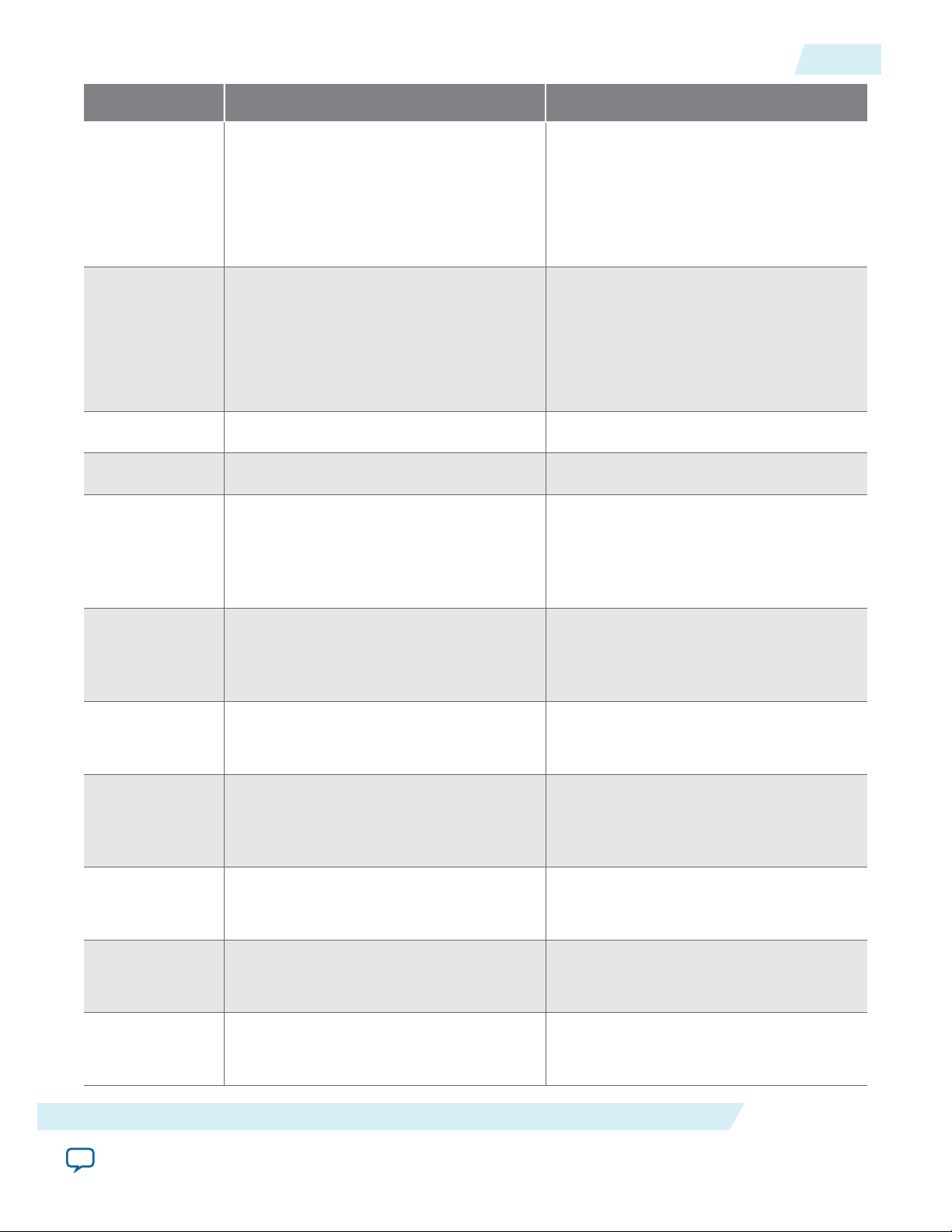

1-6

Features

UG-01154

2014.12.18

Feature Avalon‑ST Interface Avalon‑MM

Interface

Out-of-order

Not supported Supported Supported Not supported

completions

(transparent to

the Application

Layer)

Requests that

Not supported Supported Supported Supported

cross 4 KByte

address

boundary

(transparent to

the Application

Layer)

Polarity

Supported Supported Supported Supported

Inversion of

PIPE interface

signals

Avalon‑MM DMA Avalon‑ST Interface with SR-

IOV

ECRC

Supported Not supported Not supported Not supported

forwarding on

RX and TX

Number of MSI

requests

1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 1, 2, 4, 8, 16, or 32 (for

Physical Functions)

MSI-X Supported Supported Supported Supported

Legacy

Supported Supported Supported Supported

interrupts

Expansion

Supported Not supported Not supported Not supported

ROM

The V-Series Avalon-MM DMA Interface for PCIe Solutions User Guide explains how to use this IP core

and not the PCI Express protocol. Although there is inevitable overlap between these two purposes, use

this document only in conjunction with an understanding of the PCI Express Base Specification.

Altera Corporation

Datasheet

Send Feedback

Page 8

UG-01154

2014.12.18

Release Information

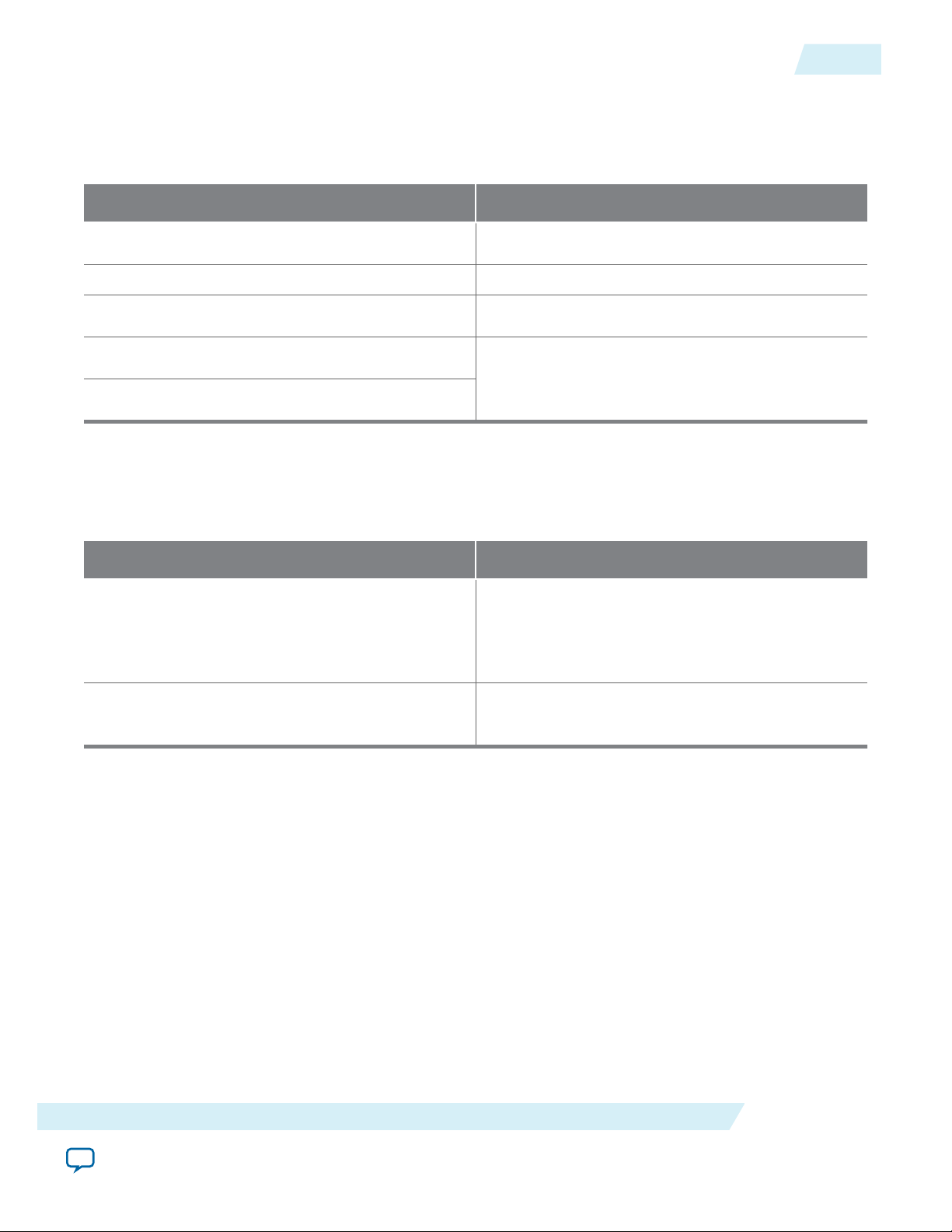

Table 1-3: Hard IP for PCI Express Release Information

Item Description

Version 14.1

Release Date December 2014

Ordering Codes No ordering code is required

Release Information

1-7

Product IDs

Vendor ID

The Product ID and Vendor ID are not required

because this IP core does not require a license.

V-Series Device Family Support

Table 1-4: Device Family Support

Device Family Support

Arria V, Arria V GZ, Cyclone V, Stratix V

Other device families Refer to the Related Information below for other

Related Information

• PCI Express Multi-Channel DMA Interface Example Design User Guide

• Avalon-MM DMA FIFO Example Design User Guide

• Arria V Avalon-MM Interface for PCIe Solutions User Guide

• Arria V Avalon-ST Interface for PCIe Solutions User Guide

• Arria V GZ Avalon-MM Interface for PCIe Solutions User Guide

• Arria V GZ Avalon-ST Interface for PCIe Solutions User Guide

• Arria 10 Avalon-MM Interface for PCIe Solutions User Guide

• Arria 10 Avalon-MM DMA Interface for PCIe Solutions User Guide

• Arria 10 Avalon-ST Interface for PCIe Solutions User Guide

• Cyclone V Avalon-MM Interface for PCIe Solutions User Guide

• Cyclone V Avalon-ST Interface for PCIe Solutions User Guide

• IP Compiler for PCI Express User Guide

• Stratix V Avalon-MM Interface for PCIe Solutions User Guide

Final. The IP core is verified with final timing

models. The IP core meets all functional and timing

requirements for the device family and can be used

in production designs.

device families:

Datasheet

Altera Corporation

Send Feedback

Page 9

1-8

Example Designs

• Stratix V Avalon-ST Interface for PCIe Solutions User Guide

• Stratix V Avalon-ST Interface with SR-IOV for PCIe Solutions User Guide

Example Designs

The following Qsys example designs are available for the V-Series Avalon-MM DMA for PCI Express IP

Core. You can download them from the <install_dir>/ip/altera/altera_pcie/altera_pcie_hip_256_avmm/

example_design/<dev> directory:

• pcie_de_ep_dma_g3x8_integrated.qsys—Arria V GZ and Stratix V

• pcie_de_ep_dma_g3x8. qsys—Arria V GZ and Stratix V

• pcie_de_ep_dma_g1x8_av_integrated. qsys—Arria V

• pcie_de_ep_g2x4_cv. qsys—Cyclone V

Related Information

Getting Started with the Avalon-MM DMA on page 2-1

Debug Features

UG-01154

2014.12.18

Debug features allow observation and control of the Hard IP for faster debugging of system-level

problems.

IP Core Verification

To ensure compliance with the PCI Express specification, Altera performs extensive verification. The

simulation environment uses multiple testbenches that consist of industry-standard bus functional

models (BFMs) driving the PCI Express link interface. Altera performs the following tests in the

simulation environment:

• Directed and pseudorandom stimuli are applied to test the Application Layer interface, Configuration

Space, and all types and sizes of TLPs

• Error injection tests that inject errors in the link, TLPs, and Data Link Layer Packets (DLLPs), and

check for the proper responses

• PCI-SIG® Compliance Checklist tests that specifically test the items in the checklist

• Random tests that test a wide range of traffic patterns

Altera provides the following two example designs that you can leverage to test your PCBs and complete

compliance base board testing (CBB testing) at PCI-SIG.

Related Information

• PCI SIG Gen3 x8 Merged Design - Stratix V

• PCI SIG Gen2 x8 Merged Design - Stratix V

Altera Corporation

Datasheet

Send Feedback

Page 10

UG-01154

2014.12.18

Compatibility Testing Environment

Compatibility Testing Environment

Altera has performed significant hardware testing to ensure a reliable solution. In addition, Altera

internally tests every release with motherboards and PCI Express switches from a variety of manufac‐

turers. All PCI-SIG compliance tests are run with each IP core release.

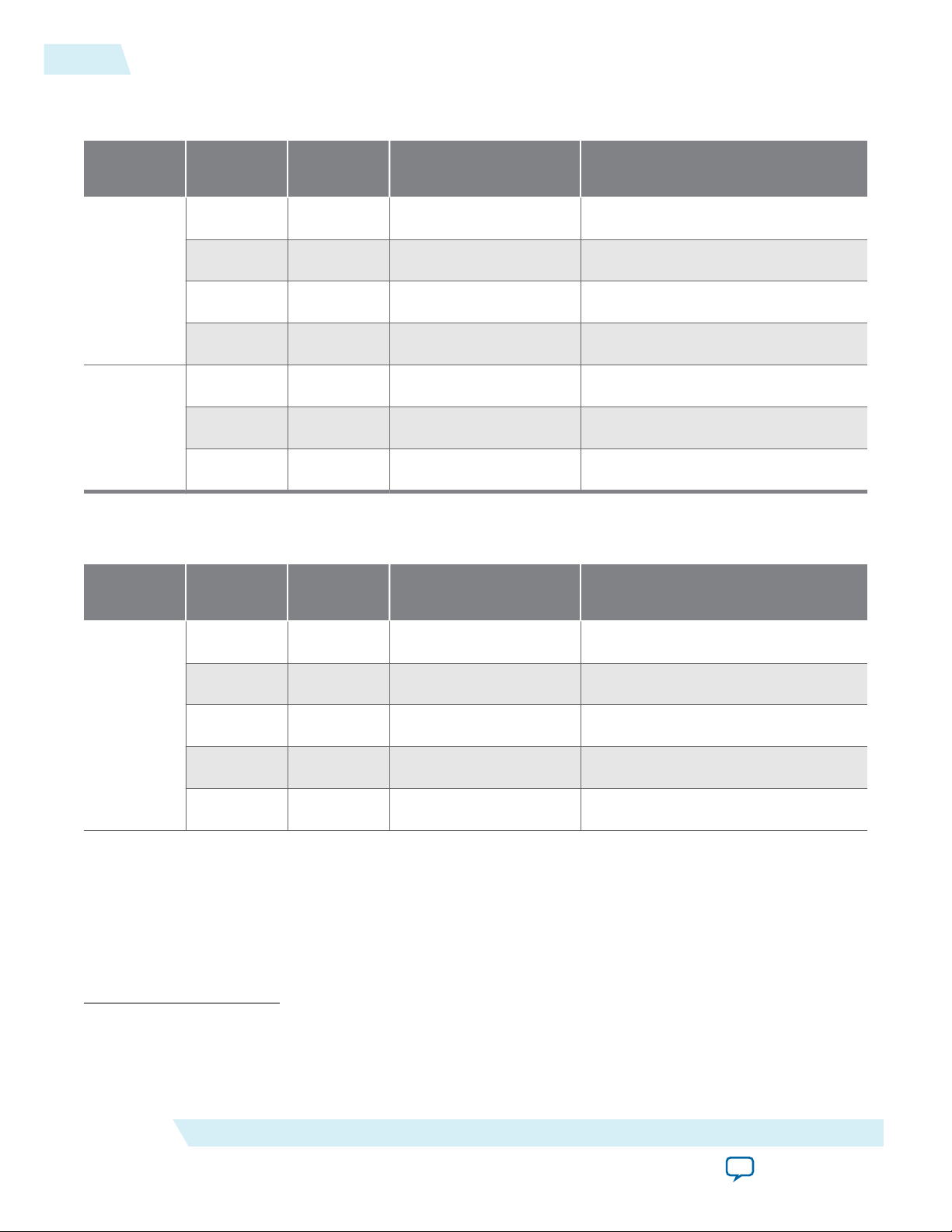

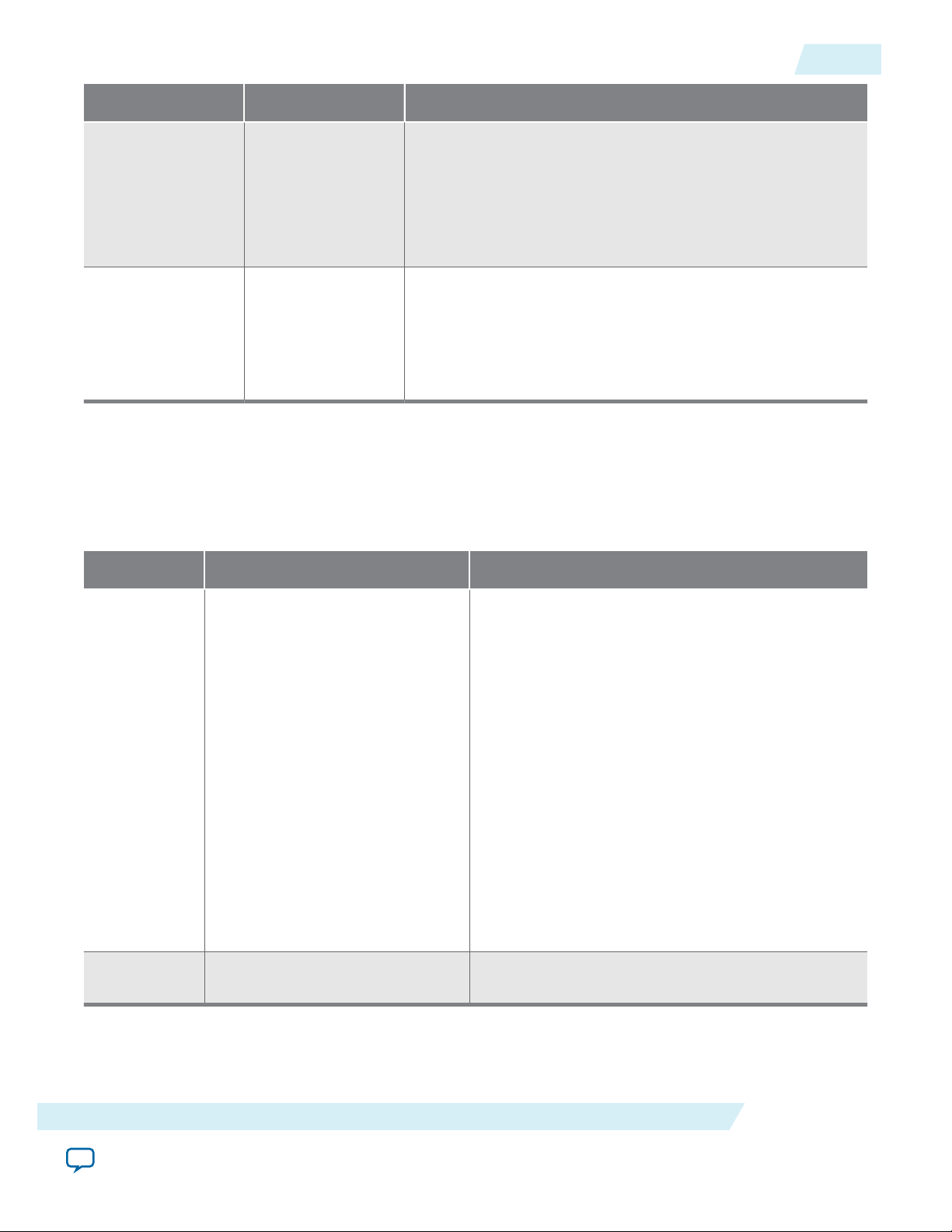

Performance and Resource Utilization

Because the PCIe protocol stack is implemented in hardened logic, it uses less than 1% of device

resources.

The V-Series variants include a soft logic bridge that functions as a front end to the hardened protocol

stack. The following table shows the typical expected device resource utilization for selected configura‐

tions using the current version of the Quartus II software targeting a V-Series device. With the exception

of M20K memory blocks, the numbers of ALMs and logic registers are rounded up to the nearest 50.

Table 1-5: Performance and Resource Utilization V-Series Avalon-MM DMA for PCI Express

Interface Width ALMs M20K Memory Blocks Logic Registers

1-9

128 1100 14 1650

256 1750 19 2600

Note: Soft calibration of the transceiver module requires additional logic. The amount of logic required

depends upon the configuration.

Related Information

Fitter Resources Reports

V-Series Recommended Speed Grades

Altera recommends setting the Quartus II Analysis & Synthesis Settings Optimization Technique to

Speed when the Application Layer clock frequency is 250 MHz. For information about optimizing

synthesis, refer to Setting Up and Running Analysis and Synthesis in Quartus II Help. For more informa‐

tion about how to effect the Optimization Technique settings, refer to Area and Timing Optimization in

volume 2 of the Quartus II Handbook. .

Datasheet

Altera Corporation

Send Feedback

Page 11

1-10

V-Series Recommended Speed Grades

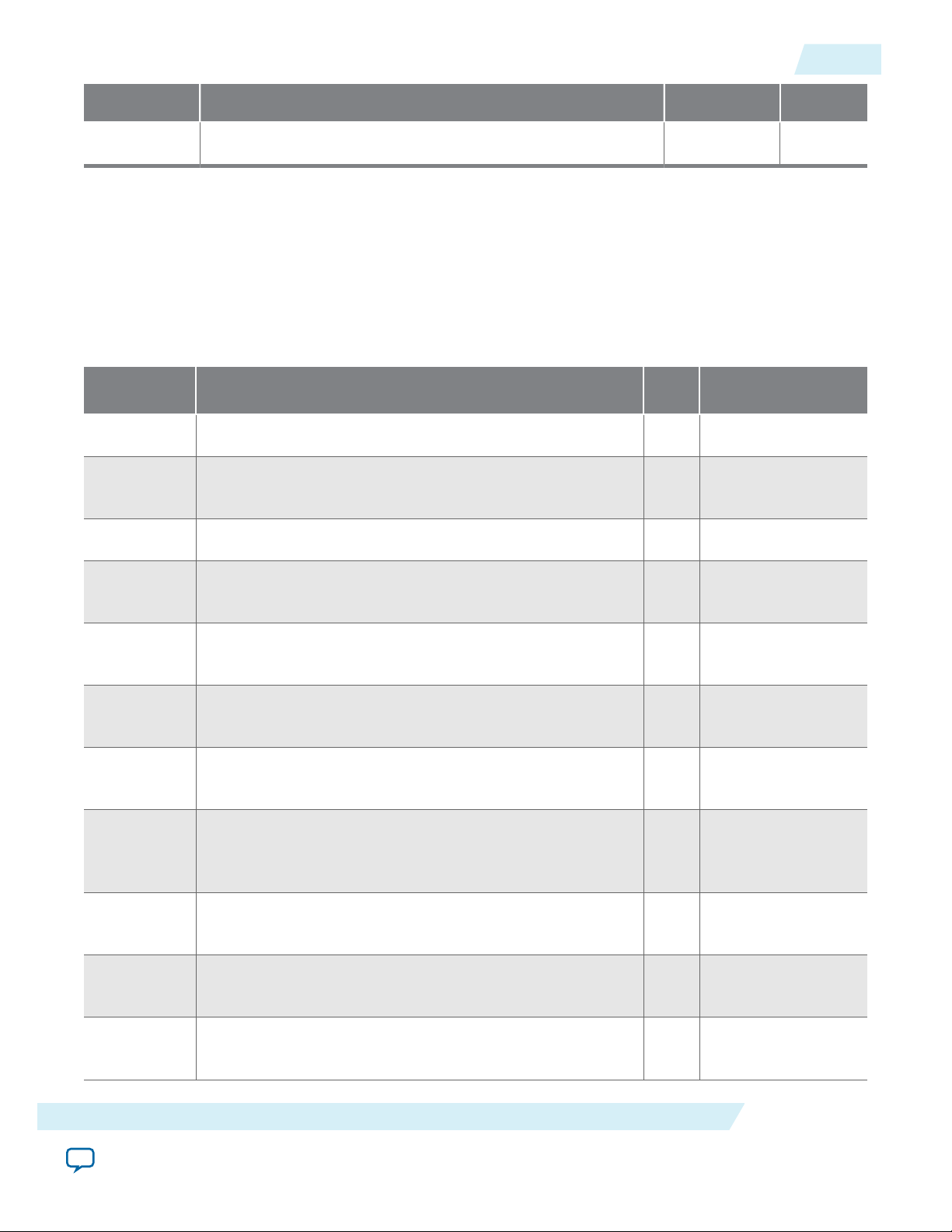

Table 1-6: Arria V Recommended Speed Grades for All Link Widths, Link Widths, and Application Layer

Clock Frequencies

UG-01154

2014.12.18

Link Rate Link Width Interface

Width

×1 64 bits 62.5

Application Clock

Frequency (MHz)

(2)

,125 –4,–5,–6

Recommended Speed Grades

×2 64 bits 125 –4,–5,–6

Gen1

×4 64 bits 125 –4,–5,–6

×8 128 bits 125 –4,–5,–6

125

–4,–5

Gen2

×1 64 bits

×2 64 bits 125 –4,–5

×4 128 bits 125 –4,–5

Table 1-7: Arria V GZ Recommended Speed Grades for All Widths, Link Widths, and Application Layer Clock

Frequencies

Link Rate Link Width Interface

Width

Application Clock

Frequency (MHz)

Recommended Speed Grades

x1 64 bits 62.5

(3)

,125 –1, –2, –3, –4

x2 64 bits 125 –1, –2, –3, –4

Gen1

x4 64 bits 125 –1, –2, –3, –4

x8 64 bits 250 –1, –2, –3

x8 128 Bits 125 –1, –2, –3, –4

(2)

This is a power-saving mode of operation

(3)

This is a power-saving mode of operation

(4)

The -4 speed grade is also possible for this configuration; however, it requires significant effort by the end

user to close timing.

Altera Corporation

Datasheet

Send Feedback

Page 12

UG-01154

2014.12.18

V-Series Recommended Speed Grades

1-11

Link Rate Link Width Interface

Width

x1 64 bits

x2 64 bits 125 –1, –2, –3, –4

x4 64 bits 250 –1, –2, –3

Gen2

x4 128 bits 125 –1, –2, –3, –4

x8 128 bits 250 –1, –2, –3

x8 256 bits 125 –1, –2, –3, –4

x1 64 bits 125 –1, –2, –3, –4

x2 64 bits 250 –1, –2, –3, –4

x2 128 bits 125 –1, –2, –3, –4

Gen3

x4 128 bits 250 –1, –2, –3

Application Clock

Frequency (MHz)

125

Recommended Speed Grades

–1, –2, –3, –4

x4 256 bits 125 –1, –2, –3,–4

x8 256 bits 250 –1, –2, –3

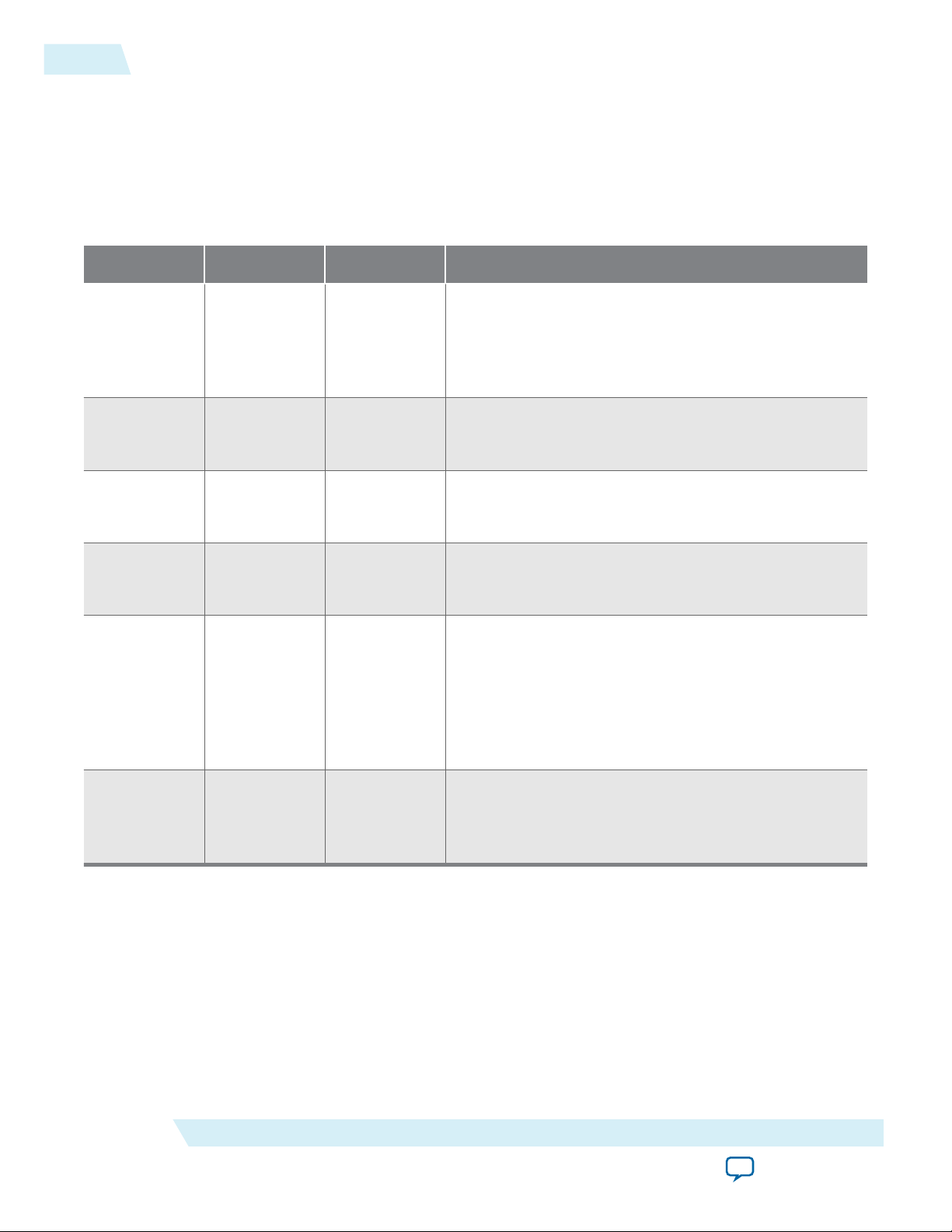

Table 1-8: Cyclone V Recommended Speed Grades for All Link Widths, Link Widths, and Application Layer

Clock Frequencies

The Gen2 data rate requires Cyclone V GT devices.

Link Rate Link Width Interface

Width

×1 64 bits 62.5

Gen1

×2 64 bits 125 –6, –7,–8

Application Clock

Frequency (MHz)

(5)

,125 –6, –7,–8

Recommended Speed Grades

×4 64 bits 125 –6, –7,–8

125

–7

Gen2

×1 64 bits

×2 64 bits 125 –7

×4 128 bits 125 –7

(5)

Datasheet

This is a power-saving mode of operation

Altera Corporation

Send Feedback

Page 13

1-12

V-Series Recommended Speed Grades

2014.12.18

Table 1-9: Stratix V Recommended Speed Grades for All Widths, Link Widths, and Application Layer Clock

Frequencies

UG-01154

Link Rate Link Width Interface

Width

x1 64 bits 62.5

x2 64 bits 125 –1, –2, –3, –4

Gen1

x4 64 bits 125 –1, –2, –3, –4

x8 64 bits 250 –1, –2, –3

x8 128 Bits 125 –1, –2, –3, –4

x1 64 bits

x2 64 bits 125 –1, –2, –3, –4

x4 64 bits 250 –1, –2, –3

Gen2

x4 128 bits 125 –1, –2, –3, –4

x8 128 bits 250 –1, –2, –3

Application Clock

Frequency (MHz)

(6)

,125 –1, –2, –3, –4

125

Recommended Speed Grades

(7)

–1, –2, –3, –4

x8 256 bits 125 –1, –2, –3, –4

x1 64 bits 125 –1, –2, –3, –4

x2 64 bits 250 –1, –2, –3, –4

x2 128 bits 125 –1, –2, –3, –4

Gen3

x4 128 bits 250 –1, –2, –3

x4 256 bits 125 –1, –2, –3,–4

x8 256 bits 250 –1, –2, –3

Related Information

• Area and Timing Optimization

• Altera Software Installation and Licensing Manual

(6)

This is a power-saving mode of operation

(7)

The -4 speed grade is also possible for this configuration; however, it requires significant effort by the end

user to close timing.

Altera Corporation

Datasheet

Send Feedback

Page 14

UG-01154

2014.12.18

• Setting up and Running Analysis and Synthesis

Steps in Creating a Design for PCI Express

Before you begin

Select the PCIe variant that best meets your design requirements.

• Is your design an Endpoint or Root Port?

• What Generation do you intend to implement?

• What link width do you intend to implement?

• What bandwidth does your application require?

• Does your design require CvP?

1. Select parameters for that variant.

2. Simulate using an Altera-provided example design. All of Altera's PCI Express example designs are

available under <install_dir>/ip/altera/altera_pcie/. Alternatively, create a simulation model and use your

own custom or third-party BFM. The Qsys Generate menu generates simulation models. Altera

supports ModelSim-Altera for all IP. The PCIe cores support the Aldec RivieraPro, Cadence NCsim,

Mentor Graphics ModelSim, and Synopsys VCS and VCS-MX simulators.

3. Compile your design using the Quartus II software. If the versions of your design and the Quartus II

software you are running do not match, regenerate your PCIe design.

4. Download your design to an Altera development board or your own PCB. Click on the All Develop‐

ment Kits link below for a list of Altera's development boards.

5. Test the hardware. You can use Altera's SignalTap® II Logic Analyzer or a third-party protocol

analyzer to observe behavior.

6. Substitute your Application Layer logic for the Application Layer logic in Altera's testbench. Then

repeat Steps 3–6. In Altera's testbenches, the PCIe core is typically called the DUT (device under test).

The Application Layer logic is typically called APPS.

Steps in Creating a Design for PCI Express

1-13

Datasheet

Related Information

• Parameter Settings on page 3-1

• Getting Started with the Avalon-MM DMA on page 2-1

• All Development Kits

Altera Corporation

Send Feedback

Page 15

2014.12.18

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Getting Started with the Avalon-MM DMA

2

UG-01154

Subscribe

Send Feedback

You can download the Qsys design example, pcie_de_ep_dma_g3x8_integrated.qsys, from the

<install_dir>/ ip/altera/altera_pcie/altera_pcie_hip_256_avmm/example_design/<dev> directory.

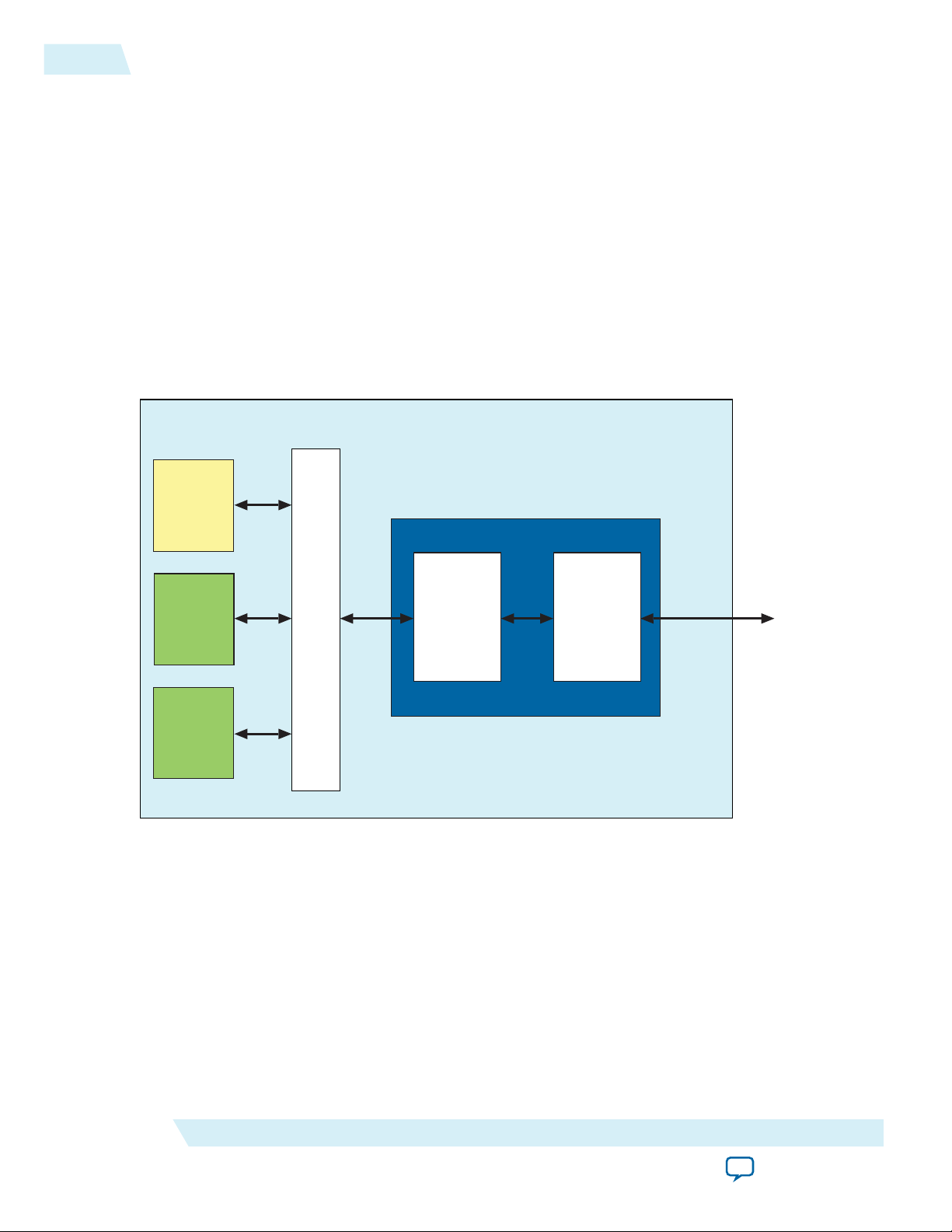

The design example includes the following components:

Avalon-MM DMA for PCI Express

This IP core includes highly efficient DMA Read and DMA Write modules. The DMA Read and Write

modules effectively move large blocks of data between the PCI Express address domain and the AvalonMM address domain using burst data transfers. Depending on the configuration you select, the DMA

Read and DMA Write modules use either a 128- or 256-bit Avalon-MM datapath.

In addition to high performance data transfer, the DMA Read and DMA Write modules ensure that the

requests on the PCI link adhere to the PCI Express Base Specification, 3.0. The DMA Read and Write

engines also perform the following functions:

• Divide the original request into multiple requests to avoid crossing 4KByte boundaries.

• Divide the original request into multiple requests to ensure that the maximum payload size is equal to

or smaller than the maximum payload size for write requests and maximum read request size for read

requests.

• Supports out-of-order completions when the original request is divided into multiple requests to

adhere to the read request size.

Using the DMA Read and DMA Write modules, you can specify descriptor entry table entries with large

payloads.

On-Chip Memory IP core

This IP core stores the DMA data. This 32-KByte memory has a 256-bit data width.

Descriptor Controller

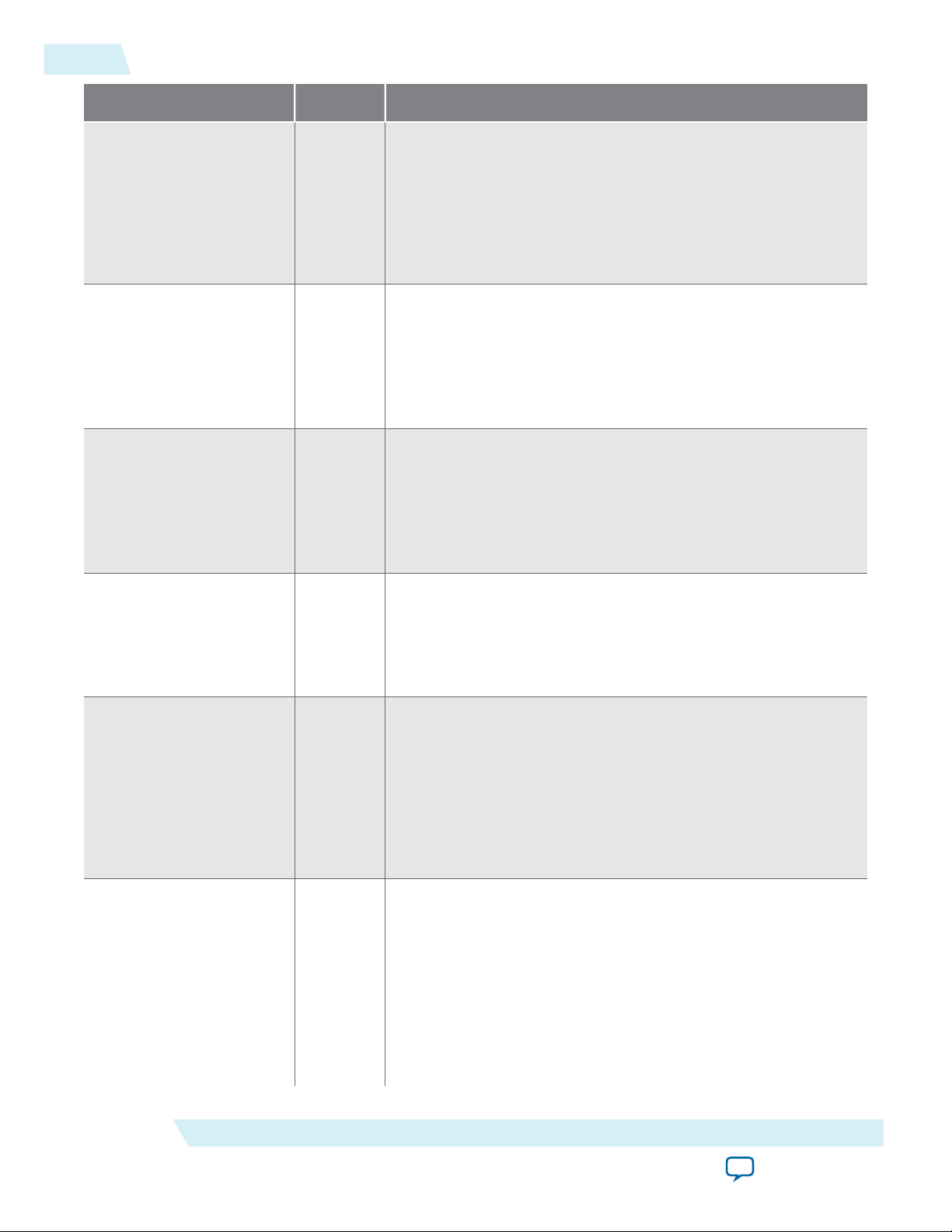

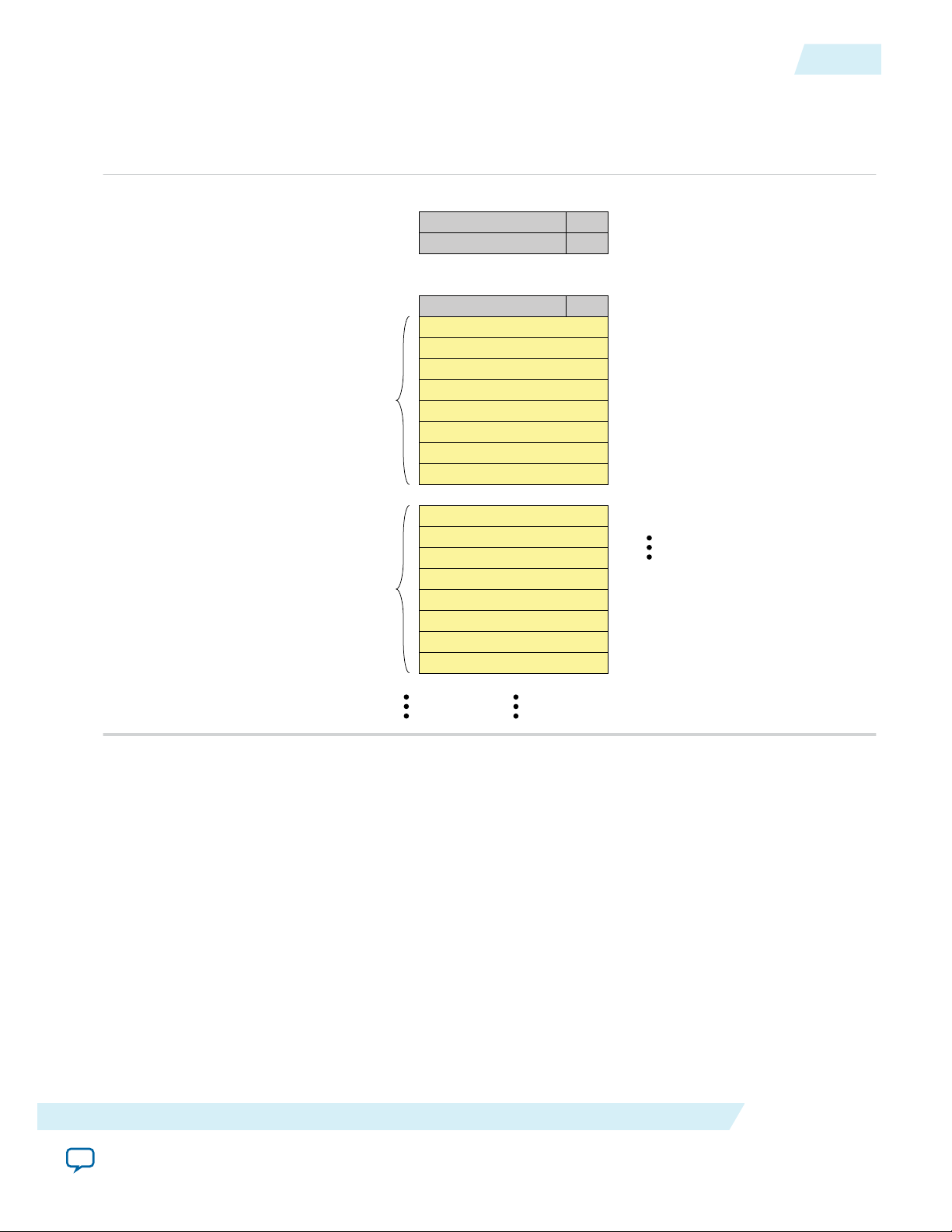

The Descriptor Controller manages the Read DMA and Write DMA modules. Host software programs

the Descriptor Controller internal registers with the location of the descriptor table. The Descriptor

Controller instructs the Read DMA module to copy the entire table to its internal FIFO. It then pushes the

table entries to DMA Read or DMA Write modules to transfer data. The Descriptor Controller also sends

DMA status upstream via an Avalon-MM TX slave port.

In this example design the Descriptor Controller parameter, Instantiate internal descriptor controller, is

on. Consequently, the Descriptor Controller is integrated into the Avalon-MM bridge as shown in the

figure below. Embedding the Descriptor Controller in Avalon-MM bridge simplifies the design. If you

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 16

Transaction,

Data Link,

and PHY

Layers

On-Chip

Memory

DMA Data

Descriptor

Controller

Qsys System Design V-Series Avalon-MM DMA for PCI Express

PCIe Link

Gen3 x8

DMA Engine

Avalon-MM to

PCIe TLP

Bridge

V-Series Avalon-MM DMA for PCI Express

Altera PCIe

Reconfig

Driver

Transceiver

Reconfiguration

Controller

Interconnect

2-2

Generating the Testbench

plan to replace the Descriptor Controller IP core with your own implementation, do not turn on the

Instantiate internal descriptor controller in the parameter editor when parameterizing the IP core.

Transceiver Reconfiguration Controller IP Core

The Transceiver Reconfiguration Controller performs offset cancellation to compensate for variations due

to process, voltage, and temperature (PVT).

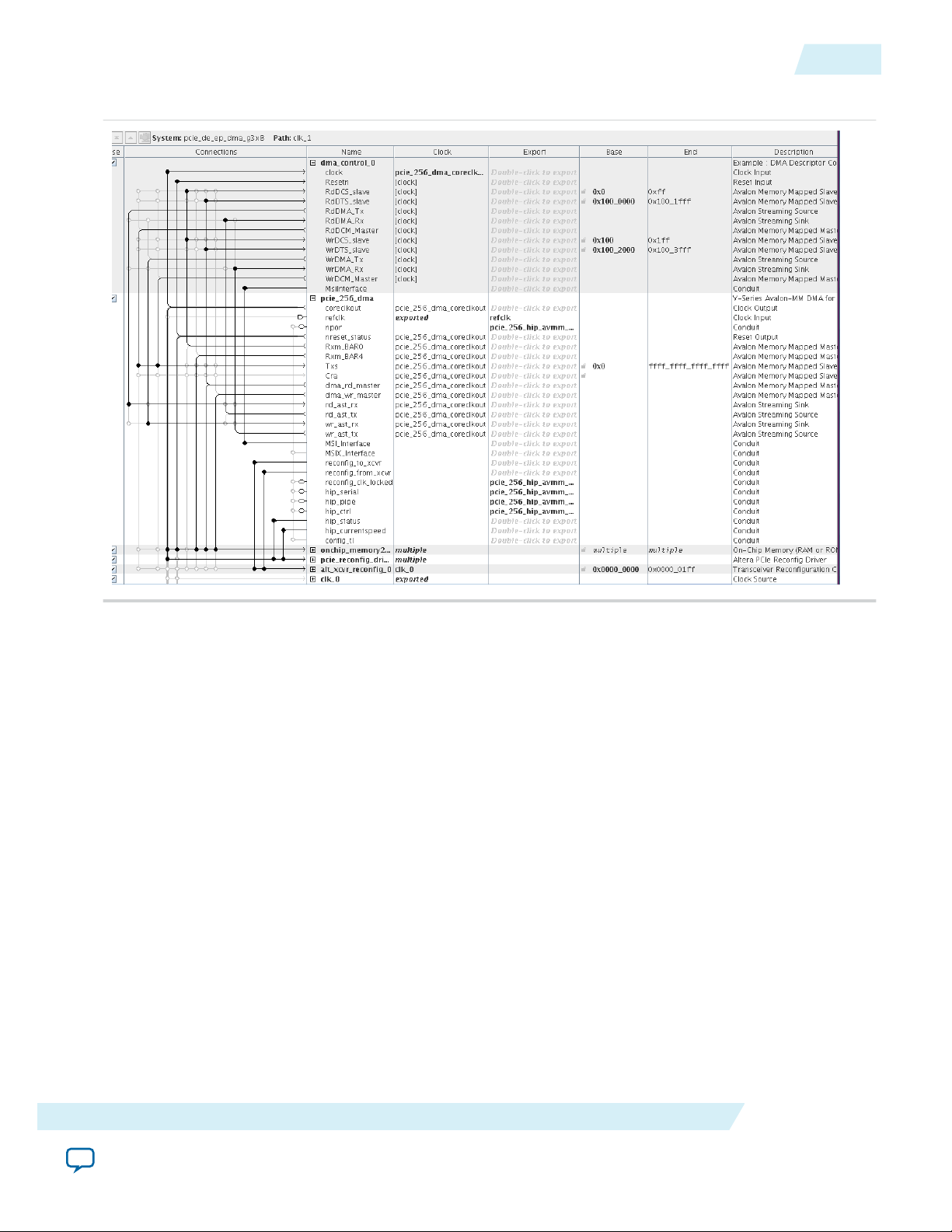

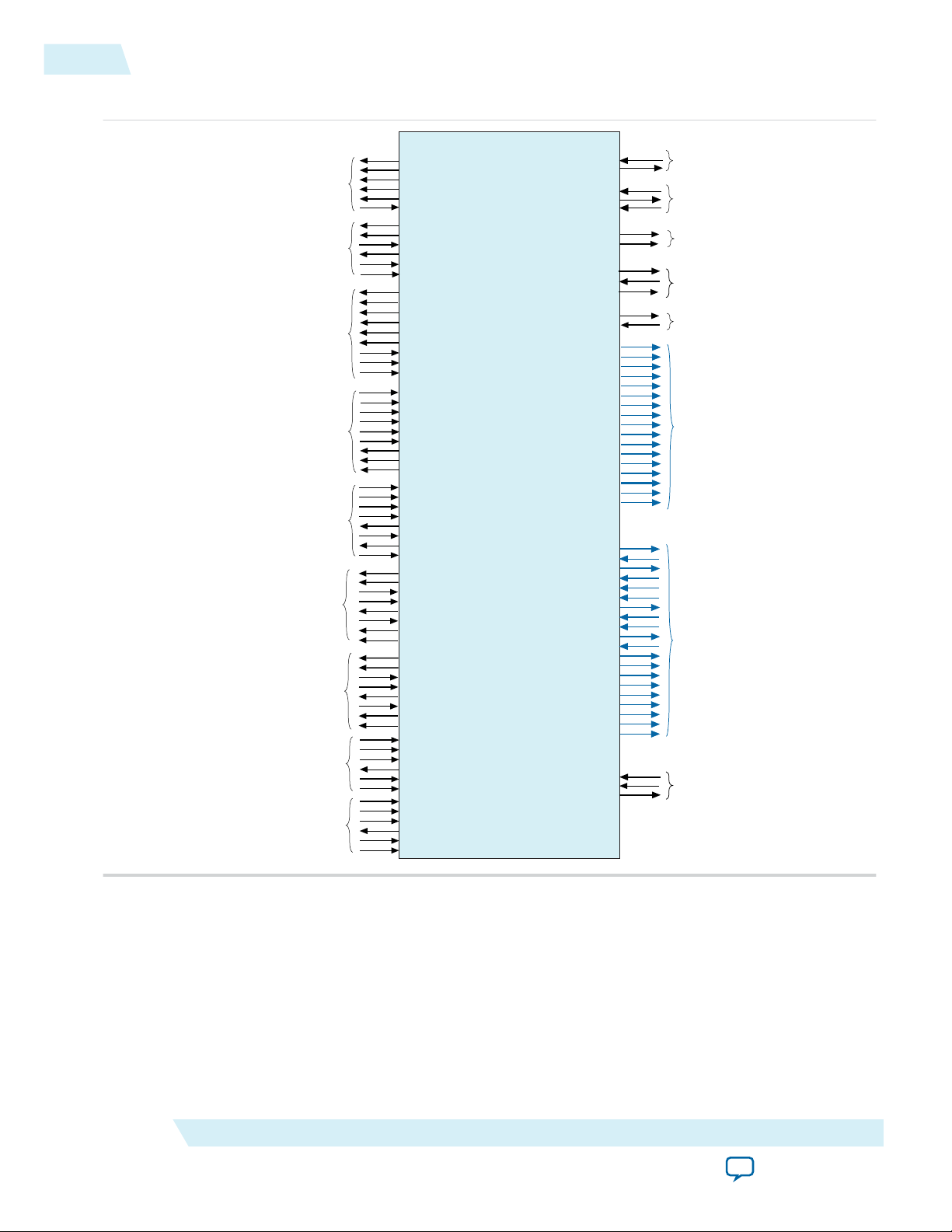

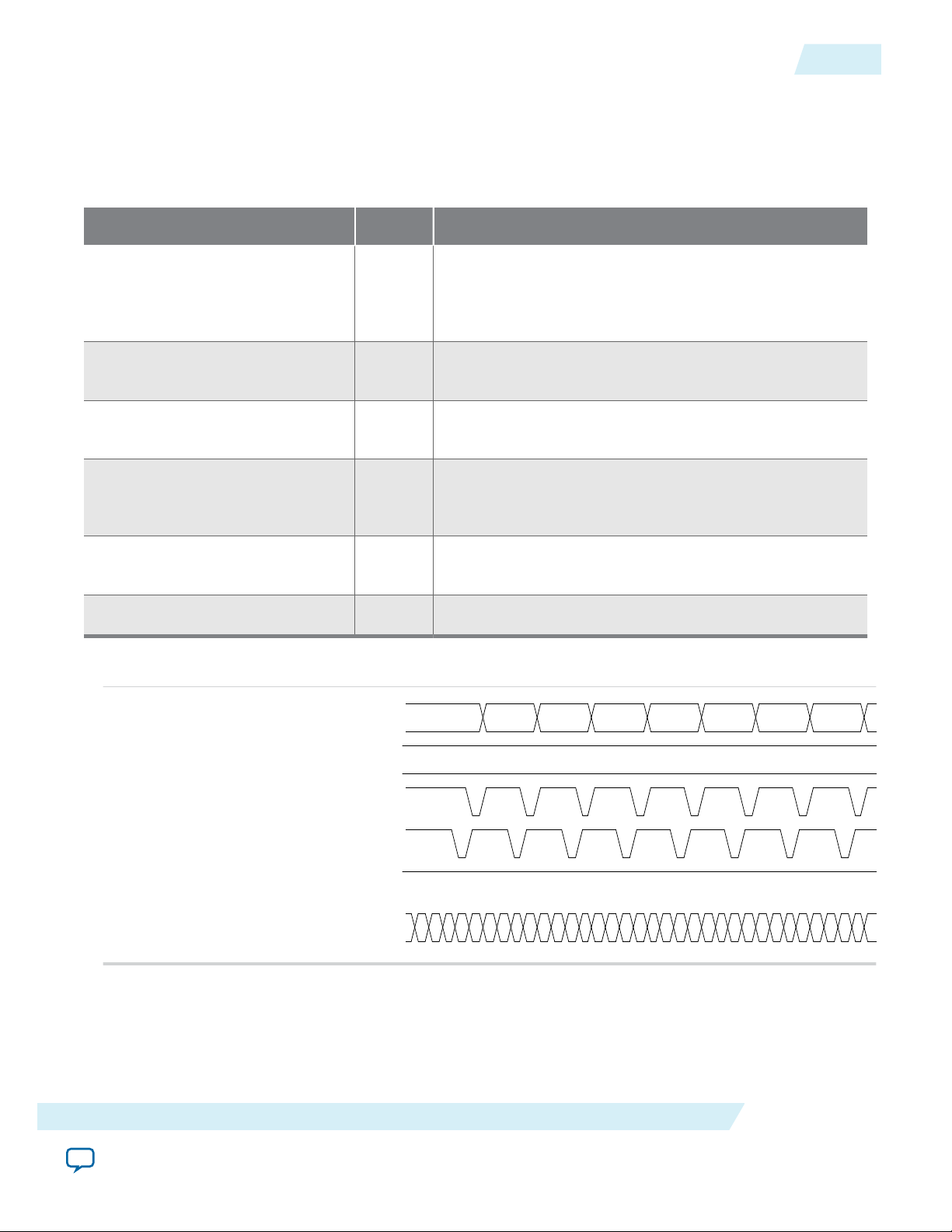

The following provides a high-level block diagram of the V-Series Avalon-MM DMA for PCI Express

Design Example.

Altera PCIe Reconfig Driver IP Core

The PCIe Reconfig Driver drives the Transceiver Reconfiguration Controller. This driver is a plain text

Verilog HDL file that you can modify if necessary to meet your system requirements.

Block Diagram of the Avalon-MM DMA for PCI Express Example Design

UG-01154

2014.12.18

Related Information

Generating the Testbench

Altera Corporation

• V-Series Avalon-MM DMA for PCI Express on page 8-8

• DMA Descriptor Controller Registers on page 5-15

1. Copy the example design, pcie_de_ep_dma_g3x8_integrated.qsys, from the installation directory:

<install_dir>/ip/altera/altera_pcie/altera_pcie_hip_256_avmm/example_design/ to your working directory.

2. Start Qsys, by typing the following command:

Getting Started with the Avalon-MM DMA

Send Feedback

Page 17

UG-01154

2014.12.18

Generating the Testbench

qsys-edit

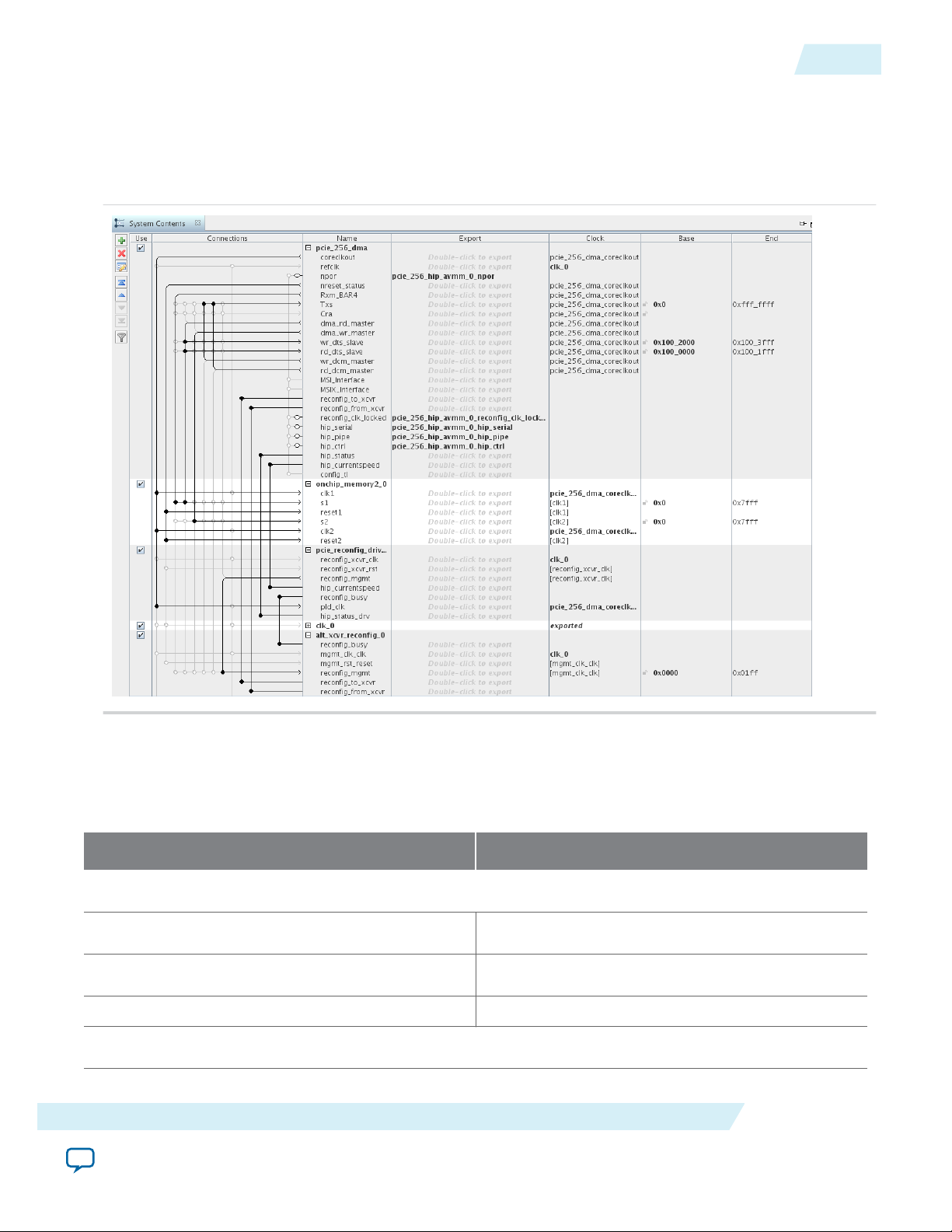

3. Open pcie_de_ep_dma_g3x8_integrated.qsys.

The following figure shows the Qsys system.

Figure 2-1: V-Series Avalon-MM DMA for PCI Express Qsys System Design

2-3

4. Click Generate > Generate Testbench System.

The Generation dialog box appears.

5. Specify the following parameters:

Table 2-1: Parameters to Specify in the Generation Dialog Box

Parameter Value

Testbench System

Create testbench Qsys system Standard, BFMs for standard Qsys interfaces

Create testbench simulation model Verilog

Allow mixed-language simulation You can leave this option off.

Output Directory

Getting Started with the Avalon-MM DMA

Send Feedback

Altera Corporation

Page 18

2-4

Understanding the Simulation Generated Files

Parameter Value

UG-01154

2014.12.18

Path

<working_dir>//pcie_de_ep_dma_g3x8_integrated

6. Click Generate.

Qsys generates the testbench.

Understanding the Simulation Generated Files

Table 2-2: Qsys Generation Output Files

Directory Description

<testbench_dir>/<variant_name>/testbench

Includes testbench subdirectories for the Aldec,

Cadence, Mentor, and Synopsys simulation tools

with the required libraries and simulation scripts.

<testbench_dir>/<variant_name>/testbench/<cad_

vendor>

<testbench_dir>/<variant_name>/testbench/<variant_

namer>_tb

Includes the HDL source files and scripts for the

simulation testbench.

Includes HDL design files

Understanding Simulation Log File Generation

Starting with the Quartus II 14.0 software release, simulation automatically creates a log file, altpcie_

monitor_<dev>_dlhip_tlp_file_log.log in your simulation directory.

Table 2-3: Sample Simulation Log File Entries

Time TLP Type Payload

(Bytes)

17989 RX CfgRd0 0004 04000001_0000000F_01080008

17989 RX MRd 0000 00000000_00000000_01080000

18021 RX CfgRd0 0004 04000001_0000010F_0108002C

18053 RX CfgRd0 0004 04000001_0000030F_0108003C

18085 RX MRd 0000 00000000_00000000_0108000C

Simulating the Example Design in ModelSim

1. In a terminal window, change directory to <workingdir>/pcie_de_ep_dma_g3x8_integrated/testbench/

mentor/ .

2. Start the ModelSim® simulator.

3. To run the simulation, type the following commands in a terminal window:

a. do msim_setup.tcl

b. ld_debug

TLP Header

Altera Corporation

Getting Started with the Avalon-MM DMA

Send Feedback

Page 19

UG-01154

2014.12.18

The ld_debug command compiles all design files and elaborates the top-level design without any

optimization.

c. run -all

The simulation performs the following operations:

• Various configuration accesses after the link is initialized

• Setup of the DMA controller to read data from the Transaction Layer Direct BFM’s shared memory

• Setup of the DMA controller to write the same data back to the Transaction Layer Direct BFM’s shared

memory

• Data comparison and report of any mismatch

Running a Gate-Level Simulation

The PCI Express testbenches run simulations at the register transfer level (RTL). However, it is possible to

create you own gate-level simulations. Contact your Altera Sales Representative for instructions and an

example that illustrate how to create a gate-level simulation from the RTL testbench.

Generating Quartus II Synthesis Files

Running a Gate-Level Simulation

2-5

1. On the Generate menu, select Generate HDL.

2. For Create HDL design files for synthesis, select Verilog.

You can leave the default settings for all other items.

3. Click Generate to generate files for Quartus II synthesis.

4. Click Finish when the generation completes.

Creating a Quartus II Project

You can create a new Quartus II project with the New Project Wizard, which helps you specify the

working directory for the project, assign the project name, and designate the name of the top-level design

entity.

1. On the Quartus II File menu, click then New Project Wizard, then Next.

2. Click Next in the New Project Wizard: Introduction (The introduction does not appear if you

previously turned it off.)

3. On the Directory, Name, Top-Level Entity page, enter the following information:

a. For What is the working directory for this project, browse to <project_dir>/pcie_de_ep_dma_g3x8_

integrated/.

b. For What is the name of this project? browse to the <project_dir>/pcie_de_ep_dma_g3x8_integrated/

synthesis directory and select pcie_de_ep_dma_g3x8_integrated.v.

c. Click Next.

4. For Project Type select Empty project.

5. Click Next.

6. On the Add Files page, add <project_dir>/pcie_de_ep_dma_g3x8_integrated/synthesis/ep_g3x8_avmm256_

integrated.qip to your Quartus II project.

7. Click Next to display the Family & Device Settings page.

Getting Started with the Avalon-MM DMA

Send Feedback

Altera Corporation

Page 20

2-6

Adding Virtual Pin Assignment to the Quartus II Settings File (.qsf)

8. On the Device page, choose the following target device family and options:

a. In the Family list, select Stratix V (GS/GT/GX/E).

b. In the Devices list, select Stratix V GX PCIe.

c. In the Available devices list, select 5SGXEA7K2F40C2.

9. Click Next to close this page and display the EDA Tool Settings page.

10.From the Simulation list, select ModelSim. From the Format list, select the HDL language you intend

to use for simulation.

11.Click Next to display the Summary page.

12.Check the Summary page to ensure that you have entered all the information correctly.

13.Click Finish.

14.Save your project.

Adding Virtual Pin Assignment to the Quartus II Settings File (.qsf)

To compile successfully you must add a virtual pin assignment statement for the PIPE interface to

your .qsf file. The PIPE interface is useful for debugging, but is not a top-level interface of the IP core.

1. Browse to the synthesis directory that includes the .qsf for your project, <project_dir>.

2. Open pcie_de_ep_dma_g3x8_integrated.qsf.

3. Add the following assignment statement:

set_instance_assignment -name VIRTUAL_PIN ON -to pcie_256_hip_avmm_0_hip_pipe_*

4. Save the .qsf file.

UG-01154

2014.12.18

Compiling the Design

1. On the Quartus II Processing menu, click Start Compilation.

2. After compilation, expand the TimeQuest Timing Analyzer folder in the Compilation Report. Note

whether the timing constraints are achieved in the Compilation Report.

If your design does not initially meet the timing constraints, you can find the optimal Fitter settings for

your design by using the Design Space Explorer. To use the Design Space Explorer, click Launch Design

Space Explorer on the Tools menu.

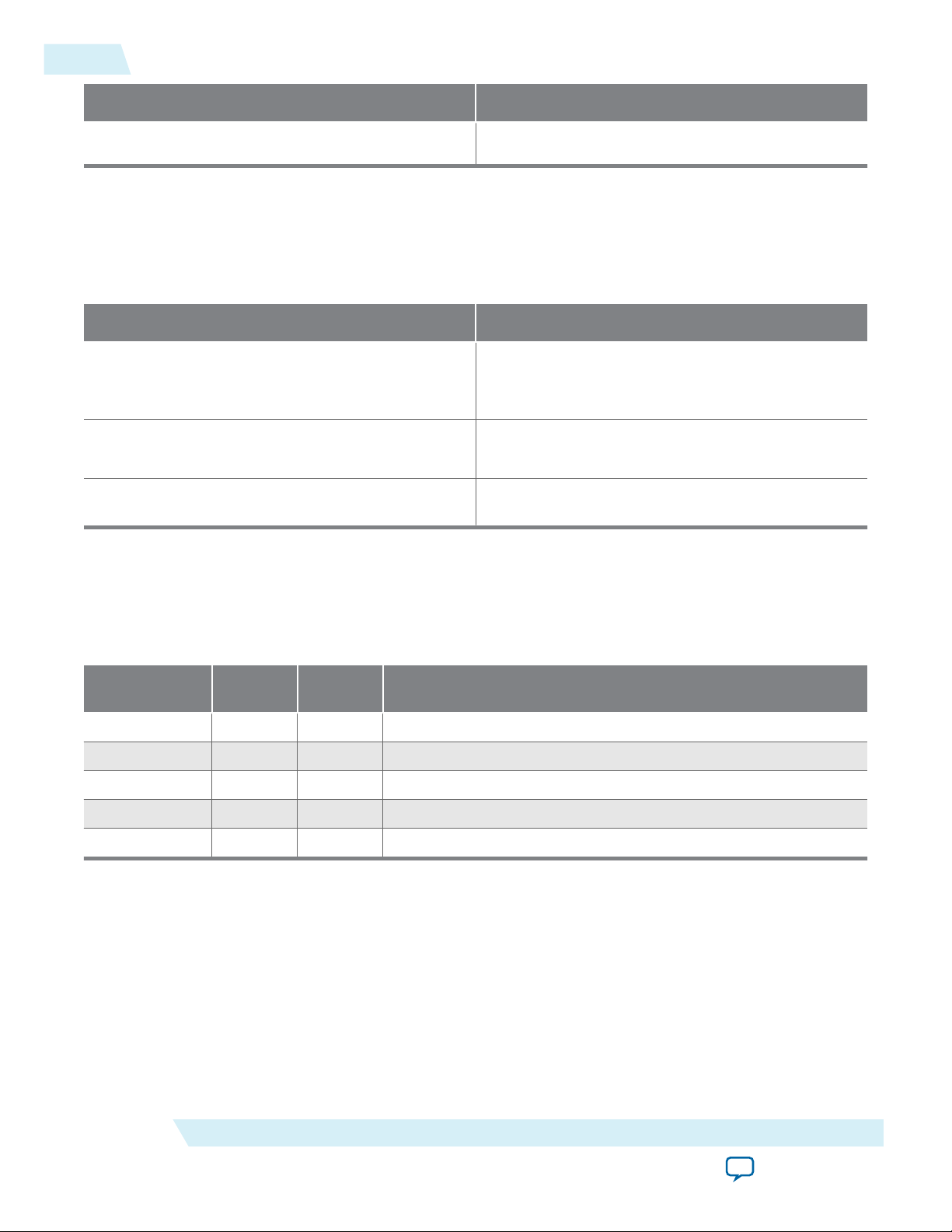

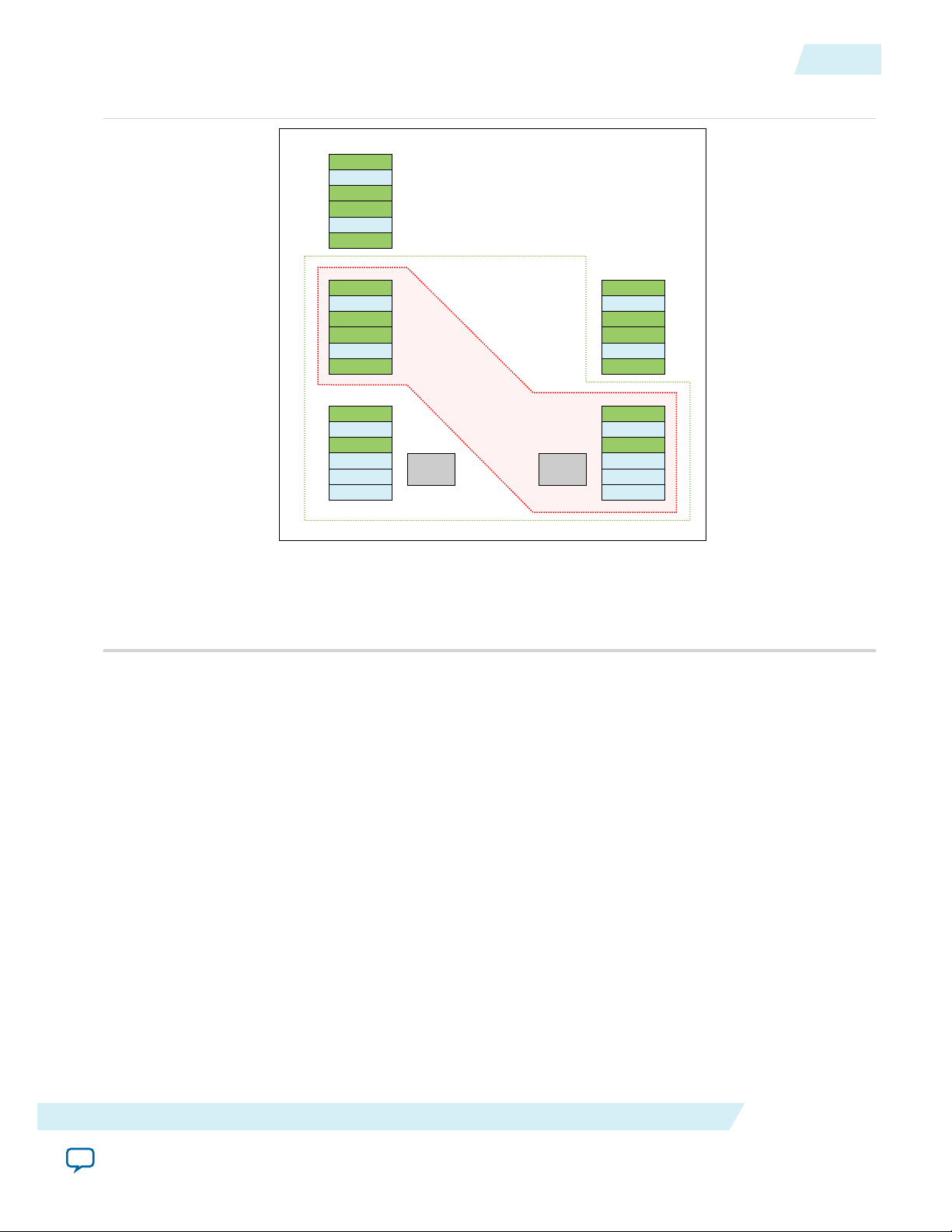

Descriptor Controller Connectivity when Instantiated Separately

This Qsys design example block diagram shows how to connect the external Descriptor Controller to the

Hard IP for PCI Expess with Avalon-MM DMA interface. This design example is available in <install_dir>/

ip/altera/altera_pcie/altera_pcie_hip_256_avmm/example_design/<dev>.

Altera Corporation

Getting Started with the Avalon-MM DMA

Send Feedback

Page 21

UG-01154

2014.12.18

Descriptor Controller Connectivity when Instantiated Separately

Figure 2-2: External Descriptor Controller Connectivity

2-7

Getting Started with the Avalon-MM DMA

Send Feedback

Altera Corporation

Page 22

2014.12.18

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Parameter Settings

3

UG-01154

Subscribe

Send Feedback

System Settings

Table 3-1: System Settings for PCI Express

Parameter Value Description

Number of Lanes x1, x2, ×4, ×8 Specifies the maximum number of lanes supported. Avalon-

MM Interface with DMA does not support x1 configurations.

Lane Rate Gen1 (2.5 Gbps)

Gen2 (2.5/5.0 Gbps)

Gen3 (2.5/5.0/8.0

Gbps)

Application

interface width

128-bit

256-bit

Specifies the maximum data rate at which the link can operate.

Specifies the width of the interface to the Application Layer.

The following table indicates the possible combinations.

Application

Interface Width

Configuration Application Layer

Clock Frequency

128 bits Gen1 x8 125 MHz

128 bits Gen2 x4 125 MHz

128 bits Gen2 x8 250 MHz

256 bits Gen2 x8 125 MHz

128 bits Gen3 x4 250 MHz

256 bits Gen3 x4 125 MHz

256 bits Gen3 x8 250 MHz

RX Buffer credit

allocation -

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

Minimum

Low

Determines the allocation of posted header credits, posted

data credits, non-posted header credits, completion header

ISO

9001:2008

Registered

Page 23

3-2

System Settings

Parameter Value Description

UG-01154

2014.12.18

performance for

received requests

Balanced

High

Maximum

credits, and completion data credits in the 16 KByte RX buffer.

The 5 settings allow you to adjust the credit allocation to

optimize your system. The credit allocation for the selected

setting displays in the message pane.

The Message window dynamically updates the number of

credits for Posted, Non-Posted Headers and Data, and

Completion Headers and Data as you change this selection.

Altera Corporation

Parameter Settings

Send Feedback

Page 24

UG-01154

2014.12.18

Parameter Value Description

• Minimum RX Buffer credit allocation -performance for

received requests )—configures the minimum PCIe

specification allowed for non-posted and posted request

credits, leaving most of the RX Buffer space for received

completion header and data. Select this option for

variations where application logic generates many read

requests and only infrequently receives single requests

from the PCIe link.

• Low—configures a slightly larger amount of RX Buffer

space for non-posted and posted request credits, but still

dedicates most of the space for received completion header

and data. Select this option for variations for which

application logic generates many read requests and

infrequently receives small bursts of requests from the

PCIe link. This option is recommended for typical

endpoint applications in which most of the PCIe traffic is

generated by a DMA engine that is located in the endpoint

application layer logic.

• Balanced—configures approximately half the RX Buffer

space to received requests and the other half of the RX

Buffer space to received completions. Select this option for

applications in which the received requests and received

completions are roughly equal.

• High—configures most of the RX Buffer space for received

requests and allocates a slightly larger than minimum

amount of space for received completions. Select this

option if most of the PCIe requests are generated by the

other end of the PCIe link and the local application layer

logic only infrequently generates a small burst of read

requests. This option is recommended for typical Root Port

applications in which most of the PCIe traffic is generated

by DMA engines located in the endpoints.

• Maximum—configures the minimum PCIe specification

allowed amount of completion space, leaving most of the

RX Buffer space for received requests. Select this option

when most of the PCIe requests are generated by the other

end of the PCIe link and the local application layer logic

never or only infrequently generates single read requests.

This option is recommended for control and status

Endpoint applications that don't generate any PCIe

requests of their own and are the target only of write and

read requests from the root complex.

System Settings

3-3

Parameter Settings

Send Feedback

Altera Corporation

Page 25

3-4

System Settings

Parameter Value Description

UG-01154

2014.12.18

Reference clock

frequency

Instantiate

internal

descriptor

controller

100 MHz

125 MHz

On/Off

The PCI Express Base Specification 3.0 requires a

100 MHz ±300 ppm reference clock. The 125 MHz reference

clock is provided as a convenience for systems that include a

125 MHz clock source. For more information about Gen3

operation, refer to 4.3.8 Refclk Specifications for 8.0 GT/s in the

specification.

For Gen3 operation, Altera recommends using a common

reference clock (0 ppm) because when using separate

reference clocks (non 0 ppm), the PCS occasionally must

insert SKP symbols, potentially causes the PCIe link to go to

recovery. Gen1 or Gen2 modes are not affected by this issue.

Systems using the common reference clock (0 ppm) are not

affected by this issue. The primary repercussion of this is a

slight decrease in bandwidth. On Gen3 x8 systems, this

bandwidth impact is negligible. If non 0 ppm mode is

required, so that separate reference clocks are being used,

please contact Altera for further information and guidance.

When you turn this option on, the descriptor controller is

included in the Avalon-MM bridge. When you turn this

option off, the descriptor controller should be included as a

separate external component. Turn this option on, if you plan

to use the Altera-provided descriptor controller in your

design. Turn this option off if you plan to modify or replace

the descriptor controller logic in your design.

Enable AvalonMM CRA Slave

hard IP status

port

Enable burst

capabilities for

RXM BAR2 port

Enable configu‐

ration via the

PCIe link

On/Off

Allows read and write access to bridge registers from the

interconnect fabric using a specialized slave port. This option

is required for Requester/Completer variants and optional for

Completer Only variants. Enabling this option allows read

and write access to bridge registers, except in the CompleterOnly single dword variations.

On/Off

When you turn on this option, the BAR2 RX Avalon-MM

masters is burst capable. If BAR2 is 32 bits and Burst capable,

then BAR3 is not available for other use. If BAR2 is 64 bits, the

BAR3 register holds the upper 32 bits of the address.

On/Off On, the Quartus II software places the Endpoint in the

location required for configuration via protocol (CvP). For

more information about CvP, click the Configuration via

Protocol (CvP) link below

Altera Corporation

Parameter Settings

Send Feedback

Page 26

UG-01154

2014.12.18

Base Address Register (BAR) Settings

Parameter Value Description

3-5

Use ATX PLL

On/Off When you turn on this option, the Hard IP for PCI Express

uses the ATX PLL instead of the CMU PLL. For other configu‐

rations, using the ATX PLL instead of the CMU PLL reduces

the number of transceiver channels that are necessary. This

option requires the use of the soft reset controller and does not

support the CvP flow.

Enable Hard IP

reset pulse at

power-up when

using the soft

reset controller

On/Off

When you turn on this option, the soft reset controller

generates a pulse at power up to reset the Hard IP. This pulse

ensures that the Hard IP is reset after programming the

device, regardless of the behavior of the dedicated PCI Express

reset pin, perstn. This option is available for Gen2 and Gen3

designs that use a soft reset controller.

Base Address Register (BAR) Settings

The type and size of BARs available depend on port type.

Table 3-2: BAR Registers

Parameter Value Description

Type Disabled

64-bit prefetchable memory

32-bit non-prefetchable memory

32-bit prefetchable memory

I/O address space

Size

N/A Qsys automatically calculates the required size after

If you select 64-bit prefetchable memory, 2

contiguous BARs are combined to form a 64-bit

prefetchable BAR; you must set the higher numbered

BAR to Disabled.

Defining memory as prefetchable allows contiguous

data to be fetched ahead. Prefetching memory is

advantageous when the requestor may require more

data from the same region than was originally

requested. If you specify that a memory is prefetch‐

able, it must have the following 2 attributes:

• Reads do not have side effects

• Write merging is allowed

The 32-bit prefetchable memory and I/O address

space BARs are only available for the Legacy

Endpoint.

you connect your components.

Parameter Settings

Send Feedback

Altera Corporation

Page 27

3-6

Device Identification Registers

UG-01154

2014.12.18

Device Identification Registers

Table 3-3: Device ID Registers

The following table lists the default values of the read-only Device ID registers. You can use the parameter editor

to change the values of these registers. Refer to Type 0 Configuration Space Registers for the layout of the Device

Identification registers.

Register Name Range Default Value Description

Vendor ID 16 bits 0x00000000

Sets the read-only value of the Vendor ID register. This

parameter can not be set to 0xFFFF per the PCI Express

Specification.

Address offset: 0x000.

Device ID 16 bits 0x00000001 Sets the read-only value of the Device ID register.

Address offset: 0x000.

Revision ID 8 bits 0x00000001 Sets the read-only value of the Revision ID register.

Address offset: 0x008.

Class code 24 bits 0x00000000 Sets the read-only value of the Class Code register.

Address offset: 0x008.

Subsystem

Vendor ID

16 bits 0x00000000 Sets the read-only value of the Subsystem Vendor ID

register in the PCI Type 0 Configuration Space. This

parameter cannot be set to 0xFFFF per the PCI Express

Base Specification. This value is assigned by PCI-SIG to

the device manufacturer.

Address offset: 0x02C.

Subsystem

Device ID

16 bits 0x00000000 Sets the read-only value of the Subsystem Device ID

register in the PCI Type 0 Configuration Space.

Address offset: 0x02C

Related Information

PCI Express Base Specification 2.1 or 3.0

PCI Express and PCI Capabilities Parameters

This group of parameters defines various capability properties of the IP core. Some of these parameters

are stored in the PCI Configuration Space - PCI Compatible Configuration Space. The byte offset

indicates the parameter address.

Altera Corporation

Parameter Settings

Send Feedback

Page 28

UG-01154

2014.12.18

Device Capabilities

Table 3-4: Capabilities Registers

Parameter Possible Values Default Value Description

Device Capabilities

3-7

Maximum

payload size

128 bytes

256 bytes

128 bytes Specifies the maximum payload size supported. This

parameter sets the read-only value of the max payload

size supported field of the Device Capabilities register

(0x084[2:0]). Address: 0x084.

Implement

completion

timeout

disable

On/Off On For Endpoints using PCI Express version 2.1 or 3.0, this

option must be On. The timeout range is selectable.

When On, the core supports the completion timeout

disable mechanism via the PCI Express Device

Control Register 2. The Application Layer logic must

implement the actual completion timeout mechanism

for the required ranges.

Error Reporting

Table 3-5: Error Reporting

Parameter Value Default Value Description

Advanced

error

reporting

(AER)

On/Off Off When On, enables the Advanced Error Reporting (AER)

capability.

ECRC

checking

ECRC

generation

Note:

1. Throughout this user guide, the terms word, dword and qword have the same meaning that they have

in the PCI Express Base Specification. A word is 16 bits, a dword is 32 bits, and a qword is 64 bits.

Related Information

PCI Express Base Specification Revision 2.1 or 3.0

Parameter Settings

Send Feedback

On/Off Off When On, enables ECRC checking. Sets the read-only

value of the ECRC check capable bit in the Advanced

Error Capabilities and Control Register. This

parameter requires you to enable the AER capability.

On/Off Off

When On, enables ECRC generation capability. Sets the

read-only value of the ECRC generation capable bit in

the Advanced Error Capabilities and Control

Register. This parameter requires you to enable the

AER capability.

Altera Corporation

Page 29

3-8

Link Capabilities

Link Capabilities

Table 3-6: Link Capabilities

Parameter Value Description

UG-01154

2014.12.18

Link port

number

Slot clock

configuration

0x01 Sets the read-only value of the port number field in the Link

Capabilities register.

On/Off When On, indicates that the Endpoint or Root Port uses the

same physical reference clock that the system provides on the

connector. When Off, the IP core uses an independent clock

regardless of the presence of a reference clock on the

connector.

MSI and MSI-X Capabilities

Table 3-7: MSI and MSI-X Capabilities

Parameter Value Description

MSI messages

requested

Implement MSI-X On/Off When On, enables the MSI-X functionality.

1, 2, 4, 8, 16 Specifies the number of messages the Application Layer can

request. Sets the value of the Multiple Message Capable

field of the Message Control register, 0x050[31:16].

MSI-X Capabilities

Table size [10:0] System software reads this field to determine the MSI-X Table

Table Offset [31:0] Points to the base of the MSI-X Table. The lower 3 bits of the

Table BAR

Indicator

Altera Corporation

Bit Range

size <n>, which is encoded as <n–1>. For example, a returned

value of 2047 indicates a table size of 2048. This field is readonly. Legal range is 0–2047 (211).

Address offset: 0x068[26:16]

table BAR indicator (BIR) are set to zero by software to form a

32-bit qword-aligned offset. This field is read-only.

[2:0] Specifies which one of a function’s BARs, located beginning at

0x10 in Configuration Space, is used to map the MSI-X table

into memory space. This field is read-only. Legal range is 0–5.

Parameter Settings

Send Feedback

Page 30

UG-01154

2014.12.18

Parameter Value Description

Power Management

3-9

Pending Bit Array

(PBA) Offset

[31:0] Used as an offset from the address contained in one of the

function’s Base Address registers to point to the base of the

MSI-X PBA. The lower 3 bits of the PBA BIR are set to zero by

software to form a 32-bit qword-aligned offset. This field is

read-only.

PBA BAR Indicator

[2:0] Specifies the function Base Address registers, located

beginning at 0x10 in Configuration Space, that maps the MSIX PBA into memory space. This field is read-only. Legal range

is 0–5.

Related Information

PCI Express Base Specification Revision 2.1 or 3.0

Power Management

Table 3-8: Power Management Parameters

Parameter Value Description

Endpoint L0s

acceptable

latency

Maximum of 64 ns

Maximum of 128 ns

Maximum of 256 ns

Maximum of 512 ns

Maximum of 1 us

Maximum of 2 us

Maximum of 4 us

No limit

This design parameter specifies the maximum acceptable

latency that the device can tolerate to exit the L0s state for any

links between the device and the root complex. It sets the

read-only value of the Endpoint L0s acceptable latency field of

the Device Capabilities Register (0x084).

This Endpoint does not support the L0s or L1 states. However,

in a switched system there may be links connected to switches

that have L0s and L1 enabled. This parameter is set to allow

system configuration software to read the acceptable latencies

for all devices in the system and the exit latencies for each link

to determine which links can enable Active State Power

Management (ASPM). This setting is disabled for Root Ports.

Parameter Settings

Send Feedback

The default value of this parameter is 64 ns. This is the safest

setting for most designs.

Altera Corporation

Page 31

3-10

PCIe Address Space Settings

Parameter Value Description

UG-01154

2014.12.18

Endpoint L1

Maximum of 1 us

acceptable

latency

Maximum of 2 us

Maximum of 4 us

Maximum of 8 us

Maximum of 16 us

Maximum of 32 us

No limit

PCIe Address Space Settings

Table 3-9: PCIe Address Space Settings

This value indicates the acceptable latency that an Endpoint

can withstand in the transition from the L1 to L0 state. It is an

indirect measure of the Endpoint’s internal buffering. It sets

the read-only value of the Endpoint L1 acceptable latency field

of the Device Capabilities Register.

This Endpoint does not support the L0s or L1 states. However,

a switched system may include links connected to switches

that have L0s and L1 enabled. This parameter is set to allow

system configuration software to read the acceptable latencies

for all devices in the system and the exit latencies for each link

to determine which links can enable Active State Power

Management (ASPM). This setting is disabled for Root Ports.

The default value of this parameter is 1 µs. This is the safest

setting for most designs.

Parameter Value Default Value Description

Address

width of

accessible

20–64

32

Specifies the width of the TX Slave Module Avalon-MM

address. This address is used unchanged as the PCIe

address.

PCIe

Memory

space

Altera Corporation

Parameter Settings

Send Feedback

Page 32

2014.12.18

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Interfaces and Signal Descriptions

4

UG-01154

Subscribe

Send Feedback

This chapter describes the top-level signals of V-Series the Avalon-MM DMA for PCI Express IP Core.

The Avalon-MM bridge includes high-performance, burst-capable Read DMA and Write DMA modules.

You can include the DMA Descriptor Controller that controls the Read DMA and Write DMA modules

in the Avalon-MM bridge or instantiate it separately. This variant is available for the following configura‐

tions:

• Gen1 x8

• Gen2 x4

• Gen2 x8

• Gen3 x4

• Gen3 x8

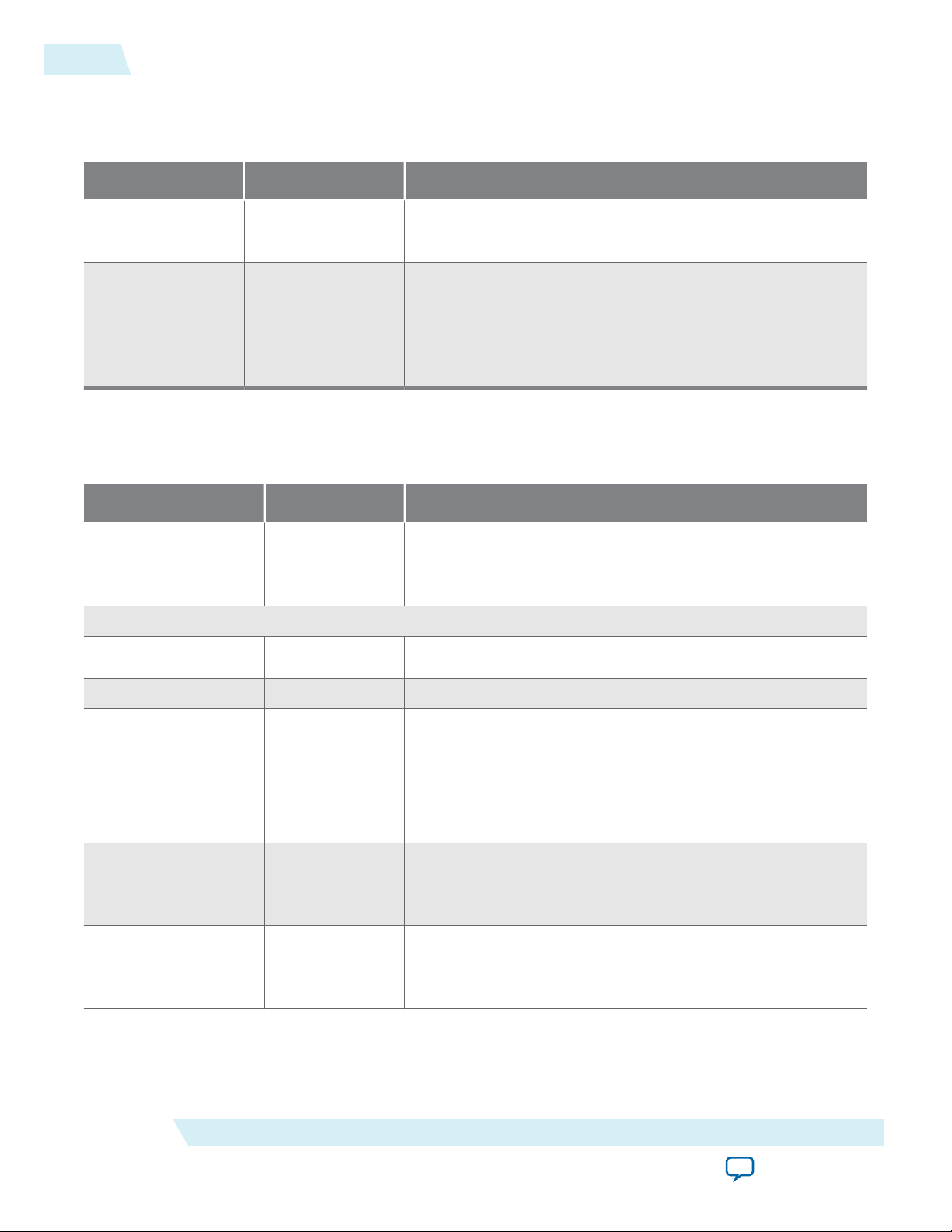

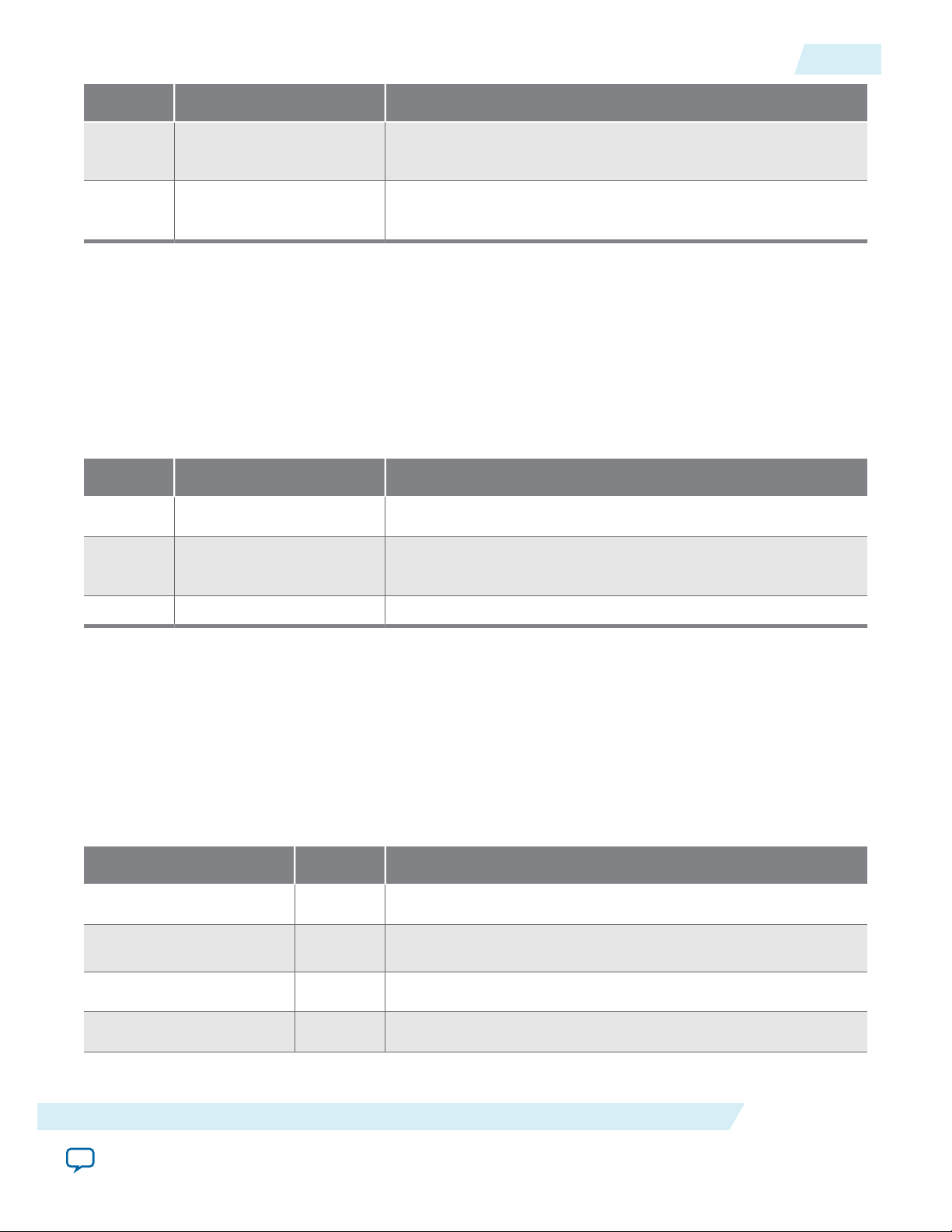

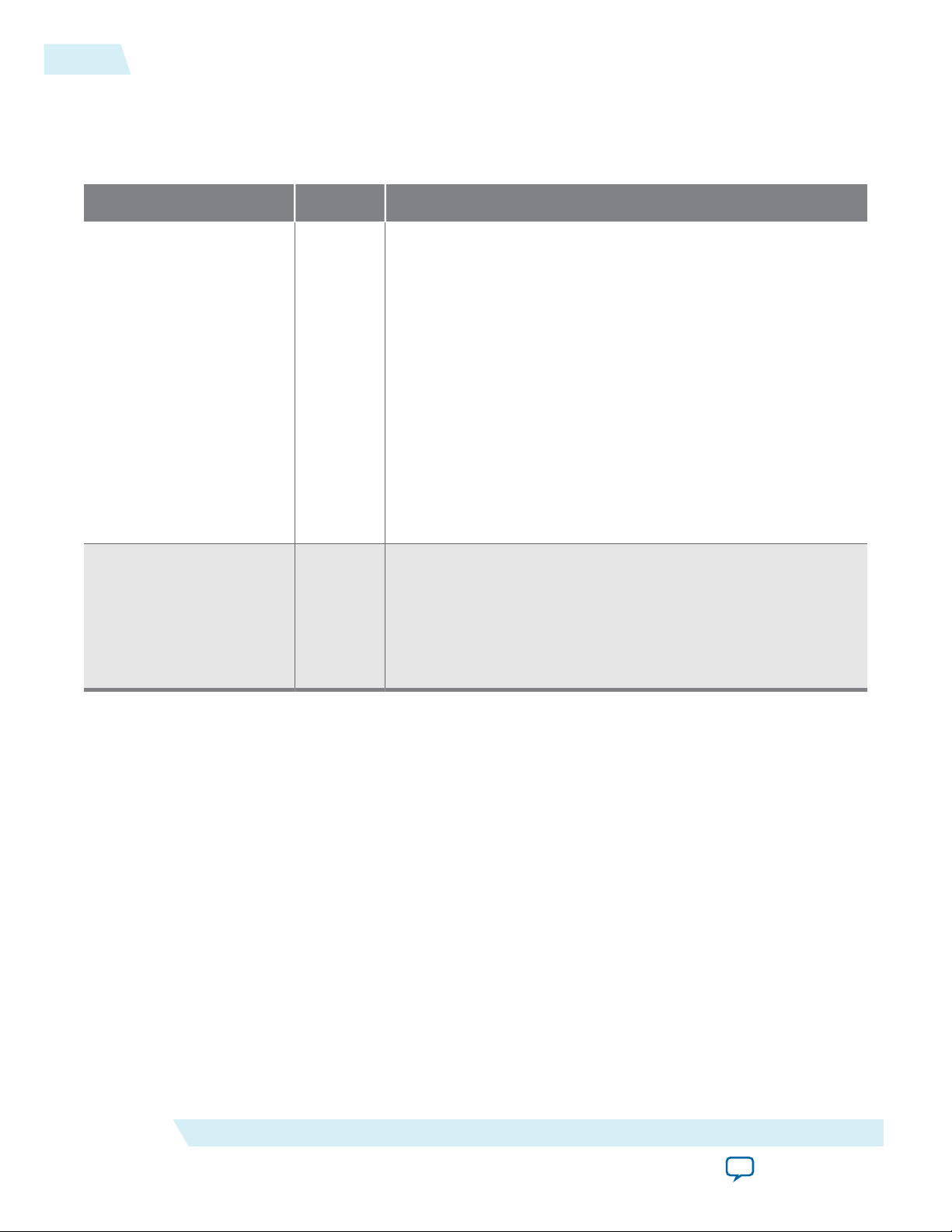

V-Series DMA Avalon-MM DMA Interface to the Application Layer

The following figures illustrate the signals in the variant that includes the high-performance, burst capable

Read DMA and Write DMA modules. The first figure illustrates this variant when the DMA Descriptor

Controller is embedded in the Avalon-MM bridge. The second figure illustrates this variant when the

DMA Descriptor Controller is instantiated separately. Depending on the device, the interface to the

Application Layer can be 128 or 256 bits.

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 33

tx_out0[<n>-1:0]

rx_in0[<n>-1:0]

Hard IP Serial

Hard IP for PCI Express Using Avalon-MM with DMA

TxsWriteData_i[31:0]

TxsRead_i

TxsWrite_i

TxsChipSelect_i

TxsAddress_i[<w>-1:0]

TxsByteEnable[3:0]

TxsReadData_o[31:0]

TxsReadDataValid_o

TxsWaitRequest_o

TX Slave:

Allows FPGA to Send Single

DWord Reads or Writes

from FPGA to Root Port

RxmRead_o

RdDCMAddress_0[63:0]

RdDCMByteEnable_o[3:0]

RdDCMReadDataValid_i

RdDCMRead Data_i[31:0]

RdDCMRead_o

RdDCMWaitRequest_i

RdDCMWriteData_o[31:0]

RdDCMWrite_o

RxmWrite_o

RxmAddress_o[<w>-1:0]

RxmBurstCount_o[5:0]

RxmByteEnable_o[3:0]

RxmWriteData_o[31:0]

RxmReadData_i[31:0]

RxmReadDataValid_i

RxmWaitRequest_i

CraWriteData_o[31:0]

CraWaitRequest_o

CraChipSelect_i

CraByteEnable_i[3:0]

CraAddress_i[13:0]

CraRead

CraWrite

CraReadData[31:0]

Host Access to

Control/Status Regs

of Avalon-MM Bridge

MsiIntfc_o[81:0]

MsixIntfc_o[15:0]

RdDmaWrite_o

RdDmaAddress_o[63:0]

RdDmaWriteData[<w>-1:0]

RdDmaBurstCount_o[4:0]

RdDmaWriteEnable_o[<w>-1:0]

RdDmaWaitRequest_i

Read DMA Avalon-MM :

Writes data from Host

memory to FPGA memory.

WrDmaRead_o

WrDmaAddress_o[63:0]

WrDmaReadData_i[<w>-1:0]

WrDmaBurstCount_o[<w>-1:0]

WrDmaWaitRequest_i

WrDmaReadDataValid_i

Write DMA Avalon-MM :

Fetch data from FPGA memory

before sending to Host memory.

MSI Inter face

npor

nreset_status

pin_perst

Reset &

Lock Status

Clocks

refclk

coreclkout

<w> = 32 or 64

Avalon-MM Master

Rd Descriptor Controller

Avalon-MM Master

Drives TX Slave to

Perform Single DWord

Transactions

to the Hard IP for PCIe

for Host to Access

Registers and Memory

1 RX Master for Each

BAR

cfg_par_err

derr_cor_ext_rcv

derr_cor_ext_rpl

derr_rpl

dlup

dlup_exit

ev128ns

ev1us

hotrst_exit

int_status[3:0]

ko_clp_spc_data[11:0]

ko_cpl_spc_header[7:0]

l2_exit

lane_act[3:0]

ltssmstate[4:0]

rx_par_err

tx_par_err

Hard IP Status

Hard IP Control &

Current Speed

Interfaces

test_in[31:0]

simu_mode_pipe

current_speed[1:0]

PIPE

(simulation

only)

reconfig_from_xcvr[<n>46-1:0]

reconfig_to_xcvr[<n>70-1:0]

reconfig_clk_locked

Transceiver

Reconfiguration

not required for

Arria 10

eidleinfersel[2:0]

phystatus0

powerdown0[1:0]

rxdata0[31:0]

rxdatak0

rxelecidle0

rxpolarity

rxstatus0[2:0]

rxvalid0

sim_ltssmstate[4:0]

sim_pipe_pclk_in

sim_pipe_rate[1:0]

txcompl0

txdata[<w>-1:0]

txdatak0

txdeemph0

txdetectrx0

txelecidle0

txmargin0

txswing

WrDCMAddress_0[63:0]

WrDCMByteEnable_o[3:0]

WrDCMReadDataValid_i

WrDCMRead Data_i[31:0]

WrDCMRead_o

WrDCMWaitRequest_i

WrDCMWriteData_o[31:0]

WrDCMWrite_o

WrDTSAddress_i[7:0]

WrDTSBurstCount_i[4:0]

WrDTSChipSelect_i

WrDTXWaitRequest_o

WrDTSWriteData_i[255:0]

WrDTSWrite_i

Wr Descriptor Controller

Avalon-MM Master

Drives TX Slave to

Perform Single DWord

Transactions

to the Hard IP for PCIe

Descriptor Controller

Avalon-MM Slave

Receives Requested

Write Descriptors from the

DMA Read Master

Descriptor Controller

Avalon-MM Slave

Receives Requested

Read Descriptors from the

DMA Read Master

RdDTSAddress_i[7:0]

RdDTSBurstCount_i[4:0]

RdDTSChipSelect_i

RdDTXWaitRequest_o

RdDTSWriteData_o[255:0]

RdDTSWrite_i

4-2

V-Series DMA Avalon-MM DMA Interface to the Application Layer

Figure 4-1: Signals When Descriptor Controller Is Embedded in the Avalon-MM Bridge

UG-01154

2014.12.18

Altera Corporation

Interfaces and Signal Descriptions

Send Feedback

Page 34

tx_out0[<n>-1:0]

rx_in0[<n>-1:0]

Hard IP Serial

Hard IP for PCI Express Using Avalon-MM with DMA

TxsWriteData_i[31:0]

TxsRead_i

TxsWrite_i

TxsChipSelect_i

TxsAddress_i[<w>-1:0]

TxsByteEnable[3:0]

TxsReadData_o[31:0]

TxsReadDataValid_o

TxsWaitRequest_o

TX Slave:

Allows FPGA to send single

dword reads or writes

from FPGA to Root Port

RxmRead_o

RxmWrite_o

RxmAddress_o[<w>-1:0]

RxmBurstCount_o[5:0]

RxmByteEnable_o[3:0]

RxmWriteData_o[31:0]

RxmReadData_i[31:0]

RxmReadDataValid_i

RxmWaitRequest_i

CraWriteData_o[31:0]

CraWaitRequest_o

CraChipSelect_i

CraByteEnable_i[3:0]

CraAddress_i[13:0]

CraRead

CraWrite

CraReadData[31:0]

Local Avalon-MM or

Host Access to

Control/Status Regs

of Avalon-MM Bridge

MsiIntfc_o[81:0]

MSIxIntfc_o[15:0]

RdDmaWrite_o

RdDmaAddress_o[63:0]

RdDmaWriteData[<w>-1:0]

RdDmaBurstCount_o[<w>-1:0]

RdDmaWriteEnable_o[<w>-1:0]

RdDmaWaitRequest_i

DMA Read Avalon-MM :

Writes data from Host

memory to FPGA memory.

WrDmaRead_o

WrDmaAddress_o[63:0]

WrDmaReadData_i[<w>-1:0]

WrDmaBurstCount_o[<w>-1:0]

WrDmaWaitRequest_i

WrDmaReadDataValid_i

DMA Write Avalon-MM :

Fetch data from FPGA memory

before sending to Host memory.

MSI and MSI-X

Interface

npor

reset_status

pin_perst

Reset &

Lock Status

Clocks

refclk

coreclkout

<w> = 32 or 64

Avalon-MM Master

for Host to access

registers and memory

1 RX Master for each

BAR

cfg_par_err

derr_cor_ext_rcv

derr_cor_ext_rpl

derr_rpl

dlup

dlup_exit

ev128ns

ev1us

hotrst_exit

int_status[3:0]

ko_cpl_spc_data[11:0]

ko_cpl_spc_header[7:0]

l2_exit

lane_act[3:0]

ltssmstate[4:0]

rx_par_err

tx_par_err

Hard IP Reset,

Status and

Link Training

Hard IP Control &

Current Speed

Interfaces

test_in[31:0]

simu_mode_pipe

current_speed[1:0]

tl_cfg_add[3:0]

tl_cfg_ctl[31:0]

tl_cfg_sts[52:0]

PIPE

(simulation

only)

reconfig_from_xcvr[<n>46-1:0]

reconfig_to_xcvr[<n>70-1:0]

reconfig_clk_locked

Transaction Layer

Transceiver

Reconfiguration

Configuration

eidleinfersel0[2:0]

phystatus0

powerdown0[1:0]

rxdata0[31:0]

rxdatak0

rxelecidle0

rxpolarity

rxstatus0[2:0]

rxvalid0

sim_ltssmstate[4:0]

sim_pipe_pclk_in

sim_pipe_rate[1:0]

txcompl0

txdata[<w>-1:0]

txdatak0

txdeemph0

txdetectrx0

txelecidle0

txmargin0

txswing

Host or

RdDmaRxData_i[159:0]

RdDmaRxValid_i

RdDmaRxReady_o

WrDmaRxData_i[159:0]

WrDmaRxValid_i

WrDmaRxReady_o

WrDmaTxData_o[31:0]

WrDmaTxValid_o

Descriptor Instructions

from

Descriptor Controller

to DMA Engine

RdDmaTxData_o[31:0]

RdDmaTxValid_o

UG-01154

2014.12.18

Read DMA Avalon-MM Master Port

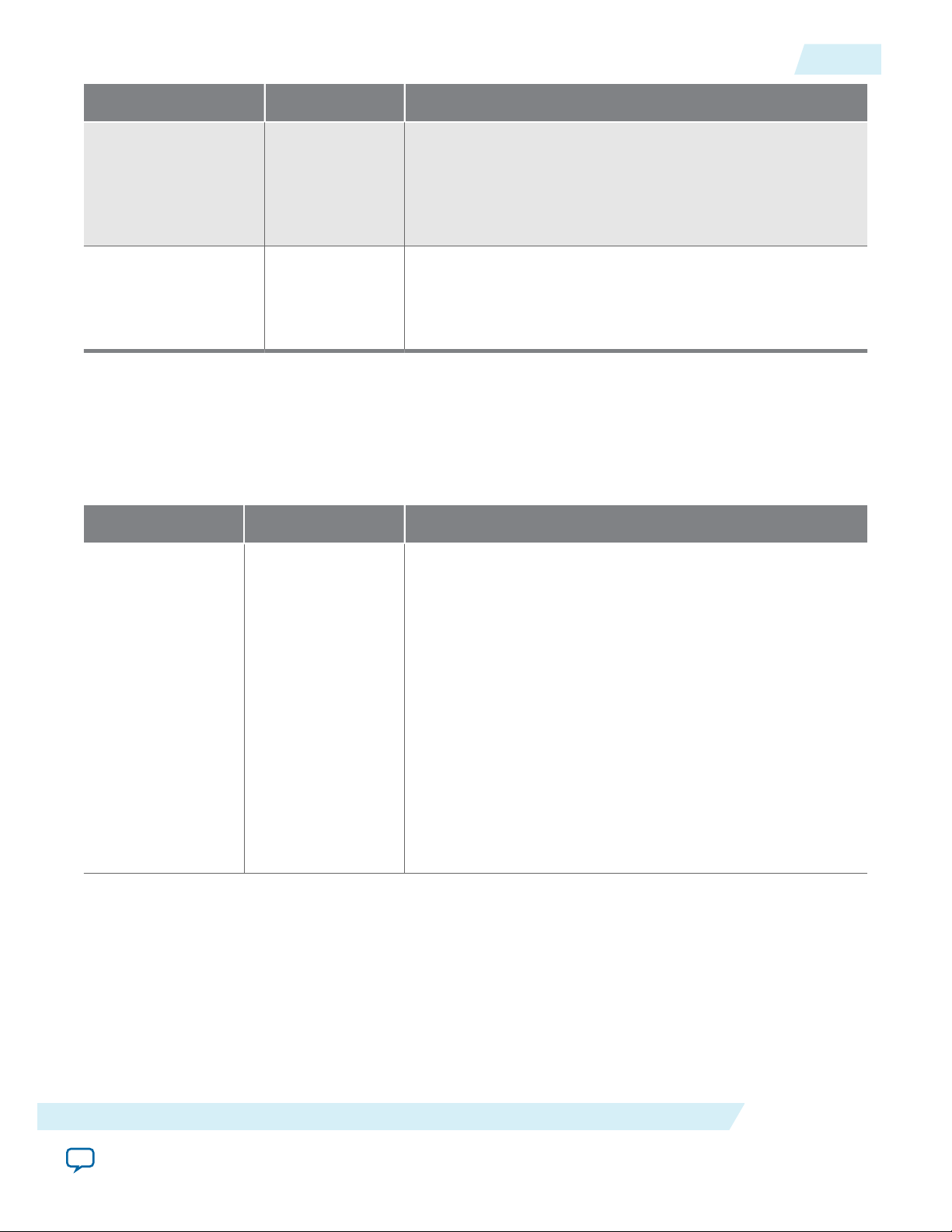

Figure 4-2: Signals When DMA Descriptor Controller Is Instantiated Externally

4-3

Read DMA Avalon-MM Master Port

Interfaces and Signal Descriptions

The Read DMA module sends memory read TLPs upstream. It writes the completion data to an external

Avalon-MM interface through the high throughput Read Master port. This port operates on descriptors

the IP core receives from the DMA Descriptor Controller.

Send Feedback

Altera Corporation

Page 35

read_data_mover\.RdDmaAddress_o[63:0]

read_data_mover\.RdDmaBurstCount_o[4:0]

read_data_mover\.RdDmaWrite_o

read_data_mover\.RdDmaWaitRequest_i

read_data_mover\.RdDmaWriteData_o[255:0]

read_data_mover\.RdDmaByteEnable_o[31:0]

100 080 100 180 200 280 300 380

. . . . . . . .

4-4

Read DMA Avalon-MM Master Port

The Read DMA Avalon-MM Master Port interface performs two functions:

• Provides the descriptor table to the Descriptor Controller: This module sends memory read requests to

fetch the descriptor table from host memory using upstream memory read requests on the Avalon-ST

read interface. This module writes the descriptor entries in to the Descriptor Controller FIFO using

this 128- or 256- bit Avalon-MM interface.

• Writes data to memory located in Avalon-MM space: After a DMA Read finishes fetching data from

the source address in host memory via normal DMA-Read operation, the Read DMA module writes

the data to the destination address in Avalon-MM address space via this interface.

Table 4-1: Read DMA 256-Bit Avalon-MM Master Interface

Signal Name Direction Description

UG-01154

2014.12.18

RdDmaWrite_o

Output When asserted, indicates that the Read DMA module is

ready to write read completion data to a memory

component in the Avalon-MM address space.

RdDmaAddress_o[63:0]

Output Specifies the write address in the Avalon-MM address

space for the read completion data.

RdDmaWriteData_o[127 or

255:0]

RdDmaBurstCount_o[4:0] or

[5:0]

Output The read completion data to be written to the

Avalon-MM address space.

Output Specifies the burst count in 128- or 256-bit words. This

bus is 5 bits for the 256-bit interface. It is 6 bits for the

128-bit interface.

RdDmaByteEnable_o[15 or

31:0]

RdDmaWaitRequest_i

Output Specifies which bytes of a 128- or 256-bit word are valid.

Input When asserted, indicates that the memory is not ready to

receive data.

Frequent assertion may incoming packet processing to

stop until RdDmaWaitRequest_i deasserts.

Figure 4-3: Read DMA Avalon-MM Master Writes Data to FPGA Memory

Altera Corporation

Interfaces and Signal Descriptions

Send Feedback

Page 36

\write_data_mover.\WrDmaAddress_o[63:0]

\write_data_mover\WrDmaBurstCount_o[4:0]

\write_data_mover.\WrDmaRead_o

\write_data_mover.\WrDmaWaitRequest_i

\write_data_mover\.WrDmaReadDataValid_i

\write_data_mover.\WrDmaReadData_i[255:0]

100 180 200 280 300 380 400 480 500

UG-01154

2014.12.18

Write DMA Avalon-MM Master Port

The Write DMA module fetches data from the Avalon-MM address space using this interface before

issuing memory write requests to transfer data to host memory.

Table 4-2: DMA Read 256-Bit Avalon-MM Master Interface

Signal Name Direction Description

Write DMA Avalon-MM Master Port

4-5

WrDmaRead_o

Output When asserted, indicates that the Write DMA module

reading data from a memory component in the

Avalon-MM address space to write to the PCIe address

space.

WrDmaAddress_o[63:0]

Output Specifies the address for the data to be read from a

memory component in the Avalon-MM address space .

WrDmaReadData_i[127 or

255:0]

WrDmaBurstCount_

o[4:0]or[5:0]

Input Specifies the completion data that will be written to the

PCIe address space by the Write DMA module.

Output Specifies the burst count in 128- or 256-bit words. This

bus is 5 bits for the 256-bit interface. It is 6 bits for the

128-bit interface

WrDmaWaitRequest_i

Input When asserted, indicates that the memory is not ready to

be read.

WrDmaReadDataValid_i

Input When asserted, indicates that WrDmaReadData_i is valid.

Figure 4-4: Write DMA Avalon-MM Master Reads Data from FPGA Memory

RX Master Module

The RX Master module translates read and write TLPs received from the PCIe link to Avalon-MM

requests for Qsys components connected to the interconnect. This module allows other PCIe

components, including host software, to access other Avalon-MM slaves connected in the Qsys system.

Interfaces and Signal Descriptions

Send Feedback

Altera Corporation

Page 37

4-6

RX Master Module

If burst mode is not enabled, the RX Master module only supports 32-bit read or write request. All other

requests received from the PCIe link are considered a violation of this device’s programming model, and

are therefore handled with the PCIe Completer Abort status. You can enable burst mode for BAR2 using

32-bit addressing or BAR2 and BAR3 using 64-bit addressing. When enabled, the module supports

dword, burst read or write requests. When the Descriptor Controller is internally instantiated, the RX

Master for BAR0 is used internally and not available for other uses.

Table 4-3: RX Master Control Interface Ports for BAR Access

Each BAR has one corresponding RX Master Control interface. In this table, <n> is the BAR number.

Signal Name Direction Description

UG-01154

2014.12.18

RxmRead_<n>_o

RxmWrite_<n>_o

RxmAddress_<n>_o[<w>1:0]

RxmBurstCount_<n>_

o[5:0]

RxmByteEnable_<n>_

o[<w>:0]

RxmDataWrite_<n>_

o[<w>:0]

Output When asserted, indicates an Avalon-MM read request.

Output When asserted, indicates an Avalon-MM write request.

Output Specifies the Avalon-MM byte address. Because all addresses are

byte addresses, the meaningful bits of this address are [<w>-1:2].

Bits 1 and 0 have a value of 0. <w> can be 32 or 64.

Output Specifies the burst count in dwords (32 bits). This optional signal

is available for BAR2 when you turn on Enable burst capabili‐

ties for RXM BAR2 ports.

Output Specifies the valid bytes of data to be written. <w> has the

following values:

• 4: for the non-bursting RX Master

• 32: for the bursting 128-bit Avalon-MM interface

• 64: for the bursting 256-bit Avalon-MM interface

Output Specifies the Avalon-MM write data. <w> has the following

values:

• 32: for the non-bursting RX Master

• 128: for the bursting 128-bit Avalon-MM interface

• 256: for the bursting 256-bit Avalon-MM interface

RxmReadData_<n>_i[<w>

:0]

RxmReadDataValid_<n>_

i[31:0]

RxmWaitRequest_<n>_i

Altera Corporation

Input Specifies the Avalon-MM read data. <w> has the following

values:

• 32: for the non-bursting RX Master

• 128: for the bursting 128-bit Avalon-MM interface

• 256: for the bursting 256-bit Avalon-MM interface

Input

When asserted, indicates that RxmReadData_i[31:0]is

valid.

Input When asserted indicates that the control register access Avalon-

MM slave port is not ready to respond.

Interfaces and Signal Descriptions

Send Feedback

Page 38

AvRxmAddress_<n>_o[63:0]

AvRxmWrite_<n>_o

AvRxmWriteData_<n>_o[31:0]

AvRxmByteEnable_<n>_o[3:0]

AvRxmWaitRequest_<n>_i

AvRxmRead_<n>_o

AvRxmReadDataValid_<n>_i

AvRxmReadData_<n>_i[31:0]

800041080

00001010 00000000 00000001 00003800 00000000

8000410C 80004110 80004114 80004118 80004100

128: for the bursting 128-bit Avalon-MM interface

UG-01154

2014.12.18

Figure 4-5: RXM Master Writes To Memory in the Avalon-MM Address Space

TX Slave Module

4-7

TX Slave Module

The TX Slave module translates Avalon-MM master read and write requests to PCI Express TLPs for the

Root Port. The TX Slave Control module supports a single outstanding non-bursting request. It typically

sends status updates to the host. This is a 32-bit Avalon-MM slave bus.

Table 4-4: TX Slave Control

Signal Name Direction Description

TxsChipSelect_i

TxsRead_i

TxsWrite_i

TxsWriteData_i[<w>1:0]

TxsAddress_i[<w>-1:0]

TxsByteEnable_i[3:0]

TxsReadData_o[<w>1:0]

TxsReadDataValid_o

Input When asserted, indicates that this slave interface is selected.

Input When asserted, specifies an TX Avalon-MM slave read request

from the Root Complex or Root Port.

Input When asserted, specifies an TX Avalon-MM slave write request

to the Root Complex or Root Port.

Input Specifies the Avalon-MM data for a write command.

Input Specifies the Avalon-MM byte address for the read or write

command. The width of this address bus is specified by the

parameter Address width of accessible PCIe memory space.

Input Specifies the valid bytes for a write command.

Output Specifies the read completion data.

Output

When asserted, indicates that TxsReadData_o[31:0] is valid.

Interfaces and Signal Descriptions

Send Feedback

Altera Corporation

Page 39

AvTxsChipSelect_i

AvTxsWrite_i

AvTxsAddress_i[27:0]

AvTxsByteEnable_i[3:0]

AvTxsWriteData_i[31:0]

AvTxsWaitRequest_o

AvTxsRead_i

AvTxsReadData_o[31:0]

AvTxsReadDataValid_o

1

4-8

32-Bit Non-Bursting Avalon-MM Control Register Access (CRA) Slave Signals

Signal Name Direction Description

UG-01154

2014.12.18

TxsWaitRequest_o

Output When asserted, indicates that the Avalon-MM slave port is not