Page 1

2014.09.02

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Altera Unique Chip ID IP Core User Guide

ug-altchipid

Subscribe

The Altera Unique Chip ID (ALTCHIP_ID) IP core allows you to uniquely identify the target FPGA before

device programming. This protects your device from receiving unauthorized programming data. Use the

IP Catalog and parameter editor to customize and generate the ALTCHIP_ID IP core.

The chip ID block has a 64 bit unique ID per die. The unique chip ID is read out from a 90 bit circular shift

register by a three pin serial interface. The initial 64 bits contain the unique ID value. The last 26 bits are a

concatenation of various fuse bits set during the manufacturing flow; these bits have Altera reserved values.

The Unique Chip ID register is implemented as a barrel shift register. For more information about customizing

IP cores.

This IP core is not supported for Arria 10 designs.Note:

Related Information

• Introduction to Altera IP Cores

• Altera IP Release Notes

Functional Description

Send Feedback

At the initial state, the data_valid signal is low because no data is read from the chip ID block. After feeding

a clock signal to the clkin input port, the ALTCHIP_ID IP core begins to acquire the unique chip ID via

the chip ID block. After acquiring the unique chip ID, the IP core asserts the data_valid signal to indicate

that the unique chip ID value at the output port is ready for retrieval.

The operation repeats only when you provide another clock signal while the data_valid signal is low. If

the data_valid signal is high when you provide another clock signal, the operation stops because the

chip_id[63..0] output holds the chip ID.

A minimum of 67 clock cycles are required for the data_valid signal to go high.

The chip_id [63:0]output port holds the value of the unique chip ID until you reconfigure the device or

reset the IP core.

Installing and Licensing IP Cores

The Altera IP Library provides many useful IP core functions for production use without purchasing an

additional license. You can evaluate any Altera IP core in simulation and compilation in the Quartus II

software using the OpenCore evaluation feature. Some Altera IP cores, such as MegaCore®functions, require

©

2014 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words

and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other

words and logos identified as trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with

Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes

no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly

agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 2

acds

quartus - Contains the Quartus II software

ip - Contains the Altera IP Library and third-party IP cores

altera - Contains the Altera IP Library source code

<IP core name> - Contains the IP core source files

2

Customizing and Generating IP Cores

that you purchase a separate license for production use. You can use the OpenCore Plus feature to evaluate

IP that requires purchase of an additional license until you are satisfied with the functionality and performance.

After you purchase a license, visit the Self Service Licensing Center to obtain a license number for any Altera

product.

Figure 1: IP Core Installation Path

ug-altchipid

2014.09.02

Note:

The default IP installation directory on Windows is <drive>:\altera\<version number>; on Linux it

is <home directory>/altera/ <version number>.

Related Information

• Altera Licensing Site

• Altera Software Installation and Licensing Manual

Customizing and Generating IP Cores

You can customize IP cores to support a wide variety of applications. The Quartus II IP Catalog and parameter

editor allow you to quickly select and configure IP core ports, features, and output files.

IP Catalog and Parameter Editor (replaces MegaWizard Plug-In Manager)

The Quartus II IP Catalog (Tools > IP Catalog) and parameter editor help you easily customize and integrate

IP cores into your project. You can use the IP Catalog and parameter editor to select, customize, and generate

files representing your custom IP variation.

Note:

The IP Catalog (Tools > IP Catalog) and parameter editor replace the MegaWizard™Plug-In Manager

for IP selection and parameterization, beginning in Quartus II software version 14.0. Use the IP

Catalog and parameter editor to locate and paramaterize Altera IP cores.

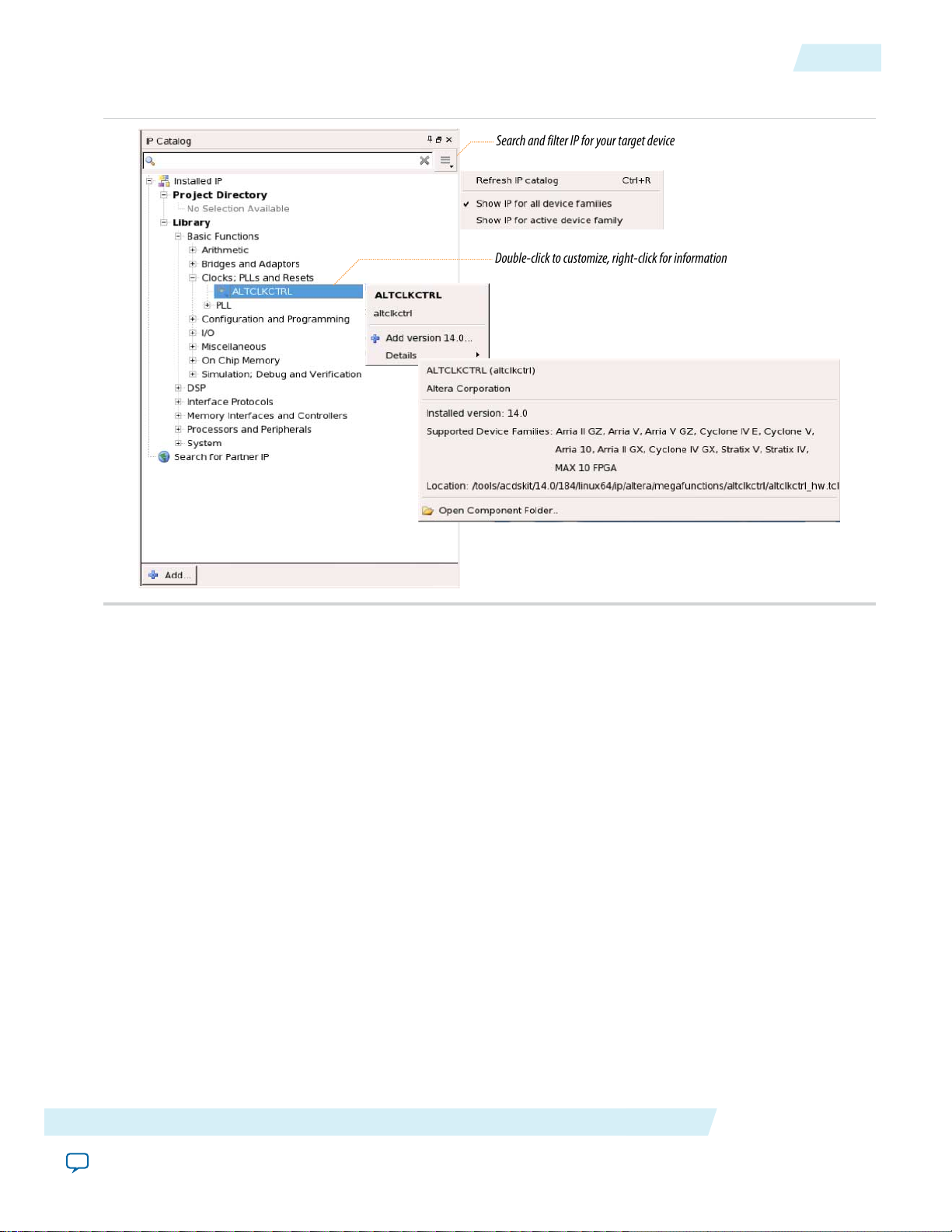

The IP Catalog lists IP cores available for your design. Double-click any IP core to launch the parameter

editor and generate files representing your IP variation. The parameter editor prompts you to specify an IP

variation name, optional ports, and output file generation options. The parameter editor generates a toplevel Qsys system file (.qsys) or Quartus II IP file (.qip) representing the IP core in your project. You can

also parameterize an IP variation without an open project.

Use the following features to help you quickly locate and select an IP core:

• Filter IP Catalog to Show IP for active device family or Show IP for all device families.

• Search to locate any full or partial IP core name in IP Catalog. Click Search for Partner IP, to access

partner IP information on the Altera website.

• Right-click an IP core name in IP Catalog to display details about supported devices, open the IP core's

installation folder, andor view links to documentation.

Altera Corporation

Altera Unique Chip ID IP Core User Guide

Send Feedback

Page 3

Search and filter IP for your target device

Double-click to customize, right-click for information

ug-altchipid

2014.09.02

Figure 2: Quartus II IP Catalog

Using the Parameter Editor

3

Note:

The IP Catalog is also available in Qsys (View > IP Catalog). The Qsys IP Catalog includes exclusive

system interconnect, video and image processing, and other system-level IP that are not available in

the Quartus II IP Catalog. For more information about using the Qsys IP Catalog, refer to Creating

a System with Qsys in the Quartus II Handbook.

Related Information

• Creating a System with Qsys

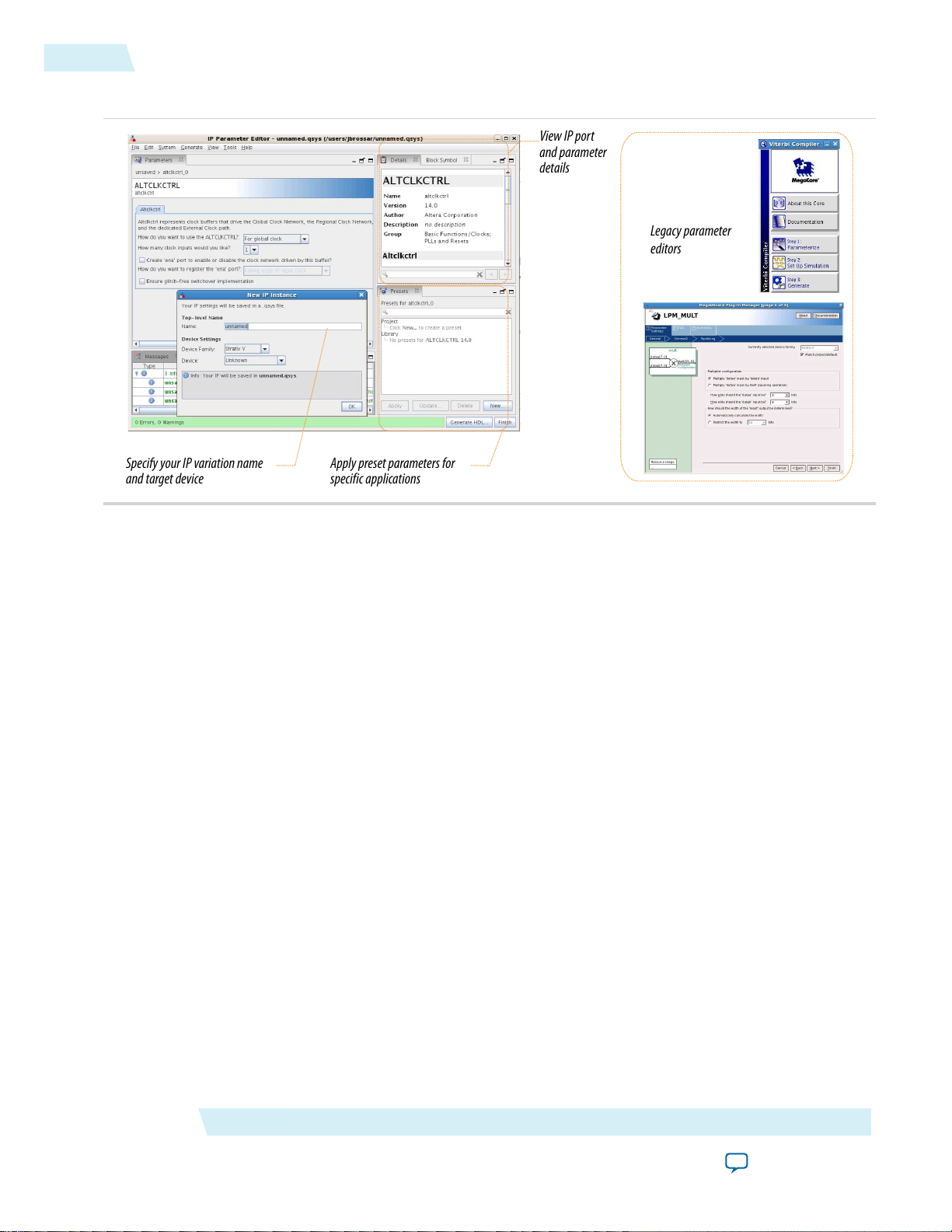

Using the Parameter Editor

The parameter editor helps you to configure IP core ports, parameters, and output file generation options.

• Use preset settings in the parameter editor (where provided) to instantly apply preset parameter values

for specific applications.

• View port and parameter descriptions, and links to documentation.

• Generate testbench systems or example designs (where provided).

Altera Unique Chip ID IP Core User Guide

Send Feedback

Altera Corporation

Page 4

View IP port

and parameter

details

Apply preset parameters for

specific applications

Specify your IP variation name

and target device

Legacy parameter

editors

4

Using the Parameter Editor

Figure 3: IP Parameter Editors

ug-altchipid

2014.09.02

Altera Corporation

Altera Unique Chip ID IP Core User Guide

Send Feedback

Page 5

Legacy parameter

editors

ug-altchipid

2014.09.02

Specifying IP Core Parameters and Options (Legacy Parameter Editors)

Specifying IP Core Parameters and Options (Legacy Parameter Editors)

The Quartus II software version 14.0 and previous uses a legacy version of the parameter editor for IP core

configuration and generation. Use the following steps to configure and generate an IP variation using a

legacy parameter editor.

5

Note:

The legacy parameter editor generates a different output file structure than the latest parameter

editor. Refer to Specifying IP Core Parameters and Options for configuration of IP cores in the Quartus

II software version 14.0a10 and later.

Figure 4: Legacy Parameter Editors

1. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize.

The parameter editor appears.

2. Specify a top-level name and output HDL file type for your IP variation. This name identifies the IP core

variation files in your project. Click OK.

3. Specify the parameters and options for your IP variation in the parameter editor. Refer to your IP core

user guide for information about specific IP core parameters.

4. Click Finish or Generate (depending on the parameter editor version). The parameter editor generates

the files for your IP variation according to your specifications. Click Exit if prompted when generation

is complete. The parameter editor adds the top-level .qip file to the current project automatically.

Note:

To manually add an IP variation generated with legacy parameter editor to a project, click Project >

Add/Remove Files in Project and add the IP variation .qip file.

Files Generated for Altera IP Cores (version 14.0 and previous)

The Quartus II software version 14.0 and previous generates the following output for your IP core.

Altera Unique Chip ID IP Core User Guide

Send Feedback

Altera Corporation

Page 6

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

<Project Directory>

<your_ip>_sim

1

<Altera IP>_instance.vo - IPFS model

2

<simulator_vendor>

<simulator setup scripts>

<your_ip>.qip - Quartus II IP integration file

<your_ip>.sip - Lists files for simulation

<your_ip>_testbench or _example - Testbench or example

1

<your_ip>.v, .sv. or .vhd - Top-level IP synthesis file

<AlteraIP_name>_instance

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist

1

<your_ip>.cmp - VHDL component declaration file

<your_ip>.bsf - Block symbol schematic file

<your_ip> - IP core synthesis files

<your_ip>.sv, .v, or .vhd - HDL synthesis files

<your_ip>.sdc - Timing constraints file

<your_ip>.ppf - XML I/O pin information file

<your_ip>.spd - Combines individual simulation scripts

1

<your_ip>_sim.f - Refers to simulation models and scripts

1

6

Upgrading IP Cores

Figure 5: IP Core Generated Files

ug-altchipid

2014.09.02

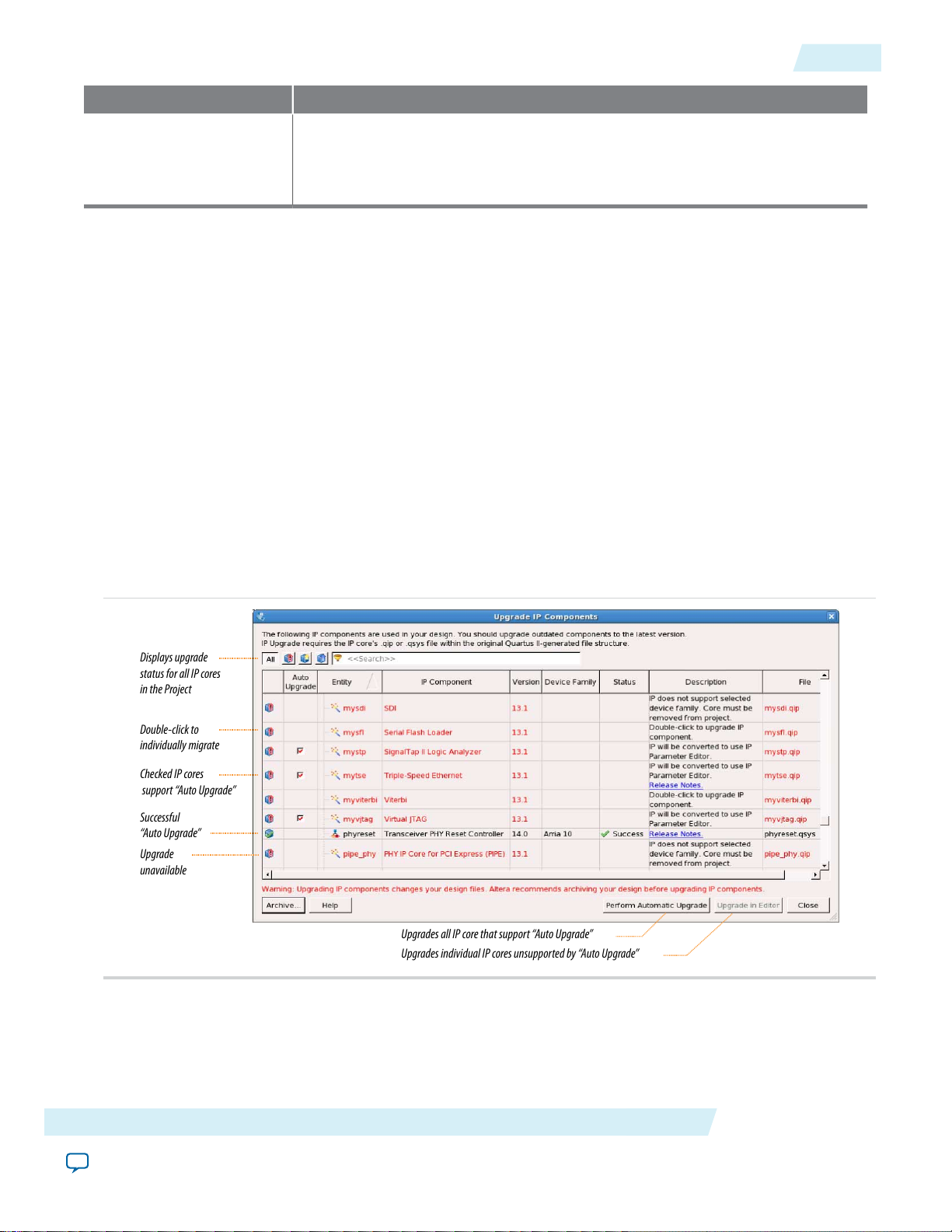

Upgrading IP Cores

IP core variants generated with a previous version of the Quartus II software may require upgrading before

use in the current version of the Quartus II software. Click Project > Upgrade IP Components to identify

and upgrade IP core variants.

The Upgrade IP Components dialog box provides instructions when IP upgrade is required, optional, or

unsupported for specific IP cores in your design. You must upgrade IP cores that require it before you can

compile the IP variation in the current version of the Quartus II software. Many Altera IP cores support

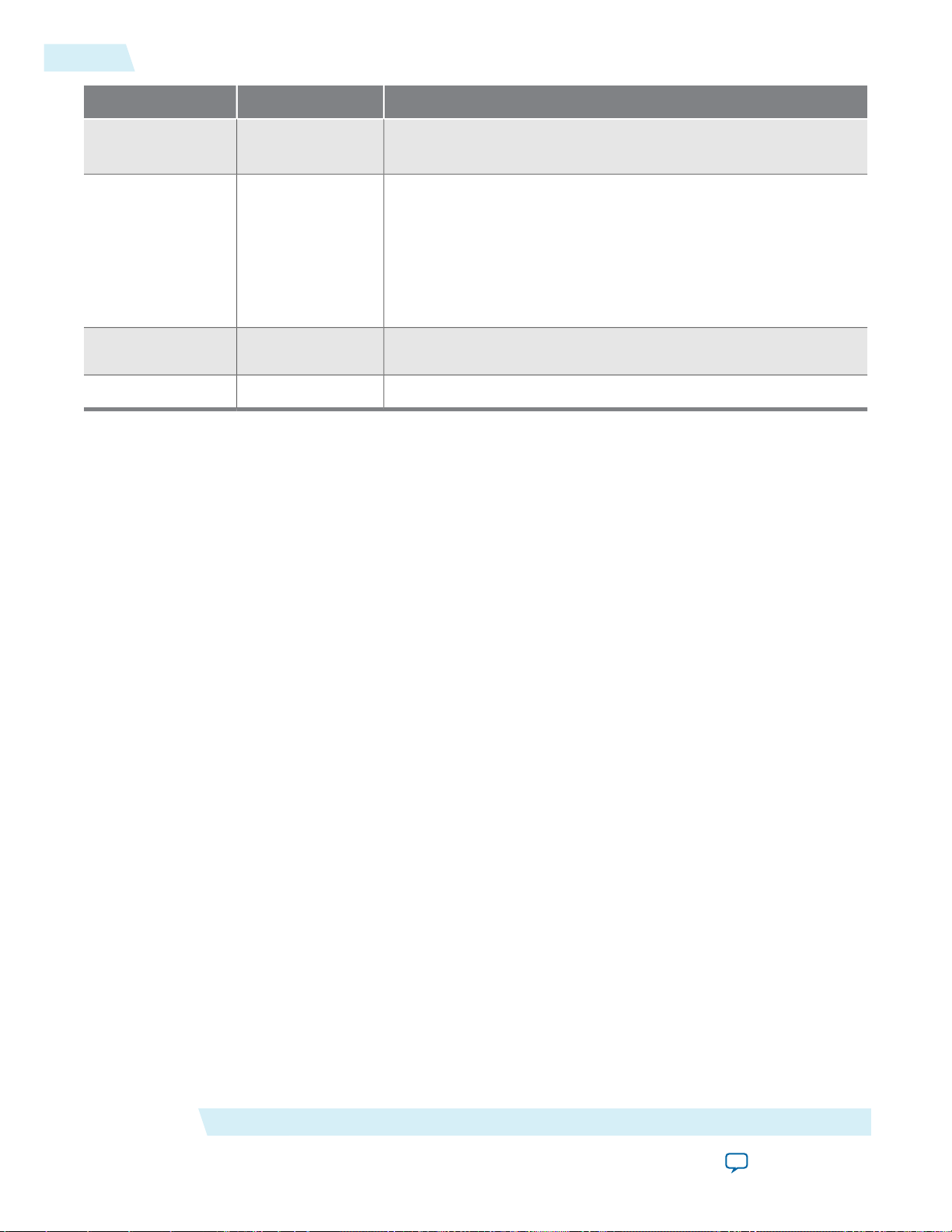

Table 1: IP Core Upgrade Status

Altera Corporation

automatic upgrade.

The upgrade process renames and preserves the existing variation file (.v, .sv, or .vhd) as <my_variant>_

BAK.v, .sv, .vhd in the project directory.

Required Upgrade IP

Components

Optional Upgrade IP

Components

Corrective ActionIP Core Status

You must upgrade the IP variation before compiling in the current version of

the Quartus II software.

Upgrade is optional for this IP variation in the current version of the Quartus II

software. You can upgrade this IP variation to take advantage of the latest

development of this IP core. Alternatively you can retain previous IP core

characteristics by declining to upgrade.

Altera Unique Chip ID IP Core User Guide

Send Feedback

Page 7

Displays upgrade

status for all IP cores

in the Project

Upgrades all IP core that support “AutoUpgrade”

Upgrades individual IP cores unsupported by “AutoUpgrade”

Checked IP cores

support “Auto Upgrade”

Successful

“Auto Upgrade”

Upgrade

unavailable

Double-click to

individually migrate

ug-altchipid

2014.09.02

Upgrading IP Cores

7

Corrective ActionIP Core Status

Upgrade Unsupported

Upgrade of the IP variation is not supported in the current version of the Quartus

II software due to IP core end of life or incompatibility with the current version

of the Quartus II software. You are prompted to replace the obsolete IP core with

a current equivalent IP core from the IP Catalog.

Before you begin

• Archive the Quartus II project containing outdated IP cores in the original version of the Quartus II

software: Click Project > Archive Project to save the project in your previous version of the Quartus II

software. This archive preserves your original design source and project files.

• Restore the archived project in the latest version of the Quartus II software: Click Project > Restore

Archived Project. Click OK if prompted to change to a supported device or overwrite the project database.

File paths in the archive must be relative to the project directory. File paths in the archive must reference

the IP variation .v or .vhd file or .qsys file (not the .qip file).

1. In the latest version of the Quartus II software, open the Quartus II project containing an outdated IP

core variation. The Upgrade IP Components dialog automatically displays the status of IP cores in your

project, along with instructions for upgrading each core. Click Project > Upgrade IP Components to

access this dialog box manually.

2. To simultaneously upgrade all IP cores that support automatic upgrade, click Perform Automatic

Upgrade. The Status and Version columns update when upgrade is complete. Example designs provided

with any Altera IP core regenerate automatically whenever you upgrade the IP core.

Figure 6: Upgrading IP Cores

Altera Unique Chip ID IP Core User Guide

Altera Corporation

Send Feedback

Page 8

8

Migrating IP Cores to a Different Device

Example 1: Upgrading IP Cores at the Command Line

You can upgrade IP cores that support auto upgrade at the command line. IP cores that do not

support automatic upgrade do not support command line upgrade.

• To upgrade a single IP core that supports auto-upgrade, type the following command:

quartus_sh –ip_upgrade –variation_files <my_ip_filepath/my_ip>.<hdl>

<qii_project>

Example:

quartus_sh -ip_upgrade -variation_files mega/pll25.v hps_testx

• To simultaneously upgrade multiple IP cores that support auto-upgrade, type the following

command:

quartus_sh –ip_upgrade –variation_files “<my_ip_filepath/my_ip1>.<hdl>;

<my_ip_filepath/my_ip2>.<hdl>” <qii_project>

Example:

quartus_sh -ip_upgrade -variation_files "mega/pll_tx2.v;mega/pll3.v" hps_testx

ug-altchipid

2014.09.02

Note:

IP cores older than Quartus II software version 12.0 do not support upgrade. Altera

verifies that the current version of the Quartus II software compiles the previous

version of each IP core. The Altera IP Release Notes reports any verification exceptions

for Altera IP cores. Altera does not verify compilation for IP cores older than the

previous two releases.

Related Information

Altera IP Release Notes

Migrating IP Cores to a Different Device

IP migration allows you to target the latest device families with IP originally generated for a different device.

Some Altera IP cores require individual migration to upgrade. The Upgrade IP Components dialog box

prompts you to double-click IP cores that require individual migration.

1. To display IP cores requiring migration, click Project > Upgrade IP Components. The Description field

prompts you to double-click IP cores that require individual migration.

2. Double-click the IP core name, and then click OK after reading the information panel.

The parameter editor appears showing the original IP core parameters.

3. For the Currently selected device family, turn off Match project/default, and then select the new target

device family.

4. Click Finish, and then click Finish again to migrate the IP variation using best-effort mapping to new

parameters and settings. Click OK if you are prompted that the IP core is unsupported for the current

device. A new parameter editor opens displaying best-effort mapped parameters.

5. Click Generate HDL, and then confirm the Synthesis and Simulation file options. Verilog is the parameter

editor default HDL for synthesis files. If your original IP core was generated for VHDL, select VHDL to

retain the original output HDL format.

Altera Corporation

Altera Unique Chip ID IP Core User Guide

Send Feedback

Page 9

ug-altchipid

2014.09.02

Simulating Altera IP Cores in other EDA Tools

9

6. To regenerate the new IP variation for the new target device, click Generate. When generation is complete,

click Close.

7. Click Finish to complete migration of the IP core. Click OK if you are prompted to overwrite IP core

files. The Device Family column displays the migrated device support. The migration process replaces

<my_ip>.qip with the <my_ip>.qsys top-level IP file in your project.

Note:

If migration does not replace <my_ip>.qip with <my_ip>.qsys, click Project > Add/Remove Files

in Project to replace the file in your project.

8. Review the latest parameters in the parameter editor or generated HDL for correctness. IP migration

may change ports, parameters, or functionality of the IP core. During migration, the IP core's HDL

generates into a library that is different from the original output location of the IP core. Update any

assignments that reference outdated locations. If your upgraded IP core is represented by a symbol in a

supporting Block Design File schematic, replace the symbol with the newly generated <my_ip>.bsf after

migration.

Note:

The migration process may change the IP variation interface, parameters, and functionality. This

may require you to change your design or to re-parameterize your variant after the Upgrade IP

Components dialog box indicates that migration is complete. The Description field identifies IP

cores that require design or parameter changes.

Related Information

Altera IP Release Notes

Simulating Altera IP Cores in other EDA Tools

The Quartus II software supports RTL and gate-level design simulation of Altera IP cores in supported EDA

simulators. Simulation involves setting up your simulator working environment, compiling simulation

model libraries, and running your simulation.

You can use the functional simulation model and the testbench or example design generated with your IP

core for simulation. The functional simulation model and testbench files are generated in a project

subdirectory. This directory may also include scripts to compile and run the testbench. For a complete list

of models or libraries required to simulate your IP core, refer to the scripts generated with the testbench.

You can use the Quartus II NativeLink feature to automatically generate simulation files and scripts.

NativeLink launches your preferred simulator from within the Quartus II software.

Altera Unique Chip ID IP Core User Guide

Send Feedback

Altera Corporation

Page 10

Post-fit timing

simulation netlist

Post-fit timing

simulation (3)

Post-fit functional

simulation netlist

Post-fit functional

simulation

Analysis & Synthesis

Fitter

(place-and-route)

TimeQuest Timing Analyzer

Device Programmer

Quartus II

Design Flow

Gate-Level Simulation

Post-synthesis

functional

simulation

Post-synthesis functional

simulation netlist

(Optional) Post-fit

timing simulation

RTL Simulation

Design Entry

(HDL, Qsys, DSP Builder)

Altera Simulation

Models

EDA

Netlist

Writer

ALTCHIP_ID

clkin

data_valid

chip_id[63..0]

reset

10

Ports

Figure 7: Simulation in Quartus II Design Flow

ug-altchipid

2014.09.02

Note:

Post-fit timing simulation is not supported for 28nm and later device archetectures. Altera IP supports

a variety of simulation models, including simulation-specific IP functional simulation models and

encrypted RTL models, and plain text RTL models. These are all cycle-accurate models. The models

support fast functional simulation of your IP core instance using industry-standard VHDL or Verilog

HDL simulators. For some cores, only the plain text RTL model is generated, and you can simulate

that model. Use the simulation models only for simulation and not for synthesis or any other purposes.

Using these models for synthesis creates a nonfunctional design.

Related Information

Simulating Altera Designs

Ports

Figure 8: ALTCHIP_ID Ports

Altera Corporation

Altera Unique Chip ID IP Core User Guide

Send Feedback

Page 11

ug-altchipid

2014.09.02

Table 2: ALTCHIP_ID Ports

Resetting the ALTCHIP_ID IP Core

DescriptionSize (in Bit)I/OPort

11

1Inputclkin

Feeds clock signal to the chip ID block. The

maximum supported frequency is 100 MHz.

When you provide a clock signal, the IP core

reads the value of the unique chip ID and

sends the value to the chip_id output port.

1Inputreset

Resets the IP core when you assert high to

the reset signal for at least one clock cycle.

The chip_id [63:0]output port holds the

value of the unique chip ID until you

reconfigure the device or reset the IP core.

1Outputdata_valid

Indicates that the unique chip ID is ready for

retrieval. If the signal is low, the IP core is in

initial state or in progress to load data from

a fuse ID. After the IP core asserts the signal,

the data is ready for retrieval at the chip_

id[63..0] output port.

64Outputchip_id

Indicates the unique chip ID according to its

respective fuse ID location. The data is only

valid after the IP core asserts the data_valid

signal.

Resetting the ALTCHIP_ID IP Core

To reset the ALTCHIP_ID IP core, you must assert high to the reset signal for at least one clock cycle. After

you deassert the reset signal, the ALTCHIP_ID IP core rereads the unique chip ID from the fuse ID block.

The ALTCHIP_ID IP core asserts the data_valid signal after completing the operation.

Document Revision History

The following table lists the revision history for this document.

Table 3: Date Version Changes

2014.09.02September, 2014

• Updated document title to reflect new name of "Altera Unique

Chip ID" IP core.

The value at power-up resets to 0.

ChangesVersionDate

Altera Unique Chip ID IP Core User Guide

Send Feedback

Altera Corporation

Page 12

12

Document Revision History

ug-altchipid

2014.09.02

ChangesVersionDate

2014.08.18August, 2014

• Updated parameterization steps for legacy parameter editor.

• Added note that this IP core does not support Arria 10 designs.

2014.06.30June, 2014

• Replaced MegaWizard Plug-In Manager information with IP

Catalog.

• Added standard information about upgrading IP cores.

• Added standard installation and licensing information.

• Removed outdated device support level information. IP core

device support is now available in IP Catalog and parameter

editor.

2013.09.20September, 2013

Updated Features to reword "Acquiring the chip ID of an FPGA

device" to "Acquiring the unique chip ID of an FPGA device"

Initial release.1.0May, 2013

Altera Corporation

Altera Unique Chip ID IP Core User Guide

Send Feedback

Loading...

Loading...