Page 1

Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

101 Innovation Drive

San Jose, CA 95134

www.altera.com

SV5V1-1.7

12.0

Page 2

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 3

Contents

Chapter Revision Dates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

Section I. Device Core

Chapter 1. Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

Logic Array Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

LAB Interconnects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

LAB Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Adaptive Logic Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–4

ALM Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–7

Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–7

Extended LUT Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–9

Arithmetic Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–10

Shared Arithmetic Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–11

ALM Interconnects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–13

Clear and Preset Logic Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–13

LAB Power Management Techniques . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–14

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–14

Chapter 2. Memory Blocks in Stratix V Devices

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Embedded Memory Block Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Parity Bit Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Byte Enable Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–4

Packed Mode Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Address Clock Enable Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–5

Mixed Width Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

Asynchronous Clear . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–7

Error Correction Code Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–8

Memory Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

Single-Port RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–10

Simple Dual-Port Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–12

True Dual-Port Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

Shift-Register Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–15

ROM Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

FIFO Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–16

Clocking Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

Independent Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

Input/Output Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

Read/Write Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–17

Single Clock Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

Design Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

Selecting Embedded Memory Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

Conflict Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–18

Read-During-Write Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–19

Same-Port Read-During-Write Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–19

Mixed-Port Read-During-Write Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–20

Power-Up Conditions and Memory Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 4

iv Contents

Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–22

Chapter 3. Variable Precision DSP Blocks in Stratix V Devices

Variable Precision DSP Block Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Operational Modes Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Variable Precision DSP Block Resource Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–4

Input Registers Bank . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Pre-Adder and Coefficient Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–7

Multipliers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Chainout Adder and Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Systolic Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–8

Output Register Bank . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Operational Mode Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

Independent Multiplier Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

9 x 9, 16 x 16, 18 x18, 27 x 27, and 36 x 18 Multipliers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–9

36-Bit Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–13

Independent Complex Multiplier Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–14

18 x 18 Complex Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–14

18 x 25 Complex Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–15

27 x 27 Complex Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–16

Multiplier Adder Sum Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–17

Sum of Square Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–20

18 x 18 Multiplication Summed with 36-Bit Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–20

Systolic FIR Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–21

Variable Precision DSP Block Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–22

Software Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–23

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–24

Chapter 4. Clock Networks and PLLs in Stratix V Devices

Clock Networks in Stratix V Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Global Clock Networks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Regional Clock Networks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

Periphery Clock Networks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3

Clock Sources Per Quadrant . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–7

Clock Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

Entire Device Clock Region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

Regional Clock Region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

Dual-Regional Clock Region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8

Clock Network Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

Dedicated Clock Input Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

Internal Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

DPA Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

HSSI Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

PLL Clock Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–9

Clock Input Pin Connections to GCLK and RCLK Networks . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–10

Clock Output Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–12

Clock Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–12

Clock Enable Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–15

Stratix V PLLs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–16

PLL Migration Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–24

Fractional PLL Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–25

Fractional PLL Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–25

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 5

Contents v

PLL External Clock I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–25

PLL Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–27

pfdena . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–27

areset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–27

locked . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–27

Clock Feedback Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–28

Source Synchronous Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–28

Source Synchronous Mode for LVDS Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–29

Direct Compensation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–30

Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–30

Zero-Delay Buffer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–31

External Feedback Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–32

Implementing Multiple PLLs in Normal Mode and Source Synchronous Mode . . . . . . . . . . . . 4–34

Clock Multiplication and Division . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–36

Programmable Duty Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–37

Clock Switchover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–37

Automatic Clock Switchover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–38

Manual Clock Switchover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–41

Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–41

PLL Reconfiguration and Dynamic Phase Shift . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–42

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–43

Section II. I/O Interfaces

Chapter 5. I/O Features in Stratix V Devices

I/O Standard Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

I/O Standards and Voltage Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–3

I/O Banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–5

Modular I/O Banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–6

I/O Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–8

3.3-V I/O Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–9

External Memory Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–9

High-Speed Differential I/O with DPA Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–9

Current Strength . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–10

Slew-Rate Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–11

I/O Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–11

Programmable IOE Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–11

Programmable Output Buffer Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–11

Open-Drain Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–12

Bus-Hold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–12

Pull-Up Resistor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–12

Pre-Emphasis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–12

Differential Output Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–13

MultiVolt I/O Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–13

OCT Support and I/O Termination Schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–14

OCT Without Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–14

R

S

OCT with Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–15

R

S

OCT with Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–17

R

T

Dynamic OCT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–17

LVDS Input R

Summary of OCT Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–19

OCT Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–20

Sharing an OCT Calibration Block on Multiple I/O Banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–20

OCT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–18

D

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 6

vi Contents

OCT Calibration Block Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–22

Power-Up Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–22

User Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–22

OCT Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–23

Serial Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–24

Example of Using Multiple OCT Calibration Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–25

Termination Schemes for I/O Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–25

Single-Ended I/O Standards Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–25

Differential I/O Standards Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–28

LVDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–30

Differential LVPECL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–31

RSDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–31

Mini-LVDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–33

LVDS Direct Loopback Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–34

Design Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–34

I/O Bank Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–34

Non-Voltage-Referenced Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–35

Voltage-Referenced Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–35

Mixing Voltage-Referenced and Non-Voltage-Referenced Standards . . . . . . . . . . . . . . . . . . . . . 5–35

Restriction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–35

V

CCPD

LVDS Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–36

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–36

Chapter 6. High-Speed Differential I/O Interfaces and DPA in Stratix V Devices

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–1

Locations of the I/O Banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

LVDS Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

LVDS SERDES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–6

Differential Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–7

Programmable Differential Output Voltage (V

Programmable V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

OD

Programmable Pre-Emphasis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–11

Differential Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–12

Differential I/O Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Receiver Hardware Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–14

DPA Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–14

Synchronizer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–15

Data Realignment Block (Bit Slip) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–15

Deserializer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–17

Receiver Datapath Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–18

Non-DPA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–18

DPA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–20

Soft-CDR Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–21

LVDS Direct Loopback Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–22

LVDS Interface with the Use External PLL Option Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–23

PLLs and Stratix V Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–27

Source-Synchronous Timing Budget . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–28

Differential Data Orientation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–28

Differential I/O Bit Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–28

Transmitter Channel-to-Channel Skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–30

Receiver Skew Margin for Non-DPA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–30

Differential Pin Placement Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–35

Guidelines for DPA-Enabled and DPA-Disabled Differential Channels . . . . . . . . . . . . . . . . . . . . . . 6–35

DPA-Enabled Channels, DPA-Disabled Channels, and Single-Ended I/Os . . . . . . . . . . . . . . . . 6–35

) and Programmable Pre-Emphasis . . . . . . . . . . . 6–9

OD

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 7

Contents vii

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–36

Chapter 7. External Memory Interfaces in Stratix V Devices

Memory Interface Pin Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–3

Using the RZQ Pins in a DQ/DQS Group for Memory Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–9

Stratix V External Memory Interface Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–9

DQS Phase-Shift Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–10

Delay-Locked Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–11

Phase Offset Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–17

PHY Clock (PHYCLK) Networks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–18

DQS Logic Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–20

DQS Delay Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–21

Update Enable Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–21

DQS Postamble Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–22

Leveling Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–23

Dynamic On-Chip Termination Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–24

I/O Element Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–25

Delay Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–27

I/O Configuration Block and DQS Configuration Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–29

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7–32

Section III. System Integration

Chapter 8. Hot Socketing and Power-On Reset in Stratix V Devices

Stratix V Hot-Socketing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–1

Stratix V Devices Can Be Driven Before Power Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–2

I/O Pins Remain Tri-Stated During Power Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–2

Insertion or Removal of a Stratix V Device from a Powered-Up System . . . . . . . . . . . . . . . . . . . . . . . 8–2

Hot-Socketing Feature Implementation in Stratix V Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–3

Power Sequencing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–4

Power-On Reset Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–5

Power-On Reset Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–7

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8–8

Chapter 9. Configuration, Design Security, and Remote System Upgrades in Stratix V Devices

Configuration Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–2

Power-On Reset Circuit and Configuration Pins Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–2

POR Delay Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–2

Power-On Reset Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–3

V

V

Configuration Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–4

Power Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–4

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–4

Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–5

Configuration Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–5

Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–5

User Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–6

Configuration Schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–7

MSEL Pin Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–7

Raw Binary File Size . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–8

Fast Passive Parallel Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–9

DCLK-to-DATA[] Ratio for FPP configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–9

Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–3

CCPGM

Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–3

CCPD

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 8

viii Contents

FPP Multi-Device Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–11

FPP Configuration Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–13

Active Serial Configuration (Serial Configuration Devices) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–17

AS Multi-Device Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–20

AS Connection Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–23

AS Configuration Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–23

Estimating the Active Serial Configuration Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–24

Programming EPCS and EPCQ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–24

Passive Serial Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–29

PS Configuration Using a MAX II Device, MAX V Device, or Microprocessor . . . . . . . . . . . . . . . . 9–29

PS Configuration Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–32

PS Configuration Using a Download Cable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–33

Multi-Device PS Configuration Using Download Cable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–35

JTAG Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–36

CONFIG_IO Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–38

Multi-Device JTAG Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–38

Device Configuration Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–40

Configuration Data Decompression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–44

Remote System Upgrades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–46

Configuration Image Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–47

Remote Update Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–48

Remote System Upgrade Using EPCQ 256 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–49

Dedicated Remote System Upgrade Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–49

Remote System Upgrade Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–51

Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–51

Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–52

Remote System Upgrade State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–53

User Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–53

Enabling the Remote System Update Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–54

ALTREMOTE_UPDATE Megafunction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–55

Design Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–55

JTAG Secure Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–57

Security Key Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–57

Security Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–58

Design Security Implementation Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–59

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9–60

Chapter 10. SEU Mitigation in Stratix V Devices

Error Detection Fundamentals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–1

Configuration Error Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–2

User Mode Error Detection and Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–2

Error Detection Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–5

Error Detection Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–6

Error Detection Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–7

Error Detection Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–8

Software Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–11

Recovering From CRC Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–11

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10–12

Chapter 11. JTAG Boundary-Scan Testing in Stratix V Devices

IEEE Std. 1149.6 Boundary-Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11–2

BST Operation Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11–3

I/O Voltage Support in a JTAG Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11–5

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 9

Contents ix

Boundary-Scan Description Language Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11–6

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11–6

Chapter 12. Power Management in Stratix V Devices

Stratix V Programmable Power Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12–2

Stratix V External Power Supply Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12–3

Temperature Sensing Diode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12–3

Internal Temperature Sensing Diode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12–4

External Temperature Sensing Diode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12–4

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12–6

Additional Information

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 10

x Contents

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 11

Chapter Revision Dates

The chapters in this document, Stratix V Device Handbook Volume 1, were revised on

the following dates. Where chapters or groups of chapters are available separately,

part numbers are listed.

Chapter 1. Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

Revised: June 2012

Part Number: SV51002-1.4

Chapter 2. Memory Blocks in Stratix V Devices

Revised: June 2012

Part Number: SV51003-1.4

Chapter 3. Variable Precision DSP Blocks in Stratix V Devices

Revised: June 2012

Part Number: SV51004-1.4

Chapter 4. Clock Networks and PLLs in Stratix V Devices

Revised: June 2012

Part Number: SV51005-1.4

Chapter 5. I/O Features in Stratix V Devices

Revised: June 2012

Part Number: SV51006-1.5

Chapter 6. High-Speed Differential I/O Interfaces and DPA in Stratix V Devices

Revised: June 2012

Part Number: SV51007-1.4

Chapter 7. External Memory Interfaces in Stratix V Devices

Revised: June 2012

Part Number: SV51008-1.4

Chapter 8. Hot Socketing and Power-On Reset in Stratix V Devices

Revised: June 2012

Part Number: SV51009-1.4

Chapter 9. Configuration, Design Security, and Remote System Upgrades in Stratix V Devices

Revised: June 2012

Part Number: SV51010-1.7

Chapter 10. SEU Mitigation in Stratix V Devices

Revised: June 2012

Part Number: SV51011-1.5

Chapter 11. JTAG Boundary-Scan Testing in Stratix V Devices

Revised: June 2012

Part Number: SV51012-1.5

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 12

xii Chapter Revision Dates

Chapter 12. Power Management in Stratix V Devices

Revised: June 2012

Part Number: SV51013-1.3

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 13

This section describes the Stratix® V device family core, which is the most

architecturally advanced, high-performance, low-power FPGA in the marketplace.

This section includes the following chapters:

■ Chapter 1, Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

■ Chapter 2, Memory Blocks in Stratix V Devices

■ Chapter 3, Variable Precision DSP Blocks in Stratix V Devices

■ Chapter 4, Clock Networks and PLLs in Stratix V Devices

Revision History

Refer to each chapter for its own specific revision history. For information on when

each chapter was updated, refer to the Chapter Revision Dates section, which appears

in the full handbook.

Section I. Device Core

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 14

I–2 Section I: Device Core

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 15

Direct link

interconnect from

adjacent block

Direct link

interconnect to

adjacent block

Row Interconnects of

Variable Speed and Length

Column Interconnects of

Variable Speed and Length

Local Interconnect is Driven

from Either Side by Columns & LABs,

and from Above by Rows

Local Interconnect

LAB

Direct link

interconnect from

adjacent block

Direct link

interconnect to

adjacent block

ALMs

MLAB

C4 C14

R24

R3/R6

June 2012

SV51002-1.4

SV51002-1.4

This chapter describes the features of the logic array blocks (LABs) in the Stratix® V

core fabric. LABs are made up of adaptive logic modules (ALMs) that you can

configure to implement logic functions, arithmetic functions, and register functions.

LABs and ALMs are the basic building blocks of the Stratix V device. ALMs provide

advanced features with efficient logic utilization and are completely

backward-compatible.

This chapter contains the following sections:

■ “Logic Array Blocks” on page 1–1

■ “Adaptive Logic Modules” on page 1–4

Logic Array Blocks

Each LAB consists of ten ALMs, various carry chains, shared arithmetic chains,

control signals, and a local interconnect. The local interconnect transfers signals

between ALMs in the same LAB. The direct link interconnect enables the LAB to drive

into the local interconnect of its left and right neighbors. The Quartus

places associated logic in the same LAB or adjacent LABs, allowing the use of local

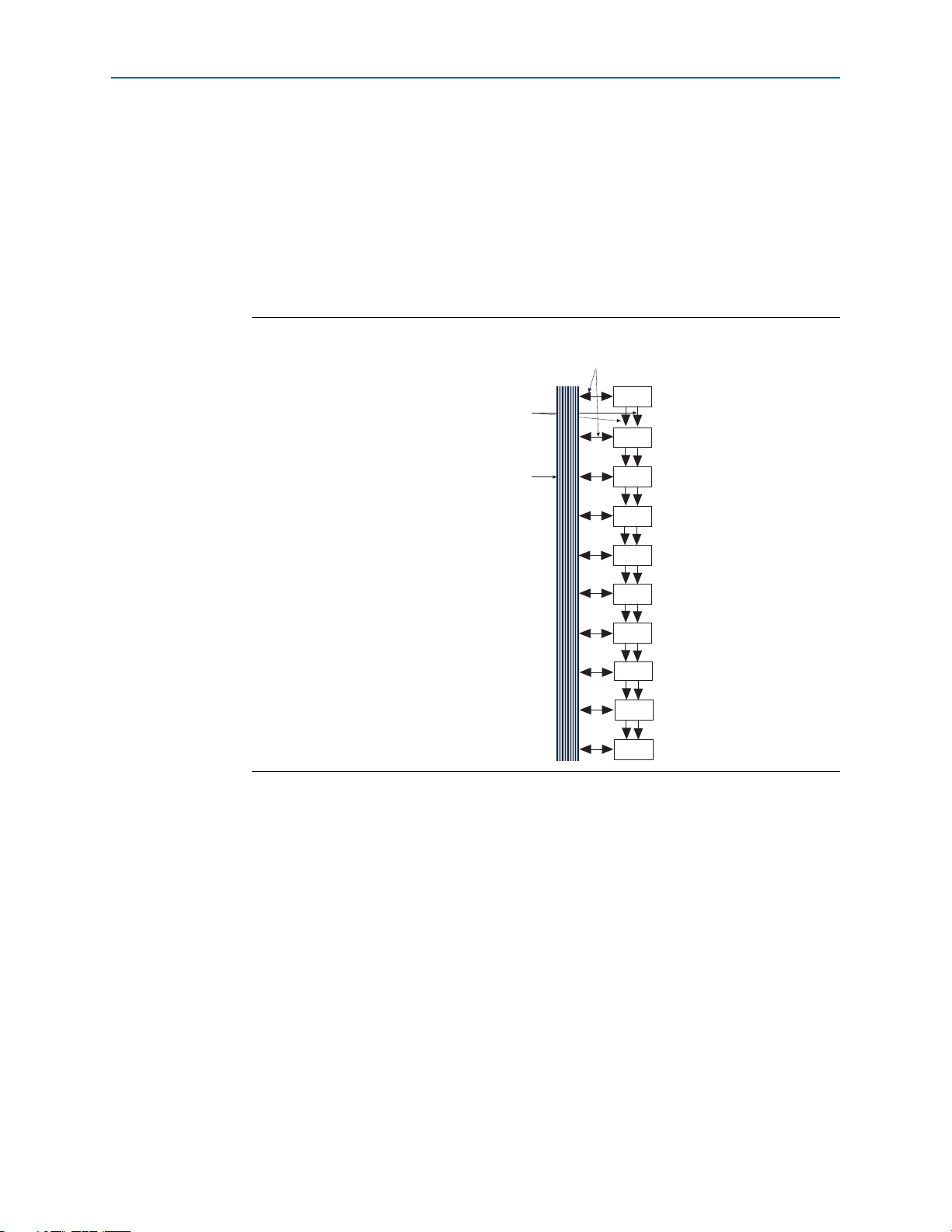

and shared arithmetic chain for performance and area efficiency. Figure 1–1 shows the

Stratix V LAB structure and the LAB interconnects.

1. Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

®

II Compiler

Figure 1–1. LAB Structure for Stratix V Devices

© 2012 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

June 2012

Feedback Subscribe

Page 16

1–2 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

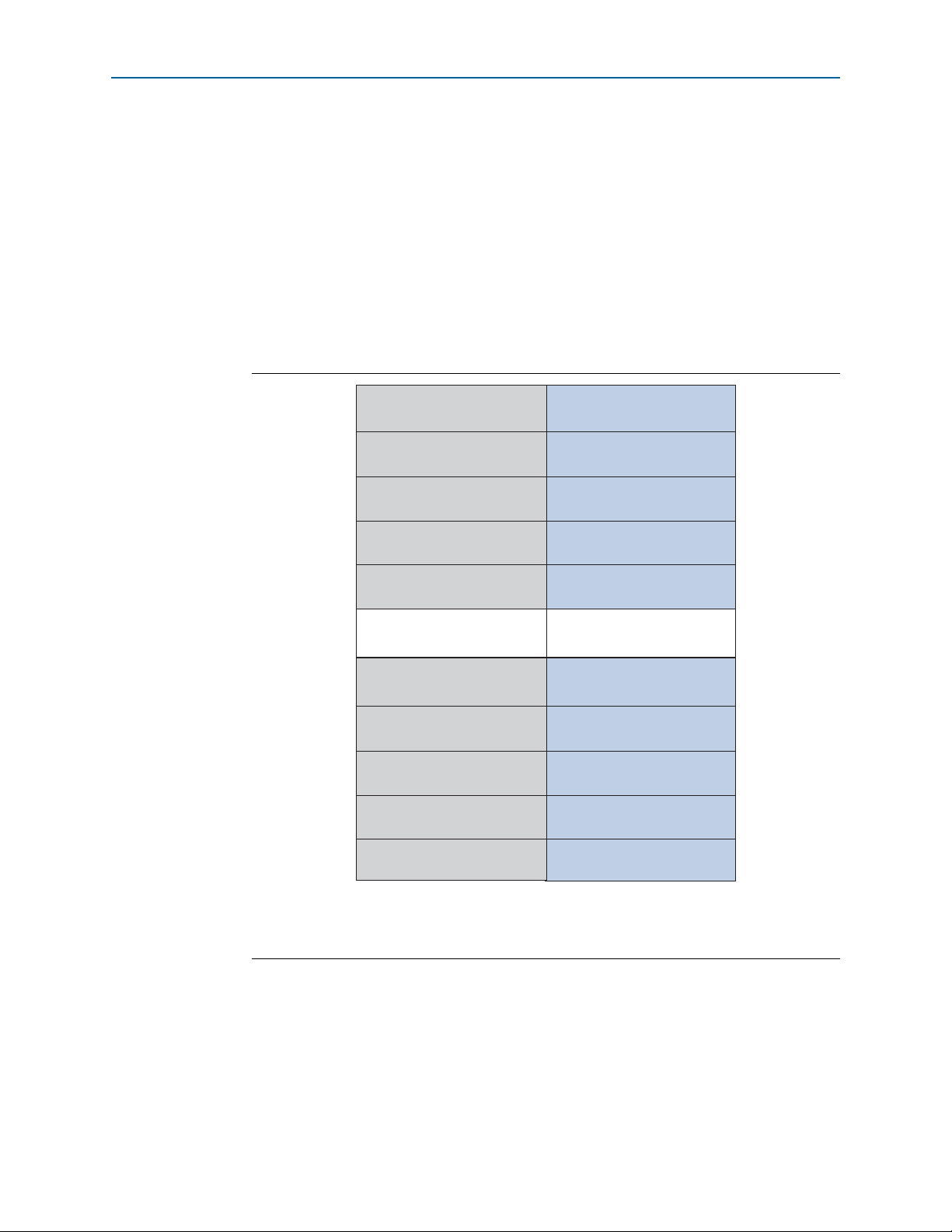

MLAB

LAB

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

LUT-based-64 x 1

Simple dual-port SRAM

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

(1)

ALM

ALM

ALM

ALM

ALM

ALM

ALM

ALM

ALM

ALM

LAB Control Block

LAB Control Block

Logic Array Blocks

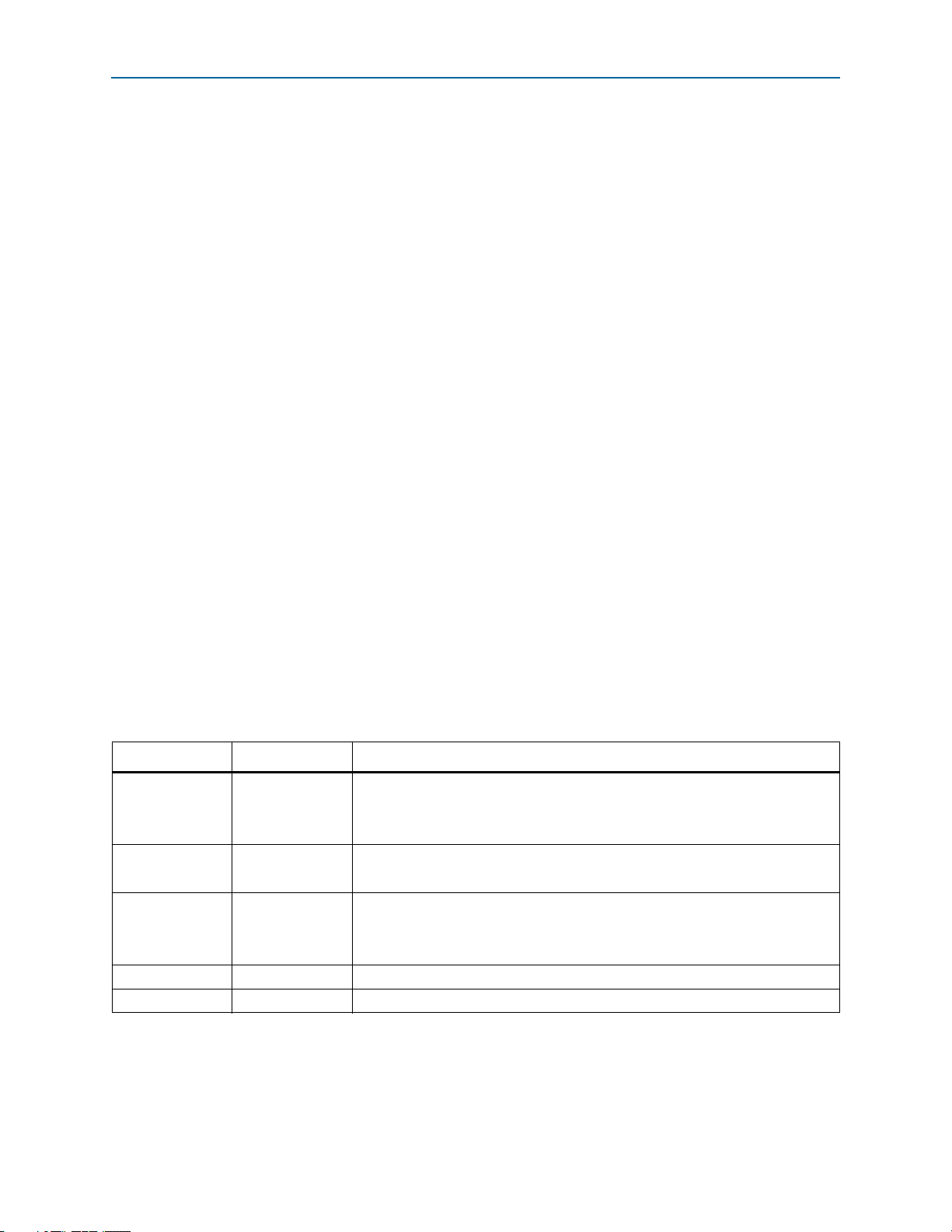

The memory LAB (MLAB) is a derivative of the Stratix V LAB. The MLAB adds

look-up table (LUT)-based SRAM capability to the LAB, as shown in Figure 1–2. The

MLAB supports a maximum of 640 bits of simple dual-port SRAM. You can configure

each ALM in an MLAB as either a 64 × 1 or a 32 × 2 block, resulting in a configuration

of either a 64 × 10 or a 32 × 20 simple dual-port SRAM block. MLAB and LAB blocks

alternate in Stratix V devices. Therefore, the maximum number of available MLABs is

half of the total number of LABs. The MLAB is a superset of the LAB and includes all

LAB features.

f For more information about MLABs, refer to the Memory Blocks in Stratix V Devices

chapter.

Figure 1–2. LAB and MLAB Structure for Stratix V Devices

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Note to Figure 1–2:

(1) You can use the MLAB ALM as a regular LAB ALM or configure it as a dual-port SRAM.

Page 17

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices 1–3

ALMs

Direct-link

interconnect

to right

Direct-link interconnect from the

right LAB, MLAB/M20K memory

block, DSP block, or IOE output

Direct-link interconnect from the

left LAB, MLAB/M20K memory

block, DSP block, or IOE output

Local

Interconnect

LAB

ALMs

Direct-link

interconnect

to left

MLAB

Logic Array Blocks

LAB Interconnects

The LAB local interconnect can drive ALMs in the same LAB. It is driven by column

and row interconnects and ALM outputs in the same LAB. Neighboring

LABs/MLABs, M20K blocks, or digital signal processing (DSP) blocks from the left or

right can also drive the LAB’s local interconnect through the direct link connection.

The direct link connection feature minimizes the use of row and column

interconnects, providing higher performance and flexibility. Each LAB can drive

30 ALMs through fast-local and direct-link interconnects.

Figure 1–3 shows the direct-link connection.

Figure 1–3. Direct-Link Connection

LAB Control Signals

Each LAB contains dedicated logic for driving control signals to its ALMs. The control

signals include three clocks, three clock enables, two asynchronous clears, one

synchronous clear, and one synchronous load, for a maximum of 10 control signals at

a time. Although you generally use synchronous load and clear signals when

implementing counters, you can also use them with other functions.

Each LAB has two unique clock sources and three clock enable signals, as shown in

Figure 1–4. The LAB control block can generate up to three clocks using two clock

sources and three clock enable signals. Each LAB’s clock and clock enable signals are

linked. For example, any ALM in a particular LAB using the

the

labclkena1

signal. If the LAB uses both the rising and falling edges of a clock, it

also uses two LAB-wide clock signals. Deasserting the clock enable signal turns off the

corresponding LAB-wide clock.

June 2012 Altera Corporation Stratix V Device Handbook

labclk1

Volume 1: Device Interfaces and Integration

signal also uses

Page 18

1–4 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

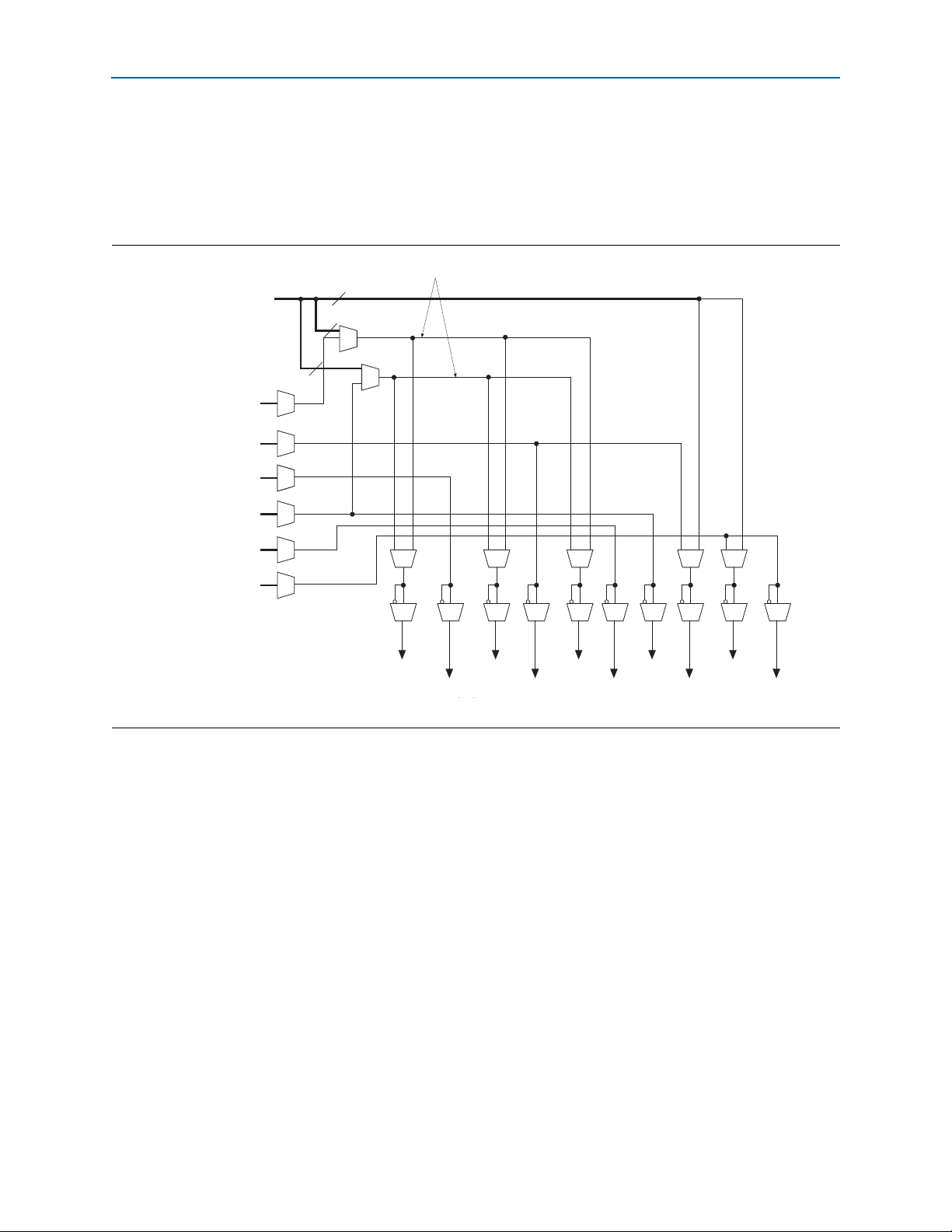

Dedicated Row LAB Clocks

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

Local Interconnect

labclk2

syncload

labclkena0

or asyncload

or labpreset

labclk0

labclk1

labclr1

labclkena1 labclkena2 labclr0 synclr

6

6

6

There are two unique

clock signals per LAB.

Adaptive Logic Modules

The LAB row clocks [5..0] and LAB local interconnects generate the LAB-wide control

signals. The MultiTrack interconnect’s inherent low skew allows clock and control

signal distribution in addition to data. The MultiTrack interconnect consists of

continuous, performance-optimized routing lines of different lengths and speeds used

for inter- and intra-design block connectivity.

Figure 1–4. LAB-Wide Control Signals

Adaptive Logic Modules

The ALM is the basic building block of logic in the Stratix V architecture. It provides

advanced features with efficient logic utilization. Each ALM contains a variety of

LUT-based resources that can be divided between two combinational adaptive LUTs

(ALUTs) and four registers. With up to eight inputs for the two combinational ALUTs,

one ALM can implement various combinations of two functions. This adaptability

allows an ALM to be completely backward-compatible with four-input LUT

architectures. One ALM can also implement any function with up to six inputs and

certain seven-input functions.

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 19

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices 1–5

datac

datad

datae1

dataf1

adder1

datae0

dataf0

dataa

datab

carry_in

carry_out

Combinational/Memory ALUT0

6-Input LUT

6-Input LUT

shared_arith_out

shared_arith_in

Combinational/Memory ALUT1

adder0

DQ

reg0

labclk

To general or

local routing

To general or

local routing

DQ

reg1

To general or

local routing

To general or

local routing

DQ

reg2

DQ

reg3

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

Adaptive Logic Modules

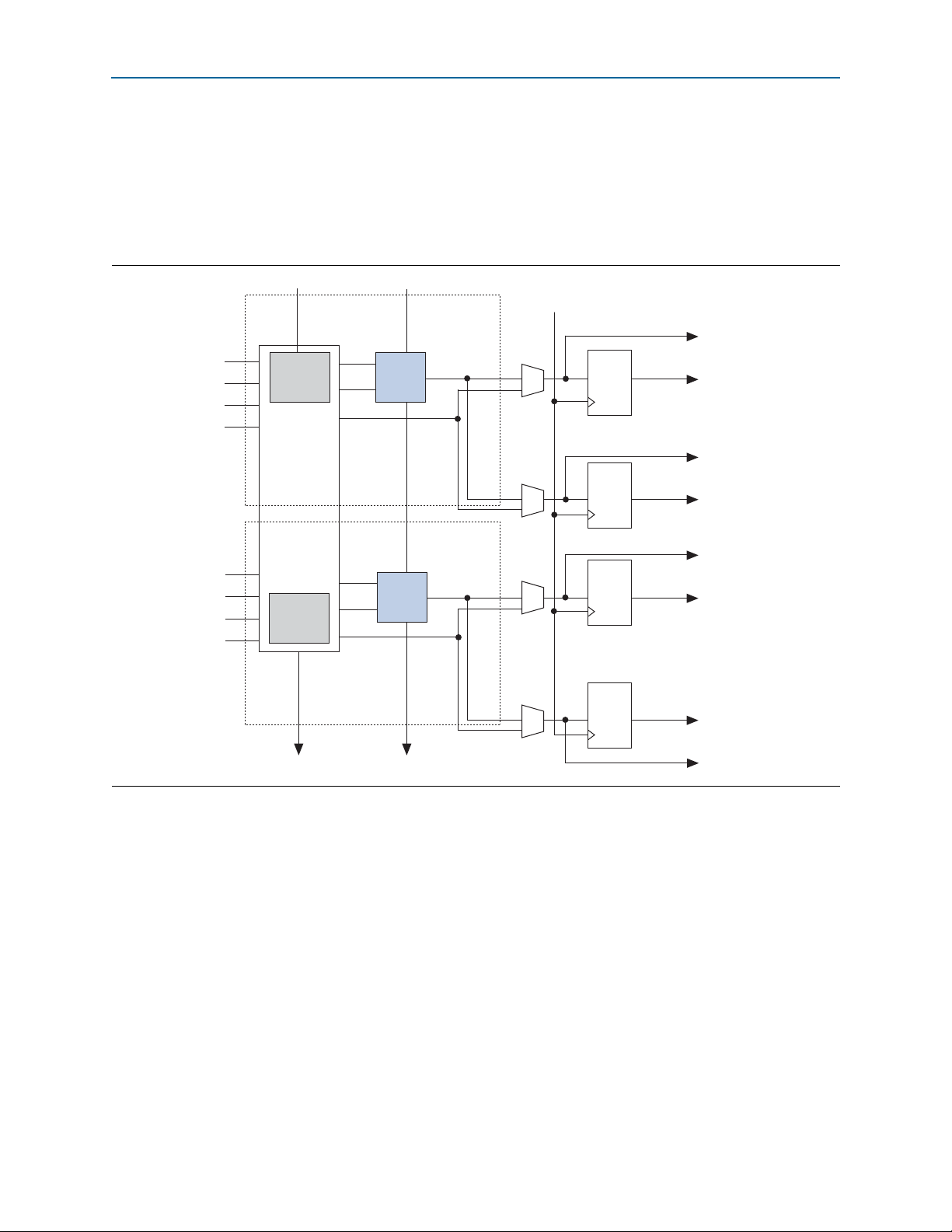

In addition to the adaptive LUT-based resources, each ALM contains four

programmable registers, two dedicated full adders, a carry chain, and a shared

arithmetic chain. Through these dedicated resources, an ALM can efficiently

implement various arithmetic functions and shift registers. Each ALM drives all types

of interconnects: local, row, column, carry chain, shared arithmetic chain, and direct

link. Figure 1–5 shows a high-level block diagram of the Stratix V ALM.

Figure 1–5. High-Level Block Diagram of the Stratix V ALM

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 20

+

carry_in

dataf0

datae0

dataa

datab

datac1

datae1

dataf1

shared_arith_out carry_out

shared_arith_in

4-INPUT

LUT

4-INPUT

LUT

3-INPUT

LUT

3-INPUT

LUT

3-INPUT

LUT

3-INPUT

LUT

+

datac0

GND

V

CC

aclr[1:0]

sclr

syncload

clk[2:0]

D

Q

CLR

D

Q

CLR

row, column

direct link routing

D

Q

CLR

row, column

direct link routing

row, column

direct link routing

row, column

direct link routing

D

Q

CLR

3

3

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

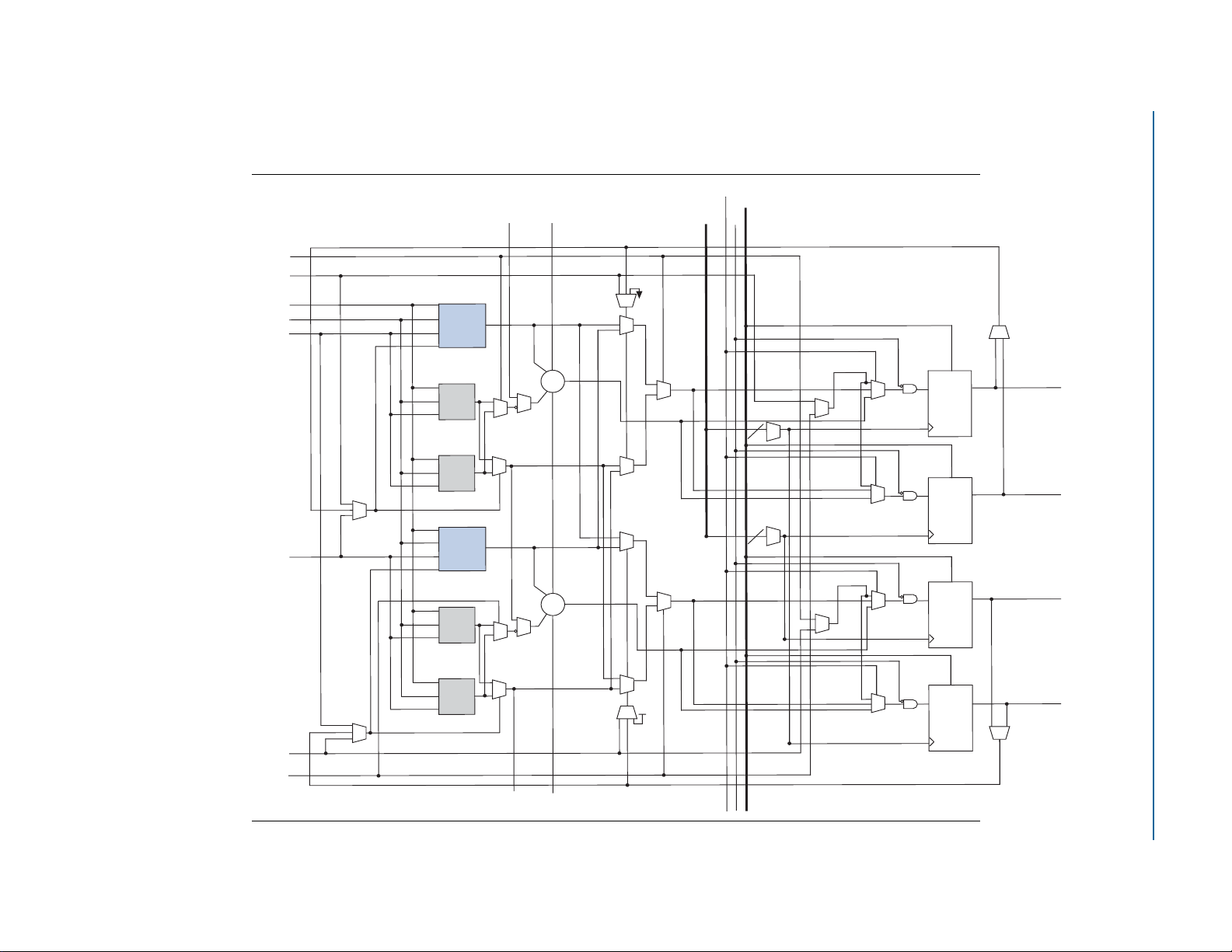

Figure 1–6 shows a detailed view of all the connections in an ALM.

Figure 1–6. ALM Connection Details for Stratix V Devices

1–6 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

Adaptive Logic Modules

Page 21

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices 1–7

Adaptive Logic Modules

One ALM contains four programmable registers. Each register has data, clock,

synchronous and asynchronous clear, and synchronous load. Global signals,

general-purpose I/O pins, or any internal logic can drive the register’s clock and

clear-control signals. Either general-purpose I/O pins or internal logic can drive the

clock enable. For combinational functions, the register is bypassed and the output of

the LUT drives directly to the outputs of an ALM.

Each ALM has two sets of outputs that drive the local, row, and column routing

resources. The LUT, adder, or register outputs can drive these output drivers (refer to

Figure 1–6). For each set of output drivers, two ALM outputs can drive column, row,

or direct-link routing connections. One of these ALM outputs can also drive local

interconnect resources. This allows the LUT or adder to drive one output while the

register drives another output.

This feature, called register packing, improves device utilization because the device

can use the register and the combinational logic for unrelated functions. Another

special packing mode allows the register output to feed back into the LUT of the same

ALM so that the register is packed with its own fan-out LUT. This provides another

mechanism for improved fitting. The ALM can also drive out registered and

unregistered versions of the LUT or adder output.

ALM Operating Modes

The Stratix V ALM operates in one of the following modes:

■ “Normal Mode” on page 1–7

■ “Extended LUT Mode” on page 1–9

■ “Arithmetic Mode” on page 1–10

■ “Shared Arithmetic Mode” on page 1–11

Each mode uses ALM resources differently. In each mode, eleven available inputs to

an ALM—the eight data inputs from the LAB local interconnect, carry-in from the

previous ALM or LAB, and the shared arithmetic chain connection from the previous

ALM or LAB—are directed to different destinations to implement the desired logic

function. LAB-wide signals provide clock, asynchronous clear, synchronous clear,

synchronous load, and clock enable control for the register. These LAB-wide signals

are available in all ALM modes.

For more information about the LAB-wide control signals, refer to “LAB Control

Signals” on page 1–3.

The Quartus II software and supported third-party synthesis tools, in conjunction

with parameterized functions such as the library of parameterized modules (LPM)

functions, automatically choose the appropriate mode for common functions such as

counters, adders, subtractors, and arithmetic functions.

Normal Mode

Normal mode is suitable for general logic applications and combinational functions.

In this mode, up to eight data inputs from the LAB local interconnect are inputs to the

combinational logic. Normal mode allows two functions to be implemented in one

Stratix V ALM, or a single function of up to six inputs. The ALM can support certain

combinations of completely independent functions and various combinations of

functions that have common inputs.

June 2012 Altera Corporation Stratix V Device Handbook

Volume 1: Device Interfaces and Integration

Page 22

1–8 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

6-Input

LUT

dataf0

datae0

dataf0

datae0

dataa

datab

dataa

datab

datab

datac

datac

dataf0

datae0

dataa

datac

6-Input

LUT

datad

datad

datae1

combout0

combout1

combout0

combout1

combout0

combout1

dataf1

datae1

dataf1

datad

datae1

dataf1

4-Input

LUT

4-Input

LUT

4-Input

LUT

6-Input

LUT

dataf0

datae0

dataa

datab

datac

datad

combout0

5-Input

LUT

5-Input

LUT

dataf0

datae0

dataa

datab

datac

datad

combout0

combout1

datae1

dataf1

5-Input

LUT

dataf0

datae0

dataa

datab

datac

datad

combout0

combout1

datae1

dataf1

5-Input

LUT

3-Input

LUT

Adaptive Logic Modules

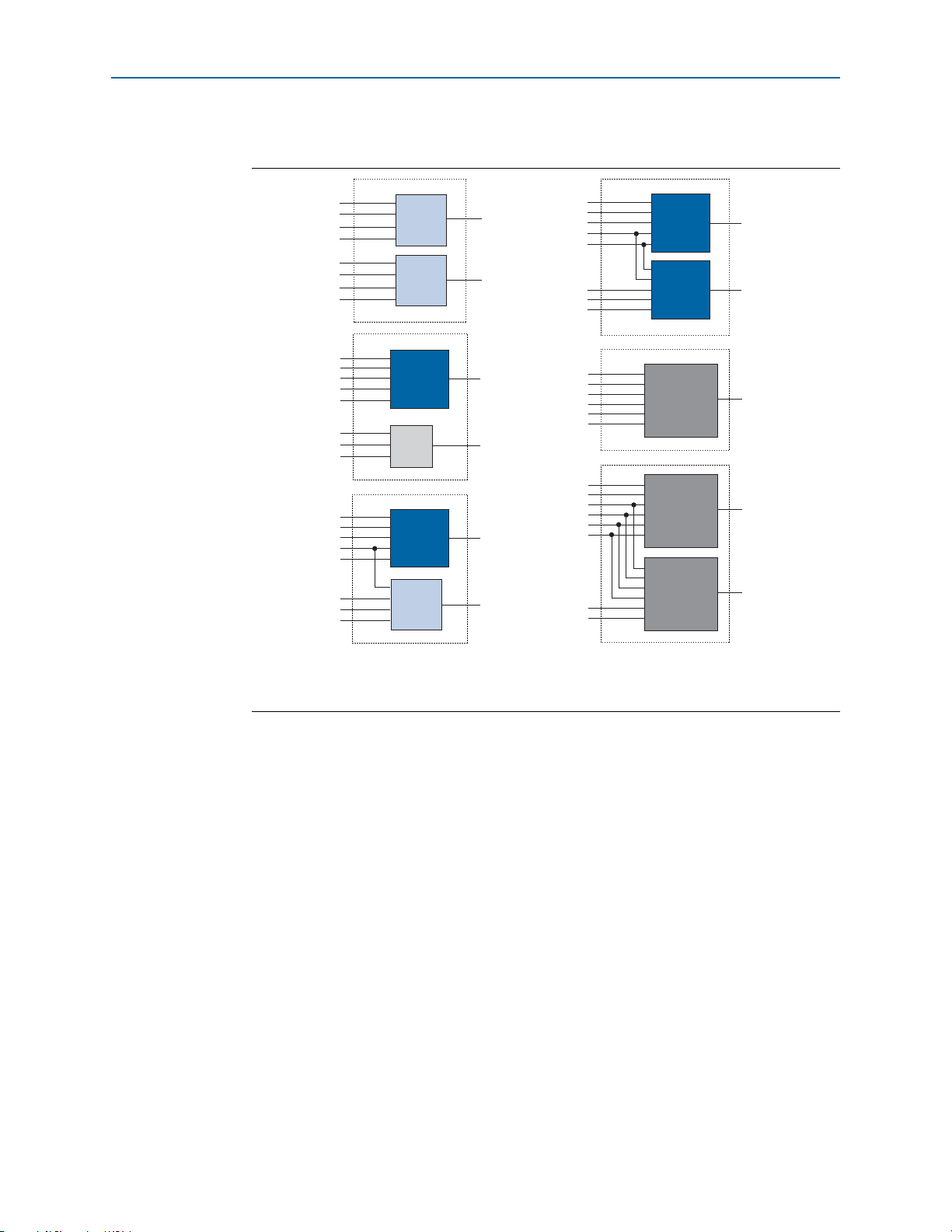

Figure 1–7 shows the supported LUT combinations in normal mode.

Figure 1–7. ALM in Normal Mode

(1)

Note to Figure 1–7:

(1) Combinations of functions with fewer inputs than those shown are also supported. For example, combinations of

functions with the following number of inputs are supported: 4 and 3, 3 and 3, 3 and 2, and 5 and 2.

Normal mode provides complete backward-compatibility with four-input LUT

architectures.

For the packing of 2 five-input functions into one ALM, the functions must have at

least two common inputs. The common inputs are

of a four-input function with a five-input function requires one common input (either

dataa

or

datab

In the case of implementing 2 six-input functions in one ALM, four inputs must be

shared and the combinational function must be the same. In a sparsely used device,

).

dataa

and

datab

. The combination

functions that could be placed in one ALM may be implemented in separate ALMs by

the Quartus II software to achieve the best possible performance. As a device begins

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

to fill up, the Quartus II software automatically uses the full potential of the Stratix V

ALM. The Quartus II Compiler automatically searches for functions using common

inputs or completely independent functions to be placed in one ALM to make efficient

use of device resources. In addition, you can manually control resource use by setting

location assignments.

Page 23

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices 1–9

6-Input

LUT

dataf0

datae0

dataa

datab

datac

datad

datae1

dataf1

DQ

DQ

To general or

local routing

To general or

local routing

To general or

local routing

reg0

reg1

These inputs are available for register packing.

(2)

labclk

datae0

combout0

5-Input

LUT

5-Input

LUT

datac

dataa

datab

datad

dataf0

datae1

dataf1

DQ

To general or

local routing

To general or

local routing

reg0

This input is available

for register packing.

(1)

Adaptive Logic Modules

You can implement any six-input function using inputs

and either

output is either driven to

register0

datae0

and

register0

and

dataf0

or

datae1

and

dataf1

register0, register0

is bypassed, or the output driven to

is bypassed, and the data drives out to the interconnect

using the top set of output drivers (refer to Figure 1–8). If you use

the output either drives to

register1

or bypasses

dataa, datab, datac, datad

. If you use

datae0

and

datae1

register1

and drives to the

dataf0

and

dataf1

,

, the

interconnect using the bottom set of output drivers. The Quartus II Compiler

automatically selects the inputs to the LUT. ALMs in normal mode support register

packing.

Figure 1–8. Input Function in Normal Mode

Notes to Figure 1–8:

(1) If you use datae1 and dataf1 as inputs to a six-input function, datae0 and dataf0 are available for register

packing.

(2) The dataf1 input is available for register packing only if the six-input function is unregistered.

(1)

,

June 2012 Altera Corporation Stratix V Device Handbook

Extended LUT Mode

Use extended LUT mode to implement a specific set of seven-input functions. The set

must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four

inputs. Figure 1–9 shows the template of supported seven-input functions using

extended LUT mode. In this mode, if the seven-input function is unregistered, the

unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 1–9 occur naturally in designs.

These functions often appear in designs as “if-else” statements in Verilog HDL or

VHDL code.

Figure 1–9. Template for Supported Seven-Input Functions in Extended LUT Mode

Note to Figure 1–9:

(1) If the seven-input function is unregistered, the unused eighth input is available for register packing. The second

register, reg1, is not available.

Volume 1: Device Interfaces and Integration

Page 24

1–10 Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices

Adaptive Logic Modules

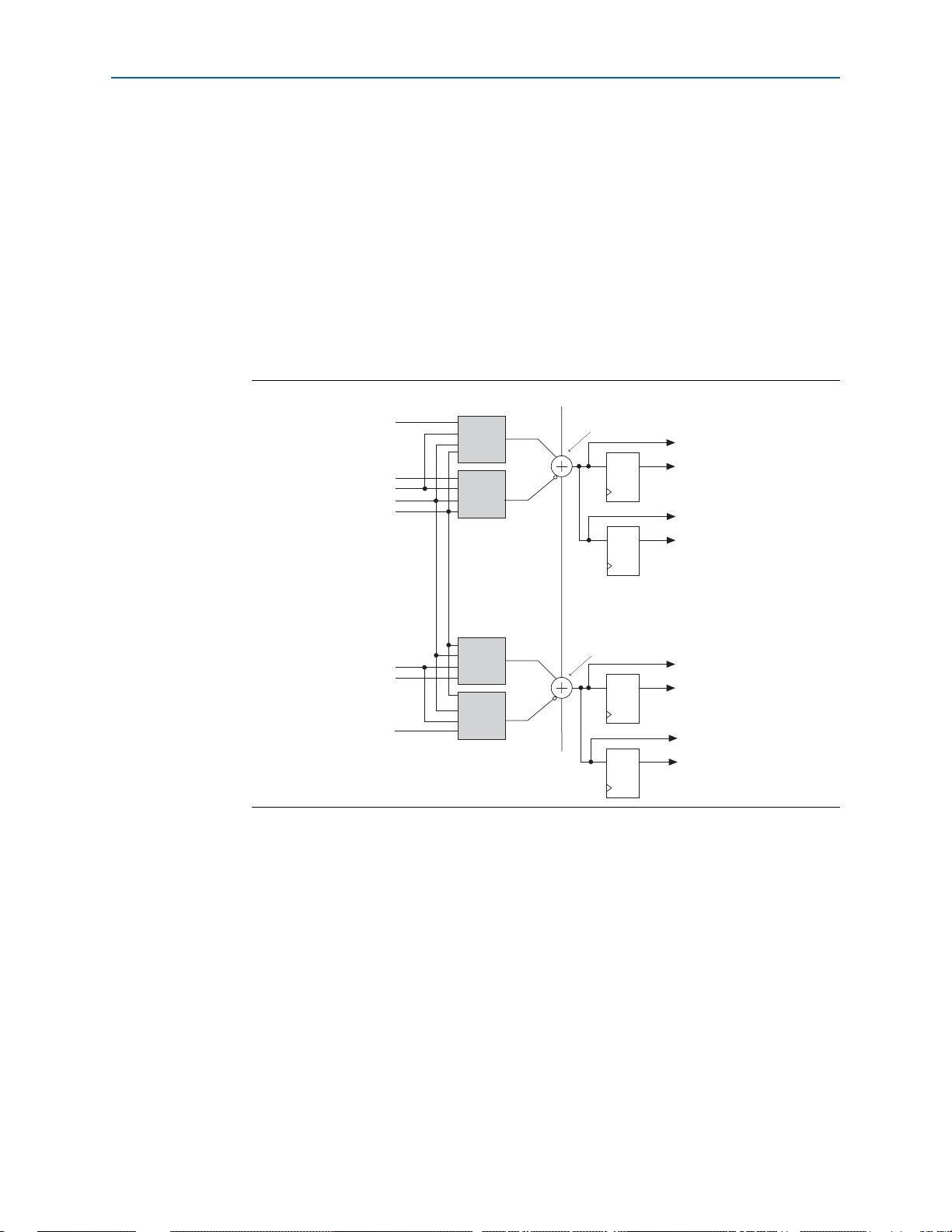

Arithmetic Mode

Arithmetic mode is ideal for implementing adders, counters, accumulators, wide

parity functions, and comparators. The ALM in arithmetic mode uses two sets of

2 four-input LUTs along with two dedicated full adders. The dedicated adders allow

the LUTs to be available to perform pre-adder logic; therefore, each adder can add the

output of 2 four-input functions.

The four LUTs share

signal feeds to

The carry-out from

adder0

adder1

dataa

and

datab

inputs. As shown in Figure 1–10, the carry-in

and the carry-out from

drives to

adder0

adder0

feeds to the carry-in of

adder1

of the next ALM in the LAB. ALMs in

arithmetic mode can drive out either registered, unregistered, or registered and

unregistered versions of the adder outputs.

Figure 1–10. ALM in Arithmetic Mode

carry_in

datae0

dataf0

datac

datab

dataa

datad

datae1

dataf1

4-Input

LUT

4-Input

LUT

4-Input

LUT

4-Input

LUT

carry_out

adder0

adder1

DQ

reg0

DQ

reg1

DQ

reg2

DQ

reg3

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

To general or

local routing

.

While operating in arithmetic mode, the ALM can support simultaneous use of the

adder’s carry output along with combinational logic outputs. In this operation, adder

output is ignored. Using the adder with combinational logic output provides resource

savings of up to 50% for functions that can use this ability.

Arithmetic mode also offers clock enable, counter enable, synchronous up/down

control, add/subtract control, synchronous clear, and synchronous load. The LAB

local interconnect data inputs generate the clock enable, counter enable, synchronous

up/down, and add/subtract control signals. These control signals are good

candidates for the inputs that are shared between the four LUTs in the ALM. The

synchronous clear and synchronous load options are LAB-wide signals that affect all

registers in the LAB. You can individually disable or enable these signals for each

register. The Quartus II software automatically places any registers that are not used

by the counter into other LABs.

Stratix V Device Handbook June 2012 Altera Corporation

Volume 1: Device Interfaces and Integration

Page 25

Chapter 1: Logic Array Blocks and Adaptive Logic Modules in Stratix V Devices 1–11

Adaptive Logic Modules

Carry Chain

The carry chain provides a fast carry function between the dedicated adders in

arithmetic or shared-arithmetic mode. The two-bit carry select feature in Stratix V

devices halves the propagation delay of carry chains within the ALM. Carry chains

can begin in either the first ALM or the fifth ALM in the LAB. The final carry-out

signal is routed to the ALM, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry-chain logic during design

processing, or you can create it manually during design entry. Parameterized

functions such as LPM functions automatically take advantage of carry chains for the

appropriate functions.

The Quartus II Compiler creates carry chains longer than 20 (10 ALMs in arithmetic or

shared arithmetic mode) by linking LABs together automatically. For enhanced

fitting, a long carry chain runs vertically, allowing fast horizontal connections to

MLAB/M20K memory and DSP blocks. A carry chain can continue as far as a full

column.

To avoid routing congestion in one small area of the device when a high fan-in

arithmetic function is implemented, the LAB can support carry chains that only use

either the top half or bottom half of the LAB before connecting to the next LAB. This

leaves the other half of the ALMs in the LAB available for implementing narrower

fan-in functions in normal mode. Carry chains that use the top five ALMs in the first

LAB carry into the top half of the ALMs in the next LAB within the column. Carry

chains that use the bottom five ALMs in the first LAB carry into the bottom half of the

ALMs in the next LAB within the column. In every alternate LAB column, the top half

can be bypassed; in the other MLAB columns, the bottom half can be bypassed.

For more information about carry-chain interconnects, refer to “ALM Interconnects”

on page 1–13.

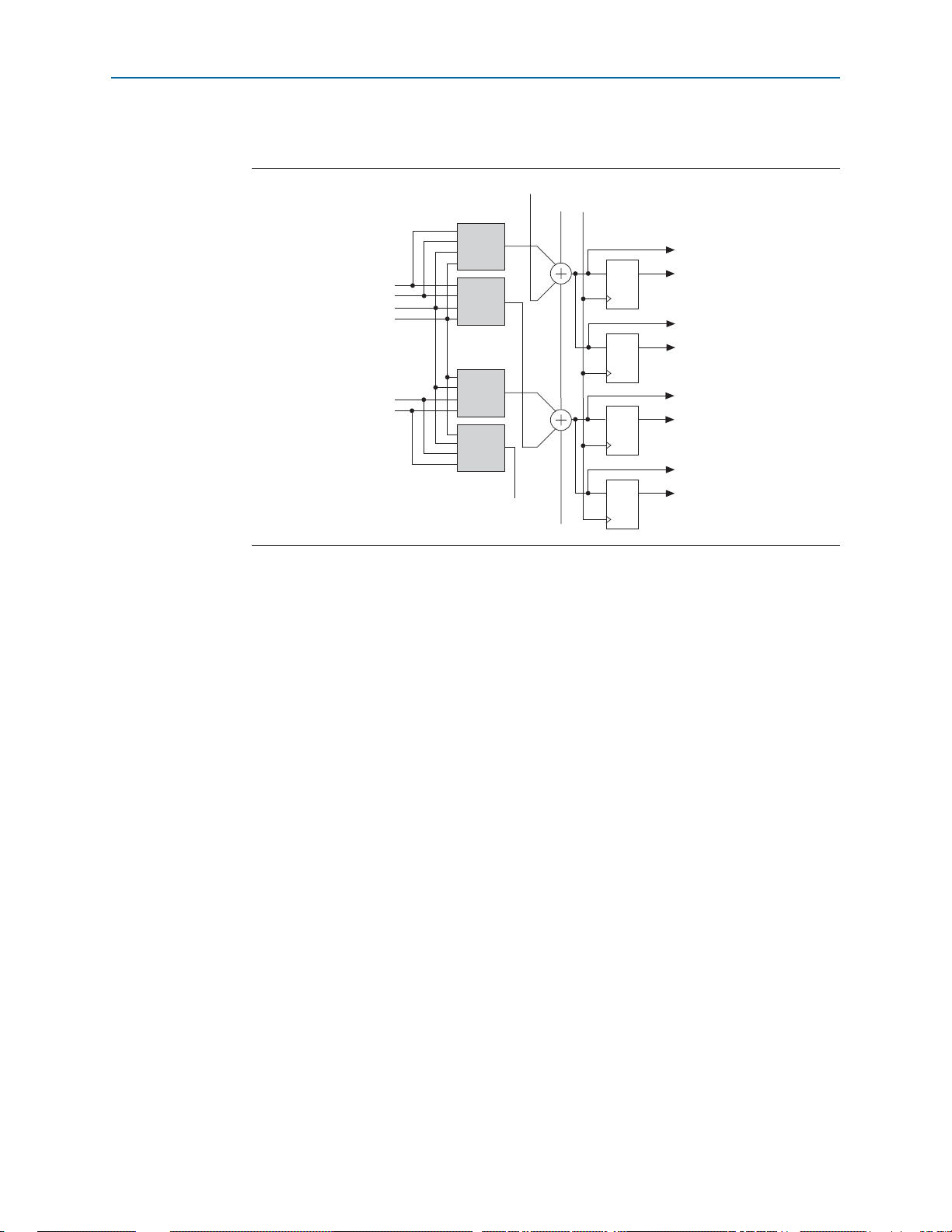

Shared Arithmetic Mode

In shared arithmetic mode, the ALM can implement a three-input add within the

ALM. In this mode, the ALM is configured with 4 four-input LUTs. Each LUT either

computes the sum of three inputs or the carry of three inputs. The output of the carry

computation is fed to the next adder (either to

the next ALM in the LAB) using a dedicated connection called the shared arithmetic

chain. This shared arithmetic chain can significantly improve the performance of an

adder tree by reducing the number of summation stages required to implement an

adder tree.

adder1

in the same ALM or to

adder0

of

June 2012 Altera Corporation Stratix V Device Handbook