Page 1

Stratix IV E FPGA Development Kit User Guide

Stratix IV E FPGA Development Kit

User Guide

101 Innovation Drive

San Jose, CA 95134

www.altera.com

UG-01067-2.1

Subscribe

Page 2

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, and specific device designations

are trademarks and/or service marks of Altera Corporation in the U.S. and other countries. All other words and logos identified as trademarks and/or service marks

are the property of Altera Corporation or their respective owners. Altera products are protected under numerous U.S. and foreign patents and pending applications,

maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard

warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of

the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to

obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 3

Contents

Chapter 1. About This Kit

Kit Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–1

Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Quartus II Subscription Edition Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Stratix IV E FPGA Development Kit Installer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–3

Chapter 2. Getting Started

Before You Begin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Inspect the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–2

Chapter 3. Software Installation

Installing the Quartus II Subscription Edition Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Licensing Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–1

Installing the Stratix IV E FPGA Development Kit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–2

Installing the USB-Blaster Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–3

Chapter 4. Development Board Setup

Setting Up the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Factory Default Switch Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–2

Chapter 5. Board Update Portal

Connecting to the Board Update Portal Web Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

Using the Board Update Portal to Update User Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–2

Chapter 6. Board Test System

Preparing the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

Running the Board Test System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–3

Using the Board Test System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–4

The Configure Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–4

The Config Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–5

Board Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–5

MAX II Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–5

JTAG Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–6

SOPC Builder Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–6

The GPIO Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–7

Character LCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–7

User DIP Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–8

User LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–8

Push Button Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–8

7-Segment Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–8

Graphics LCD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–8

Ethernet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–8

The Flash Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–9

Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–9

Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

Random Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 4

iv Contents

Increment Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

CFI Query . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

Flash Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–10

The SSRAM Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–11

Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–11

Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–12

Random Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–12

Increment Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–12

The DDR3 Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Performance Indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–13

Error Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–14

Number of Addresses to Write and Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–14

Data Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–14

Read and Write Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–14

The QDRII+ Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–15

Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–15

Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–15

Performance Indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–15

Error Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–16

Number of Addresses to Write and Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–16

Data Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–16

The RLDRAMII Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–17

Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–17

Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–17

Performance Indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–17

Error Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–18

Number of Addresses to Write and Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–18

Data Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–18

Read and Write Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–18

The HSMC Tab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–19

Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–19

Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–20

Data Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–20

Error Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–20

Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–20

Stop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–20

Performance Indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–20

The Power Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–21

General Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–22

Temperature Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–23

Power Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–23

12-V Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–23

Power Graph . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–23

Graph Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–23

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–23

Calculating Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–24

Configuring the FPGA Using the Quartus II Programmer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6–2

4

Appendix A. Programming the Flash Memory Device

CFI Flash Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 5

Contents v

Preparing Design Files for Flash Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–2

Creating Flash Files Using the Nios II EDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–2

Programming Flash Memory Using the Board Update Portal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3

Programming Flash Memory Using the Nios II EDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3

Restoring the Flash Device to the Factory Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–4

Restoring the MAX II CPLD to the Factory Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–5

Additional Information

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 6

vi Contents

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 7

1. About This Kit

The Altera® Stratix®IV E FPGA Development Kit is a complete design environment

that includes both the hardware and software you need to develop Stratix IV E FPGA

designs. The board and the one-year license for the Quartus

everything you need to begin developing custom Stratix IV E FPGA designs. The

following list describes what you can accomplish with the kit:

■ Develop and test memory subsystems consisting of DDR3, RLDRAM II, and

QDR II+ memories.

■ Build designs capable of migrating to Altera’s low-cost HardCopy

■ Take advantage of the modular and scalable design by using the high-speed

mezzanine card (HSMC) connectors to interface to over 30 different HSMCs

provided by Altera partners, supporting protocols such as Serial RapidIO

10 Gigabit Ethernet, SONET, Common Public Radio Interface (CPRI), Open Base

Station Architecture Initiative (OBSAI) and others.

■ Develop FPGAs design for cost-sensitive applications.

®

II software provide

®

IV ASICs.

®

,

Kit Features

Hardware

■ Measure the FPGA's low power consumption.

This section briefly describes the Stratix IV E FPGA Development Kit contents.

The Stratix IV E FPGA Development Kit includes the following hardware:

■ Stratix IV E FPGA development board—A development platform that allows you

to develop and prototype hardware designs running on the Stratix IV E EP4SE530

FPGA.

f For detailed information about the board components and interfaces, refer

to the Stratix IV E FPGA Development Board Reference Manual.

■ HSMC loopback board—A daughtercard that allows for loopback testing all

signals on the HSMC interface using the Board Test System.

■ HSMC debug breakout board—A daughtercard that routes 40 CMOS signals to a

0.1" header and adds 20 LEDs to the remaining 40 CMOS signals.

■ Power supply and cables—The kit includes the following items:

■ Power supply and AC adapters for North America/Japan, Europe, and the

United Kingdom

■ USB cable

■ Ethernet cable

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 8

1–2 Chapter 1: About This Kit

Kit Features

Software

The software for this kit, described in the following sections, is available on the Altera

website for immediate downloading. You can also request to have Altera mail the

software to you on DVDs.

Quartus II Subscription Edition Software

The Quartus II Subscription Edition Software is a licensed set of Altera tools with full

functionality. Your kit includes a one-year Development Kit license for the Quartus II

software (Windows platform only). This license entitles you to all the features of the

subscription edition for a period of one year.

1 After the year, your Development Kit license will no longer be valid and you will not

be permitted to use this version of the Quartus II software. To continue using the

Quartus II software, you should download the free Quartus II Web edition or

purchase a subscription to Quartus II software.

f Download the Quartus II Subscription Edition Software from the Quartus II

Subscription Edition Software page of the Altera website. Alternatively, you can

request a DVD from the Altera IP and Software DVD Request Form page of the Altera

website.

The Quartus II Subscription Edition Software includes the following items:

■ Quartus II Software—The Quartus II software, including the Qsys and SOPC

Builder system development tool, provides a comprehensive environment for

system-on-a-programmable-chip (SOPC) design. The Quartus II software

integrates into nearly any design environment and provides interfaces to

industry-standard EDA tools.

■ MegaCore

®

IP Library—A library that contains Altera IP MegaCore functions. You

can evaluate MegaCore functions by using the OpenCore Plus feature to do the

following:

■ Simulate behavior of a MegaCore function within your system.

■ Verify functionality of your design, and quickly and easily evaluate its size and

speed.

■ Generate time-limited device programming files for designs that include

MegaCore functions.

■ Program a device and verify your design in hardware.

1 The OpenCore Plus hardware evaluation feature is an evaluation tool for

prototyping only. You must purchase a license to use a MegaCore function

in production.

f For more information about OpenCore Plus, refer to AN 320: OpenCore Plus

Evaluation of Megafunctions.

■ Nios

®

II Embedded Design Suite (EDS)—A full-featured set of tools that allow you

to develop embedded software for the Nios II processor which you can include in

your Altera FPGA designs.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 9

Chapter 1: About This Kit 1–3

Kit Features

Stratix IV E FPGA Development Kit Installer

The license-free Stratix IV E FPGA Development Kit installer includes all the

documentation and design examples for the kit.

Download the Stratix IV E FPGA Development Kit installer from the Stratix IV E

FPGA Development Kit page of the Altera website. Alternatively, you can request a

Development Kit DVD from the Altera Kit Installations DVD Request Form page of

the Altera website.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 10

1–4 Chapter 1: About This Kit

Kit Features

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 11

The remaining chapters in this user guide lead you through the following Stratix IV E

FPGA development board setup steps:

■ Inspecting the contents of the kit

■ Installing the design and kit software

■ Setting up, powering up, and verifying correct operation of the FPGA

■ Configuring the Stratix IV E FPGA

■ Running the Board Test System designs

f For complete information about the FPGA development board, refer to the

Stratix IV E FPGA Development Board Reference Manual.

Before You Begin

2. Getting Started

development board

Before using the kit or installing the software, check the kit contents and inspect the

board to verify that you received all of the items listed in “Kit Features” on page 1–1.

If any of the items are missing, contact Altera before you proceed.

Inspect the Board

To inspect the board, perform the following steps:

1. Place the board on an anti-static surface and inspect it to ensure that it has not been

damaged during shipment.

c Without proper anti-static handling, you can damage the board.

2. Verify that all components are on the board and appear intact.

1 In typical applications with the Stratix IV E FPGA development board, a heat sink is

not necessary. However, under extreme conditions or for engineering sample silicon

the board might require additional cooling to stay within operating temperature

guidelines. You can perform power consumption and thermal modeling to determine

whether your application requires additional cooling. For information about

measuring board and FPGA temperature in real time, refer to “The Power Monitor”

on page 6–21.

f For more information about power consumption and thermal modeling, refer to

AN 358: Thermal Management for FPGAs.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 12

2–2 Chapter 2: Getting Started

References

References

Use the following links to check the Altera website for other related information:

■ For the latest board design files and reference designs, refer to the Stratix IV E

FPGA Development Kit page.

■ For additional daughter cards available for purchase, refer to the Development

Board Daughtercards page.

■ For the Stratix IV E device documentation, refer to the Literature: Stratix IV

Devices page.

■ To purchase devices from the eStore, refer to the Devices page.

■ For Stratix IV E OrCAD symbols, refer to the Capture CIS Symbols page.

■ For Nios II 32-bit embedded processor solutions, refer to the Embedded

Processing page.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 13

3. Software Installation

This chapter explains how to install the following software:

■ Quartus II Subscription Edition Software

■ Stratix IV E FPGA Development Kit

■ USB-Blaster™ driver

Installing the Quartus II Subscription Edition Software

The Quartus II Subscription Edition Software provides the necessary tools used for

developing hardware and software for Altera FPGAs. Included in the Quartus II

Subscription Edition Software are the Quartus II software, the Nios II EDS, and the

MegaCore IP Library. The Quartus II software (including Qsys and SOPC Builder)

and the Nios II EDS are the primary FPGA development tools used to create the

reference designs in this kit. To install the Altera development tools, perform the

following steps:

1. Run the Quartus II Subscription Edition Software installer you acquired in

“Software” on page 1–2.

2. Follow the on-screen instructions to complete the installation process.

f If you have difficulty installing the Quartus II software, refer to Altera Software

Installation and Licensing Manual.

Licensing Considerations

Purchasing this kit entitles you to a one-year Development Kit license for the

Quartus II Subscription Edition Software.

1 After the year, your Development Kit license will no longer be valid and you will not

be permitted to use this version of the Quartus II software. To continue using the

Quartus II software, you should download the free Quartus II Web edition or

purchase a subscription to Quartus II software.

Before using the Quartus II software, you must activate your license, identify specific

users and computers, and obtain and install a license file.

If you already have a licensed version of the Subscription Edition, you can use that

license file with this kit. If not, you need to obtain and install a license file. To begin,

go to the Self Service Licensing Center page of the Altera website, log into or create

your myAltera account, and take the following actions:

1. On the Activate Products page, enter the serial number provided with your

development kit in the License Activation Code box.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 14

3–2 Chapter 3: Software Installation

Installing the Stratix IV E FPGA Development Kit

1 Your serial number is printed on the development kit box below the bottom

bar code. The number is 10 or 11 alphanumeric characters and does not

contain hyphens. Figure 3–1 shows 3S150SPXXXX as an example serial

number.

Figure 3–1. Locating Your Serial Number

2. Consult the Activate Products table, to determine how to proceed.

a. If the administrator listed for your product is someone other than you, skip the

remaining steps and contact your administrator to become a licensed user.

b. If the administrator listed for your product is you, proceed to step 3.

c. If the administrator listed for your product is Stocking, activate the product,

making you the administrator, and proceed to step 3.

3. Use the Create New License page to license your product for a specific user (you)

on specific computers. The Manage Computers and Manage Users pages allow

you to add users and computers not already present in the licensing system.

1 To license the Quartus II software, you need your computer’s network

interface card (NIC) ID, a number that uniquely identifies your computer.

On the computer you use to run the Quartus II software, type

ipconfig /all

at a command prompt to determine the NIC ID. Your NIC ID

is the 12-digit hexadecimal number on the Physical Address line.

4. When licensing is complete, Altera emails a license.dat file to you. Store the file on

your computer and use the License Setup page of the Options dialog box in the

Quartus_II software to enable the software.

f For complete licensing details, refer to Altera Software Installation and Licensing Manual.

Installing the Stratix IV E FPGA Development Kit

To install the Stratix IV E FPGA Development Kit, perform the following steps:

1. Run the Stratix IV E FPGA Development Kit installer you acquired in “Software”

on page 1–2.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 15

Chapter 3: Software Installation 3–3

<install dir>

documents

board_design_files

The default Windows installation directory is C:\altera\

<version>

\.

examples

factory_recovery

demos

kits

stratixIVE_4se530_fpga

Installing the USB-Blaster Driver

2. Follow the on-screen instructions to complete the installation process. Be sure that

the installation directory you choose is in the same relative location to your

Quartus II software as the default locations.

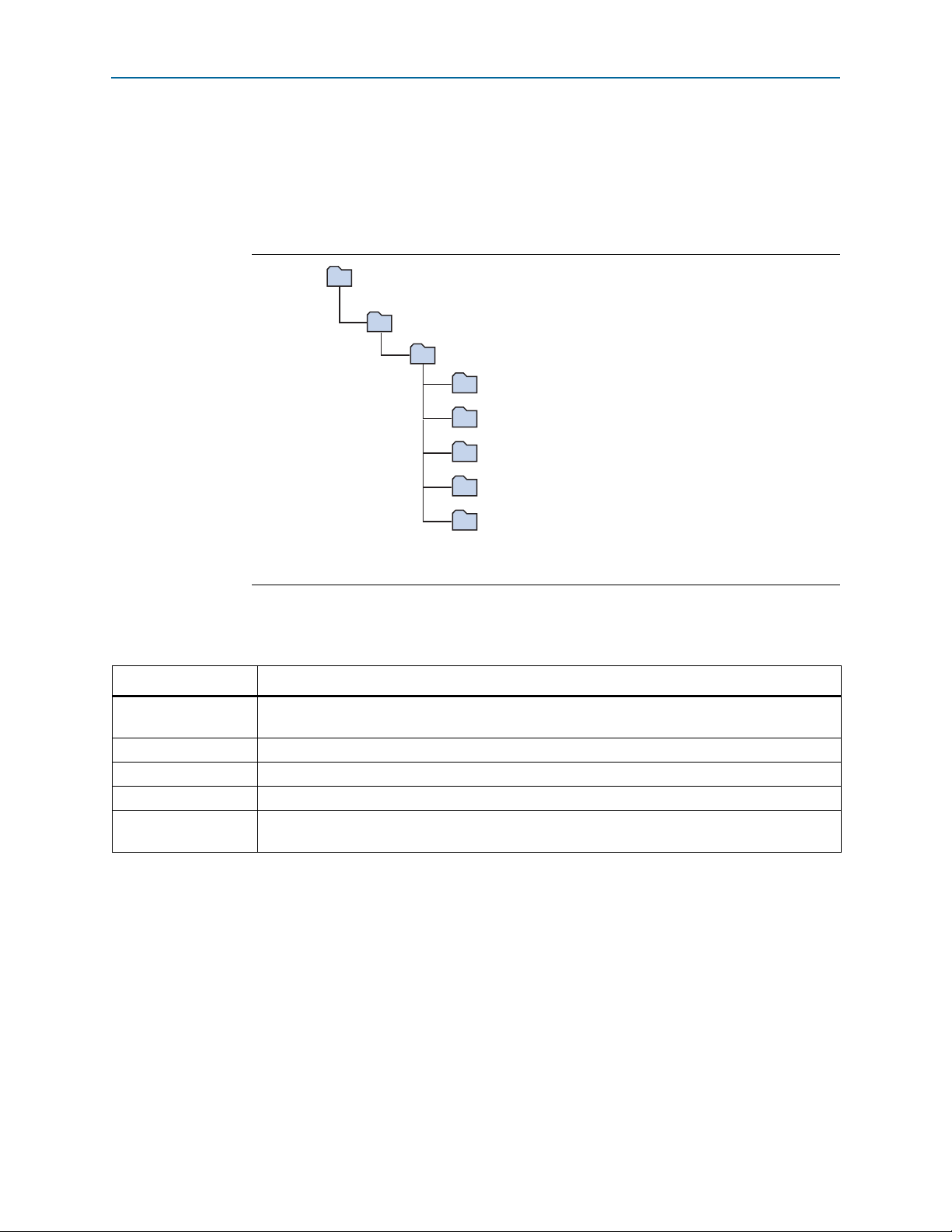

The installation program creates the Stratix IV E FPGA Development Kit directory

structure shown in Figure 3–2.

Figure 3–2. Stratix IV E FPGA Development Kit Installed Directory Structure (1)

Note to Figure 3–2:

(1) Early-release versions might have slightly different directory names.

Tab le 3– 1 lists the file directory names and a description of their contents.

Table 3–1. Installed Directory Contents

Directory Name Description of Contents

board_design_files

demos Contains demonstration applications, if present; not all kits include demos.

documents Contains the kit documentation.

examples Contains the sample design files for the Stratix IV E FPGA Development Kit.

factory_recovery

Contains schematic, layout, assembly, and bill of material board design files. Use these files as a

starting point for a new prototype board design.

Contains the original data programmed onto the board before shipment. Use this data to restore

the board with its original factory contents.

Installing the USB-Blaster Driver

The Stratix IV E FPGA development board includes integrated USB-Blaster circuitry

for FPGA programming. However, for the host computer and board to communicate,

you must install the USB-Blaster driver on the host computer.

f Installation instructions for the USB-Blaster driver for your operating system are

available on the Altera website. On the Altera Programming Cable Driver Information

page of the Altera website, locate the table entry for your configuration and click the

link to access the instructions.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 16

3–4 Chapter 3: Software Installation

Installing the USB-Blaster Driver

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 17

The instructions in this chapter explain how to set up the Stratix IV E FPGA

development board.

Setting Up the Board

To prepare and apply power to the board, perform the following steps:

1. The Stratix IV E FPGA development board ships with its board switches

preconfigured to support the design examples in the kit. If you suspect your board

might not be currently configured with the default settings, follow the instructions

in “Factory Default Switch Settings” on page 4–2 to return the board to its factory

settings before proceeding.

2. The FPGA development board ships with design examples stored in the flash

memory device. Verify the PGM CONFIG SELECT rotary switch (SW5) is set to the

0 position to load the design stored in the factory portion of flash memory.

Figure 4–1 shows the switch location on the Stratix IV E FPGA development

board.

4. Development Board Setup

3. Connect the DC adapter (+16 V, 3.75 A) to the DC power jack (J22) on the FPGA

board and plug the cord into a power outlet.

c Use only the supplied power supply. Power regulation circuitry on the

board can be damaged by power supplies with greater voltage.

4. Set the POWER switch (SW3) to the on position. When power is supplied to the

board, a blue LED (D21) illuminates indicating that the board has power.

The MAX II device on the board contains (among other things) a parallel flash loader

(PFL) megafunction. When the board powers up, the PFL reads a design from flash

memory and configures the FPGA. The PGM CONFIG SELECT rotary switch (SW5)

controls which design to load. When the switch is in the 0 position, the PFL loads the

design from the factory portion of flash memory. When the switch is in the 1 position,

the PFL loads the design from the user hardware portion of flash memory.

1 The kit includes a MAX II design which contains the MAX II PFL megafunction. The

design resides in the <install dir>\kits\stratixIVE_4se530_fpga\examples\max2

directory.

When configuration is complete, the CONF DONE LED (D22) illuminates, signaling

that the Stratix IV E device configured successfully.

f For more information about the PFL megafunction, refer to Parallel Flash Loader

Megafunction User Guide.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 18

4–2 Chapter 4: Development Board Setup

12345678

ON

4321

12345678

0

123

QDRII_DRIVE

60

50

MIN

J7

VCC_VCCL_SEL

J21

USB

J4

Clock

Enable

SW1

MSEL0

J2

MAXII_JTAG_EN

J10

SHUNT = 1.8V_QDR

J11

FAN

J12

HSMB JTAG EN

J5

HSMA_JTAG_EN

J15

SHUNT = 1.8V_RLD

J18

SW5

SW2

MAX II DIPSWITCH

Rotary

Switch

OPEN

OPEN

SW4

Board Settings

PGM CONFIG SELECT

Factory Default Switch Settings

Factory Default Switch Settings

This section shows the factory switch settings for the Stratix IV E FPGA development

board. Figure 4–1 shows the switch locations and the default position of each switch

on the top side of the board.

Figure 4–1. Switch Locations and Default Settings on the Board Top

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 19

Chapter 4: Development Board Setup 4–3

RLD_ZQ_IMPED

60

50

MAX

J28

DDR3_TEST_HDR

J29

Factory Default Switch Settings

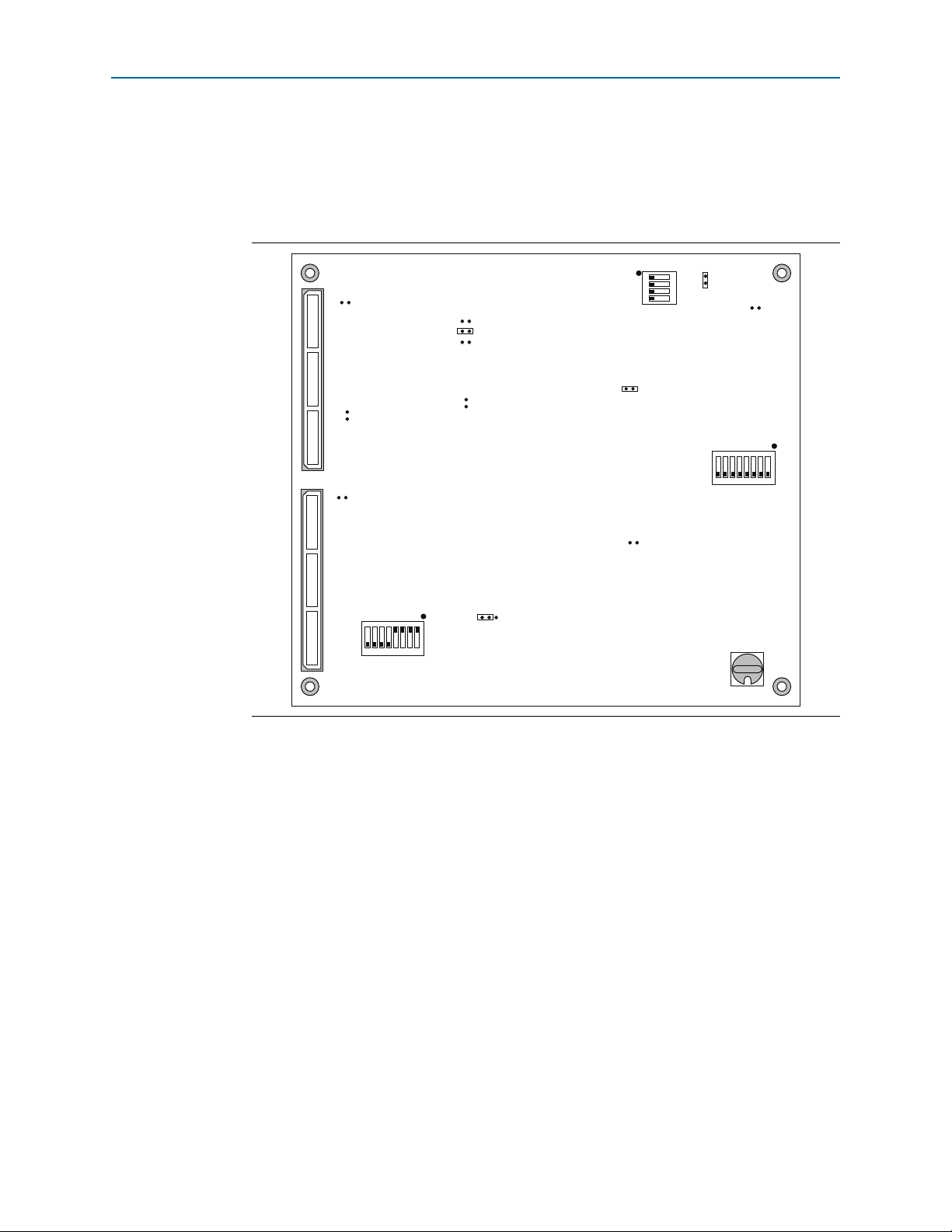

Figure 4–2 shows the switch locations and the default position of each switch on the

bottom side of the board.

Figure 4–2. Switch Locations and Default Settings on the Board Bottom

To restore the switches to their factory default settings, perform the following steps:

1. Set the PGM CONFIG SELECT rotary switch (SW5) to the 0 position, as shown in

Figure 4–1.

2. Set DIP switch bank (SW1) to match Ta bl e 4– 1 and Figure 4–1.

Table 4–1. SW1 Dip Switch Settings (Part 1 of 2)

Switch

Board

Label

Switch 1 has the following options:

1 CLK50_EN

2 CLK66_EN

■ When on, the 50 MHz clock is disabled.

■ When off, the 50 MHz clock is enabled.

Switch 2 has the following options:

■ When on, the 66 MHz clock is disabled.

■ When off, the 66 MHz clock is enabled.

Function

Default

Position

Off

Off

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 20

4–4 Chapter 4: Development Board Setup

Factory Default Switch Settings

Table 4–1. SW1 Dip Switch Settings (Part 2 of 2)

Switch

Board

Label

Switch 3 has the following options:

3 CLK100_EN

■ When on, the 100 MHz clock is disabled.

■ When off, the 100 MHz clock is enabled.

Switch 4 has the following options:

4 CLK125_EN

■ When on, the 125 MHz clock is disabled.

■ When off, the 125 MHz clock is enabled.

3. Set DIP switch bank (SW2) to match Ta bl e 4– 2 and Figure 4–1.

Table 4–2. SW2 Dip Switch Settings

Switch

Board

Label

Switch 1 is a MAX II user-defined switch and has the following options:

1DIP0

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 2 is a MAX II user-defined switch and has the following options:

2DIP1

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 3 is a MAX II user-defined switch and has the following options:

3DIP2

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 4 is a MAX II user-defined switch and has the following options:

4DIP3

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 5 is a MAX II user-defined switch and has the following options:

5DIP4

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 6 is a MAX II user-defined switch and has the following options:

6DIP5

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 7 is a MAX II user-defined switch and has the following options:

7DIP6

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 8 has the following options:

8 CLK66_SEL

■ When closed, the 66 MHz clock is selected.

■ When open, the SMA input clock is selected.

Function

Function

Default

Position

Off

Off

Default

Position

Closed

Closed

Closed

Closed

Closed

Closed

Closed

Closed

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 21

Chapter 4: Development Board Setup 4–5

Factory Default Switch Settings

4. Set DIP switch bank (SW4) to match Ta bl e 4– 3 and Figure 4–1.

Table 4–3. SW4 Dip Switch Settings

Switch

Board

Label

1 USER_DIPSW0

2 USER_DIPSW1

3 USER_DIPSW2

4 USER_DIPSW3

5 USER_DIPSW4

6 USER_DIPSW5

7 USER_DIPSW6

8 USER_DIPSW7

Function

Switch 1 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 2 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 3 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 4 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 5 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 6 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 7 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Switch 8 is a user-defined switch and has the following options:

■ When closed, a logic 0 is selected.

■ When open, a logic 1 is selected.

Default

Position

Open

Open

Open

Open

Closed

Closed

Closed

Closed

5. Set the board jumpers to match Ta bl e 4 –4 , Figure 4–1, and Figure 4–2.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 22

4–6 Chapter 4: Development Board Setup

Factory Default Switch Settings

c Installing shunts in certain configurations might cause damage to devices

on your board. Pay specific attention to the Function column details.

Table 4–4. Jumper Settings (Part 1 of 2)

Board

Reference

Board

Label

J2 MSEL0

J4 USB DISABLE

J5 HSMB_JTAG_EN

J7 QDRII DRIVE

J10 MAXII_JTAG_EN

J11 SHUNT=1.8V QDR

J15 HSMA_JTAG_EN

J18 SHUNT=1.8V RLD

Function

This jumper has the following options:

■ Installing the shunt sets MSEL0 to logic 0.

■ Removing the shunt sets MSEL0 to logic 1.

This jumper has the following options:

■ Installing the shunt disables the onboard USB-Blaster.

■ Removing the shunt enables the onboard USB-Blaster.

This jumper has the following options:

■ Installing the shunt includes HSMC port B in the JTAG chain.

■ Removing the shunt removes HSMC port B from the JTAG chain.

This jumper has the following options:

■ Installing the shunt on pins 1 and 2 sets the QDR II output

impedance to the minimum value possible.

■ Installing the shunt on pins 3 and 4 sets the QDR II output

impedance to 50 Ω.

■ Installing the shunt on pins 5 and 6 sets the QDR II output

impedance to 60 Ω.

Always keep one and only one shunt installed. Other configurations

might cause damage to the device.

This jumper has the following options:

■ Installing the shunt includes the MAX II EMP2210 device in the

JTAG chain.

■ Removing the shunt removes the MAX II device from the JTAG

chain.

This jumper has the following options:

■ Installing the shunt sets QDR II VDDQ to 1.8 V.

■ Removing the shunt sets QDR II VDDQ to 1.5 V.

This jumper has the following options:

■ Installing the shunt includes HSMC port A in the JTAG chain.

■ Removing the shunt removes HSMC port A from the JTAG chain.

This jumper has the following options:

■ Installing the shunt sets RLDRAM II VDDQ to 1.8 V.

■ Removing the shunt sets RLDRAM II VDDQ to 1.5 V.

Default

Shunt Position

Installed

Not installed

Not installed

Installed on

pins 3 and 4

Installed

Not installed

Not installed

Not installed

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 23

Chapter 4: Development Board Setup 4–7

Factory Default Switch Settings

Table 4–4. Jumper Settings (Part 2 of 2)

Board

Reference

Board

Label

J21 VCC_VCCL_SEL

J28 RLD_ZQ_IMPED

f For more information about the FPGA board settings, refer to the Stratix IV E FPGA

Development Board Reference Manual.

Function

This jumper has the following options:

■ Installing the shunt on pins 1 and 2 sets VCC and VCCL to 0.9 V.

■ Installing the shunt on pins 2 and 3 sets VCC and VCCL to 1.1 V.

■ Removing the shunt sets VCC and VCCL to 0.6 V.

Always keep a shunt installed on pins 1 and 2 only. The current version

of the Stratix IV E device requires 0.9 V.

To use the RLDRAM II impedance drive jumpers, set the mode

register. When the mode register is not set, the RLDRAM II output

impedance is 50 Ω. The RLDRAM II impedance drive jumpers have the

following options:

■ Installing the shunt on pins 1 and 2 sets the RLDRAM II output

impedance to the maximum value possible.

■ Installing the shunt on pins 3 and 4 sets the RLDRAM II output

impedance to 50 Ω.

■ Installing the shunt on pins 5 and 6 sets the RLDRAM II output

impedance to 60 Ω.

Installing more than one shunt might cause damage to the device.

Default

Shunt Position

Installed on

pins 1 and 2

Not installed

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 24

4–8 Chapter 4: Development Board Setup

Factory Default Switch Settings

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 25

5. Board Update Portal

The Stratix IV E FPGA Development Kit ships with the Board Update Portal design

example stored in the factory portion of the flash memory on the board. The design

consists of a Nios II embedded processor, an Ethernet MAC, and an HTML web

server.

When you power up the board with the PGM CONFIG SELECT rotary switch (SW5)

in the 0 position, the Stratix IV E FPGA configures with the Board Update Portal

design example. The design can obtain an IP address from any DHCP server and

serve a web page from the flash on your board to any host computer on the same

network. The web page allows you to upload new FPGA designs to the user hardware

portion of flash memory, and provides links to useful information on the Altera

website, including kit-specific links and design resources.

1 After successfully updating the user hardware flash memory, you can load the user

design from flash memory into the FPGA. To do so, set the PGM CONFIG SELECT

rotary switch (SW5) to the 1 position and power cycle the board.

The source code for the Board Update Portal design resides in the <install

dir>\kits\stratixIVE_4se530_fpga\examples directory. If the Board Update Portal is

corrupted or deleted from the flash memory, refer to “Restoring the Flash Device to

the Factory Settings” on page A–4 to restore the board with its original factory

contents.

Connecting to the Board Update Portal Web Page

This section provides instructions to connect to the Board Update Portal web page.

1 Before you proceed, ensure that you have the following:

■ A PC with a connection to a working Ethernet port on a DHCP enabled network.

■ A separate working Ethernet port connected to the same network for the board.

■ The Ethernet and power cables that are included in the kit.

To connect to the Board Update Portal web page, perform the following steps:

1. With the board powered down, set the PGM CONFIG SELECT rotary switch

(SW5) to the 0 position.

2. Attach the Ethernet cable from the board to your LAN.

3. Power up the board. The board connects to the LAN’s gateway router, and obtains

an IP address. The LCD on the board displays the IP address.

4. Launch a web browser on a PC that is connected to the same network, and enter

the IP address from the LCD into the browser address bar. The Board Update

Portal web page appears in the browser.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 26

5–2 Chapter 5: Board Update Portal

1 You can click Stratix IV E FPGA Development Kit on the Board Update

Portal web page to access the kit’s home page for documentation updates

and additional new designs.

f You c an al so n avi g ate directly to the Stratix IV E FPGA Development Kit page of the

Altera website to determine if you have the latest kit software.

Using the Board Update Portal to Update User Designs

Using the Board Update Portal to Update User Designs

The Board Update Portal allows you to write new designs to the user hardware

portion of flash memory. Designs must be in the Nios II Flash Programmer File

(.flash) format.

1 Design files available from the Stratix IV E FPGA Development Kit page include

.flash files. You can also create .flash files from your own custom design. Refer to

“Preparing Design Files for Flash Programming” on page A–2 for information about

preparing your own design for upload.

To upload a design over the network into the user portion of flash memory on your

board, perform the following steps:

1. Perform the steps in “Connecting to the Board Update Portal Web Page” to access

the Board Update Portal web page.

2. In the Hardware File Name field specify the .flash file that you either downloaded

from the Altera website or created on your own. If there is a software component

to the design, specify it in the same manner using the Software File Name field,

otherwise leave the Software File Name field blank.

3. Click Upload. The progress bar indicates the percent complete.

4. To configure the FPGA with the new design after the flash memory upload process

is complete, set the PGM CONFIG SELECT rotary switch (SW5) to the 1 position

and power cycle the board, or press the RESET CONFIGn button (S1).

1 As long as you don’t overwrite the factory image in the flash memory device, you can

continue to use the Board Update Portal to write new designs to the user hardware

portion of flash memory. If you do overwrite the factory image, you can restore it by

following the instructions in “Restoring the Flash Device to the Factory Settings” on

page A–4.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 27

6. Board Test System

The kit includes a design example and application called the Board Test System to test

the functionality of the Stratix IV E FPGA development board. The application

provides an easy-to-use interface to alter functional settings and observe the results.

You can use the application to test board components, modify functional parameters,

observe performance, and measure power usage. The application is also useful as a

reference for designing systems. To install the application, follow the steps in

“Installing the Stratix IV E FPGA Development Kit” on page 3–2.

The application provides access to the following Stratix IV E FPGA development

board features:

■ General purpose I/O (GPIO)

■ SRAM

■ Flash memory

■ DDR3, RLDRAM II, and QDR II+ memories

■ HSMC connectors

■ Character LCD

■ Graphics LCD

■ Ethernet

The application allows you to exercise most of the board components. While using the

application, you reconfigure the FPGA several times with test designs specific to the

functionality you are testing.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 28

6–2 Chapter 6: Board Test System

The Board Test System GUI communicates over the JTAG bus to a test design running

in the Stratix IV E device. Figure 6–1 shows the initial GUI for a board that is in the

factory configuration.

Figure 6–1. Board Test System Graphical User Interface

Several designs are provided to test the major board features. Each design provides

data for one or more tabs in the application. The Configure menu identifies the

appropriate design to download to the FPGA for each tab.

After successful FPGA configuration, the appropriate tab appears and allows you to

exercise the related board features. Highlights appear in the board picture around the

corresponding components.

The Power Monitor button starts the Power Monitor application that measures and

reports current power and temperature information for the board. Because the

application communicates over the JTAG bus to the MAX II device, you can measure

the power of any design in the FPGA, including your own designs.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 29

Chapter 6: Board Test System 6–3

Preparing the Board

1 The Board Test System and Power Monitor share the JTAG bus with other

applications like the Nios II debugger and the SignalTap

Analyzer. Because the Quartus II programmer uses most of the bandwidth of the

JTAG bus, other applications using the JTAG bus might time out. Be sure to close the

other applications before attempting to reconfigure the FPGA using the Quartus II

Programmer.

Preparing the Board

With the power to the board off, following these steps:

1. Connect the USB cable to the board.

2. Verify the settings for the board settings DIP switch banks (SW1, SW2, and SW4)

match Table 4–1 on page 4–3, Table 4–2 on page 4–4, and Table 4–3 on page 4–5.

3. Set the PGM CONFIG SELECT rotary switch (SW5) to the 1 position.

4. Verify the settings for the jumpers match Table 4–4 on page 4–6. These settings

determine the devices to include in the JTAG chain, among other important

default settings.

f For more information about the board’s DIP switch and jumper settings,

®

II Embedded Logic

refer to the Stratix IV E FPGA Development Board Reference Manual.

5. Turn the power to the board on. The board loads the design stored in the user

hardware portion of flash memory into the FPGA. If your board is still in the

factory configuration or if you have downloaded a newer version of the Board Test

System to flash memory through the Board Update Portal, the design loads the

GPIO, SRAM, and flash memory tests.

c To ensure operating stability, keep the USB cable connected and the board

powered on when running the demonstration application. The application

cannot run correctly unless the USB cable is attached and the board is on.

Running the Board Test System

To run the application, navigate to the <install

dir>\kits\stratixIVE_4se530_fpga\examples\board_test_system directory and run

the BoardTestSystem.exe application.

1 On Windows, click Start > All Programs > Altera > Stratix IV E FPGA Development

Kit <version> > Board Test System to run the application.

A GUI appears, displaying the application tab that corresponds to the design running

in the FPGA. The Stratix IV E FPGA development board’s flash memory ships

preconfigured with the design that corresponds to the Config, GPIO, and SSRAM

and Flash tabs.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 30

6–4 Chapter 6: Board Test System

Using the Board Test System

1 If you power up your board with the PGM CONFIG SELECT rotary switch (SW5) in a

position other than the 1 position, or if you load your own design into the FPGA with

the Quartus II Programmer, you receive a message prompting you to configure your

board with a valid Board Test System design. Refer to “The Configure Menu” for

information about configuring your board.

Using the Board Test System

This section describes each control in the Board Test System application.

The Configure Menu

Use the Configure menu (Figure 6–2) to select the design you want to use. Each design

example tests different functionality that corresponds to one or more application tabs.

Figure 6–2. The Configure Menu

To configure the FPGA with a test system design, perform the following steps:

1. On the Configure menu, click one of the following options to determine how to

pass data through the JTAG chain:

■ Use Fast Configuration—Compresses the data for faster loading.

■ Use Quartus II Programmer—Uses the standard JTAG-based configuration

method.

2. On the Configure menu, click the configure command that corresponds to the

functionality you wish to test.

3. In the dialog box that appears, click Configure or Download Start to download

the corresponding design’s SRAM Object File (.sof) to the FPGA. The download

process usually takes about a minute.

4. When configuration finishes, close the Quartus II Programmer, if using it. The

design begins running in the FPGA. The corresponding GUI application tabs that

interface with the design enable.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 31

Chapter 6: Board Test System 6–5

Using the Board Test System

The Config Tab

The Config tab shows information about the board’s current configuration.

Figure 6–1 on page 6–2 shows the Config tab. The tab displays the contents of the

MAX II registers, the JTAG chain, the board’s MAC address, the flash memory map,

and other details stored on the board.

The following sections describe the controls on the Config tab.

Board Information

The Board information controls display static information about your board.

■ MAX II ver—Indicates the version of MAX II code currently running on the board.

The MAX II code resides in the <install

dir>\kits\stratixIVE_4se530_fpga\examples directory. Newer revisions of this

code might be available on the Stratix IV E FPGA Development Kit page of the

Altera website.

■ MAC—Indicates the MAC address of the board.

MAX II Registers

The MAX II registers control allow you to view and change the current MAX II

register values as described in Table 6–1. Changes to the register values with the GUI

take effect immediately. For example, writing a 0 to SRST resets the board.

Table 6–1. MAX II Registers

Register Name

System Reset

(SRST)

Page Select Register

(PSR)

Read/Write

Capability

Description

Write only Set to 0 to initiate an FPGA reconfiguration.

Determines which of the up to eight (0-7) pages of flash

Read / Write

memory to use for FPGA reconfiguration. The flash memory

ships with pages 0 and 1 preconfigured.

When set to 0, the value in PSR determines the page of

Page Select Override

(PSO)

Read / Write

flash memory to use for FPGA reconfiguration. When set to

1, the value in PSS determines the page of flash memory to

use for FPGA reconfiguration.

Page Select Switch

(PSS)

■ PSO—Sets the MAX II PSO register. The following options are available:

■ Use PSR—Allows the PSR to determine the page of flash memory to use for

Read only Holds the current value of the rotary switch (SW5).

FPGA reconfiguration.

■ Use PSS—Allows the PSS to determine the page of flash memory to use for

FPGA reconfiguration.

■ PSR—Sets the MAX II PSR register. The numerical values in the list corresponds to

the page of flash memory to load during FPGA reconfiguration. Refer to Tabl e 6– 1

for more information.

■ PSS—Displays the MAX II PSS register value. Refer to Tab le 6– 1 for the list of

available options.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 32

6–6 Chapter 6: Board Test System

■ SRST—Resets the system and reloads the FPGA with a design from flash memory

Using the Board Test System

based on the other MAX II register values. Refer to Tab le 6– 1 for more information.

1 Because the Config tab requires that a specific design is running in the FPGA, writing

a 0 to SRST or changing the PSO value can cause the Board Test System to stop

running.

JTAG Chain

The JTAG chain control shows all the devices currently in the JTAG chain. The

Stratix IV E device is always the first device in the chain.

1 Installing the shunt jumper on jumper J10 includes the MAX II device in the JTAG

chain.

SOPC Builder Memory Map

The SOPC Builder memory map control shows the memory map of the FPGA

design’s SOPC Builder system.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 33

Chapter 6: Board Test System 6–7

Using the Board Test System

The GPIO Tab

The GPIO tab allows you to interact with all the general purpose user I/O

components on your board. You can write to the character LCD, read DIP switch

settings, turn LEDs on or off, write to the 7-segment display, load images to the

graphics LCD, run a server program on the Ethernet port, and detect push button

presses. Figure 6–3 shows the GPIO tab.

Figure 6–3. The GPIO Tab

The following sections describe the controls on the GPIO tab.

Character LCD

The Character LCD controls allow you to display text strings on the character LCD on

your board. Type text in the text boxes and then click Write.

1 If you exceed the 16 character display limit on either line, a warning message appears.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 34

6–8 Chapter 6: Board Test System

Using the Board Test System

User DIP Switches

The read-only User DIP switch control displays the current positions of the switches

in the user DIP switch bank (SW1). Change the switches on the board to see the

graphical display change accordingly.

User LEDs

The User LEDs control displays the current state of the user LEDs. Click the LED

buttons to turn the board LEDs on and off.

Push Button Switches

The read-only Push Button switches control displays the current state of the board

user push buttons. Press a push button on the board to see the graphical display

change accordingly.

7-Segment Display

The 7-segment display controls allow you to display hexadecimal numbers on the

7-segment display on your board. Type hexadecimal numbers in the text box and then

click Write.

Graphics LCD

The Graphics LCD control allows you to display Bitmap Image Files (.bmp) on the

graphics LCD on your board.

■ Select File—Allows you to browse your file system and select a .bmp image to

load.

■ Load—Downloads the selected file to the board.

Ethernet

Click Start Simple Socket Server to run the simple_socket_server.elf program that

was downloaded into FPGA during configuration.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 35

Chapter 6: Board Test System 6–9

Using the Board Test System

The Flash Tab

The Flash tab allows you to read and write flash memory on your board. Figure 6–4

shows the Flash tab.

Figure 6–4. The Flash Tab

The following sections describe the controls on the Flash tab.

Read

The Read control reads the flash memory on your board. Type a starting address in

the text box and click Read. Values starting at the specified address appear in the

table. The base address of flash memory in this Nios II-based BTS design is

0x0800.0000. The valid address range within the 64-MB flash memory is 0x0000.0000

through 0x03FF.FFFF, as shown in the GUI.

1 If you enter an address outside of the flash memory address space, a warning

message identifies the valid flash memory address range.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 36

6–10 Chapter 6: Board Test System

Using the Board Test System

Write

The Wri te control writes the flash memory on your board. To update the flash

memory contents, change values in the table and click Wr ite. The application writes

the new values to flash memory and then reads the values back to guarantee that the

graphical display accurately reflects the memory contents.

1 To prevent overwriting the dedicated portions of flash memory, the application limits

the writable flash memory address range from 0x03FE.0000 to 0x03FF.FFFF (which

corresponds to the unused flash memory address range shown in Table A–1 on

page A–1).

Random Test

Starts a random data pattern test to flash memory where the data pattern contents are

read back and displayed. Errors are reported in the messages window. This test takes

10-15 seconds to run with an hour-glass displayed while the test is busy.

Increment Test

Starts an incrementing data pattern test to flash memory where the data pattern

contents are read back and displayed. Errors are reported in the messages window.

This test takes 10-15 seconds to run with an hour-glass displayed while the test is

busy.

CFI Query

The CFI Query control updates the memory table, displaying the CFI ROM table

contents from the flash device.

Reset

The Reset control executes the flash device’s reset command and updates the memory

table displayed on the Flash tab.

Erase

Erases flash memory, which is limited to a scratch page in the upper 128K block.

Flash Memory Map

Displays the flash memory map for the Stratix IV E FPGA Development Kit.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 37

Chapter 6: Board Test System 6–11

Using the Board Test System

The SSRAM Tab

The SSRAM tab allows you to read and write SSRAM on your board. Figure 6–5

shows the SSRAM tab.

Figure 6–5. The SSRAM Tab

The following sections describe the controls on the SSRAM tab.

Read

Reads the SSRAM on your board. To see the SSRAM contents, type a starting address

in the text box and click Read. Values starting at the specified address appear in the

table. The base address of SRAM in this Nios II-based BTS design is 0x0D00.0000. The

valid address range within the 2-MB SRAM is 0x0000.0000 through 0x001F.FFFF, as

shown in the GUI.

1 If you enter an address outside of the 0x0000.0000 to 0x001F.FFFF SSRAM address

space, a warning message identifies the valid SSRAM address range.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 38

6–12 Chapter 6: Board Test System

Using the Board Test System

Write

Writes the SSRAM on your board. To update the SSRAM contents, change values in

the table and click Write. The application writes the new values to SSRAM and then

reads the values back to guarantee that the graphical display accurately reflects the

memory contents.

Random Test

Starts a random data pattern to SSRAM. After writing a block of SRAM with this data

pattern, the contents are read back and displayed. Errors are reported in the messages

window.

Increment Test

Starts an incrementing data pattern test to SSRAM. After writing a block of SRAM

with this data pattern, the contents are read back and displayed. Errors are reported in

the messages window.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 39

Chapter 6: Board Test System 6–13

Using the Board Test System

The DDR3 Tab

The DDR3 tab allows you to read and write the DDR3 memory on your board.

Figure 6–6 shows the DDR3 tab.

Figure 6–6. The DDR3 Tab

The following sections describe the controls on the DDR3 tab.

Start

The Start control initiates DDR3 memory transaction performance analysis.

Stop

The Stop control terminates transaction performance analysis.

Performance Indicators

These controls display current transaction performance analysis information collected

since you last pressed Start:

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 40

6–14 Chapter 6: Board Test System

■ Write, Read, and To t al performance bars—Show the percentage of maximum

Using the Board Test System

theoretical data rate that the requested transactions are able to achieve.

■ Write (MBps), Read (MBps), and Total (MBps)—Show the number of bytes of

data analyzed per second. The data bus is 72 bits wide and the frequency is

533 MHz double data rate (1066 Mbps per pin), equating to a theoretical

maximum bandwidth of 9594 MBps.

Error Control

The Error control controls display data errors detected during analysis and allow you

to insert errors:

■ Detected errors—Displays the number of data errors detected in the hardware.

■ Inserted errors—Displays the number of errors inserted into the transaction

stream.

■ Insert Error—Inserts a one-word error into the transaction stream each time you

click the button. Insert Error is only enabled during transaction performance

analysis.

■ Clear—Resets the Detected errors and Inserted errors counters to zeros.

Number of Addresses to Write and Read

The Number of addresses to write and read control determines the number of

addresses to use in each iteration of reads and writes. Valid values range from 8 to

16,777,216.

Data Type

The Data type control specifies the type of data contained in the transactions. The

following data types are available for analysis:

■ PRBS—Selects pseudo-random bit sequences.

■ Memory—Selects a generic data pattern stored in the on chip memory of the

Stratix IV E device.

■ Math—Selects data generated from a simple math function within the FPGA

fabric.

Read and Write Control

The Read and write control specifies the type of transactions to analyze. The

following transaction types are available for analysis:

■ Write then read—Selects read and write transactions for analysis.

■ Read only—Selects read transactions for analysis.

■ Write only—Selects write transactions for analysis.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 41

Chapter 6: Board Test System 6–15

Using the Board Test System

The QDRII+ Tab

The QDRII+ tab allows you to read and write the QDR II+ memory on your board.

Figure 6–7 shows the QDRII+ tab.

Figure 6–7. The QDRII+ Tab

The following sections describe the controls on the QDRII+ tab.

Start

The Start control initiates QDR II+ memory transaction performance analysis.

Stop

The Stop control terminates transaction performance analysis.

Performance Indicators

These controls display current transaction performance analysis information collected

since you last clicked Start:

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 42

6–16 Chapter 6: Board Test System

■ Write and Read performance bars—Show the percentage of maximum theoretical

Using the Board Test System

data rate that the requested transactions are able to achieve.

■ Write (MBp s ) and Read (MBps)—Show the number of bytes of data analyzed per

second. The QDR II+ bus is 18 bits wide for both read and write, and the frequency

is 400 MHz double data rate (800 Mbps per pin), equating to a theoretical

maximum bandwidth of 1800 MBps, and 3600 MBps for simultaneous read and

write.

Error Control

The Error control controls display data errors detected during analysis and allow you

to insert errors:

■ Detected errors—Displays the number of data errors detected in the hardware.

■ Inserted errors—Displays the number of errors inserted into the transaction

stream.

■ Insert Error—Inserts a one-word error into the transaction stream each time you

click the button. Insert Error is only enabled during transaction performance

analysis.

■ Clear—Resets the Detected errors and Inserted errors counters to zeros.

Number of Addresses to Write and Read

The Number of addresses to write and read control determines the number of

addresses to use in each iteration of reads and writes. Valid values range from 8 to

1,048,576.

Data Type

The Data type control specifies the type of data contained in the transactions. The

following data types are available for analysis:

■ PRBS—Selects pseudo-random bit sequences.

■ Memory—Selects a generic data pattern stored in the on chip memory of the

Stratix IV E device.

■ Math—Selects data generated from a simple math function within the FPGA

fabric.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 43

Chapter 6: Board Test System 6–17

Using the Board Test System

The RLDRAMII Tab

The RLDRAMII tab allows you to read and write the RLDRAM II on your board.

Figure 6–8 shows the RLDRAMII tab.

Figure 6–8. The RLDRAMII Tab

The following sections describe the controls on the RLDRAMII tab.

Start

The Start control initiates RLDRAM II memory transaction performance analysis.

Stop

The Stop control terminates transaction performance analysis.

Performance Indicators

These controls display current transaction performance analysis information collected

since you last clicked Start:

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 44

6–18 Chapter 6: Board Test System

■ Write, Read, and To t al performance bars—Show the percentage of maximum

Using the Board Test System

theoretical data rate that the requested transactions are able to achieve.

■ Write (MBps), Read (MBps), and Total (MBps)—Show the number of bytes of

data analyzed per second. The RLDRAMII bus is 36 bits wide and the frequency is

400 MHz double data rate (800 Mbps per pin), equating to a theoretical maximum

bandwidth of 3600 MBps.

Error Control

The Error control controls display data errors detected during analysis and allow you

to insert errors:

■ Detected errors—Displays the number of data errors detected in the hardware.

■ Inserted errors—Displays the number of errors inserted into the transaction

stream.

■ Insert Error—Inserts a one-word error into the transaction stream each time you

click the button. Insert Error is only enabled during transaction performance

analysis.

■ Clear—Resets the Detected errors and Inserted errors counters to zeros.

Number of Addresses to Write and Read

The Number of addresses to write and read control determines the number of

addresses to use in each iteration of reads and writes. Valid values range from 8 to

16,777,216.

Data Type

The Data type control specifies the type of data contained in the transactions. The

following data types are available for analysis:

■ PRBS—Selects pseudo-random bit sequences.

■ Memory—Selects a generic data pattern stored in the on chip memory of the

Stratix IV E device.

■ Math—Selects data generated from a simple math function within the FPGA

fabric.

Read and Write Control

The Read and write control control specifies the type of transactions to analyze. The

following transaction types are available for analysis:

■ Write then read—Selects read and write transactions for analysis.

■ Read only—Selects read transactions for analysis.

■ Write only—Selects write transactions for analysis.

Stratix IV E FPGA Development Kit User Guide June 2011 Altera Corporation

Page 45

Chapter 6: Board Test System 6–19

Using the Board Test System

The HSMC Tab

The HSMC tab allows you to perform loopback tests on the HSMC A and HSMC B

ports. Figure 6–9 shows the HSMC tab.

Figure 6–9. The HSMC Tab

1 You must have the loopback HSMC installed on the HSMC connector that you are

testing for this test to work correctly.

The following sections describe the controls on the HSMC tab.

Status

The Status control displays the following status information during the loopback test:

■ PLL lock—Shows the PLL locked or unlocked state.

■ Channel lock—Shows the channel locked or unlocked state. When locked, all

lanes are word aligned and channel bonded.

■ Pattern sync—Shows the pattern synced or not synced state. The pattern is

considered synced when the start of the data sequence is detected.

June 2011 Altera Corporation Stratix IV E FPGA Development Kit User Guide

Page 46

6–20 Chapter 6: Board Test System

Using the Board Test System

Port

The Port control allows you to specify the type of test to run on the HSMC ports. The

following HSMC port tests are available:

■ HSMA x17 LVDS SERDES

■ HSMA x3 single-ended loopback

■ HSMB x17 LVDS SERDES

■ HSMB x3 single-ended loopback

Data Type

The Data type control specifies the type of data contained in the transactions. The

following data types are available for analysis: