Page 1

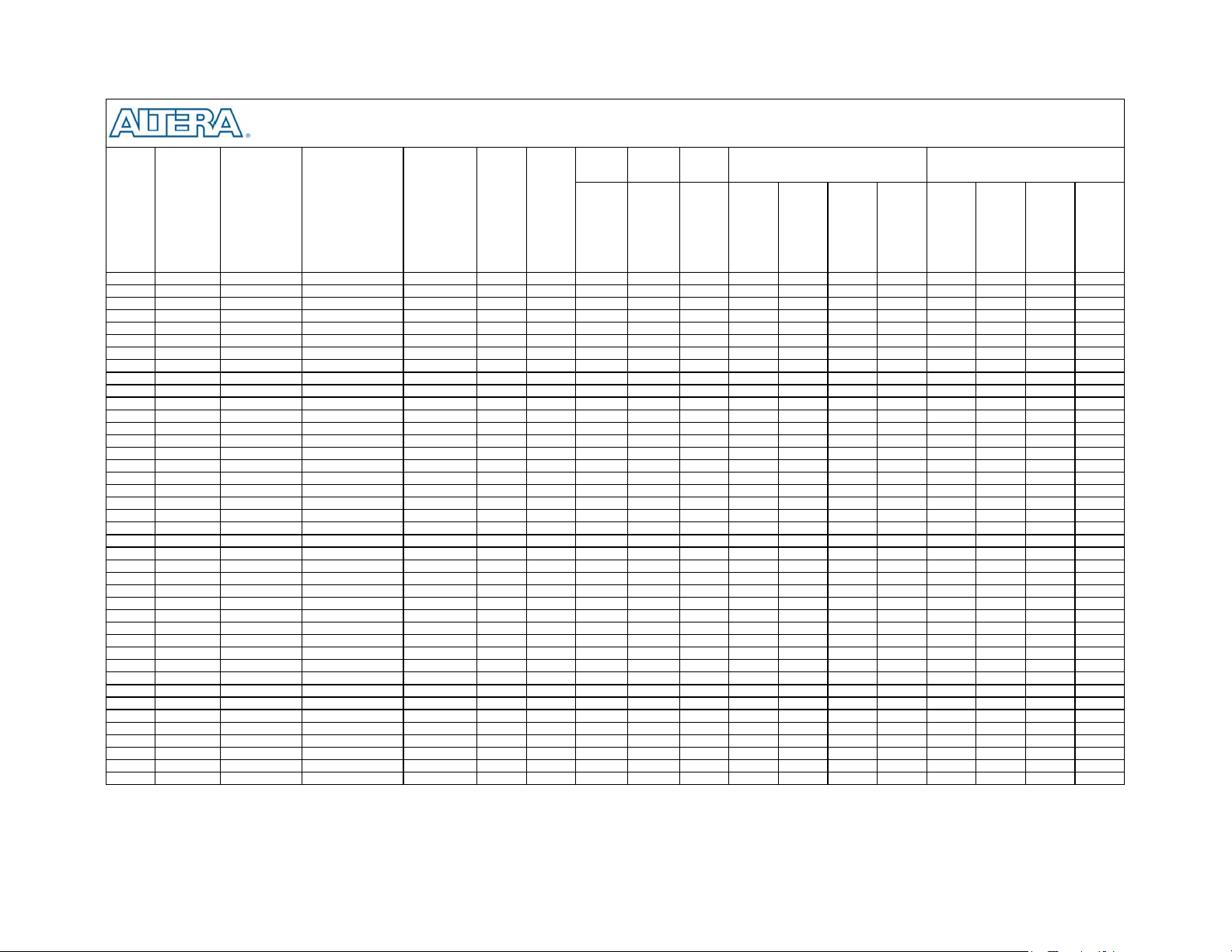

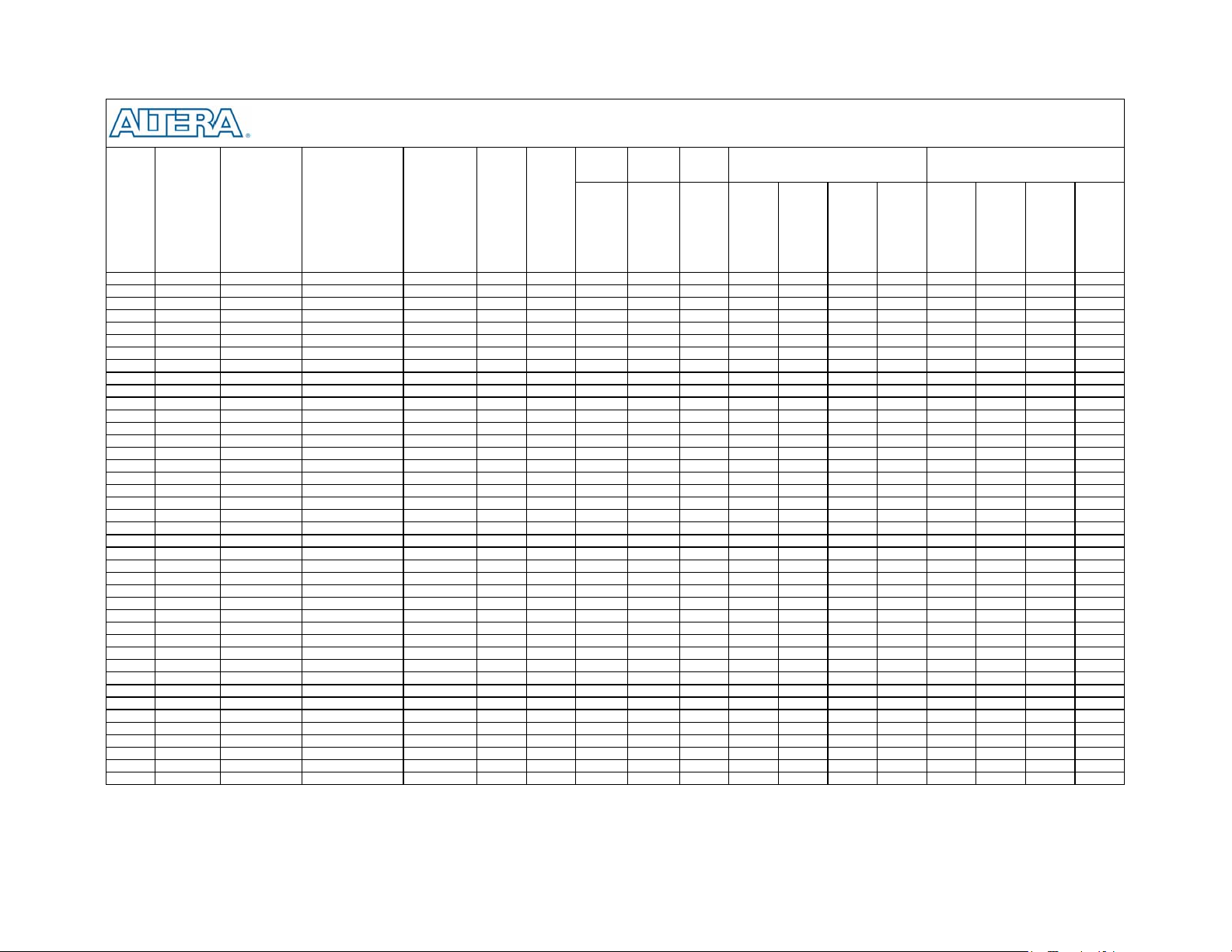

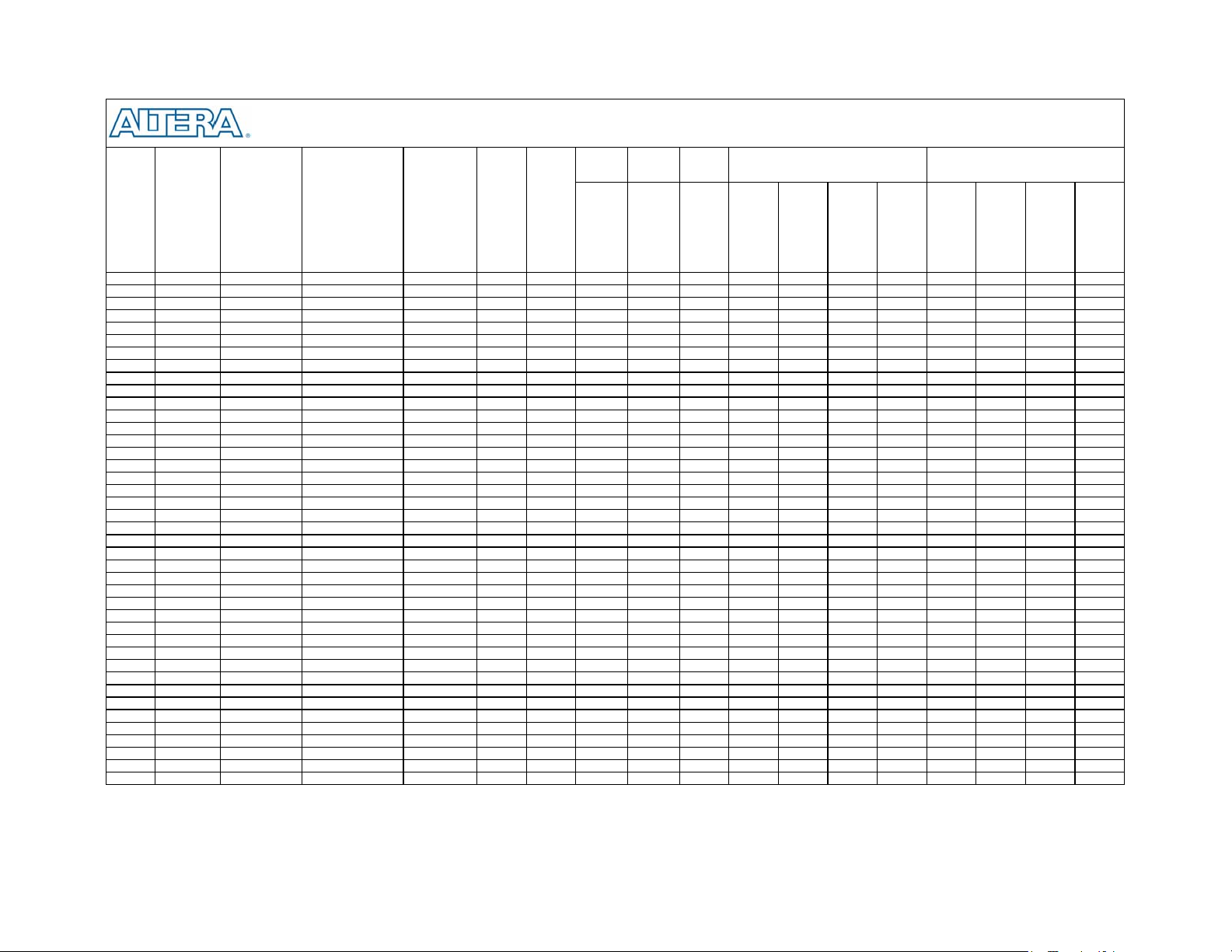

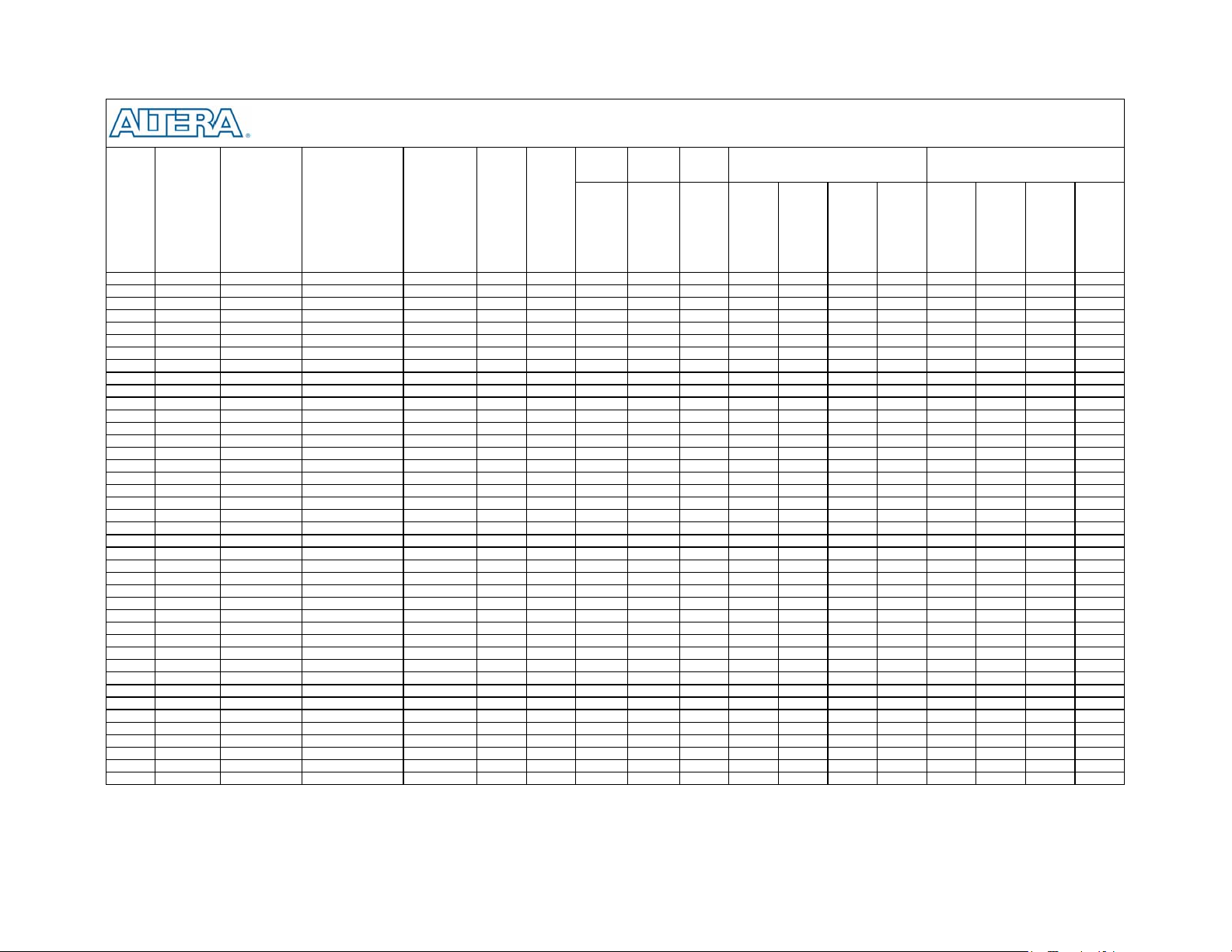

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 1 of 47

Number

B2 VREFB2N0 FPLL7CLKp INPUT C39 C34

B2 VREFB2N0 FPLL7CLKn INPUT C38 C33

B2 VREFB2N0 IO DIFFIO_TX58p G33 DQ18L0 DQ18L0

B2 VREFB2N0 IO DIFFIO_TX58n G32 DQ18L1 DQ18L1

B2 VREFB2N0 IO DIFFIO_RX57p D37 DQ0L0 DQ0L0

B2 VREFB2N0 IO DIFFIO_RX57n D36 DQ0L1 DQ0L1

B2 VREFB2N0 IO DIFFIO_TX57p J32 DQS18L DQS18L

B2 VREFB2N0 IO DIFFIO_TX57n J31 DQ18L2 DQ18L2

B2 VREFB2N0 IO DIFFIO_RX56p E37 DQS0L DQS0L

B2 VREFB2N0 IO DIFFIO_RX56n E36 DQ0L2 DQ0L2

B2 VREFB2N0 IO DIFFIO_TX56p K32 DQ18L3 DQ18L3

B2 VREFB2N0 IO DIFFIO_TX56n K31 DM18L

B2 VREFB2N0 IO DIFFIO_RX55p D39 DQ0L3 DQ0L3

B2 VREFB2N0 IO DIFFIO_RX55n D38 DM0L

B2 VREFB2N0 IO DIFFIO_TX55p K30 DQ19L0 DQ19L0

B2 VREFB2N0 IO DIFFIO_TX55n L31 DQ19L1 DQ19L1

B2 VREFB2N0 IO DIFFIO_RX54p F38 DQ1L0 DQ1L0

B2 VREFB2N0 IO DIFFIO_RX54n F37 DQ1L1 DQ1L1

B2 VREFB2N0 IO DIFFIO_TX54p K34 DQS19L DQS19L

B2 VREFB2N0 IO DIFFIO_TX54n K33 DQ19L2 DQ19L2

B2 VREFB2N0 VREFB2N0 VREFB2N0 W35 R30

B2 VREFB2N0 IO DIFFIO_RX53p J34 DQS1L DQS1L

B2 VREFB2N0 IO DIFFIO_RX53n J33 DQ1L2 DQ1L2

B2 VREFB2N0 IO DIFFIO_TX53p L34 DQ19L3 DQ19L3

B2 VREFB2N0 IO DIFFIO_TX53n L33 DM19L

B2 VREFB2N0 IO DIFFIO_RX52p E39 DQ1L3 DQ1L3

B2 VREFB2N0 IO DIFFIO_RX52n F39 DM1L

B2 VREFB2N0 IO DIFFIO_TX52p M32 DQ20L0 DQ20L0

B2 VREFB2N0 IO DIFFIO_TX52n M31 DQ20L1 DQ20L1

B2 VREFB2N0 IO DIFFIO_RX51p G38 DQ2L0 DQ2L0

B2 VREFB2N0 IO DIFFIO_RX51n G37 DQ2L1 DQ2L1

B2 VREFB2N0 IO DIFFIO_TX51p N32 F30 DQS20L DQS20L

B2 VREFB2N0 IO DIFFIO_TX51n N31 G31 DQ20L2 DQ20L2 DQ25L0

B2 VREFB2N0 IO DIFFIO_RX50p H37 D33 DQS2L DQS2L

B2 VREFB2N0 IO DIFFIO_RX50n H36 D32 DQ2L2 DQ2L2 DQ3L0

B2 VREFB2N0 IO DIFFIO_TX50p N34 H29 DQ20L3 DQ20L3 DQ25L1

B2 VREFB2N0 IO DIFFIO_TX50n N33 G30 DM20L DQS25L

VREF Group Pin

Name/Function

VCCD_PLL7 L28 K25

VCCA_PLL7 J29 J26

GNDA_PLL7 K29 K26

GNDA_PLL7 K28 J25

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

ersion 1.5

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

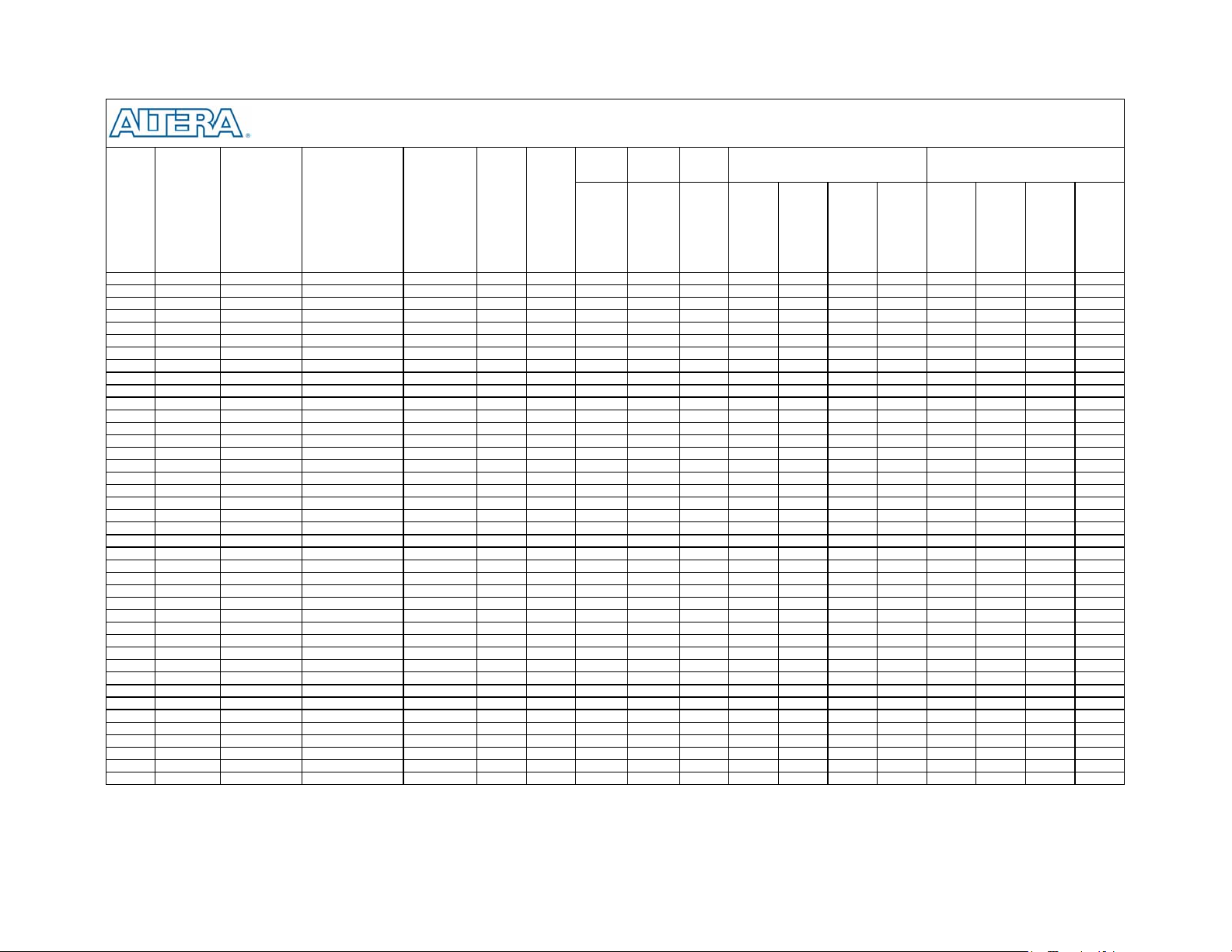

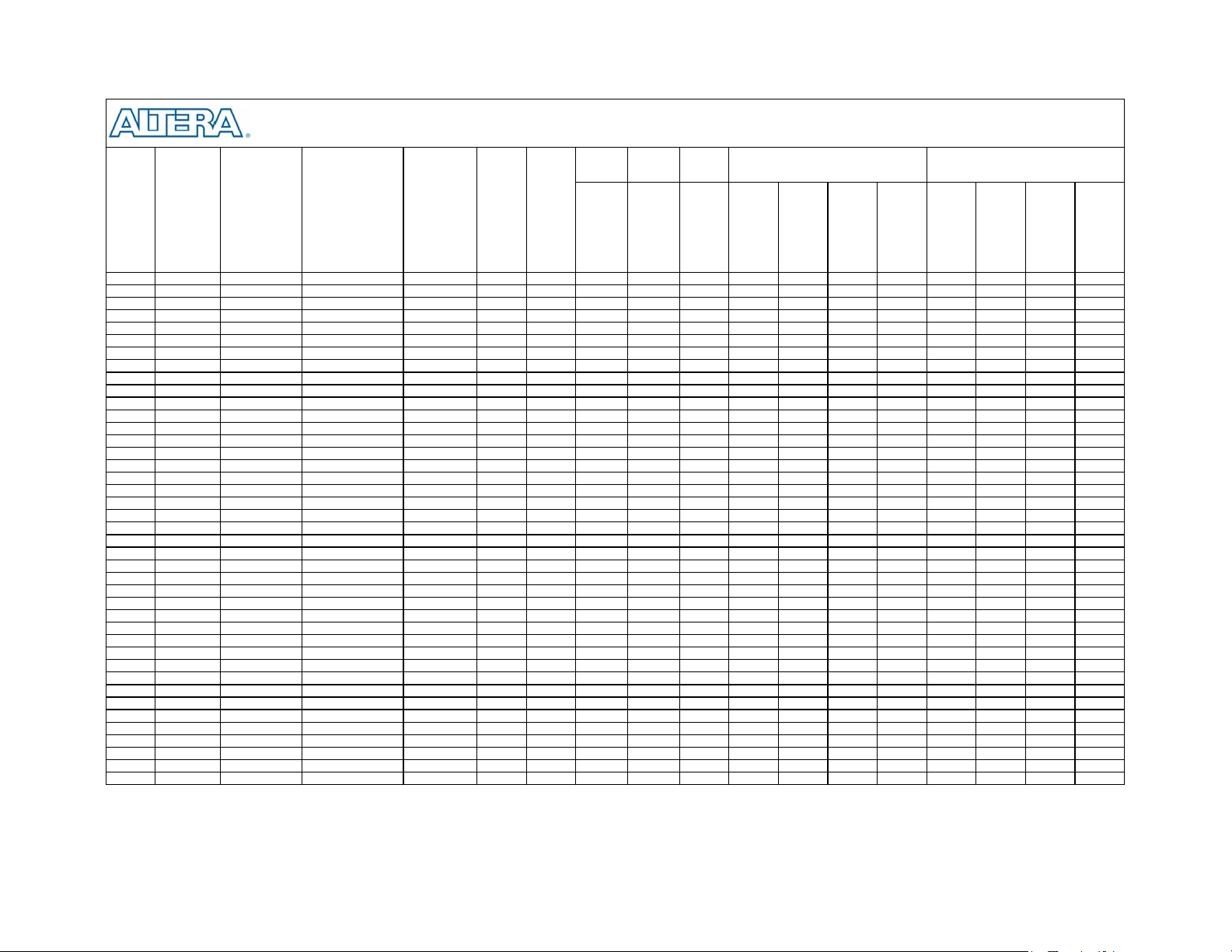

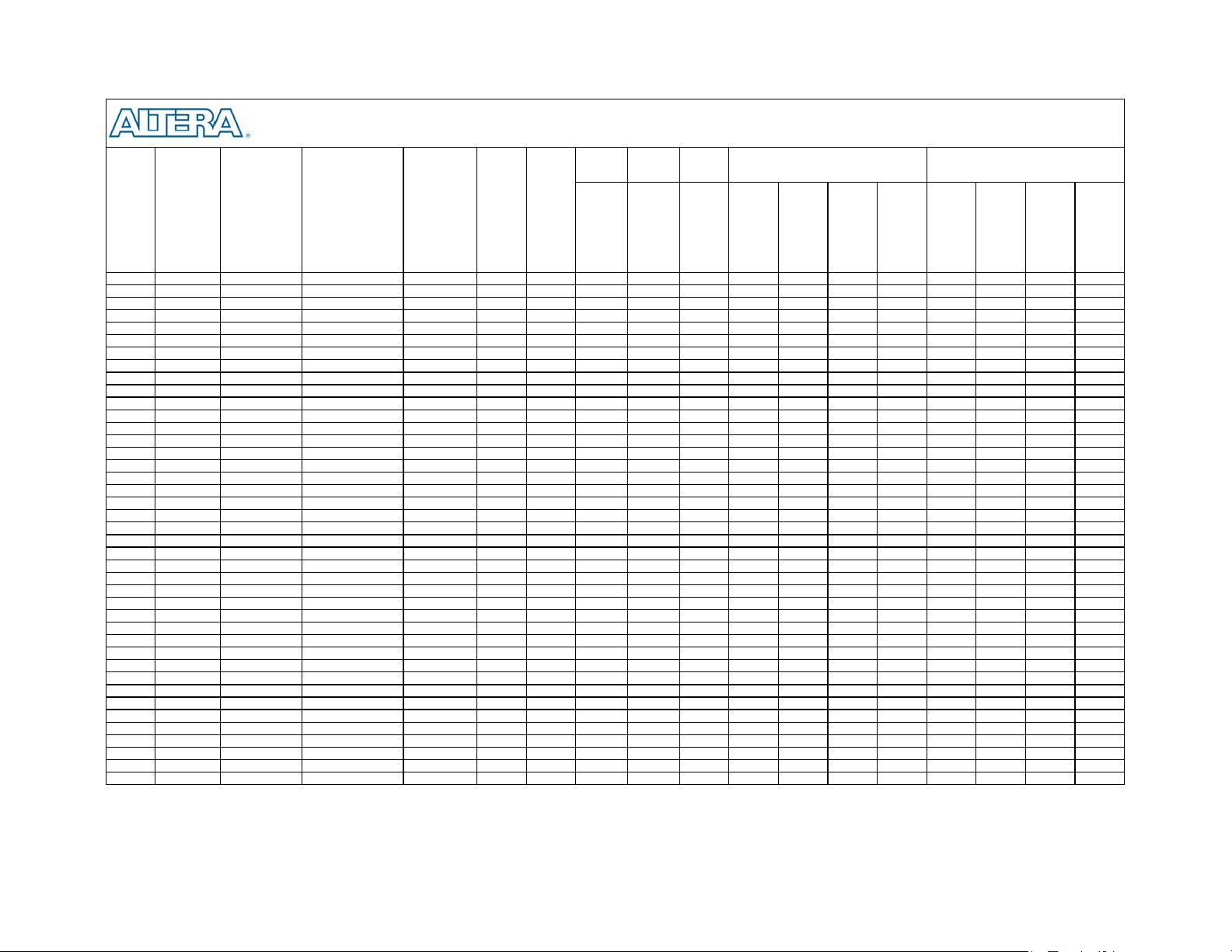

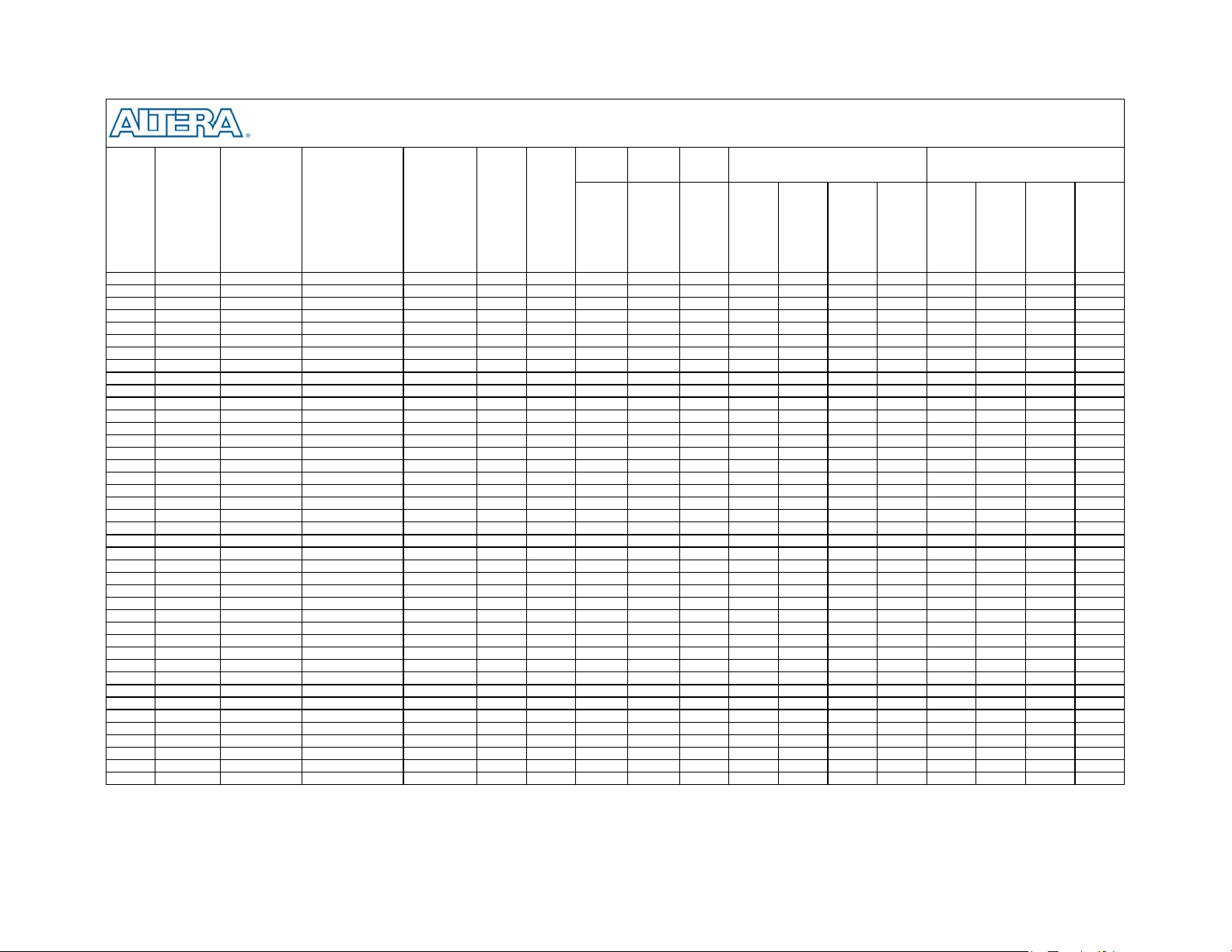

Page 2

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 2 of 47

ersion 1.5

Number

B2 VREFB2N0 IO DIFFIO_RX49p G39 E32 DQ2L3 DQS0L DQS0L DQ2L3 DQ3L1 DQS0L DQS0L

B2 VREFB2N0 IO DIFFIO_RX49n H39 E31 DM2L DQ0L2 DQ0L2 DQS3L DQ0L2 DQ0L2

B2 VREFB2N0 IO DIFFIO_TX49p N27 J28 DQ21L0 DQ21L0 DQ13L3 DQ13L3 DQ21L0 DQ25L2 DQ13L3 DQ17L2

B2 VREFB2N0 IO DIFFIO_TX49n P28 K27 DQ21L1 DQ21L1 DM13L DM13L DQ21L1 DQ25L3 DQ17L3

B2 VREFB2N1 IO DIFFIO_RX48p M34 E34 DQ3L0 DQ3L0 DQ0L0 DQ0L0 DQ3L0 DQ3L2 DQ0L0 DQ0L0

B2 VREFB2N1 IO DIFFIO_RX48n M33 D34 DQ3L1 DQ3L1 DQ0L1 DQ0L1 DQ3L1 DQ3L3 DQ0L1 DQ0L1

B2 VREFB2N1 IO DIFFIO_TX48p P34 J30 DQS21L DQS21L DQS21L DQ26L0

B2 VREFB2N1 IO DIFFIO_TX48n P33 J29 DQ21L2 DQ21L2 DQ21L2 DQ26L1 DQ17L0

B2 VREFB2N1 IO DIFFIO_RX47p K36 F32 DQS3L DQS3L DQ0L3 DQ0L3 DQS3L DQ4L0 DQ0L3 DQ0L3

B2 VREFB2N1 IO DIFFIO_RX47n K35 F31 DQ3L2 DQ3L2 DM0L DM0L DQ3L2 DQ4L1 DQ1L0

B2 VREFB2N1 IO DIFFIO_TX47p P30 K30 DQ21L3 DQ21L3 DQ21L3 DQS26L

B2 VREFB2N1 IO DIFFIO_TX47n R31 K29 DM21L DM21L DQ26L2

B2 VREFB2N1 IO DIFFIO_RX46p J37 F34 DQ3L3 DQ3L3 DQS13L DQS13L DQ3L3 DQS4L DQS13L DQ1L1

B2 VREFB2N1 IO DIFFIO_RX46n J36 F33 DM3L DM3L DQ13L2 DQ13L2 DQ4L2 DQ13L2 DQS1L

B2 VREFB2N1 IO DIFFIO_TX46p R33 L26 DQ22L0 DQ22L0 DQS14L DQS14L DQ22L0 DQ26L3 DQS14L DQS18L

B2 VREFB2N1 IO DIFFIO_TX46n R32 L25 DQ22L1 DQ22L1 DQ14L2 DQ14L2 DQ22L1 DQ27L0 DQ14L2 DQ18L2

B2 VREFB2N1 IO DIFFIO_RX45p L37 G33 DQ4L0 DQ4L0 DQ1L0 DQ1L0 DQ4L0 DQ4L3 DQ1L0 DQ1L2

B2 VREFB2N1 IO DIFFIO_RX45n L36 G32 DQ4L1 DQ4L1 DQ1L1 DQ1L1 DQ4L1 DQ5L0 DQ1L1 DQ1L3

B2 VREFB2N1 IO DIFFIO_TX45p P27 M26 DQS22L DQS22L DQ13L0 DQ13L0 DQS22L DQ27L1 DQ13L0 DQ17L1

B2 VREFB2N1 IO DIFFIO_TX45n R27 M25 DQ22L2 DQ22L2 DQ13L1 DQ13L1 DQ22L2 DQS27L DQ13L1 DQS17L

B2 VREFB2N1 IO DIFFIO_RX44p J39 H32 DQS4L DQS4L DQS4L DQ5L1

B2 VREFB2N1 IO DIFFIO_RX44n J38 H31 DQ4L2 DQ4L2 DQ4L2 DQS5L

B2 VREFB2N1 IO DIFFIO_TX44p R30 K28 DQ22L3 DQ22L3 DQ14L3 DQ14L3 DQ22L3 DQ27L2 DQ14L3 DQ18L3

B2 VREFB2N1 IO DIFFIO_TX44n T29 L28 DM22L DM22L DM14L DM14L DQ27L3 DQ19L0

B2 VREFB2N1 VREFB2N1 VREFB2N1 T36 M30

B2 VREFB2N1 IO DIFFIO_RX43p K38 G34 DQ4L3 DQ4L3 DQS1L DQS1L DQ4L3 DQ5L2 DQS1L DQ2L0

B2 VREFB2N1 IO DIFFIO_RX43n K37 H34 DM4L DM4L DQ1L2 DQ1L2 DQ5L3 DQ1L2 DQ2L1

B2 VREFB2N1 IO DIFFIO_TX43p T33 L29 DQ23L0 DQ23L0 DQ14L0 DQ14L0 DQ23L0 DQ28L0 DQ14L0 DQ18L0

B2 VREFB2N1 IO DIFFIO_TX43n T32 M29 DQ23L1 DQ23L1 DQ14L1 DQ14L1 DQ23L1 DQ28L1 DQ14L1 DQ18L1

B2 VREFB2N1 IO DIFFIO_RX42p K39 J32 DQ5L0 DQ5L0 DQ1L3 DQ1L3 DQ5L0 DQ6L0 DQ1L3 DQS2L

B2 VREFB2N1 IO DIFFIO_RX42n L39 J31 DQ5L1 DQ5L1 DM1L DM1L DQ5L1 DQ6L1 DQ2L2

B2 VREFB2N1 IO DIFFIO_TX42p U34 M28 DQS23L DQS23L DQS15L DQS15L DQS23L DQS28L DQS15L DQ19L2

B2 VREFB2N1 IO DIFFIO_TX42n U33 M27 DQ23L2 DQ23L2 DQ15L2 DQ15L2 DQ23L2 DQ28L2 DQ15L2 DQ19L3

B2 VREFB2N1 IO DIFFIO_RX41p M37 J34 DQS5L DQS5L DQ2L0 DQ2L0 DQS5L DQS6L DQ2L0 DQ2L3

B2 VREFB2N1 IO DIFFIO_RX41n M36 J33 DQ5L2 DQ5L2 DQ2L1 DQ2L1 DQ5L2 DQ6L2 DQ2L1 DQ3L0

B2 VREFB2N1 IO DIFFIO_TX41p T31 N27 DQ23L3 DQ23L3 DQ15L3 DQ15L3 DQ23L3 DQ28L3 DQ15L3

B2 VREFB2N1 IO DIFFIO_TX41n T30 N26 DM23L DM23L DM15L DM15L DQ29L0

B2 VREFB2N1 IO DIFFIO_RX40p N36 K33 DQ5L3 DQ5L3 DQS2L DQS2L DQ5L3 DQ6L3 DQS2L DQ3L1

B2 VREFB2N1 IO DIFFIO_RX40n N35 K32 DM5L DM5L DQ2L2 DQ2L2 DQ7L0 DQ2L2 DQS3L

B2 VREFB2N1 IO DIFFIO_TX40p R26 N25 DQ24L0 DQ24L0 DQ15L0 DQ15L0 DQ24L0 DQ29L1 DQ15L0 DQ19L1

B2 VREFB2N1 IO DIFFIO_TX40n T26 N24 DQ24L1 DQ24L1 DQ15L1 DQ15L1 DQ24L1 DQS29L DQ15L1 DQS19L

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

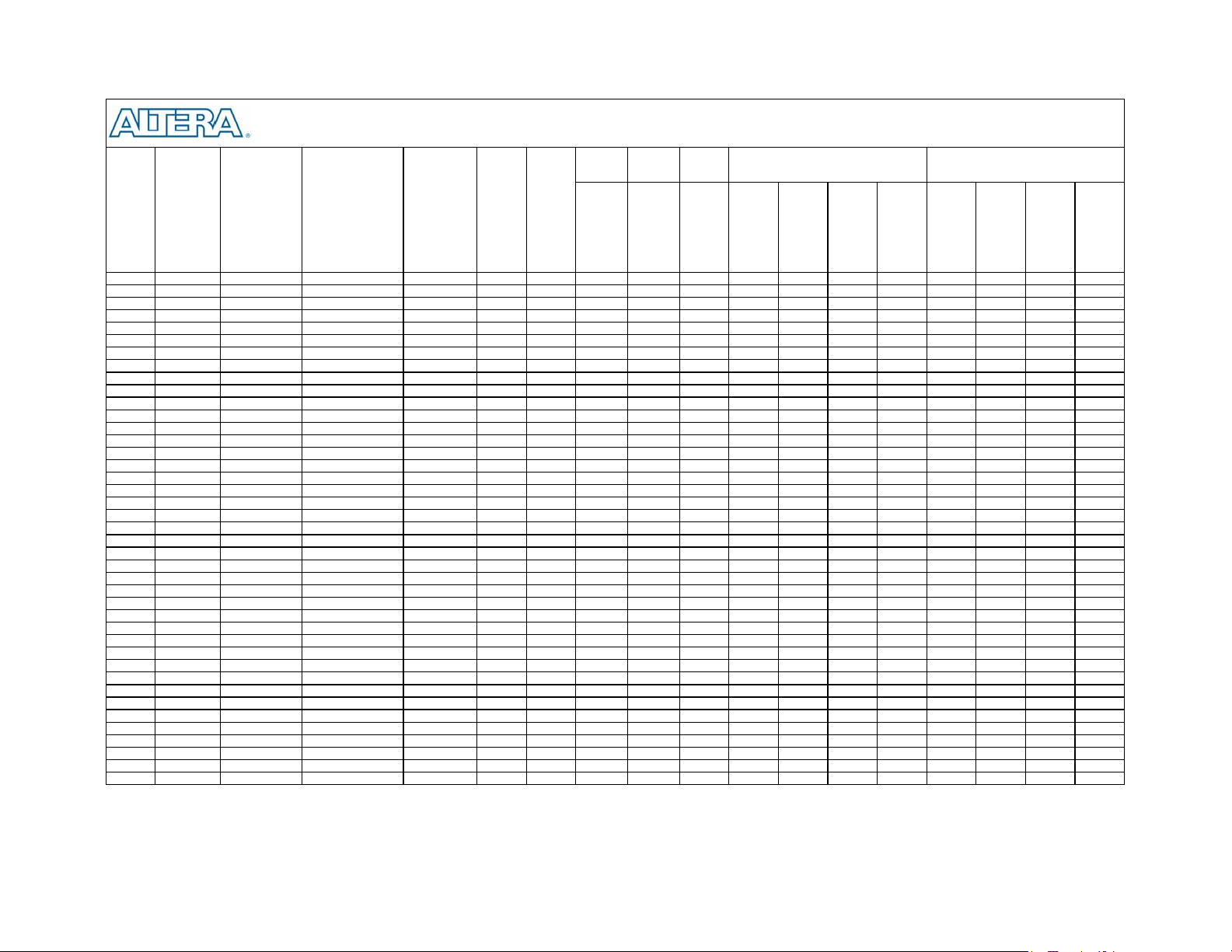

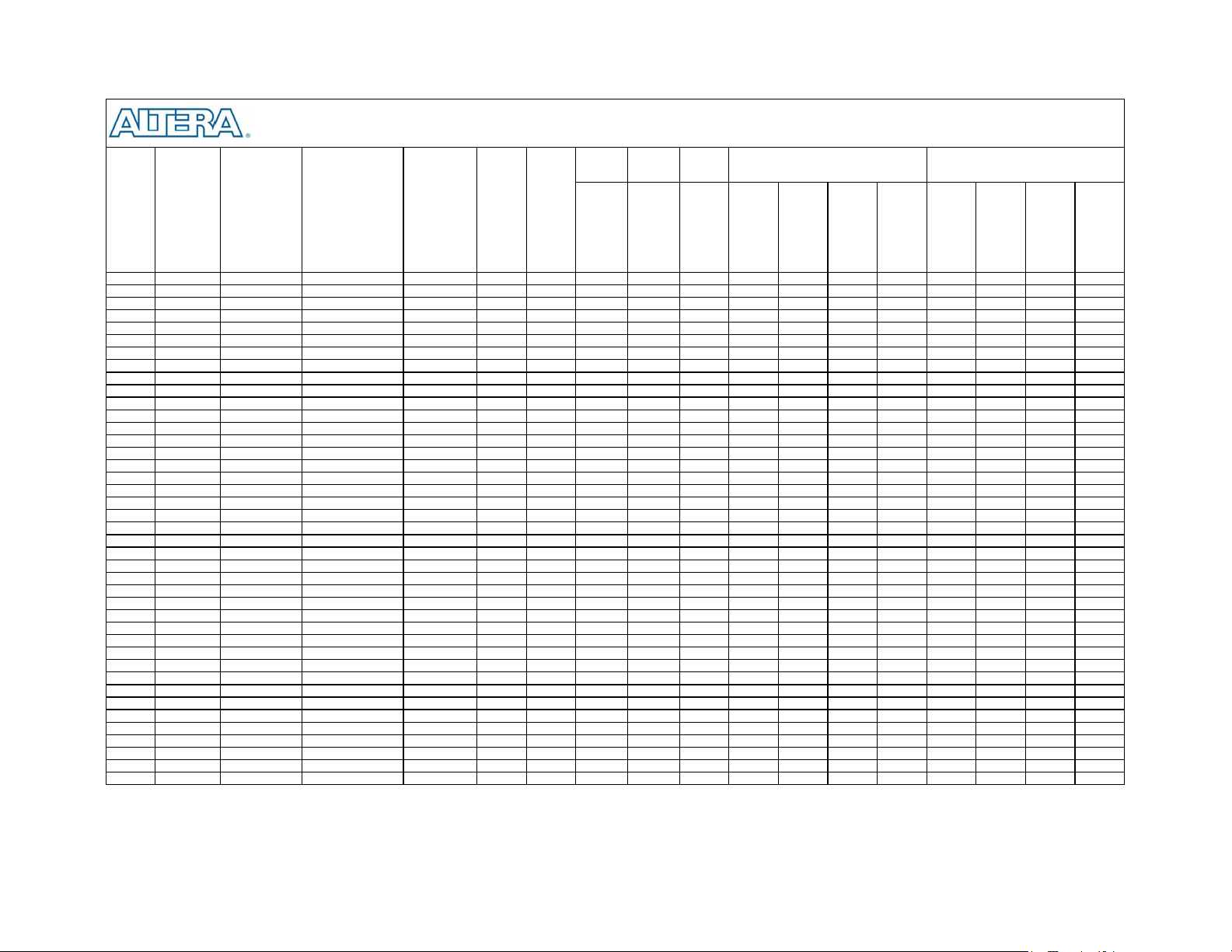

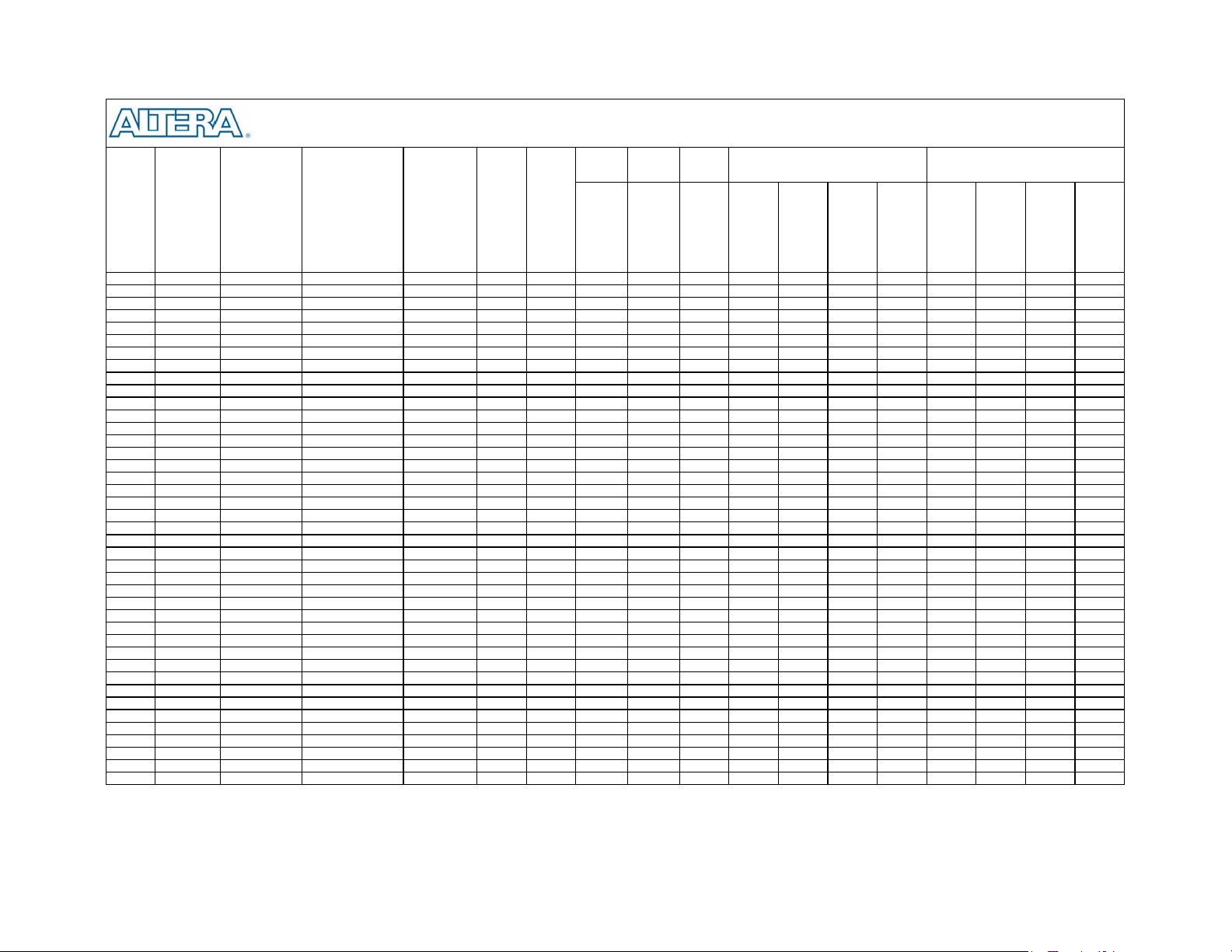

Page 3

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 3 of 47

ersion 1.5

Number

B2 VREFB2N1 IO DIFFIO_RX39p M39 L32 DQ6L0 DQ6L0 DQ2L3 DQ2L3 DQ6L0 DQ7L1 DQ2L3 DQ3L2

B2 VREFB2N1 IO DIFFIO_RX39n M38 L31 DQ6L1 DQ6L1 DM2L DM2L DQ6L1 DQS7L DQ3L3

B2 VREFB2N1 IO DIFFIO_TX39p T25 N23 DQS24L DQS24L DQS24L DQ29L2

B2 VREFB2N1 IO DIFFIO_TX39n T24 P23 DQ24L2 DQ24L2 DQ24L2 DQ29L3

B2 VREFB2N2 IO DIFFIO_RX38p N38 L34 DQS6L DQS6L DQ3L0 DQ3L0 DQS6L DQ7L2 DQ3L0 DQ4L0

B2 VREFB2N2 IO DIFFIO_RX38n N37 K34 DQ6L2 DQ6L2 DQ3L1 DQ3L1 DQ6L2 DQ7L3 DQ3L1 DQ4L1

B2 VREFB2N2 IO DIFFIO_TX38p T27 N29 DQ24L3 DQ24L3 DQ24L3 DQ30L0

B2 VREFB2N2 IO DIFFIO_TX38n U27 N28 DM24L DM24L DQ30L1

B2 VREFB2N2 IO DIFFIO_RX37p N39 M32 DQ6L3 DQ6L3 DQS3L DQS3L DQ6L3 DQ8L0 DQS3L DQS4L

B2 VREFB2N2 IO DIFFIO_RX37n P39 M31 DM6L DM6L DQ3L2 DQ3L2 DQ8L1 DQ3L2 DQ4L2

B2 VREFB2N2 IO DIFFIO_TX37p U25 P29 DQ25L0 DQ25L0 DQ25L0 DQS30L

B2 VREFB2N2 IO DIFFIO_TX37n V26 P28 DQ25L1 DQ25L1 DQ25L1 DQ30L2

B2 VREFB2N2 IO DIFFIO_RX36p R35 M34 DQ7L0 DQ7L0 DQ3L3 DQ3L3 DQ7L0 DQS8L DQ3L3 DQ4L3

B2 VREFB2N2 IO DIFFIO_RX36n R34 M33 DQ7L1 DQ7L1 DM3L DM3L DQ7L1 DQ8L2 DQ5L0

B2 VREFB2N2 IO DIFFIO_TX36p V25 R29 DQS25L DQS25L DQ16L0 DQ16L0 DQS25L DQ30L3 DQ16L0

B2 VREFB2N2 IO DIFFIO_TX36n W25 R28 DQ25L2 DQ25L2 DQ16L1 DQ16L1 DQ25L2 DQ31L0 DQ16L1

B2 VREFB2N2 IO DIFFIO_RX35p T35 N31 DQS7L DQS7L DQ4L0 DQ4L0 DQS7L DQ8L3 DQ4L0 DQ5L1

B2 VREFB2N2 IO DIFFIO_RX35n T34 N30 DQ7L2 DQ7L2 DQ4L1 DQ4L1 DQ7L2 DQ9L0 DQ4L1 DQS5L

B2 VREFB2N2 IO DIFFIO_TX35p V31 R23 DQ25L3 DQ25L3 DQS16L DQS16L DQ25L3 DQ31L1 DQS16L

B2 VREFB2N2 IO DIFFIO_TX35n U30 T23 DM25L DM25L DQ16L2 DQ16L2 DQS31L DQ16L2

B2 VREFB2N2 IO DIFFIO_RX34p P37 N33 DQ7L3 DQ7L3 DQS4L DQS4L DQ7L3 DQ9L1 DQS4L DQ5L2

B2 VREFB2N2 IO DIFFIO_RX34n P36 N32 DM7L DM7L DQ4L2 DQ4L2 DQS9L DQ4L2 DQ5L3

B2 VREFB2N2 IO DIFFIO_TX34p W27 T29 DQ26L0 DQ26L0 DQ16L3 DQ16L3 DQ26L0 DQ31L2 DQ16L3

B2 VREFB2N2 IO DIFFIO_TX34n W26 T28 DQ26L1 DQ26L1 DM16L DM16L DQ26L1 DQ31L3

B2 VREFB2N2 VREFB2N2 VREFB2N2 M35 K31

B2 VREFB2N2 IO DIFFIO_RX33p R37 P32 DQ8L0 DQ8L0 DQ4L3 DQ4L3 DQ8L0 DQ9L2 DQ4L3 DQ6L0

B2 VREFB2N2 IO DIFFIO_RX33n R36 P31 DQ8L1 DQ8L1 DM4L DM4L DQ8L1 DQ9L3 DQ6L1

B2 VREFB2N2 IO DIFFIO_TX33p V28 U24 DQS26L DQS26L DQ17L0 DQ17L0 DQS26L DQ32L0 DQ17L0 DQ20L0

B2 VREFB2N2 IO DIFFIO_TX33n V27 U23 DQ26L2 DQ26L2 DQ17L1 DQ17L1 DQ26L2 DQ32L1 DQ17L1 DQ20L1

B2 VREFB2N2 IO DIFFIO_RX32p R39 N34 DQS8L DQS8L DQ5L0 DQ5L0 DQS8L DQ10L0 DQ5L0 DQS6L

B2 VREFB2N2 IO DIFFIO_RX32n R38 P34 DQ8L2 DQ8L2 DQ5L1 DQ5L1 DQ8L2 DQ10L1 DQ5L1 DQ6L2

B2 VREFB2N2 IO DIFFIO_TX32p V35 U31 DQ26L3 DQ26L3 DQS17L DQS17L DQ26L3 DQS32L DQS17L DQS20L

B2 VREFB2N2 IO DIFFIO_TX32n V34 U30 DM26L DM26L DQ17L2 DQ17L2 DQ32L2 DQ17L2 DQ20L2

B2 VREFB2N2 IO DIFFIO_RX31p U37 R32 DQ8L3 DQ8L3 DQS5L DQS5L DQ8L3 DQS10L DQS5L DQ6L3

B2 VREFB2N2 IO DIFFIO_RX31n U36 R31 DM8L DM8L DQ5L2 DQ5L2 DQ10L2 DQ5L2 DQ7L0

B2 VREFB2N2 IO DIFFIO_TX31p V33 U29 DQ27L0 DQ27L0 DQ17L3 DQ17L3 DQ27L0 DQ32L3 DQ17L3 DQ20L3

B2 VREFB2N2 IO DIFFIO_TX31n V32 U28 DQ27L1 DQ27L1 DM17L DM17L DQ27L1 DQ33L0 DQ21L0

B2 VREFB2N2 IO DIFFIO_RX30p T38 R34 DQ5L3 DQ5L3 DQ10L3 DQ5L3 DQ7L1

B2 VREFB2N2 IO DIFFIO_RX30n T37 R33 DM5L DM5L DQS7L

B2 VREFB2N2 IO DIFFIO_TX30p W34 W29 DQS27L DQS27L DQ18L0 DQ18L0 DQS27L DQ33L1 DQ18L0 DQ21L1

B2 VREFB2N2 IO DIFFIO_TX30n W33 V29 DQ27L2 DQ27L2 DQ18L1 DQ18L1 DQ27L2 DQS33L DQ18L1 DQS21L

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

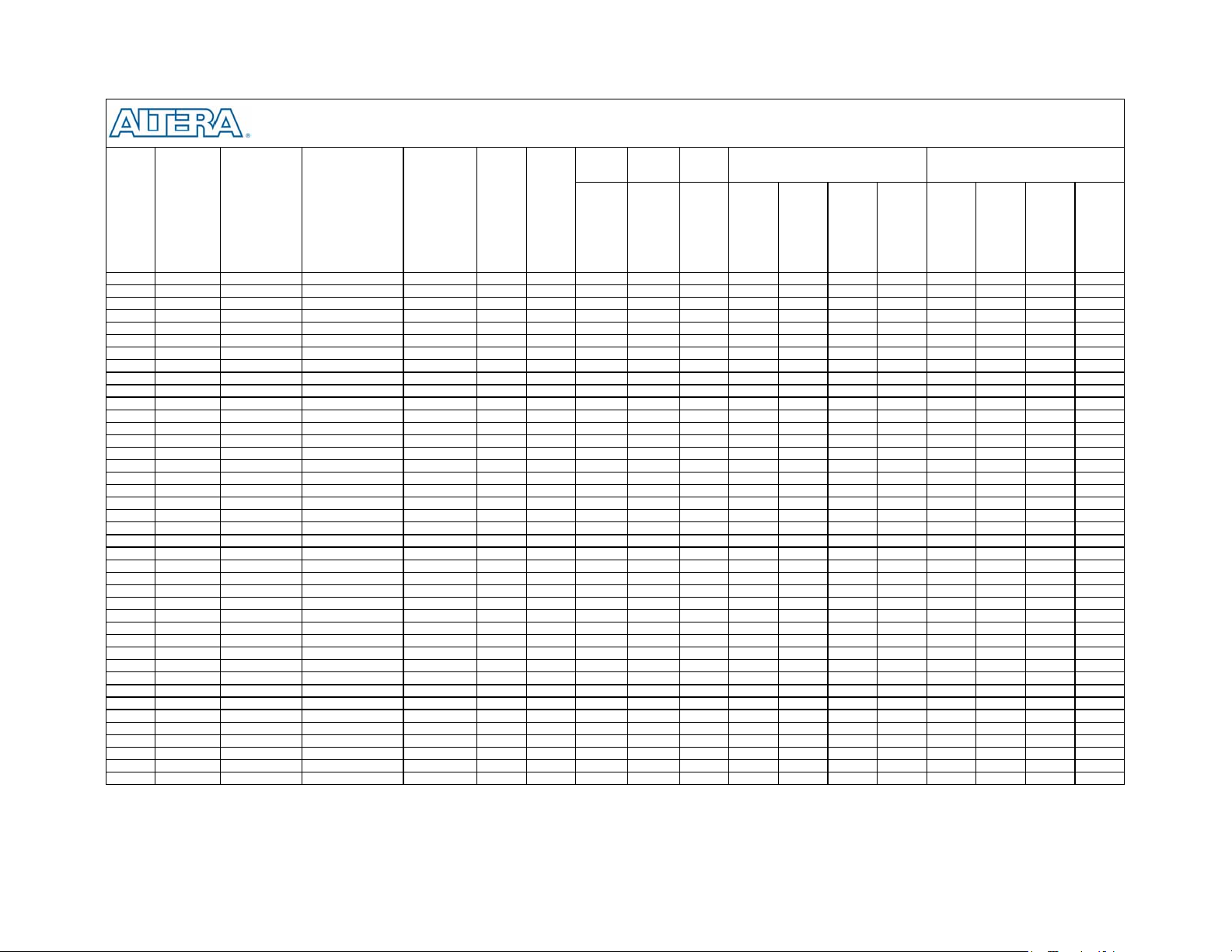

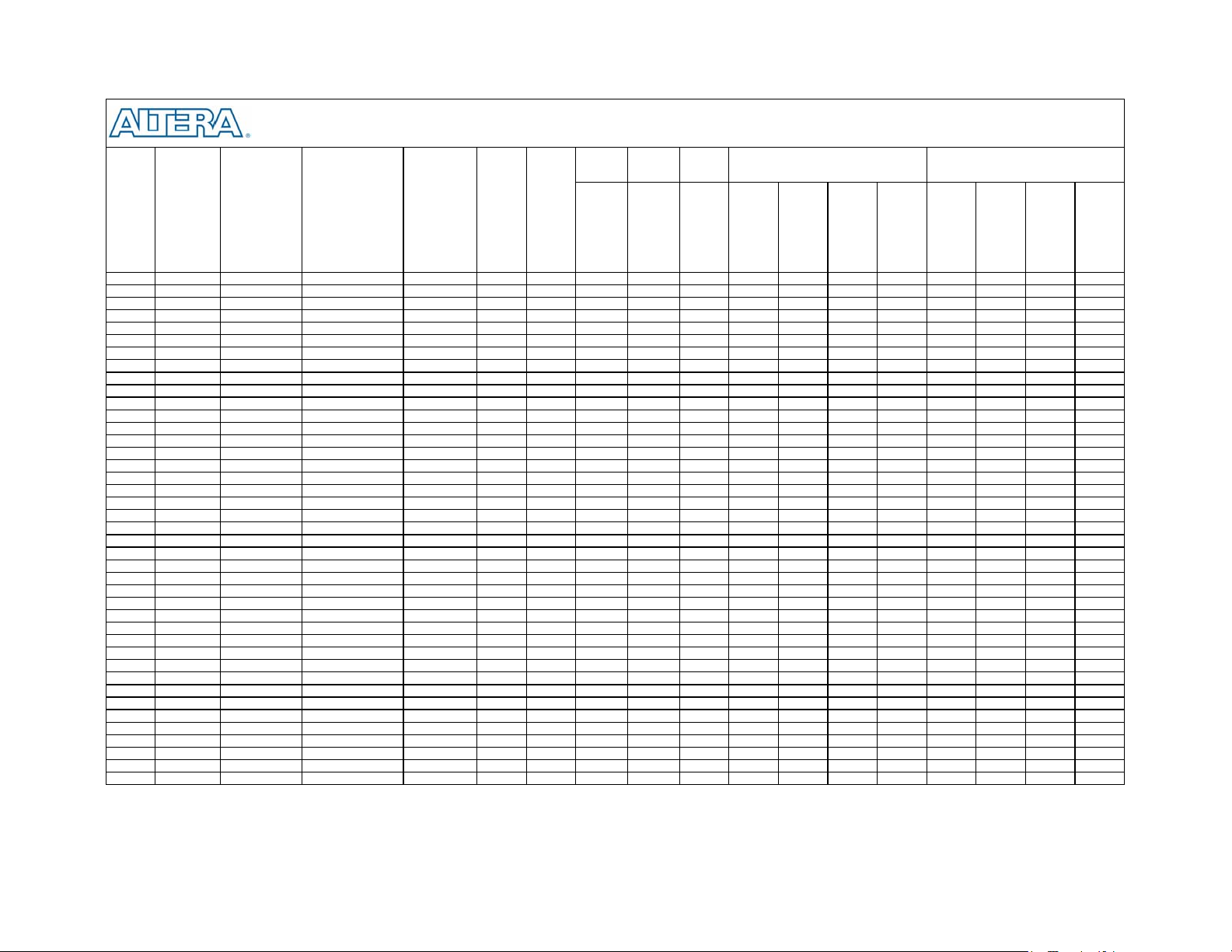

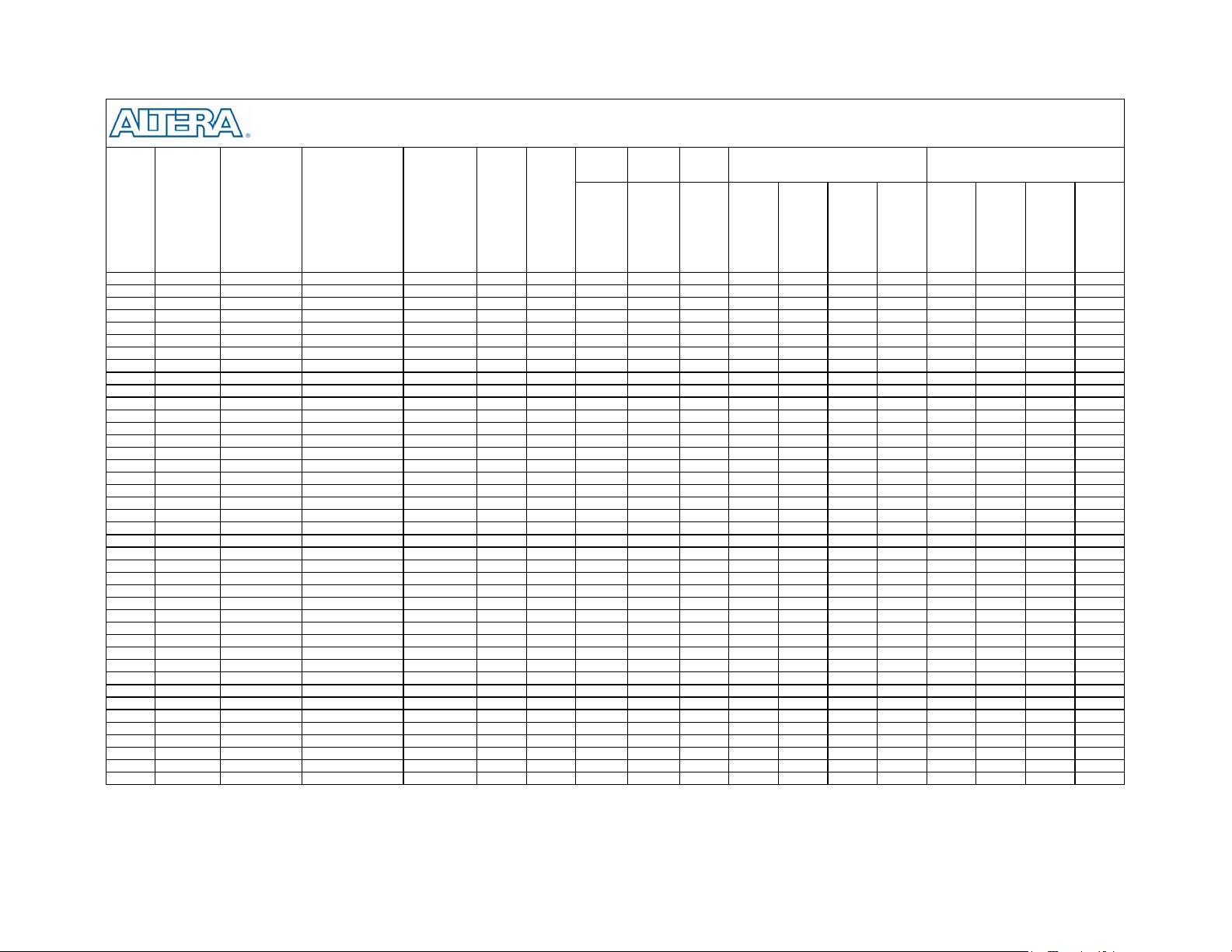

Page 4

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 4 of 47

ersion 1.5

Number

B2 VREFB2N2 IO DIFFIO_RX29p U39 T32 DQS18L DQS18L DQS18L DQ7L2

B2 VREFB2N2 IO DIFFIO_RX29n T39 T31 DQ18L2 DQ18L2 DQ18L2 DQ7L3

B2 VREFB2N2 IO DIFFIO_TX29p W32 U27 DQ27L3 DQ27L3 DQ18L3 DQ18L3 DQ27L3 DQ33L2 DQ18L3 DQ21L2

B2 VREFB2N2 IO DIFFIO_TX29n Y31 V28 DM27L DM27L DM18L DM18L DQ33L3 DQ21L3

B2 VREFB2N2 IO CLK0n/DIFFIO_RX_C0n V38 T34

B2 VREFB2N2 IO CLK0p/DIFFIO_RX_C0p V39 U34

B2 VREFB2N2 CLK1n INPUT V36 U32

B2 VREFB2N2 CLK1p INPUT V37 U33

B1 VREFB1N0 IO CLK2p/DIFFIO_RX_C1p W39 W34

B1 VREFB1N0 IO CLK2n/DIFFIO_RX_C1n W38 V34

B1 VREFB1N0 CLK3p INPUT W37 V32

B1 VREFB1N0 CLK3n INPUT W36 V31

B1 VREFB1N0 IO DIFFIO_RX28p Y37 W31 DQ9L0 DQ9L0 DQ6L0 DQ6L0 DQ9L0 DQ11L0 DQ6L0 DQ8L0

B1 VREFB1N0 IO DIFFIO_RX28n Y36 W30 DQ9L1 DQ9L1 DQ6L1 DQ6L1 DQ9L1 DQ11L1 DQ6L1 DQ8L1

B1 VREFB1N0 IO DIFFIO_TX28p Y25 V23 DQ28L0 DQ28L0 DQ19L0 DQ19L0 DQ28L0 DQ34L0 DQ19L0

B1 VREFB1N0 IO DIFFIO_TX28n AA25 W23 DQ28L1 DQ28L1 DQ19L1 DQ19L1 DQ28L1 DQ34L1 DQ19L1

B1 VREFB1N0 IO DIFFIO_RX27p AA39 W33 DQS9L DQS9L DQS6L DQS6L DQS9L DQS11L DQS6L DQS8L

B1 VREFB1N0 IO DIFFIO_RX27n Y39 W32 DQ9L2 DQ9L2 DQ6L2 DQ6L2 DQ9L2 DQ11L2 DQ6L2 DQ8L2

B1 VREFB1N0 IO DIFFIO_TX27p Y27 Y24 DQS28L DQS28L DQS19L DQS19L DQS28L DQS34L DQS19L

B1 VREFB1N0 IO DIFFIO_TX27n AA26 Y23 DQ28L2 DQ28L2 DQ19L2 DQ19L2 DQ28L2 DQ34L2 DQ19L2

B1 VREFB1N0 IO DIFFIO_RX26p AA38 Y32 DQ9L3 DQ9L3 DQ6L3 DQ6L3 DQ9L3 DQ11L3 DQ6L3 DQ8L3

B1 VREFB1N0 IO DIFFIO_RX26n AA37 Y31 DM9L DM9L DM6L DM6L DQ12L0 DQ9L0

B1 VREFB1N0 IO DIFFIO_TX26p AA27 W28 DQ28L3 DQ28L3 DQ19L3 DQ19L3 DQ28L3 DQ34L3 DQ19L3

B1 VREFB1N0 IO DIFFIO_TX26n AB27 Y29 DM28L DM28L DM19L DM19L DQ35L0

B1 VREFB1N0 IO DIFFIO_RX25p AA35 Y34 DQ10L0 DQ10L0 DQ7L0 DQ7L0 DQ10L0 DQ12L1 DQ7L0 DQ9L1

B1 VREFB1N0 IO DIFFIO_RX25n AA34 Y33 DQ10L1 DQ10L1 DQ7L1 DQ7L1 DQ10L1 DQS12L DQ7L1 DQS9L

B1 VREFB1N0 IO DIFFIO_TX25p Y34 Y28 DQ29L0 DQ29L0 DQ20L0 DQ20L0 DQ29L0 DQ35L1 DQ20L0

B1 VREFB1N0 IO DIFFIO_TX25n Y33 Y27 DQ29L1 DQ29L1 DQ20L1 DQ20L1 DQ29L1 DQS35L DQ20L1

B1 VREFB1N0 VREFB1N0 VREFB1N0 AH35 AE31

B1 VREFB1N0 IO DIFFIO_RX24p AB39 AA32 DQS10L DQS10L DQS7L DQS7L DQS10L DQ12L2 DQS7L DQ9L2

B1 VREFB1N0 IO DIFFIO_RX24n AB38 AA31 DQ10L2 DQ10L2 DQ7L2 DQ7L2 DQ10L2 DQ12L3 DQ7L2 DQ9L3

B1 VREFB1N0 IO DIFFIO_TX24p AA32 AA29 DQS29L DQS29L DQS20L DQS20L DQS29L DQ35L2 DQS20L

B1 VREFB1N0 IO DIFFIO_TX24n AA31 AA28 DQ29L2 DQ29L2 DQ20L2 DQ20L2 DQ29L2 DQ35L3 DQ20L2

VREF Group Pin

Name/Function

VCCD_PLL1 W28 R27

VCCA_PLL1 V30 T25

GNDA_PLL1 W30 T26

GNDA_PLL1 W29 R26

GNDA_PLL2 Y28 W26

GNDA_PLL2 AA29 V26

VCCA_PLL2 Y30 V25

VCCD_PLL2 AA28 W27

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 5

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 5 of 47

ersion 1.5

Number

B1 VREFB1N0 IO DIFFIO_RX23p AB37 AB31 DQ10L3 DQ10L3 DQ7L3 DQ7L3 DQ10L3 DQ13L0 DQ7L3 DQ10L0

B1 VREFB1N0 IO DIFFIO_RX23n AB36 AB30 DM10L DM10L DM7L DM7L DQ13L1 DQ10L1

B1 VREFB1N0 IO DIFFIO_TX23p AB25 AA23 DQ29L3 DQ29L3 DQ20L3 DQ20L3 DQ29L3 DQ36L0 DQ20L3

B1 VREFB1N0 IO DIFFIO_TX23n AC25 AB23 DM29L DM29L DM20L DM20L DQ36L1

B1 VREFB1N0 IO DIFFIO_RX22p AB35 AB33 DQ11L0 DQ11L0 DQ8L0 DQ8L0 DQ11L0 DQS13L DQ8L0 DQS10L

B1 VREFB1N0 IO DIFFIO_RX22n AB34 AB32 DQ11L1 DQ11L1 DQ8L1 DQ8L1 DQ11L1 DQ13L2 DQ8L1 DQ10L2

B1 VREFB1N0 IO DIFFIO_TX22p AB26 AA26 DQ30L0 DQ30L0 DQ21L0 DQ21L0 DQ30L0 DQS36L DQ21L0 DQ22L0

B1 VREFB1N0 IO DIFFIO_TX22n AC27 AA25 DQ30L1 DQ30L1 DQ21L1 DQ21L1 DQ30L1 DQ36L2 DQ21L1 DQ22L1

B1 VREFB1N0 IO DIFFIO_RX21p AC37 AA34 DQS11L DQS11L DQS8L DQS8L DQS11L DQ13L3 DQS8L DQ10L3

B1 VREFB1N0 IO DIFFIO_RX21n AC36 AB34 DQ11L2 DQ11L2 DQ8L2 DQ8L2 DQ11L2 DQ14L0 DQ8L2 DQ11L0

B1 VREFB1N0 IO DIFFIO_TX21p AB30 AB29 DQS30L DQS30L DQS21L DQS21L DQS30L DQ36L3 DQS21L DQS22L

B1 VREFB1N0 IO DIFFIO_TX21n AB29 AB28 DQ30L2 DQ30L2 DQ21L2 DQ21L2 DQ30L2 DQ37L0 DQ21L2 DQ22L2

B1 VREFB1N0 IO DIFFIO_RX20p AC39 AC32 DQ11L3 DQ11L3 DQ8L3 DQ8L3 DQ11L3 DQ14L1 DQ8L3 DQ11L1

B1 VREFB1N0 IO DIFFIO_RX20n AD39 AC31 DM11L DM11L DM8L DM8L DQS14L DQS11L

B1 VREFB1N0 IO DIFFIO_TX20p AB32 AB24 DQ30L3 DQ30L3 DQ21L3 DQ21L3 DQ30L3 DQ37L1 DQ21L3 DQ22L3

B1 VREFB1N0 IO DIFFIO_TX20n AB31 AC24 DM30L DM30L DM21L DM21L DQS37L DQ23L0

B1 VREFB1N1 IO DIFFIO_RX19p AD35 AC34 DQ12L0 DQ12L0 DQ9L0 DQ9L0 DQ12L0 DQ14L2 DQ9L0 DQ11L2

B1 VREFB1N1 IO DIFFIO_RX19n AD34 AC33 DQ12L1 DQ12L1 DQ9L1 DQ9L1 DQ12L1 DQ14L3 DQ9L1 DQ11L3

B1 VREFB1N1 IO DIFFIO_TX19p AA33 AB26 DQ31L0 DQ31L0 DQ22L0 DQ22L0 DQ31L0 DQ37L2 DQ22L0 DQ23L1

B1 VREFB1N1 IO DIFFIO_TX19n AB33 AB25 DQ31L1 DQ31L1 DQ22L1 DQ22L1 DQ31L1 DQ37L3 DQ22L1 DQS23L

B1 VREFB1N1 IO DIFFIO_RX18p AD38 AD32 DQS12L DQS12L DQS9L DQS9L DQS12L DQ15L0 DQS9L DQ12L0

B1 VREFB1N1 IO DIFFIO_RX18n AD37 AD31 DQ12L2 DQ12L2 DQ9L2 DQ9L2 DQ12L2 DQ15L1 DQ9L2 DQ12L1

B1 VREFB1N1 IO DIFFIO_TX18p AD26 AC27 DQS31L DQS31L DQS31L DQ38L0

B1 VREFB1N1 IO DIFFIO_TX18n AD25 AB27 DQ31L2 DQ31L2 DQ31L2 DQ38L1

B1 VREFB1N1 IO DIFFIO_RX17p AE39 AE33 DQ12L3 DQ12L3 DQ9L3 DQ9L3 DQ12L3 DQS15L DQ9L3 DQS12L

B1 VREFB1N1 IO DIFFIO_RX17n AE38 AE32 DM12L DM12L DM9L DM9L DQ15L2 DQ12L2

B1 VREFB1N1 IO DIFFIO_TX17p AE27 AD26 DQ31L3 DQ31L3 DQ22L3 DQ22L3 DQ31L3 DQS38L DQ22L3 DQ24L0

B1 VREFB1N1 IO DIFFIO_TX17n AE26 AD25 DM31L DM31L DM22L DM22L DQ38L2 DQ24L1

B1 VREFB1N1 IO DIFFIO_RX16p AE37 AD34 DQ13L0 DQ13L0 DQ10L0 DQ10L0 DQ13L0 DQ15L3 DQ10L0 DQ12L3

B1 VREFB1N1 IO DIFFIO_RX16n AE36 AE34 DQ13L1 DQ13L1 DQ10L1 DQ10L1 DQ13L1 DQ16L0 DQ10L1 DQ13L0

B1 VREFB1N1 IO DIFFIO_TX16p AC34 AC29 DQ32L0 DQ32L0 DQ23L0 DQ23L0 DQ32L0 DQ38L3 DQ23L0 DQS24L

B1 VREFB1N1 IO DIFFIO_TX16n AC33 AC28 DQ32L1 DQ32L1 DQ23L1 DQ23L1 DQ32L1 DQ39L0 DQ23L1 DQ24L2

B1 VREFB1N1 IO DIFFIO_RX15p AF39 AF32 DQS13L DQS13L DQS10L DQS10L DQS13L DQ16L1 DQS10L DQ13L1

B1 VREFB1N1 IO DIFFIO_RX15n AG39 AF31 DQ13L2 DQ13L2 DQ10L2 DQ10L2 DQ13L2 DQS16L DQ10L2 DQS13L

B1 VREFB1N1 IO DIFFIO_TX15p AC30 AD29 DQS32L DQS32L DQS22L DQS22L DQS32L DQ39L1 DQS22L DQ23L2

B1 VREFB1N1 IO DIFFIO_TX15n AD30 AD28 DQ32L2 DQ32L2 DQ22L2 DQ22L2 DQ32L2 DQS39L DQ22L2 DQ23L3

B1 VREFB1N1 VREFB1N1 VREFB1N1 AD36 AC30

B1 VREFB1N1 IO DIFFIO_RX14p AE35 AF34 DQ13L3 DQ13L3 DQ13L3 DQ16L2

B1 VREFB1N1 IO DIFFIO_RX14n AE34 AF33 DM13L DM13L DQ16L3

B1 VREFB1N1 IO DIFFIO_TX14p AD32 AE30 DQ32L3 DQ32L3 DQ23L3 DQ23L3 DQ32L3 DQ39L2 DQ23L3 DQ25L1

B1 VREFB1N1 IO DIFFIO_TX14n AD31 AE29 DM32L DM32L DM23L DM23L DQ39L3 DQS25L

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 6

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 6 of 47

ersion 1.5

Number

B1 VREFB1N1 IO DIFFIO_RX13p AF37 AG32 DQ14L0 DQ14L0 DQ14L0 DQ17L0

B1 VREFB1N1 IO DIFFIO_RX13n AF36 AG31 DQ14L1 DQ14L1 DQ14L1 DQ17L1

B1 VREFB1N1 IO DIFFIO_TX13p AD33 AE28 DQ33L0 DQ33L0 DQ24L0 DQ24L0 DQ33L0 DQ40L0 DQ24L0 DQ25L2

B1 VREFB1N1 IO DIFFIO_TX13n AE33 AE27 DQ33L1 DQ33L1 DQ24L1 DQ24L1 DQ33L1 DQ40L1 DQ24L1 DQ25L3

B1 VREFB1N1 IO DIFFIO_RX12p AG38 AG34 DQS14L DQS14L DQS11L DQS11L DQS14L DQS17L DQS11L DQS14L

B1 VREFB1N1 IO DIFFIO_RX12n AG37 AH34 DQ14L2 DQ14L2 DQ11L2 DQ11L2 DQ14L2 DQ17L2 DQ11L2 DQ14L2

B1 VREFB1N1 IO DIFFIO_TX12p AD27 AF30 DQS33L DQS33L DQS23L DQS23L DQS33L DQS40L DQS23L DQ24L3

B1 VREFB1N1 IO DIFFIO_TX12n AE28 AF29 DQ33L2 DQ33L2 DQ23L2 DQ23L2 DQ33L2 DQ40L2 DQ23L2 DQ25L0

B1 VREFB1N1 IO DIFFIO_RX11p AG36 AH33 DQ14L3 DQ14L3 DQ10L3 DQ10L3 DQ14L3 DQ17L3 DQ10L3 DQ13L2

B1 VREFB1N1 IO DIFFIO_RX11n AG35 AH32 DM14L DM14L DM10L DM10L DQ18L0 DQ13L3

B1 VREFB1N1 IO DIFFIO_TX11p AE32 AF28 DQ33L3 DQ33L3 DQ24L3 DQ24L3 DQ33L3 DQ40L3 DQ24L3 DQS26L

B1 VREFB1N1 IO DIFFIO_TX11n AE31 AF27 DM33L DM33L DM24L DM24L DQ41L0 DQ26L2

B1 VREFB1N1 IO DIFFIO_RX10p AH39 AJ34 DQ15L0 DQ15L0 DQ25L0 DQ25L0 DQ15L0 DQ18L1 DQ25L0 DQ15L1

B1 VREFB1N1 IO DIFFIO_RX10n AH38 AJ33 DQ15L1 DQ15L1 DQ25L1 DQ25L1 DQ15L1 DQS18L DQ25L1 DQS15L

B1 VREFB1N1 IO DIFFIO_TX10p AF34 AG29 DQ34L0 DQ34L0 DQS24L DQS24L DQ34L0 DQ41L1 DQS24L DQ26L0

B1 VREFB1N1 IO DIFFIO_TX10n AF33 AG28 DQ34L1 DQ34L1 DQ24L2 DQ24L2 DQ34L1 DQS41L DQ24L2 DQ26L1

B1 VREFB1N2 IO DIFFIO_RX9p AH37 AJ32 DQS15L DQS15L DQ11L0 DQ11L0 DQS15L DQ18L2 DQ11L0 DQ14L0

B1 VREFB1N2 IO DIFFIO_RX9n AH36 AJ31 DQ15L2 DQ15L2 DQ11L1 DQ11L1 DQ15L2 DQ18L3 DQ11L1 DQ14L1

B1 VREFB1N2 IO DIFFIO_TX9p AE30 AH31 DQS34L DQS34L DQS25L DQS25L DQS34L DQ41L2 DQS25L DQ26L3

B1 VREFB1N2 IO DIFFIO_TX9n AE29 AH30 DQ34L2 DQ34L2 DQ25L2 DQ25L2 DQ34L2 DQ41L3 DQ25L2 DQ27L0

B1 VREFB1N2 IO DIFFIO_RX8p AJ39 AL34 DQ15L3 DQ15L3 DQ11L3 DQ11L3 DQ15L3 DQ19L0 DQ11L3 DQ14L3

B1 VREFB1N2 IO DIFFIO_RX8n AK39 AK34 DM15L DM15L DM11L DM11L DQ19L1 DQ15L0

B1 VREFB1N2 IO DIFFIO_TX8p AF28 AH29 DQ34L3 DQ34L3 DQ34L3 DQ27L1

B1 VREFB1N2 IO DIFFIO_TX8n AF27 AH28 DM34L DM34L DQS27L

B1 VREFB1N2 IO DIFFIO_RX7p AJ37 AK32 DQ16L0 DQ25L3 DQ25L3 DQ16L0 DQS19L DQ25L3 DQ15L2

B1 VREFB1N2 IO DIFFIO_RX7n AJ36 AK31 DQ16L1 DM25L DM25L DQ16L1 DQ19L2 DQ15L3

B1 VREFB1N2 IO DIFFIO_TX7p AG34 AJ30 DQ35L0 DQ35L0 DQ27L2

B1 VREFB1N2 IO DIFFIO_TX7n AG33 AJ29 DQ35L1 DQ35L1 DQ27L3

B1 VREFB1N2 IO DIFFIO_RX6p AK38 AL33 DQS16L DQS16L DQ19L3

B1 VREFB1N2 IO DIFFIO_RX6n AK37 AL32 DQ16L2 DQ16L2

B1 VREFB1N2 IO DIFFIO_TX6p AF30 DQS35L DQS35L

B1 VREFB1N2 IO DIFFIO_TX6n AG30 DQ35L2 DQ35L2

B1 VREFB1N2 IO DIFFIO_RX5p AL39 DQ16L3 DQ16L3

B1 VREFB1N2 IO DIFFIO_RX5n AL38 DM16L

B1 VREFB1N2 IO DIFFIO_TX5p AG32 DQ35L3 DQ35L3

B1 VREFB1N2 IO DIFFIO_TX5n AG31 DM35L

B1 VREFB1N2 VREFB1N2 VREFB1N2 AA36 Y30

B1 VREFB1N2 IO DIFFIO_RX4p AK36 DQ17L0 DQ17L0

B1 VREFB1N2 IO DIFFIO_RX4n AK35 DQ17L1 DQ17L1

B1 VREFB1N2 IO DIFFIO_TX4p AH34 DQ36L0 DQ36L0

B1 VREFB1N2 IO DIFFIO_TX4n AH33 DQ36L1 DQ36L1

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 7

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 7 of 47

ersion 1.5

Number

B1 VREFB1N2 IO DIFFIO_RX3p AN39 DQS17L DQS17L

B1 VREFB1N2 IO DIFFIO_RX3n AM39 DQ17L2 DQ17L2

B1 VREFB1N2 IO DIFFIO_TX3p AJ34 DQS36L DQS36L

B1 VREFB1N2 IO DIFFIO_TX3n AJ33 DQ36L2 DQ36L2

B1 VREFB1N2 IO DIFFIO_RX2p AP39 DQ17L3 DQ17L3

B1 VREFB1N2 IO DIFFIO_RX2n AP38 DM17L

B1 VREFB1N2 IO DIFFIO_TX2p AK34 DQ36L3 DQ36L3

B1 VREFB1N2 IO DIFFIO_TX2n AK33 DM36L

B1 VREFB1N2 IO DIFFIO_RX1p AR39

B1 VREFB1N2 IO DIFFIO_RX1n AT39

B1 VREFB1N2 IO DIFFIO_TX1p AL34

B1 VREFB1N2 IO DIFFIO_TX1n AL33

B1 VREFB1N2 FPLL8CLKn INPUT AU38 AM33

B1 VREFB1N2 FPLL8CLKp INPUT AU39 AM34

B1 VREFB1N2 IO DIFFIO_TX0p AM34

B1 VREFB1N2 IO DIFFIO_TX0n AM33

B8 VREFB8N0 TDI TDI AP34 AL31

B8 VREFB8N0 TMS TMS AP33 AM32

B8 VREFB8N0 TCK TCK AU35 AL30

B8 VREFB8N0 TRST TRST AP32 AM31

B8 VREFB8N0 nCONFIG nCONFIG AR34 AE24

B8 VREFB8N0 VCCSEL VCCSEL AT34 AF24

B8 VREFB8N0 IO AN31 AK29 DQ0B0 DQ0B0 DQ0B0 DQ0B0

B8 VREFB8N0 IO AP31 DQ0B1 DQ0B1

B8 VREFB8N0 IO CS AR33 AH27

B8 VREFB8N0 IO CLKUSR AT33 AH26

B8 VREFB8N0 IO nWS AU34 AG26

B8 VREFB8N0 IO nRS AT32 AG25

B8 VREFB8N0 IO AH28 AC23 DQS0B DQ0B1 DQS0B DQ0B1

B8 VREFB8N0 IO AP30 AH25 DQ0B2 DQS0B DQ0B2 DQS0B

B8 VREFB8N0 IO AN30 DQ0B3 DQ0B3

B8 VREFB8N0 IO AT31 AL29 DM0B DQ0B2 DQ0B2

B8 VREFB8N0 VREFB8N0 VREFB8N0 AR27 AK28

B8 VREFB8N0 IO AH27 AB22 DQ1B0 DQ0B3 DQ1B0 DQ0B3

B8 VREFB8N0 IO AJ27 DQ1B1 DQ1B1

B8 VREFB8N0 IO DQ17B AW37 AM30 DQ8B8 DQS1B DM0B DQ17B3 DQS1B DQ1B0 DQ17B3

B8 VREFB8N0 IO DQSn17B AV36 AN31 DQ8B4 DQ3B14 DQ1B33 DQ1B2 DQ1B0 DQSB17B DQ1B2 DQ1B1 DQSB17B

VREF Group Pin

Name/Function

GNDA_PLL8 AK28 AE26

GNDA_PLL8 AK29 AF25

VCCA_PLL8 AL29 AF26

VCCD_PLL8 AJ28 AE25

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 8

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 8 of 47

ersion 1.5

Number

B8 VREFB8N0 IO DQ17B AV37 AN32 DQ8B7 DQ3B17 DQ1B3 DQ1B1 DQ17B2 DQ1B3 DQS1B DQ17B2

B8 VREFB8N0 IO DQ17B AV34 AP32 DQ8B6 DQ3B16 DQ1B35 DM1B DQS1B DQ17B1 DQ1B2 DQ17B1

B8 VREFB8N0 IO DQ17B AW35 AP30 DQ8B5 DQ3B15 DQ1B34 DQ2B0 DQ1B2 DQ17B0 DQ2B0 DQ1B3 DQ17B0

B8 VREFB8N0 IO DQS17B AW36 AP31 DQVLD8B DQ2B1 DQ1B3 DQS17B DQ2B1 DQ2B0 DQS17B

B8 VREFB8N0 IO AL28 AG23 DQS2B DM1B DQS2B DQ2B1

B8 VREFB8N0 IO AN29 AD23 DQ2B2 DQ2B0 DQ2B2 DQS2B

B8 VREFB8N0 IO DQ16B AW34 AP29 DQ8B3 DQ3B13 DQ1B32 DQ2B3 DQ2B1 DQ16B3 DQ2B3 DQ2B2 DQ16B3

B8 VREFB8N0 IO DQSn16B AV33 AN29 DQSn8B DQ3B9 DQ1B28 DM2B DQS2B DQSB16B DQ2B3 DQSB16B

B8 VREFB8N0 IO DQ16B AU33 AM29 DQ8B2 DQ3B12 DQ1B31 DQ3B0 DQ2B2 DQ16B2 DQ3B0 DQ3B0 DQ16B2

B8 VREFB8N0 IO DQ16B AU32 AP28 DQ8B1 DQ3B11 DQ1B30 DQ3B1 DQ2B3 DQ16B1 DQ3B1 DQ3B1 DQ16B1

B8 VREFB8N0 IO DQ16B AW32 AM28 DQ8B0 DQ3B10 DQ1B29 DQS3B DM2B DQ16B0 DQS3B DQS3B DQ16B0

B8 VREFB8N0 IO DQS16B AW33 AN28 DQS8B DQVLD3B DQ3B2 DQ3B0 DQS16B DQ3B2 DQ3B2 DQS16B

B8 VREFB8N0 IO AH26 DQ3B3 DQ3B3

B8 VREFB8N0 IO AK27 AF23 DM3B DQ3B1 DQ3B3

B8 VREFB8N0 IO DQ15B AU31 AJ27 DQ7B8 DQ3B8 DQ1B27 DQ4B0 DQS3B DQ15B3 DQ4B0 DQ4B0 DQ15B3

B8 VREFB8N0 IO DQSn15B AV31 AL28 DQ7B4 DQSn3B DQ1B23 DQ4B1 DQ3B2 DQSB15B DQ4B1 DQ4B1 DQSB15B

B8 VREFB8N1 IO DQ15B AW31 AJ28 DQ7B7 DQ3B7 DQ1B26 DQS4B DQ3B3 DQ15B2 DQS4B DQS4B DQ15B2

B8 VREFB8N1 IO DQ15B AW30 AM27 DQ7B6 DQ3B6 DQ1B25 DQ4B2 DM3B DQ15B1 DQ4B2 DQ4B2 DQ15B1

B8 VREFB8N1 IO DQ15B AU30 AP27 DQ7B5 DQ3B5 DQ1B24 DQ4B3 DQ4B0 DQ15B0 DQ4B3 DQ4B3 DQ15B0

B8 VREFB8N1 IO DQS15B AV30 AL27 DQVLD7B DQS3B DM4B DQ4B1 DQS15B DQ5B0 DQS15B

B8 VREFB8N1 IO AG26 AE23 DQ5B0 DQS4B DQ5B0 DQ5B1

B8 VREFB8N1 IO AM28 DQ5B1 DQ5B1

B8 VREFB8N1 IO DQ14B AT29 AN26 DQ7B3 DQ3B4 DQ1B22 DQS5B DQ4B2 DQ14B3 DQS5B DQS5B DQ14B3

B8 VREFB8N1 IO DQSn14B AU29 AL26 DQSn7B DQ3B0 DQ1B18 DQ5B2 DQ4B3 DQSB14B DQ5B2 DQ5B2 DQSB14B

B8 VREFB8N1 IO DQ14B AR28 AJ26 DQ7B2 DQ3B3 DQ1B21 DQ5B3 DM4B DQ14B2 DQ5B3 DQ5B3 DQ14B2

B8 VREFB8N1 IO DQ14B AW29 AK26 DQ7B1 DQ3B2 DQ1B20 DM5B DQ5B0 DQ14B1 DQ6B0 DQ14B1

B8 VREFB8N1 IO DQ14B AT28 AP26 DQ7B0 DQ3B1 DQ1B19 DQ6B0 DQ5B1 DQ14B0 DQ6B0 DQ6B1 DQ14B0

B8 VREFB8N1 IO DQS14B AU28 AM26 DQS7B DQ6B1 DQS5B DQS14B DQ6B1 DQS6B DQS14B

B8 VREFB8N1 IO AH25 AC22 DQS6B DQ5B2 DQS6B DQ6B2

B8 VREFB8N1 IO AP29 AD22 DQ6B2 DQ5B3 DQ6B2 DQ6B3

B8 VREFB8N1 IO AL27 DQ6B3 DQ6B3

B8 VREFB8N1 IO AJ25 AG22 DM6B DM5B DQ7B0

B8 VREFB8N1 VREFB8N1 VREFB8N1 AR24 AK25

B8 VREFB8N1 IO AN28 DQ7B0 DQ7B0

B8 VREFB8N1 IO AT30 AF22 DQ7B1 DQ6B0 DQ7B1 DQ7B1

B8 VREFB8N1 IO DQ13B AT27 AJ24 DQ6B8 DQS7B DQ6B1 DQ13B3 DQS7B DQS7B DQ13B3

B8 VREFB8N1 IO DQSn13B AV28 AL25 DQ6B4 DQ2B14 DQSn1B DQ7B2 DQS6B DQSB13B DQ7B2 DQ7B2 DQSB13B

B8 VREFB8N1 IO DQ13B AW28 AJ25 DQ6B7 DQ2B17 DQ1B17 DQ7B3 DQ6B2 DQ13B2 DQ7B3 DQ7B3 DQ13B2

B8 VREFB8N1 IO DQ13B AW27 AN25 DQ6B6 DQ2B16 DQ1B16 DM7B DQ6B3 DQ13B1 DQ8B0 DQ13B1

B8 VREFB8N1 IO DQ13B AU27 AP25 DQ6B5 DQ2B15 DQ1B15 DQ8B0 DM6B DQ13B0 DQ8B0 DQ8B1 DQ13B0

B8 VREFB8N1 IO DQS13B AV27 AM25 DQVLD6B DQS1B DQ8B1 DQ7B0 DQS13B DQ8B1 DQS8B DQS13B

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 9

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 9 of 47

ersion 1.5

Number

B8 VREFB8N1 IO AM27 AE22 DQS8B DQ7B1 DQS8B DQ8B2

B8 VREFB8N1 IO AG25 DQ8B2 DQ8B2

B8 VREFB8N1 IO DQ12B AW26 AM24 DQ6B3 DQ2B13 DQ1B14 DQ8B3 DQS7B DQ12B3 DQ8B3 DQ8B3 DQ12B3

B8 VREFB8N1 IO DQSn12B AT26 AL24 DQSn6B DQ2B9 DQ1B10 DM8B DQ7B2 DQSB12B DQ9B0 DQSB12B

B8 VREFB8N1 IO DQ12B AU26 AJ23 DQ6B2 DQ2B12 DQ1B13 DQ9B0 DQ7B3 DQ12B2 DQ9B0 DQ9B1 DQ12B2

B8 VREFB8N1 IO DQ12B AR25 AK23 DQ6B1 DQ2B11 DQ1B12 DQ9B1 DM7B DQ12B1 DQ9B1 DQS9B DQ12B1

B8 VREFB8N1 IO DQ12B AP25 AP24 DQ6B0 DQ2B10 DQ1B11 DQS9B DQ8B0 DQ12B0 DQS9B DQ9B2 DQ12B0

B8 VREFB8N1 IO DQS12B AT25 AL23 DQS6B DQVLD2B DQVLD1B DQ9B2 DQ8B1 DQS12B DQ9B2 DQ9B3 DQS12B

B8 VREFB8N1 IO AF25 AB21 DQ9B3 DQS8B DQ9B3 DQ10B0

B8 VREFB8N1 IO AK25 AC21 DM9B DQ8B2 DQ10B1

B8 VREFB8N1 IO AP28 DQ10B0 DQ10B0

B8 VREFB8N1 IO AP27 AH24 DQ10B1 DQ8B3 DQ10B1 DQS10B

B8 VREFB8N2 IO AH24 AB20 DQS10B DM8B DQS10B DQ10B2

B8 VREFB8N2 IO AN27 DQ10B2 DQ10B2

B8 VREFB8N2 IO DQ11B AV25 AM23 DQ5B8 DQ2B8 DQ1B9 DQ10B3 DQ9B0 DQ11B3 DQ10B3 DQ10B3 DQ11B3

B8 VREFB8N2 IO DQSn11B AU25 AN23 DQ5B4 DQSn2B DQ1B5 DM10B DQ9B1 DQSB11B DQ11B0 DQSB11B

B8 VREFB8N2 IO DQ11B AW25 AP23 DQ5B7 DQ2B7 DQ1B8 DQ11B0 DQS9B DQ11B2 DQ11B0 DQ11B1 DQ11B2

B8 VREFB8N2 IO DQ11B AP24 AM22 DQ5B6 DQ2B6 DQ1B7 DQ11B1 DQ9B2 DQ11B1 DQ11B1 DQS11B DQ11B1

B8 VREFB8N2 IO DQ11B AT24 AP22 DQ5B5 DQ2B5 DQ1B6 DQS11B DQ9B3 DQ11B0 DQS11B DQ11B2 DQ11B0

B8 VREFB8N2 IO DQS11B AU24 AN22 DQVLD5B DQS2B DQ11B2 DM9B DQS11B DQ11B2 DQ11B3 DQS11B

B8 VREFB8N2 IO AG24 AC20 DQ11B3 DQ10B0 DQ11B3 DQ12B0

B8 VREFB8N2 IO AL25 AH21 DM11B DQ10B1 DQ12B1

B8 VREFB8N2 IO AK24 DQ12B0 DQ12B0

B8 VREFB8N2 IO AM25 AH22 DQ12B1 DQS10B DQ12B1 DQS12B

B8 VREFB8N2 IO AG23 AC19 DQS12B DQ10B2 DQS12B DQ12B2

B8 VREFB8N2 IO AN26 DQ12B2 DQ12B2

B8 VREFB8N2 IO DQ10B AV24 AJ22 DQ5B3 DQ2B4 DQ1B4 DQ12B3 DQ10B3 DQ10B3 DQ12B3 DQ12B3 DQ10B3

B8 VREFB8N2 IO DQSn10B AT23 AL22 DQSn5B DQ2B0 DQ1B0 DM12B DM10B DQSB10B DQ13B0 DQSB10B

B8 VREFB8N2 IO DQ10B AW24 AM21 DQ5B2 DQ2B3 DQ1B3 DQ13B0 DQ11B0 DQ10B2 DQ13B0 DQ13B1 DQ10B2

B8 VREFB8N2 IO DQ10B AW23 AP21 DQ5B1 DQ2B2 DQ1B2 DQ13B1 DQ11B1 DQ10B1 DQ13B1 DQS13B DQ10B1

B8 VREFB8N2 IO DQ10B AP23 AJ21 DQ5B0 DQ2B1 DQ1B1 DQS13B DQS11B DQ10B0 DQS13B DQ13B2 DQ10B0

B8 VREFB8N2 IO DQS10B AU23 AL21 DQS5B DQ13B2 DQ11B2 DQS10B DQ13B2 DQ13B3 DQS10B

B8 VREFB8N2 VREFB8N2 VREFB8N2 AR21 AK22

B8 VREFB8N2 IO AG22 AB18 DQ13B3 DQ11B3 DQ13B3

B8 VREFB8N2 IO AL24 AC18 DM13B DM11B

B8 VREFB8N2 IO AP26

B8 VREFB8N2 IO AN25 AH23

B8 VREFB8N2 IO RUnLU AL21 AH18

B8 VREFB8N2 IO DEV_OE AM21 AG20

B8 VREFB8N2 IO DEV_CLRn AM22 AH20

B8 VREFB8N2 IO nCS AN23 AJ18

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 10

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 10 of 47

ersion 1.5

Number

B12 VREFB8N2 IO PLL12_FBn/OUT2n AN22 AJ20

B12 VREFB8N2 IO PLL12_FBp/OUT2p AP22 AK20

B8 VREFB8N2 IO AM24

B8 VREFB8N2 IO AN24 AB17

B12 VREFB8N2 IO PLL12_OUT1n AR22 AL20

B12 VREFB8N2 IO PLL12_OUT1p AT21 AM20

B12 VREFB8N2 IO PLL12_OUT0n AT22 AN20

B12 VREFB8N2 IO PLL12_OUT0p AU22 AP20

B8 VREFB8N2 IO CLK5n AN21 AH19

B8 VREFB8N2 IO CLK5p AP21 AJ19

B8 VREFB8N2 IO CLK4n AV22 AM19

B8 VREFB8N2 IO CLK4p AW22 AN19

B12 VCC_PLL12_OUT AJ24 AE20

B10 VCC_PLL6_OUT AJ18 AG16

B7 VREFB7N0 IO CLK7p AV21 AL19

B7 VREFB7N0 IO CLK7n AU21 AK19

B7 VREFB7N0 IO CLK6p AW20 AP18

B7 VREFB7N0 IO CLK6n AW21 AP19

B10 VREFB7N0 IO PLL6_OUT1p AU20 AM18

B10 VREFB7N0 IO PLL6_OUT1n AT20 AL18

B10 VREFB7N0 IO PLL6_OUT0p AW19 AP17

B10 VREFB7N0 IO PLL6_OUT0n AV19 AN17

B10 VREFB7N0 IO PLL6_FBp/OUT2p AP20 AM17

B10 VREFB7N0 IO PLL6_FBn/OUT2n AN20 AL17

B7 VREFB7N0 IO AH20 AH17 DQ14B0 DQ12B0 DQ14B0 DQ14B0

B7 VREFB7N0 IO AG21 AC17 DQ14B1 DQ12B1 DQ14B1 DQ14B1

B7 VREFB7N0 IO AG20 AC16 DQS14B DQS12B DQS14B DQS14B

B7 VREFB7N0 IO AM19 DQ14B2 DQ14B2

B7 VREFB7N0 IO DQ9B AN19 AJ16 DQ4B8 DQ14B3 DQ12B2 DQ9B3 DQ14B3 DQ14B2 DQ9B3

B7 VREFB7N0 IO DQSn9B AP19 AL16 DQ4B4 DQ1B14 DQ0B33 DM14B DQ12B3 DQSB9B DQ14B3 DQSB9B

B7 VREFB7N0 VREFB7N0 VREFB7N0 AR19 AK17

B7 VREFB7N0 IO DQ9B AU19 AK16 DQ4B7 DQ1B17 DQ15B0 DM12B DQ9B2 DQ15B0 DQ15B0 DQ9B2

B7 VREFB7N0 IO DQ9B AT19 AN16 DQ4B6 DQ1B16 DQ0B35 DQ15B1 DQ13B0 DQ9B1 DQ15B1 DQ15B1 DQ9B1

VREF Group Pin

Name/Function

VCCD_PLL12 AJ21 AF20

VCCA_PLL12 AL22 AE18

GNDA_PLL12 AJ22 AF18

GNDA_PLL12 AK22 AF19

GNDA_PLL6 AK20 AF17

VCCA_PLL6 AL20 AE16

VCCD_PLL6 AJ19 AF16

GNDA_PLL6 AK19 AE17

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 11

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 11 of 47

ersion 1.5

Number

B7 VREFB7N0 IO DQ9B AN18 AP16 DQ4B5 DQ1B15 DQ0B34 DQS15B DQ13B1 DQ9B0 DQS15B DQS15B DQ9B0

B7 VREFB7N0 IO DQS9B AP18 AM16 DQVLD4B DQ15B2 DQS13B DQS9B DQ15B2 DQ15B2 DQS9B

B7 VREFB7N0 IO AF21 AB16 DQ15B3 DQ13B2 DQ15B3 DQ15B3

B7 VREFB7N0 IO AG19 AJ17 DM15B DQ13B3 DQ16B0

B7 VREFB7N0 IO DQ8B AR18 AH16 DQ4B3 DQ1B13 DQ0B32 DQ16B0 DM13B DQ8B3 DQ16B0 DQ16B1 DQ8B3

B7 VREFB7N0 IO DQSn8B AU18 AM15 DQSn4B DQ1B9 DQ0B28 DQ16B1 DQ14B0 DQSB8B DQ16B1 DQS16B DQSB8B

B7 VREFB7N0 IO DQ8B AW17 AH15 DQ4B2 DQ1B12 DQ0B31 DQS16B DQ14B1 DQ8B2 DQS16B DQ16B2 DQ8B2

B7 VREFB7N0 IO DQ8B AT18 AJ15 DQ4B1 DQ1B11 DQ0B30 DQ16B2 DQS14B DQ8B1 DQ16B2 DQ16B3 DQ8B1

B7 VREFB7N0 IO DQ8B AW18 AP15 DQ4B0 DQ1B10 DQ0B29 DQ16B3 DQ14B2 DQ8B0 DQ16B3 DQ17B0 DQ8B0

B7 VREFB7N0 IO DQS8B AV18 AL15 DQS4B DQVLD1B DM16B DQ14B3 DQS8B DQ17B1 DQS8B

B7 VREFB7N0 IO AF19 AC15 DQ17B0 DM14B DQ17B0 DQS17B

B7 VREFB7N0 IO AK18 AG14 DQ17B1 DQ15B0 DQ17B1 DQ17B2

B7 VREFB7N0 IO DQ7B AP17 AP14 DQ3B8 DQ1B8 DQ0B27 DQS17B DQ15B1 DQ7B3 DQS17B DQ17B3 DQ7B3

B7 VREFB7N0 IO DQSn7B AU17 AM14 DQ3B4 DQSn1B DQ0B23 DQ17B2 DQS15B DQSB7B DQ17B2 DQ18B0 DQSB7B

B7 VREFB7N1 IO DQ7B AV16 AK14 DQ3B7 DQ1B7 DQ0B26 DQ17B3 DQ15B2 DQ7B2 DQ17B3 DQ18B1 DQ7B2

B7 VREFB7N1 IO DQ7B AW16 AJ14 DQ3B6 DQ1B6 DQ0B25 DM17B DQ15B3 DQ7B1 DQS18B DQ7B1

B7 VREFB7N1 IO DQ7B AN17 AN14 DQ3B5 DQ1B5 DQ0B24 DQ18B0 DM15B DQ7B0 DQ18B0 DQ18B2 DQ7B0

B7 VREFB7N1 IO DQS7B AT17 AL14 DQVLD3B DQS1B DQ18B1 DQ16B0 DQS7B DQ18B1 DQ18B3 DQS7B

B7 VREFB7N1 IO AL18 DQS18B DQS18B

B7 VREFB7N1 IO AG18 AD14 DQ18B2 DQ16B1 DQ18B2 DQ19B0

B7 VREFB7N1 IO DQ6B AT16 AP13 DQ3B3 DQ1B4 DQ0B22 DQ18B3 DQS16B DQ6B3 DQ18B3 DQ19B1 DQ6B3

B7 VREFB7N1 IO DQSn6B AP16 AM13 DQSn3B DQ1B0 DQ0B18 DM18B DQ16B2 DQSB6B DQS19B DQSB6B

B7 VREFB7N1 IO DQ6B AU16 AH13 DQ3B2 DQ1B3 DQ0B21 DQ19B0 DQ16B3 DQ6B2 DQ19B0 DQ19B2 DQ6B2

B7 VREFB7N1 IO DQ6B AN15 AJ13 DQ3B1 DQ1B2 DQ0B20 DQ19B1 DM16B DQ6B1 DQ19B1 DQ19B3 DQ6B1

B7 VREFB7N1 IO DQ6B AN16 AN13 DQ3B0 DQ1B1 DQ0B19 DQS19B DQ17B0 DQ6B0 DQS19B DQ20B0 DQ6B0

B7 VREFB7N1 IO DQS6B AP15 AL13 DQS3B DQ19B2 DQ17B1 DQS6B DQ19B2 DQ20B1 DQS6B

B7 VREFB7N1 IO AF18 AE14 DQ19B3 DQS17B DQ19B3 DQS20B

B7 VREFB7N1 IO AM18 AF14 DM19B DQ17B2 DQ20B2

B7 VREFB7N1 IO DQ5B AW15 AP12 DQ2B8 DQ20B0 DQ17B3 DQ5B3 DQ20B0 DQ20B3 DQ5B3

B7 VREFB7N1 IO DQSn5B AV15 AM12 DQ2B4 DQ0B14 DQSn0B DQ20B1 DM17B DQSB5B DQ20B1 DQ21B0 DQSB5B

B7 VREFB7N1 VREFB7N1 VREFB7N1 AR16 AK13

B7 VREFB7N1 IO DQ5B AW14 AH11 DQ2B7 DQ0B17 DQ0B17 DQS20B DQ18B0 DQ5B2 DQS20B DQ21B1 DQ5B2

B7 VREFB7N1 IO DQ5B AR15 AH12 DQ2B6 DQ0B16 DQ0B16 DQ20B2 DQ18B1 DQ5B1 DQ20B2 DQS21B DQ5B1

B7 VREFB7N1 IO DQ5B AT15 AJ12 DQ2B5 DQ0B15 DQ0B15 DQ20B3 DQS18B DQ5B0 DQ20B3 DQ21B2 DQ5B0

B7 VREFB7N1 IO DQS5B AU15 AL12 DQVLD2B DQS0B DM20B DQ18B2 DQS5B DQ21B3 DQS5B

B7 VREFB7N1 IO AG17 AC14 DQ21B0 DQ18B3 DQ21B0 DQ22B0

B7 VREFB7N1 IO AJ16 DQ21B1 DQ21B1

B7 VREFB7N1 IO DQ4B AP14 AP11 DQ2B3 DQ0B13 DQ0B14 DQS21B DM18B DQ4B3 DQS21B DQ22B1 DQ4B3

B7 VREFB7N1 IO DQSn4B AU14 AM11 DQSn2B DQ0B9 DQ0B10 DQ21B2 DQ19B0 DQSB4B DQ21B2 DQS22B DQSB4B

B7 VREFB7N1 IO DQ4B AV13 AJ11 DQ2B2 DQ0B12 DQ0B13 DQ21B3 DQ19B1 DQ4B2 DQ21B3 DQ22B2 DQ4B2

B7 VREFB7N1 IO DQ4B AN14 AK11 DQ2B1 DQ0B11 DQ0B12 DM21B DQS19B DQ4B1 DQ22B3 DQ4B1

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 12

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 12 of 47

ersion 1.5

Number

B7 VREFB7N1 IO DQ4B AW13 AN11 DQ2B0 DQ0B10 DQ0B11 DQ22B0 DQ19B2 DQ4B0 DQ22B0 DQ23B0 DQ4B0

B7 VREFB7N1 IO DQS4B AT14 AL11 DQS2B DQVLD0B DQVLD0B DQ22B1 DQ19B3 DQS4B DQ22B1 DQ23B1 DQS4B

B7 VREFB7N1 IO AH16 AE13 DQS22B DM19B DQS22B DQS23B

B7 VREFB7N1 IO AK16 AF13 DQ22B2 DQ20B0 DQ22B2 DQ23B2

B7 VREFB7N1 IO DQ3B AU13 AP10 DQ1B8 DQ0B8 DQ0B9 DQ22B3 DQ20B1 DQ3B3 DQ22B3 DQ23B3 DQ3B3

B7 VREFB7N1 IO DQSn3B AP13 AM10 DQ1B4 DQSn0B DQ0B5 DM22B DQS20B DQSB3B DQ24B0 DQSB3B

B7 VREFB7N1 IO DQ3B AN12 AH10 DQ1B7 DQ0B7 DQ0B8 DQ23B0 DQ20B2 DQ3B2 DQ23B0 DQ24B1 DQ3B2

B7 VREFB7N1 IO DQ3B AT13 AJ10 DQ1B6 DQ0B6 DQ0B7 DQ23B1 DQ20B3 DQ3B1 DQ23B1 DQS24B DQ3B1

B7 VREFB7N1 IO DQ3B AN13 AN10 DQ1B5 DQ0B5 DQ0B6 DQS23B DM20B DQ3B0 DQS23B DQ24B2 DQ3B0

B7 VREFB7N1 IO DQS3B AP12 AL10 DQVLD1B DQS0B DQ23B2 DQ21B0 DQS3B DQ23B2 DQ24B3 DQS3B

B7 VREFB7N2 IO AG16 AD13 DQ23B3 DQ21B1 DQ23B3 DQ25B0

B7 VREFB7N2 IO AL16 AH14 DM23B DQS21B DQ25B1

B7 VREFB7N2 IO DQ2B AW12 AP9 DQ1B3 DQ0B4 DQ0B4 DQ24B0 DQ21B2 DQ2B3 DQ24B0 DQS25B DQ2B3

B7 VREFB7N2 IO DQSn2B AV12 AM9 DQSn1B DQ0B0 DQ0B0 DQ24B1 DQ21B3 DQSB2B DQ24B1 DQ25B2 DQSB2B

B7 VREFB7N2 IO DQ2B AR12 AH9 DQ1B2 DQ0B3 DQ0B3 DQS24B DM21B DQ2B2 DQS24B DQ25B3 DQ2B2

B7 VREFB7N2 IO DQ2B AW11 AH8 DQ1B1 DQ0B2 DQ0B2 DQ24B2 DQ22B0 DQ2B1 DQ24B2 DQ26B0 DQ2B1

B7 VREFB7N2 IO DQ2B AT12 AJ9 DQ1B0 DQ0B1 DQ0B1 DQ24B3 DQ22B1 DQ2B0 DQ24B3 DQ26B1 DQ2B0

B7 VREFB7N2 IO DQS2B AU12 AL9 DQS1B DM24B DQS22B DQS2B DQS26B DQS2B

B7 VREFB7N2 IO AJ15 DQ25B0 DQ25B0

B7 VREFB7N2 IO AH15 AC13 DQ25B1 DQ22B2 DQ25B1 DQ26B2

B7 VREFB7N2 IO DQ1B AW10 AP8 DQ0B8 DQS25B DQ22B3 DQ1B3 DQS25B DQ26B3 DQ1B3

B7 VREFB7N2 IO DQSn1B AU11 AM8 DQ0B4 DQ25B2 DM22B DQSB1B DQ25B2 DQ27B0 DQSB1B

B7 VREFB7N2 IO DQ1B AN11 AJ8 DQ0B7 DQ25B3 DQ23B0 DQ1B2 DQ25B3 DQ27B1 DQ1B2

B7 VREFB7N2 IO DQ1B AU10 AK8 DQ0B6 DM25B DQ23B1 DQ1B1 DQS27B DQ1B1

B7 VREFB7N2 IO DQ1B AV10 AN8 DQ0B5 DQ26B0 DQS23B DQ1B0 DQ26B0 DQ27B2 DQ1B0

B7 VREFB7N2 IO DQS1B AT11 AL8 DQVLD0B DQ26B1 DQ23B2 DQS1B DQ26B1 DQ27B3 DQS1B

B7 VREFB7N2 VREFB7N2 VREFB7N2 AR13 AK10

B7 VREFB7N2 IO AG15 AE11 DQS26B DQ23B3 DQS26B DQ28B0

B7 VREFB7N2 IO AK15 AG13 DQ26B2 DM23B DQ26B2 DQ28B1

B7 VREFB7N2 IO DQ0B AW9 AP7 DQ0B3 DQ26B3 DQ24B0 DQ0B3 DQ26B3 DQS28B DQ0B3

B7 VREFB7N2 IO DQSn0B AT10 AM7 DQSn0B DM26B DQ24B1 DQSB0B DQ28B2 DQSB0B

B7 VREFB7N2 IO DQ0B AP10 AG8 DQ0B2 DQ27B0 DQS24B DQ0B2 DQ27B0 DQ28B3 DQ0B2

B7 VREFB7N2 IO DQ0B AN10 AH7 DQ0B1 DQ27B1 DQ24B2 DQ0B1 DQ27B1 DQ29B0 DQ0B1

B7 VREFB7N2 IO DQ0B AU9 AJ7 DQ0B0 DQS27B DQ24B3 DQ0B0 DQS27B DQ29B1 DQ0B0

B7 VREFB7N2 IO DQS0B AT9 AL7 DQS0B DQ27B2 DM24B DQS0B DQ27B2 DQS29B DQS0B

B7 VREFB7N2 IO AM15 AF11 DQ27B3 DQ27B3 DQ29B2

B7 VREFB7N2 IO AL15 DM27B

B7 VREFB7N2 IO AM16 AG11 DQ29B3

B7 VREFB7N2 IO AM13 AG10

B7 VREFB7N2 IO RDN7 AH14 AE10

B7 VREFB7N2 IO RUP7 AG14 AE9

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 13

V

Number

Page 13 of 47

B7 VREFB7N2 IO AL13

B7 VREFB7N2 IO AK13 AF10

B7 VREFB7N2 PORSEL PORSEL AL10 AE8

B7 VREFB7N2 nIO_PULLUP nIO_PULLUP AL11 AE7

B7 VREFB7N2 PLL_ENA PLL_ENA AL12 AF8

B7 VREFB7N2 nCEO nCEO AM10 AF9

B16 GXB_RX15n AL2

B16 GXB_RX15p AL1

B16 GXB_TX15n AL5

B16 GXB_TX15p AL4

B16 GXB_RX14n AJ2

B16 GXB_RX14p AJ1

B16 GXB_TX14n AJ5

B16 GXB_TX14p AJ4

B16 RREFB16 AD7

B16 REFCLK0_B16n AH8

B16 REFCLK0_B16p AH7

B16 REFCLK1_B16n AF8

B16 REFCLK1_B16p AF7

B16 GXB_RX12n AG2

B16 GXB_RX12p AG1

B16 GXB_TX12n AG5

B16 GXB_TX12p AG4

B16 GXB_RX13n AE2

B16 GXB_RX13p AE1

B16 GXB_TX13n AE5

B16 GXB_TX13p AE4

B15 GXB_RX11n AC2 AM2

B15 GXB_RX11p AC1 AM1

B15 GXB_TX11n AC5 AP5

B15 GXB_TX11p AC4 AP4

B15 GXB_RX10n AA2 AK2

B15 GXB_RX10p AA1 AK1

B15 GXB_TX10n AA5 AM5

B15 GXB_TX10p AA4 AM4

VREF Group Pin

Name/Function

GND AM12 AF7

VCCL_B16 AE9

VCCA AF12

VCCA AD9

VCCA AF10

GND AF11

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

DQ group for DQS

mode

x16/x18

Mode

DQ group for DQS

Pin Information for the Stratix® II GX EP2SGX90 Device

ersion 1.5

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 14

V

Number

Page 14 of 47

B15 RREFB15 Y7 AH4

B15 REFCLK0_B15n AB8 AK5

B15 REFCLK0_B15p AB7 AK4

B15 REFCLK1_B15n V8 AH2

B15 REFCLK1_B15p V7 AH1

B15 GXB_RX8n W2 AF2

B15 GXB_RX8p W1 AF1

B15 GXB_TX8n W5 AF5

B15 GXB_TX8p W4 AF4

B15 GXB_RX9n U2 AD2

B15 GXB_RX9p U1 AD1

B15 GXB_TX9n U5 AD5

B15 GXB_TX9p U4 AD4

B14 GXB_RX7n R2 AB2

B14 GXB_RX7p R1 AB1

B14 GXB_TX7n R5 AB5

B14 GXB_TX7p R4 AB4

B14 GXB_RX6n N2 Y2

B14 GXB_RX6p N1 Y1

B14 GXB_TX6n N5 Y5

B14 GXB_TX6p N4 Y4

B14 RREFB14 T7 V4

B14 REFCLK0_B14n P8 V2

B14 REFCLK0_B14p P7 V1

B14 REFCLK1_B14n M8 U7

B14 REFCLK1_B14p M7 U6

B14 GXB_RX4n L2 R2

B14 GXB_RX4p L1 R1

VREF Group Pin

Name/Function

VCCL_B15 AA9 AB8

VCCA AB12 AC11

VCCA Y9 AA8

VCCA AB10 AC9

GND AB11 AC10

NC V10 W7

NC V11 W8

VCCA V12 W12

VCCL_B14 T9 V8

VCCA U12 W11

VCCA R9 U8

VCCA U10 W9

GND U11 W10

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

DQ group for DQS

mode

x16/x18

Mode

DQ group for DQS

Pin Information for the Stratix® II GX EP2SGX90 Device

ersion 1.5

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 15

V

Number

Page 15 of 47

B14 GXB_TX4n L5 R5

B14 GXB_TX4p L4 R4

B14 GXB_RX5n J2 N2

B14 GXB_RX5p J1 N1

B14 GXB_TX5n J5 N5

B14 GXB_TX5p J4 N4

B13 GXB_RX3n G2 L2

B13 GXB_RX3p G1 L1

B13 GXB_TX3n G5 L5

B13 GXB_TX3p G4 L4

B13 GXB_RX2n E2 J2

B13 GXB_RX2p E1 J1

B13 GXB_TX2n E5 J5

B13 GXB_TX2p E4 J4

B13 RREFB13 K7 G4

B13 REFCLK0_B13n H8 G2

B13 REFCLK0_B13p H7 G1

B13 REFCLK1_B13n F8 E5

B13 REFCLK1_B13p F7 E4

B13 GXB_RX0n C2 E2

B13 GXB_RX0p C1 E1

B13 GXB_TX0n C5 C5

B13 GXB_TX0p C4 C4

B13 GXB_RX1n A4 C2

B13 GXB_RX1p A3 C1

B13 GXB_TX1n A7 A5

B13 GXB_TX1p A6 A4

B4 VREFB4N0 TDO TDO H13 H10

B4 VREFB4N0 MSEL3 MSEL3 H12 H11

B4 VREFB4N0 MSEL2 MSEL2 J13 J10

B4 VREFB4N0 MSEL1 MSEL1 J12 J9

B4 VREFB4N0 MSEL0 MSEL0 J11 K10

B4 VREFB4N0 IO H15 M13

B4 VREFB4N0 IO J15 L13

VREF Group Pin

Name/Function

VCCL_B13 M9 P8

VCCA N12 R11

VCCA L9 N8

VCCA N10 R9

GND N11 R10

TEMPDIODEp H10 J8

TEMPDIODEn J10 J7

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

DQ group for DQS

mode

x16/x18

Mode

DQ group for DQS

Pin Information for the Stratix® II GX EP2SGX90 Device

ersion 1.5

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 16

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 16 of 47

ersion 1.5

Number

B4 VREFB4N0 IO RUP4 N13 J11

B4 VREFB4N0 IO RDN4 N14 K11

B4 VREFB4N0 IO J16 H13 DQ28T3

B4 VREFB4N0 IO K15 H14 DQ28T2

B4 VREFB4N0 IO K16 M14 DM26T DM23T DQS28T

B4 VREFB4N0 IO M14 DQ26T3 DQ26T3

B4 VREFB4N0 IO DQS0T D9 D7 DQS0T DQ26T2 DQ23T3 DQS0T DQ26T2 DQ28T1 DQS0T

B4 VREFB4N0 IO DQ0T C9 F7 DQ0T0 DQS26T DQ23T2 DQ0T0 DQS26T DQ28T0 DQ0T0

B4 VREFB4N0 IO DQ0T G10 G7 DQ0T1 DQ26T1 DQS23T DQ0T1 DQ26T1 DQ27T3 DQ0T1

B4 VREFB4N0 IO DQ0T F10 H8 DQ0T2 DQ26T0 DQ23T1 DQ0T2 DQ26T0 DQ27T2 DQ0T2

B4 VREFB4N0 IO DQSn0T D10 C7 DQSn0T DM25T DQ23T0 DQSB0T DQS27T DQSB0T

B4 VREFB4N0 IO DQ0T A9 A7 DQ0T3 DQ25T3 DM22T DQ0T3 DQ25T3 DQ27T1 DQ0T3

B4 VREFB4N0 IO L15 DQ25T2 DQ25T2

B4 VREFB4N0 IO P15 M15 DQS25T DQ22T3 DQS25T DQ27T0

B4 VREFB4N0 VREFB4N0 VREFB4N0 E13 E10

B4 VREFB4N0 IO DQS1T D11 D8 DQVLD0T DQ25T1 DQ22T2 DQS1T DQ25T1 DQ26T3 DQS1T

B4 VREFB4N0 IO DQ1T C10 B8 DQ0T5 DQ25T0 DQS22T DQ1T0 DQ25T0 DQ26T2 DQ1T0

B4 VREFB4N0 IO DQ1T A10 E8 DQ0T6 DM24T DQ22T1 DQ1T1 DQS26T DQ1T1

B4 VREFB4N0 IO DQ1T G11 F8 DQ0T7 DQ24T3 DQ22T0 DQ1T2 DQ24T3 DQ26T1 DQ1T2

B4 VREFB4N0 IO DQSn1T C11 C8 DQ0T4 DQ24T2 DM21T DQSB1T DQ24T2 DQ26T0 DQSB1T

B4 VREFB4N0 IO DQ1T B10 A8 DQ0T8 DQS24T DQ21T3 DQ1T3 DQS24T DQ25T3 DQ1T3

B4 VREFB4N0 IO N15 L14 DQ24T1 DQ21T2 DQ24T1 DQ25T2

B4 VREFB4N0 IO M15 K13 DQ24T0 DQS21T DQ24T0 DQS25T

B4 VREFB4N0 IO DQS2T C12 D9 DQS1T DM23T DQ21T1 DQS2T DQ25T1 DQS2T

B4 VREFB4N0 IO DQ2T D12 F9 DQ1T0 DQ0T1 DQ0T1 DQ23T3 DQ21T0 DQ2T0 DQ23T3 DQ25T0 DQ2T0

B4 VREFB4N0 IO DQ2T A11 G8 DQ1T1 DQ0T2 DQ0T2 DQ23T2 DM20T DQ2T1 DQ23T2 DQ24T3 DQ2T1

B4 VREFB4N0 IO DQ2T E12 G9 DQ1T2 DQ0T3 DQ0T3 DQS23T DQ20T3 DQ2T2 DQS23T DQ24T2 DQ2T2

B4 VREFB4N0 IO DQSn2T B12 C9 DQSn1T DQ0T0 DQ0T0 DQ23T1 DQ20T2 DQSB2T DQ23T1 DQS24T DQSB2T

B4 VREFB4N0 IO DQ2T A12 A9 DQ1T3 DQ0T4 DQ0T4 DQ23T0 DQS20T DQ2T3 DQ23T0 DQ24T1 DQ2T3

B4 VREFB4N0 IO H16 J13 DM22T DQ20T1 DQ24T0

B4 VREFB4N0 IO P16 DQ22T3 DQ22T3

B4 VREFB4N1 IO DQS3T D13 D10 DQVLD1T DQS0T DQ22T2 DQ20T0 DQS3T DQ22T2 DQ23T3 DQS3T

B4 VREFB4N1 IO DQ3T B13 B10 DQ1T5 DQ0T5 DQ0T6 DQS22T DM19T DQ3T0 DQS22T DQ23T2 DQ3T0

B4 VREFB4N1 IO DQ3T G12 F10 DQ1T6 DQ0T6 DQ0T7 DQ22T1 DQ19T3 DQ3T1 DQ22T1 DQS23T DQ3T1

B4 VREFB4N1 IO DQ3T F12 G10 DQ1T7 DQ0T7 DQ0T8 DQ22T0 DQ19T2 DQ3T2 DQ22T0 DQ23T1 DQ3T2

B4 VREFB4N1 IO DQSn3T C13 C10 DQ1T4 DQSn0T DQ0T5 DM21T DQS19T DQSB3T DQ23T0 DQSB3T

B4 VREFB4N1 IO DQ3T A13 A10 DQ1T8 DQ0T8 DQ0T9 DQ21T3 DQ19T1 DQ3T3 DQ21T3 DQ22T3 DQ3T3

B4 VREFB4N1 IO L16 N17 DQ21T2 DQ19T0 DQ21T2 DQ22T2

B4 VREFB4N1 IO N16 M16 DQS21T DM18T DQS21T DQS22T

B4 VREFB4N1 IO DQS4T F13 D11 DQS2T DQVLD0T DQVLD0T DQ21T1 DQ18T3 DQS4T DQ21T1 DQ22T1 DQS4T

B4 VREFB4N1 IO DQ4T D14 B11 DQ2T0 DQ0T10 DQ0T11 DQ21T0 DQ18T2 DQ4T0 DQ21T0 DQ22T0 DQ4T0

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 17

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 17 of 47

ersion 1.5

Number

B4 VREFB4N1 IO DQ4T G13 E11 DQ2T1 DQ0T11 DQ0T12 DM20T DQS18T DQ4T1 DQ21T3 DQ4T1

B4 VREFB4N1 IO DQ4T G14 F11 DQ2T2 DQ0T12 DQ0T13 DQ20T3 DQ18T1 DQ4T2 DQ20T3 DQ21T2 DQ4T2

B4 VREFB4N1 IO DQSn4T F14 C11 DQSn2T DQ0T9 DQ0T10 DQ20T2 DQ18T0 DQSB4T DQ20T2 DQS21T DQSB4T

B4 VREFB4N1 IO DQ4T C14 A11 DQ2T3 DQ0T13 DQ0T14 DQS20T DM17T DQ4T3 DQS20T DQ21T1 DQ4T3

B4 VREFB4N1 IO H18 J14 DQ20T1 DQ17T3 DQ20T1 DQ21T0

B4 VREFB4N1 IO M16 K14 DQ20T0 DQ17T2 DQ20T0 DQ20T3

B4 VREFB4N1 IO DQS5T C15 D12 DQVLD2T DQS0T DM19T DQS17T DQS5T DQ20T2 DQS5T

B4 VREFB4N1 IO DQ5T D15 F12 DQ2T5 DQ0T15 DQ0T15 DQ19T3 DQ17T1 DQ5T0 DQ19T3 DQS20T DQ5T0

B4 VREFB4N1 IO DQ5T E15 G12 DQ2T6 DQ0T16 DQ0T16 DQ19T2 DQ17T0 DQ5T1 DQ19T2 DQ20T1 DQ5T1

B4 VREFB4N1 IO DQ5T A14 G11 DQ2T7 DQ0T17 DQ0T17 DQS19T DM16T DQ5T2 DQS19T DQ20T0 DQ5T2

B4 VREFB4N1 VREFB4N1 VREFB4N1 E16 E13

B4 VREFB4N1 IO DQSn5T B15 C12 DQ2T4 DQ0T14 DQSn0T DQ19T1 DQ16T3 DQSB5T DQ19T1 DQ19T3 DQSB5T

B4 VREFB4N1 IO DQ5T A15 A12 DQ2T8 DQ19T0 DQ16T2 DQ5T3 DQ19T0 DQ19T2 DQ5T3

B4 VREFB4N1 IO J18 DM18T

B4 VREFB4N1 IO N17 N18 DQ18T3 DQS16T DQ18T3 DQS19T

B4 VREFB4N1 IO DQS6T D16 D13 DQS3T DQ18T2 DQ16T1 DQS6T DQ18T2 DQ19T1 DQS6T

B4 VREFB4N1 IO DQ6T B16 B13 DQ3T0 DQ1T1 DQ0T19 DQS18T DQ16T0 DQ6T0 DQS18T DQ19T0 DQ6T0

B4 VREFB4N1 IO DQ6T G15 F13 DQ3T1 DQ1T2 DQ0T20 DQ18T1 DM15T DQ6T1 DQ18T1 DQ18T3 DQ6T1

B4 VREFB4N1 IO DQ6T F15 G13 DQ3T2 DQ1T3 DQ0T21 DQ18T0 DQ15T3 DQ6T2 DQ18T0 DQ18T2 DQ6T2

B4 VREFB4N1 IO DQSn6T C16 C13 DQSn3T DQ1T0 DQ0T18 DM17T DQ15T2 DQSB6T DQS18T DQSB6T

B4 VREFB4N1 IO DQ6T A16 A13 DQ3T3 DQ1T4 DQ0T22 DQ17T3 DQS15T DQ6T3 DQ17T3 DQ18T1 DQ6T3

B4 VREFB4N1 IO P18 M17 DQ17T2 DQ15T1 DQ17T2 DQ18T0

B4 VREFB4N1 IO K18 N19 DQS17T DQ15T0 DQS17T DQ17T3

B4 VREFB4N1 IO DQS7T F16 D14 DQVLD3T DQS1T DQ17T1 DM14T DQS7T DQ17T1 DQ17T2 DQS7T

B4 VREFB4N1 IO DQ7T G17 B14 DQ3T5 DQ1T5 DQ0T24 DQ17T0 DQ14T3 DQ7T0 DQ17T0 DQS17T DQ7T0

B4 VREFB4N1 IO DQ7T D17 F14 DQ3T6 DQ1T6 DQ0T25 DM16T DQ14T2 DQ7T1 DQ17T1 DQ7T1

B4 VREFB4N1 IO DQ7T G16 E14 DQ3T7 DQ1T7 DQ0T26 DQ16T3 DQS14T DQ7T2 DQ16T3 DQ17T0 DQ7T2

B4 VREFB4N2 IO DQSn7T F17 C14 DQ3T4 DQSn1T DQ0T23 DQ16T2 DQ14T1 DQSB7T DQ16T2 DQ16T3 DQSB7T

B4 VREFB4N2 IO DQ7T C17 A14 DQ3T8 DQ1T8 DQ0T27 DQS16T DQ14T0 DQ7T3 DQS16T DQ16T2 DQ7T3

B4 VREFB4N2 IO H19 M19 DQ16T1 DM13T DQ16T1 DQS16T

B4 VREFB4N2 IO N18 DQ16T0 DQ16T0

B4 VREFB4N2 IO DQS8T B18 D15 DQS4T DQVLD1T DM15T DQ13T3 DQS8T DQ16T1 DQS8T

B4 VREFB4N2 IO DQ8T A18 A15 DQ4T0 DQ1T10 DQ0T29 DQ15T3 DQ13T2 DQ8T0 DQ15T3 DQ16T0 DQ8T0

B4 VREFB4N2 IO DQ8T A17 F15 DQ4T1 DQ1T11 DQ0T30 DQ15T2 DQS13T DQ8T1 DQ15T2 DQ15T3 DQ8T1

B4 VREFB4N2 IO DQ8T D18 G15 DQ4T2 DQ1T12 DQ0T31 DQS15T DQ13T1 DQ8T2 DQS15T DQ15T2 DQ8T2

B4 VREFB4N2 IO DQSn8T C18 C15 DQSn4T DQ1T9 DQ0T28 DQ15T1 DQ13T0 DQSB8T DQ15T1 DQS15T DQSB8T

B4 VREFB4N2 IO DQ8T E18 G14 DQ4T3 DQ1T13 DQ0T32 DQ15T0 DM12T DQ8T3 DQ15T0 DQ15T1 DQ8T3

B4 VREFB4N2 IO N19 F19 DM14T DQ12T3 DQ15T0

B4 VREFB4N2 IO N20 M18 DQ14T3 DQ12T2 DQ14T3 DQ14T3

B4 VREFB4N2 IO DQS9T F18 C16 DQVLD4T DQ14T2 DQS12T DQS9T DQ14T2 DQ14T2 DQS9T

B4 VREFB4N2 IO DQ9T D19 A16 DQ4T5 DQ1T15 DQ0T34 DQS14T DQ12T1 DQ9T0 DQS14T DQS14T DQ9T0

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 18

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 18 of 47

ersion 1.5

Number

B4 VREFB4N2 IO DQ9T G18 B16 DQ4T6 DQ1T16 DQ0T35 DQ14T1 DQ12T0 DQ9T1 DQ14T1 DQ14T1 DQ9T1

B4 VREFB4N2 IO DQ9T C19 F16 DQ4T7 DQ1T17 DQ14T0 DM11T DQ9T2 DQ14T0 DQ14T0 DQ9T2

B4 VREFB4N2 VREFB4N2 VREFB4N2 E19 E16

B4 VREFB4N2 IO DQSn9T F19 D16 DQ4T4 DQ1T14 DQ0T33 DM13T DQ11T3 DQSB9T DQ13T3 DQSB9T

B4 VREFB4N2 IO DQ9T G19 G16 DQ4T8 DQ13T3 DQ11T2 DQ9T3 DQ13T3 DQ13T2 DQ9T3

B4 VREFB4N2 IO H21 G18 DQ13T2 DQS11T DQ13T2 DQS13T

B4 VREFB4N2 IO N21 F18 DQS13T DQ11T1 DQS13T DQ13T1

B4 VREFB4N2 IO M20 DQ13T1 DQ13T1

B4 VREFB4N2 IO J21 G19 DQ13T0 DQ11T0 DQ13T0 DQ13T0

B9 VREFB4N2 IO PLL5_FBn/OUT2n G20 F17

B9 VREFB4N2 IO PLL5_FBp/OUT2p F20 E17

B9 VREFB4N2 IO PLL5_OUT0n B19 B17

B9 VREFB4N2 IO PLL5_OUT0p A19 A17

B9 VREFB4N2 IO PLL5_OUT1n D20 D17

B9 VREFB4N2 IO PLL5_OUT1p C20 C17

B4 VREFB4N2 IO CLK12n A21 A19

B4 VREFB4N2 IO CLK12p A20 A18

B4 VREFB4N2 IO CLK13n C21 D18

B4 VREFB4N2 IO CLK13p B21 C18

B9 VCC_PLL5_OUT L18 H16

B11 VCC_PLL11_OUT L24 K20

B3 VREFB3N0 IO CLK14p C22 B19

B3 VREFB3N0 IO CLK14n D21 C19

B3 VREFB3N0 IO CLK15p F21 D19

B3 VREFB3N0 IO CLK15n G21 E19

B11 VREFB3N0 IO PLL11_OUT0p A22 A20

B11 VREFB3N0 IO PLL11_OUT0n B22 B20

B11 VREFB3N0 IO PLL11_OUT1p D22 C20

B11 VREFB3N0 IO PLL11_OUT1n E22 D20

B3 VREFB3N0 IO G25 M20

B3 VREFB3N0 IO F26

B11 VREFB3N0 IO PLL11_FBp/OUT2p F22 E20

B11 VREFB3N0 IO PLL11_FBn/OUT2n G22 F20

VREF Group Pin

Name/Function

VCCD_PLL5 L19 H17

VCCA_PLL5 J20 K16

GNDA_PLL5 K19 J16

GNDA_PLL5 K20 J17

GNDA_PLL11 K22 J18

GNDA_PLL11 L22 K18

VCCA_PLL11 J22 K17

VCCD_PLL11 L21 J19

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 19

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 19 of 47

ersion 1.5

Number

B3 VREFB3N0 IO PGM2 G23 G20

B3 VREFB3N0 IO PGM1 H22 H20

B3 VREFB3N0 IO PGM0 N22 H22

B3 VREFB3N0 IO ASDO P22 N21

B3 VREFB3N0 IO nCSO G24 G21

B3 VREFB3N0 IO CRC_ERROR H24 G22

B3 VREFB3N0 IO DATA0 J24 J20

B3 VREFB3N0 IO DATA1 R22 J22

B3 VREFB3N0 VREFB3N0 VREFB3N0 E21 E22

B3 VREFB3N0 IO DQS10T C23 D22 DQS5T DQS10T DQS10T

B3 VREFB3N0 IO DQ10T F23 C21 DQ5T0 DQ2T1 DQ1T1 DM10T DQ10T0 DQ10T0

B3 VREFB3N0 IO DQ10T A23 A21 DQ5T1 DQ2T2 DQ1T2 DM12T DQ10T3 DQ10T1 DQ12T3 DQ10T1

B3 VREFB3N0 IO DQ10T A24 F21 DQ5T2 DQ2T3 DQ1T3 DQ12T3 DQ10T2 DQ10T2 DQ12T3 DQ12T2 DQ10T2

B3 VREFB3N0 IO DQSn10T D23 D21 DQSn5T DQ2T0 DQ1T0 DQ12T2 DQS10T DQSB10T DQ12T2 DQS12T DQSB10T

B3 VREFB3N0 IO DQ10T B24 F22 DQ5T3 DQ2T4 DQ1T4 DQS12T DQ10T1 DQ10T3 DQS12T DQ12T1 DQ10T3

B3 VREFB3N0 IO G26 M21 DQ12T1 DQ10T0 DQ12T1 DQ12T0

B3 VREFB3N0 IO N24 DQ12T0 DQ12T0

B3 VREFB3N0 IO H25 G23 DM11T DM9T DQ11T3

B3 VREFB3N0 IO K24 M22 DQ11T3 DQ9T3 DQ11T3 DQ11T2

B3 VREFB3N0 IO F27 DQ11T2 DQ11T2

B3 VREFB3N0 IO G27 N22 DQS11T DQ9T2 DQS11T DQS11T

B3 VREFB3N0 IO DQS11T C24 C22 DQVLD5T DQS2T DQ11T1 DQS9T DQS11T DQ11T1 DQ11T1 DQS11T

B3 VREFB3N0 IO DQ11T D24 A22 DQ5T5 DQ2T5 DQ1T6 DQ11T0 DQ9T1 DQ11T0 DQ11T0 DQ11T0 DQ11T0

B3 VREFB3N0 IO DQ11T F24 B22 DQ5T6 DQ2T6 DQ1T7 DM10T DQ9T0 DQ11T1 DQ10T3 DQ11T1

B3 VREFB3N0 IO DQ11T A25 F23 DQ5T7 DQ2T7 DQ1T8 DQ10T3 DM8T DQ11T2 DQ10T3 DQ10T2 DQ11T2

B3 VREFB3N0 IO DQSn11T C25 D23 DQ5T4 DQSn2T DQ1T5 DQ10T2 DQ8T3 DQSB11T DQ10T2 DQS10T DQSB11T

B3 VREFB3N0 IO DQ11T B25 E23 DQ5T8 DQ2T8 DQ1T9 DQS10T DQ8T2 DQ11T3 DQS10T DQ10T1 DQ11T3

B3 VREFB3N0 IO F28 DQ10T1 DQ10T1

B3 VREFB3N0 IO K25 L22 DQ10T0 DQS8T DQ10T0 DQ10T0

B3 VREFB3N1 IO J25 G24 DM9T DQ8T1 DQ9T3

B3 VREFB3N1 IO J27 DQ9T3 DQ9T3

B3 VREFB3N1 IO F29 K22 DQ9T2 DQ8T0 DQ9T2 DQ9T2

B3 VREFB3N1 IO M24 DQS9T DQS9T

B3 VREFB3N1 IO DQS12T D25 C23 DQS6T DQVLD2T DQVLD1T DQ9T1 DM7T DQS12T DQ9T1 DQS9T DQS12T

B3 VREFB3N1 IO DQ12T F25 B23 DQ6T0 DQ2T10 DQ1T11 DQ9T0 DQ7T3 DQ12T0 DQ9T0 DQ9T1 DQ12T0

B3 VREFB3N1 IO DQ12T E25 A23 DQ6T1 DQ2T11 DQ1T12 DM8T DQ7T2 DQ12T1 DQ9T0 DQ12T1

B3 VREFB3N1 IO DQ12T C26 D24 DQ6T2 DQ2T12 DQ1T13 DQ8T3 DQS7T DQ12T2 DQ8T3 DQ8T3 DQ12T2

B3 VREFB3N1 IO DQSn12T D26 C24 DQSn6T DQ2T9 DQ1T10 DQ8T2 DQ7T1 DQSB12T DQ8T2 DQ8T2 DQSB12T

B3 VREFB3N1 IO DQ12T A26 F24 DQ6T3 DQ2T13 DQ1T14 DQS8T DQ7T0 DQ12T3 DQS8T DQS8T DQ12T3

B3 VREFB3N1 IO N25 M23 DQ8T1 DM6T DQ8T1 DQ8T1

B3 VREFB3N1 IO G28 L23 DQ8T0 DQ6T3 DQ8T0 DQ8T0

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 20

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 20 of 47

ersion 1.5

Number

B3 VREFB3N1 IO DQS13T B27 B25 DQVLD6T DQS1T DM7T DQ6T2 DQS13T DQ7T3 DQS13T

B3 VREFB3N1 IO DQ13T D27 A24 DQ6T5 DQ2T15 DQ1T15 DQ7T3 DQS6T DQ13T0 DQ7T3 DQ7T2 DQ13T0

B3 VREFB3N1 IO DQ13T A27 A25 DQ6T6 DQ2T16 DQ1T16 DQ7T2 DQ6T1 DQ13T1 DQ7T2 DQS7T DQ13T1

B3 VREFB3N1 IO DQ13T A28 F25 DQ6T7 DQ2T17 DQ1T17 DQS7T DQ6T0 DQ13T2 DQS7T DQ7T1 DQ13T2

B3 VREFB3N1 IO DQSn13T B28 C25 DQ6T4 DQ2T14 DQSn1T DQ7T1 DM5T DQSB13T DQ7T1 DQ7T0 DQSB13T

B3 VREFB3N1 IO DQ13T C27 D25 DQ6T8 DQ7T0 DQ5T3 DQ13T3 DQ7T0 DQ6T3 DQ13T3

B3 VREFB3N1 IO D30 DM6T

B3 VREFB3N1 IO M25 M24 DQ6T3 DQ5T2 DQ6T3 DQ6T2

B3 VREFB3N1 VREFB3N1 VREFB3N1 E24 E25

B3 VREFB3N1 IO L25 DQ6T2 DQ6T2

B3 VREFB3N1 IO D31 H23 DQS6T DQS5T DQS6T DQS6T

B3 VREFB3N1 IO H27 DQ6T1 DQ6T1

B3 VREFB3N1 IO N26 K23 DQ6T0 DQ5T1 DQ6T0 DQ6T1

B3 VREFB3N1 IO DQS14T C28 C26 DQS7T DM5T DQ5T0 DQS14T DQ6T0 DQS14T

B3 VREFB3N1 IO DQ14T D28 B26 DQ7T0 DQ3T1 DQ1T19 DQ5T3 DM4T DQ14T0 DQ5T3 DQ5T3 DQ14T0

B3 VREFB3N1 IO DQ14T A29 E26 DQ7T1 DQ3T2 DQ1T20 DQ5T2 DQ4T3 DQ14T1 DQ5T2 DQ5T2 DQ14T1

B3 VREFB3N1 IO DQ14T E28 F26 DQ7T2 DQ3T3 DQ1T21 DQS5T DQ4T2 DQ14T2 DQS5T DQS5T DQ14T2

B3 VREFB3N1 IO DQSn14T C29 D26 DQSn7T DQ3T0 DQ1T18 DQ5T1 DQS4T DQSB14T DQ5T1 DQ5T1 DQSB14T

B3 VREFB3N1 IO DQ14T D29 A26 DQ7T3 DQ3T4 DQ1T22 DQ5T0 DQ4T1 DQ14T3 DQ5T0 DQ5T0 DQ14T3

B3 VREFB3N1 IO H28 J23 DM4T DQ4T0 DQ4T3

B3 VREFB3N1 IO G29 DQ4T3 DQ4T3

B3 VREFB3N1 IO DQS15T B30 B28 DQVLD7T DQS3T DQ4T2 DM3T DQS15T DQ4T2 DQ4T2 DQS15T

B3 VREFB3N1 IO DQ15T C30 A27 DQ7T5 DQ3T5 DQ1T24 DQS4T DQ3T3 DQ15T0 DQS4T DQS4T DQ15T0

B3 VREFB3N1 IO DQ15T A31 A28 DQ7T6 DQ3T6 DQ1T25 DQ4T1 DQ3T2 DQ15T1 DQ4T1 DQ4T1 DQ15T1

B3 VREFB3N1 IO DQ15T A30 C27 DQ7T7 DQ3T7 DQ1T26 DQ4T0 DQS3T DQ15T2 DQ4T0 DQ4T0 DQ15T2

B3 VREFB3N2 IO DQSn15T B31 C28 DQ7T4 DQSn3T DQ1T23 DM3T DQ3T1 DQSB15T DQ3T3 DQSB15T

B3 VREFB3N2 IO DQ15T C31 D27 DQ7T8 DQ3T8 DQ1T27 DQ3T3 DQ3T0 DQ15T3 DQ3T3 DQ3T2 DQ15T3

B3 VREFB3N2 IO K27 F29 DQ3T2 DM2T DQ3T2 DQS3T

B3 VREFB3N2 IO M26 DQS3T DQS3T

B3 VREFB3N2 IO DQS16T A33 C29 DQS8T DQVLD3T DQ3T1 DQ2T3 DQS16T DQ3T1 DQ3T1 DQS16T

B3 VREFB3N2 IO DQ16T A32 A29 DQ8T0 DQ3T10 DQ1T29 DQ3T0 DQ2T2 DQ16T0 DQ3T0 DQ3T0 DQ16T0

B3 VREFB3N2 IO DQ16T C32 D28 DQ8T1 DQ3T11 DQ1T30 DM2T DQS2T DQ16T1 DQ2T3 DQ16T1

B3 VREFB3N2 IO DQ16T C33 E29 DQ8T2 DQ3T12 DQ1T31 DQ2T3 DQ2T1 DQ16T2 DQ2T3 DQ2T2 DQ16T2

B3 VREFB3N2 IO DQSn16T B33 D29 DQSn8T DQ3T9 DQ1T28 DQ2T2 DQ2T0 DQSB16T DQ2T2 DQS2T DQSB16T

B3 VREFB3N2 IO DQ16T A34 B29 DQ8T3 DQ3T13 DQ1T32 DQS2T DM1T DQ16T3 DQS2T DQ2T1 DQ16T3

B3 VREFB3N2 IO J28 K24 DQ2T1 DQ1T3 DQ2T1 DQ2T0

B3 VREFB3N2 IO L27 J24 DQ2T0 DQ1T2 DQ2T0 DQ1T3

B3 VREFB3N2 IO DQS17T A36 A31 DQVLD8T DM1T DQS1T DQS17T DQ1T2 DQS17T

B3 VREFB3N2 IO DQ17T A35 A30 DQ8T5 DQ3T15 DQ1T34 DQ1T3 DQ1T1 DQ17T0 DQ1T3 DQS1T DQ17T0

B3 VREFB3N2 IO DQ17T B34 A32 DQ8T6 DQ3T16 DQ1T35 DQ1T2 DQ1T0 DQ17T1 DQ1T2 DQ1T1 DQ17T1

B3 VREFB3N2 IO DQ17T B37 B32 DQ8T7 DQ3T17 DQS1T DM0T DQ17T2 DQS1T DQ1T0 DQ17T2

VREF Group Pin

Name/Function

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 21

Pin Information for the Stratix® II GX EP2SGX90 Device

V

Page 21 of 47

ersion 1.5

Number

B3 VREFB3N2 IO DQSn17T B36 B31 DQ8T4 DQ3T14 DQ1T33 DQ1T1 DQ0T3 DQSB17T DQ1T1 DQ0T3 DQSB17T

B3 VREFB3N2 IO DQ17T A37 C30 DQ8T8 DQ1T0 DQ0T2 DQ17T3 DQ1T0 DQ0T2 DQ17T3

B3 VREFB3N2 IO E34 DM0T

B3 VREFB3N2 IO M27 J27 DQ0T3 DQS0T DQ0T3 DQS0T

B3 VREFB3N2 VREFB3N2 VREFB3N2 E27 E28

B3 VREFB3N2 IO F30 DQ0T2 DQ0T2

B3 VREFB3N2 IO J30 G29 DQS0T DQ0T1 DQS0T DQ0T1

B3 VREFB3N2 IO H31 H28 DQ0T1 DQ0T0 DQ0T1 DQ0T0

B3 VREFB3N2 IO M28 DQ0T0 DQ0T0

B3 VREFB3N2 IO DATA2 D32 G25

B3 VREFB3N2 IO DATA3 D33 F27

B3 VREFB3N2 IO DATA4 F31 H25

B3 VREFB3N2 IO DATA5 H30 G27

B3 VREFB3N2 IO DATA6 G30 G26

B3 VREFB3N2 IO DATA7 F32 H26

B3 VREFB3N2 IO RDYnBSY G31 F28

B3 VREFB3N2 IO INIT_DONE E33 G28

B3 VREFB3N2 nSTATUS nSTATUS C34 C31

B3 VREFB3N2 nCE nCE D34 D30

B3 VREFB3N2 DCLK DCLK C35 C32

B3 VREFB3N2 CONF_DONE CONF_DONE D35 D31

VREF Group Pin

Name/Function

VCCIO2 P31 P25

VCCIO2 R29 P26

VCCIO2 U31 U25

VCCIO2 V29 U26

VCCIO2 W31

VCCIO1 AA30 AC25

VCCIO1 AC31 AC26

VCCIO1 AD29 Y25

VCCIO1 AF31 Y26

VCCIO1 AG29

VCCIO1 AJ31

VCCIO8 AK21 AE19

VCCIO8 AK23 AE21

VCCIO8 AK26 AF21

VCCIO8 AL23 AG19

VCCIO8 AL26

VCCIO7 AK14 AE12

VCCIO7 AK17 AE15

VCCIO7 AL14 AF12

VCCIO7 AL17 AF15

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

x16/x18

DQ group for DQS

mode

Mode

DQ group for DQS

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 22

V

Number

Page 22 of 47

VREF Group Pin

Name/Function

VCCIO7 AL19

VCCT_B15 W11 AA10

VCCT_B15 Y11 Y10

VCCH_B15 W12 AA11

VCCH_B15 Y12 Y11

VCCR W10 AA9

VCCR Y10 Y9

VCCA W9 Y8

VCCT_B16 AC11

VCCT_B16 AD11

VCCH_B16 AC12

VCCH_B16 AD12

VCCR AC10

VCCR AD10

VCCA AC9

VCCT_B13 K11 M10

VCCT_B13 L11 N10

VCCH_B13 K12 M11

VCCH_B13 L12 N11

VCCR K10 M9

VCCR L10 N9

VCCA K9 M8

VCCT_B14 P11 T10

VCCT_B14 R11 U10

VCCH_B14 P12 T11

VCCH_B14 R12 U11

VCCR P10 T9

VCCR R10 U9

VCCA P9 T8

VCCP W13 AA12

VCCP Y13 Y12

VCCP AC13

VCCP AD13

VCCP K13 M12

VCCP L13 N12

VCCP P13 T12

VCCP R13 U12

VCCIO4 J14 J12

VCCIO4 J17 J15

VCCIO4 J19 K12

VCCIO4 K14 K15

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

DQ group for DQS

mode

x16/x18

Mode

DQ group for DQS

Pin Information for the Stratix® II GX EP2SGX90 Device

ersion 1.5

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 23

V

Number

Page 23 of 47

VREF Group Pin

Name/Function

VCCIO4 K17

VCCIO3 J23 H19

VCCIO3 J26 J21

VCCIO3 K21 K19

VCCIO3 K23 K21

VCCIO3 K26

VCCINT AA15 AA13

VCCINT AA17 AA15

VCCINT AA23 AA17

VCCINT AB14 AA19

VCCINT AB16 AA21

VCCINT AB18 P14

VCCINT AB20 P16

VCCINT AB22 P18

VCCINT AB24 P20

VCCINT AC15 R13

VCCINT AC17 R15

VCCINT AC19 R17

VCCINT AC21 R19

VCCINT AC23 R21

VCCINT AD14 T14

VCCINT AD15 T16

VCCINT AD16 T18

VCCINT AD17 T20

VCCINT AD18 T22

VCCINT AD19 U13

VCCINT AD20 U15

VCCINT AD21 U17

VCCINT AD22 U19

VCCINT AD23 U21

VCCINT AD24 V14

VCCINT T14 V16

VCCINT T15 V18

VCCINT T16 V20

VCCINT T17 W13

VCCINT T18 W15

VCCINT T19 W17

VCCINT T20 W19

VCCINT T21 W21

VCCINT T22 Y14

VCCINT T23 Y16

Optional Function(s) Configuration

Function

F1508 F1152

x8/x9

Mode

DQ group for DQS

mode

x16/x18

Mode

DQ group for DQS

Pin Information for the Stratix® II GX EP2SGX90 Device

ersion 1.5

x32/x36

Mode

mode

DQ group for DQS

mode

DQ group for non-

DQS mode (non-

migratable) F1508

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

DQ group for non-

DQS mode (non-

migratable) F1508

x4 Mode (Note 2)x5 Mode (Note 1)Bank

DQ group for non-

DQS mode (non-

migratable) F1152

DQ group for non-

DQS mode

(migratable) F1508

DQ group for non-

DQS mode

(migratable) F1152

PT-EP2SGX90-1.5

Copyright © 2007 Altera Corp.

Pin List

Page 24

V

Number

Page 24 of 47

VREF Group Pin