Page 1

Stratix Device Handbook, Volume 1

101 Innovation Drive

San Jose, CA 95134

(408) 544-7000

http://www.altera.com

S5V1-3.4

Page 2

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and

service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants

performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera

Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ii Altera Corporation

Page 3

Contents

Chapter Revision Dates .......................................................................... vii

About This Handbook .............................................................................. ix

How to Find Information ........................................................................................................................ ix

How to Contact Altera ............................................................................................................................. ix

Typographic Conventions ........................................................................................................................ x

Section I. Stratix Device Family Data Sheet

Revision History ............................................................................................................................ Part I–1

Chapter 1. Introduction

Introduction ............................................................................................................................................ 1–1

Features ................................................................................................................................................... 1–2

Chapter 2. Stratix Architecture

Functional Description .......................................................................................................................... 2–1

Logic Array Blocks ................................................................................................................................ 2–3

LAB Interconnects ............................................................................................................................ 2–4

LAB Control Signals ......................................................................................................................... 2–5

Logic Elements ....................................................................................................................................... 2–6

LUT Chain & Register Chain .......................................................................................................... 2–8

addnsub Signal ................................................................................................................................. 2–8

LE Operating Modes ........................................................................................................................ 2–8

Clear & Preset Logic Control ........................................................................................................ 2–13

MultiTrack Interconnect ..................................................................................................................... 2–14

TriMatrix Memory ............................................................................................................................... 2–21

Memory Modes ............................................................................................................................... 2–22

Clear Signals .................................................................................................................................... 2–24

Parity Bit Support ........................................................................................................................... 2–24

Shift Register Support .................................................................................................................... 2–25

Memory Block Size ......................................................................................................................... 2–26

Independent Clock Mode .............................................................................................................. 2–44

Input/Output Clock Mode ........................................................................................................... 2–46

Read/Write Clock Mode ............................................................................................................... 2–49

Single-Port Mode ............................................................................................................................ 2–51

Multiplier Block .............................................................................................................................. 2–57

Adder/Output Blocks ................................................................................................................... 2–61

Modes of Operation ....................................................................................................................... 2–64

Altera Corporation iii

Page 4

Contents Stratix Device Handbook, Volume 1

DSP Block Interface ........................................................................................................................ 2–70

PLLs & Clock Networks ..................................................................................................................... 2–73

Global & Hierarchical Clocking ................................................................................................... 2–73

Enhanced & Fast PLLs ................................................................................................................... 2–81

Enhanced PLLs ............................................................................................................................... 2–87

Fast PLLs ........................................................................................................................................ 2–100

I/O Structure ...................................................................................................................................... 2–104

Double-Data Rate I/O Pins ......................................................................................................... 2–111

External RAM Interfacing ........................................................................................................... 2–115

Programmable Drive Strength ................................................................................................... 2–119

Open-Drain Output ...................................................................................................................... 2–120

Slew-Rate Control ........................................................................................................................ 2–120

Bus Hold ........................................................................................................................................ 2–121

Programmable Pull-Up Resistor ................................................................................................ 2–122

Advanced I/O Standard Support .............................................................................................. 2–122

Differential On-Chip Termination ............................................................................................. 2–127

MultiVolt I/O Interface ............................................................................................................... 2–129

High-Speed Differential I/O Support ............................................................................................ 2–130

Dedicated Circuitry ...................................................................................................................... 2–137

Byte Alignment ............................................................................................................................. 2–140

Power Sequencing & Hot Socketing ............................................................................................... 2–140

Chapter 3. Configuration & Testing

IEEE Std. 1149.1 (JTAG) Boundary-Scan Support ............................................................................ 3–1

SignalTap II Embedded Logic Analyzer ............................................................................................ 3–5

Configuration ......................................................................................................................................... 3–5

Operating Modes .............................................................................................................................. 3–5

Configuring Stratix FPGAs with JRunner .................................................................................... 3–7

Configuration Schemes ................................................................................................................... 3–7

Partial Reconfiguration .................................................................................................................... 3–7

Remote Update Configuration Modes .......................................................................................... 3–8

Stratix Automated Single Event Upset (SEU) Detection ................................................................ 3–12

Custom-Built Circuitry .................................................................................................................. 3–13

Software Interface ........................................................................................................................... 3–13

Temperature Sensing Diode ............................................................................................................... 3–13

Chapter 4. DC & Switching Characteristics

Operating Conditions ........................................................................................................................... 4–1

Power Consumption ........................................................................................................................... 4–17

Timing Model ....................................................................................................................................... 4–19

Preliminary & Final Timing .......................................................................................................... 4–19

Performance .................................................................................................................................... 4–20

Internal Timing Parameters .......................................................................................................... 4–22

External Timing Parameters ......................................................................................................... 4–33

Stratix External I/O Timing .......................................................................................................... 4–36

I/O Timing Measurement Methodology .................................................................................... 4–60

External I/O Delay Parameters .................................................................................................... 4–66

iv Altera Corporation

Page 5

Contents Contents

Maximum Input & Output Clock Rates ...................................................................................... 4–76

High-Speed I/O Specification ........................................................................................................... 4–87

PLL Specifications ................................................................................................................................ 4–94

DLL Specifications ............................................................................................................................. 4–102

Chapter 5. Reference & Ordering Information

Software .................................................................................................................................................. 5–1

Device Pin-Outs ..................................................................................................................................... 5–1

Ordering Information ........................................................................................................................... 5–1

Index

Altera Corporation v

Page 6

Contents Stratix Device Handbook, Volume 1

vi Altera Corporation

Page 7

Chapter Revision Dates

The chapters in this book, Stratix Device Handbook, Volume 1, were revised on the following dates.

Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: July 2005

Part number: S51001-3.2

Chapter 2. Stratix Architecture

Revised: July 2005

Part number: S51002-3.2

Chapter 3. Configuration & Testing

Revised: July 2005

Part number: S51003-1.3

Chapter 4. DC & Switching Characteristics

Revised: January 2006

Part number: S51004-3.4

Chapter 5. Reference & Ordering Information

Revised: September 2004

Part number: S51005-2.1

Altera Corporation vii

Page 8

Chapter Revision Dates Stratix Device Handbook, Volume 1

viii Altera Corporation

Page 9

About This Handbook

This handbook provides comprehensive information about the Altera®

Stratix family of devices.

How to Find Information

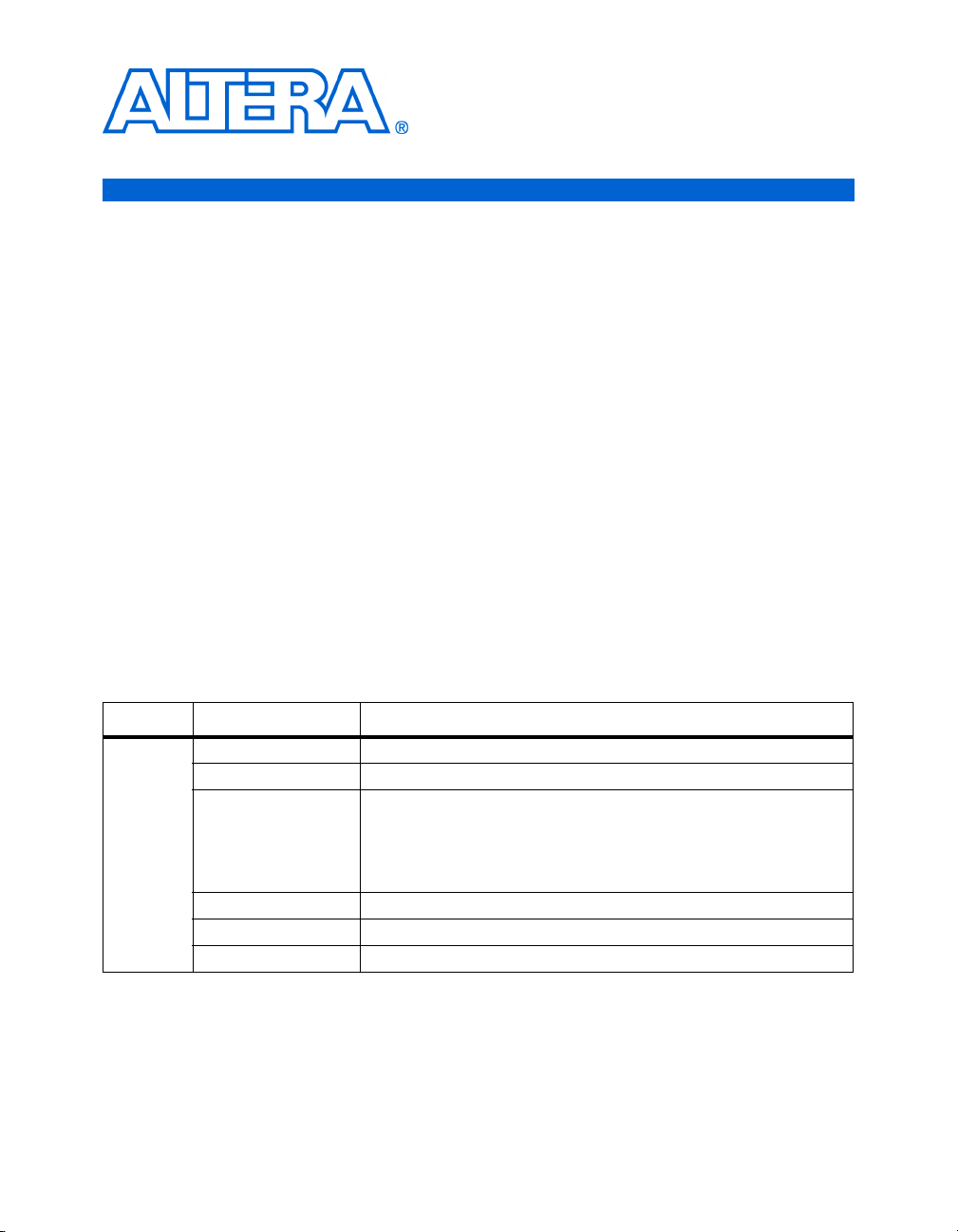

How to Contact Altera

Information Type USA & Canada All Other Locations

Technical support www.altera.com/mysupport/ www.altera.com/mysupport/

Product literature www.altera.com www.altera.com

Altera literature services literature@altera.com literature@altera.com

Non-technical customer

service

FTP site ftp.altera.com ftp.altera.com

You can find more information in the following ways:

■ The Adobe Acrobat Find feature, which searches the text of a PDF

document. Click the binoculars toolbar icon to open the Find dialog

box.

■ Acrobat bookmarks, which serve as an additional table of contents in

PDF documents.

■ Thumbnail icons, which provide miniature previews of each page,

provide a link to the pages.

■ Numerous links, shown in green text, which allow you to jump to

related information.

For the most up-to-date information about Altera products, go to the

Altera world-wide web site at www.altera.com. For technical support on

this product, go to www.altera.com/mysupport. For additional

information about Altera products, consult the sources shown below.

(800) 800-EPLD (3753)

(7:00 a.m. to 5:00 p.m. Pacific Time)

(800) 767-3753 + 1 408-544-7000

+1 408-544-8767

7:00 a.m. to 5:00 p.m. (GMT -8:00)

Pacific Time

7:00 a.m. to 5:00 p.m. (GMT -8:00)

Pacific Time

Altera Corporation ix

Page 10

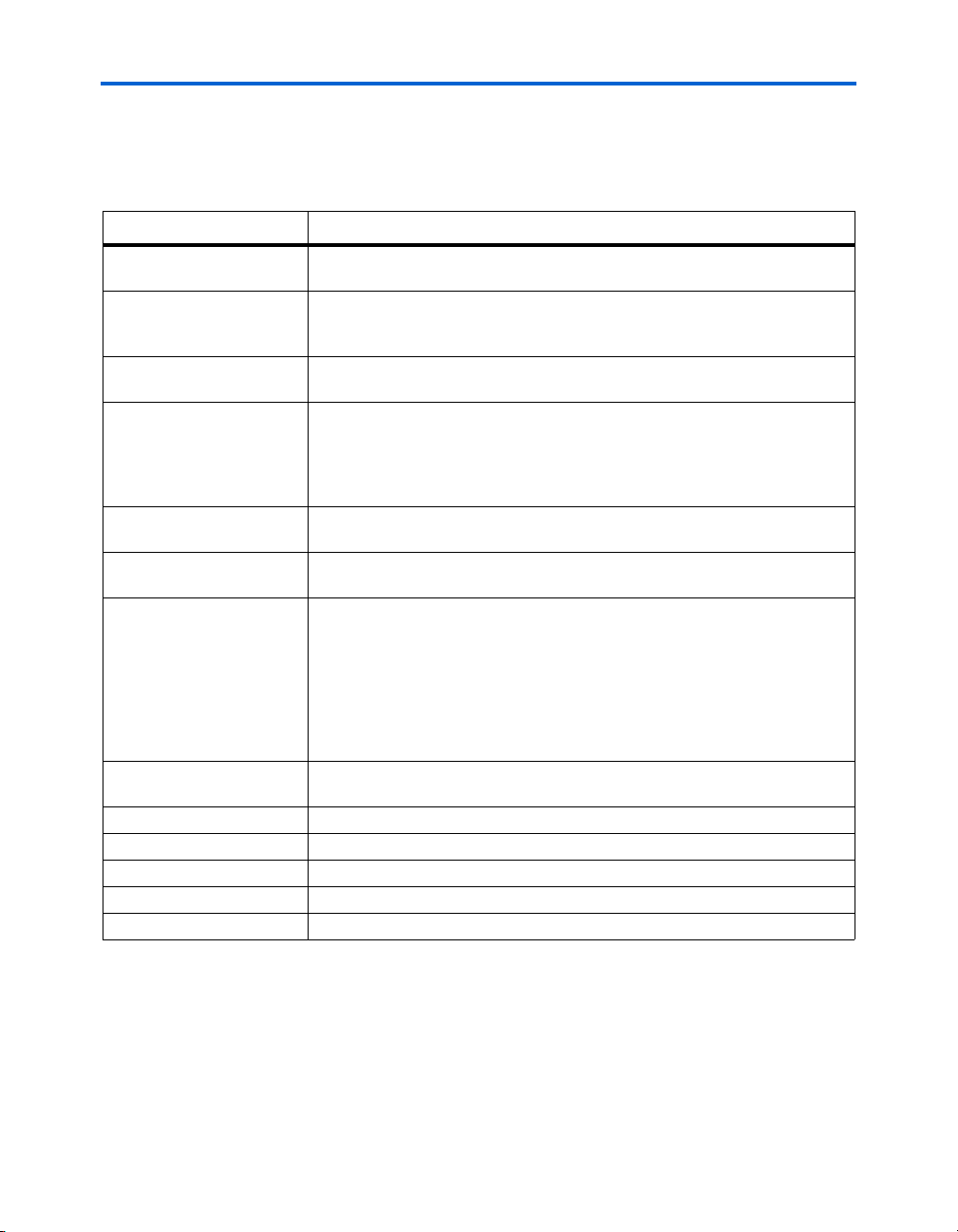

Typographic Conventions Stratix Device Handbook, Volume 1

Typographic

This document uses the typographic conventions shown below.

Conventions

Visual Cue Meaning

Bold Type with Initial

Capital Letters

bold type External timing parameters, directory names, project names, disk drive names,

Italic Type with Initial Capital

Letters

Italic type Internal timing parameters and variables are shown in italic type.

Initial Capital Letters Keyboard keys and menu names are shown with initial capital letters. Examples:

“Subheading Title” References to sections within a document and titles of on-line help topics are

Courier type Signal and port names are shown in lowercase Courier type. Examples: data1,

1., 2., 3., and

a., b., c., etc.

● • Bullets are used in a list of items when the sequence of the items is not important.

■

v The checkmark indicates a procedure that consists of one step only.

1 The hand points to information that requires special attention.

r The angled arrow indicates you should press the Enter key.

f The feet direct you to more information on a particular topic.

Command names, dialog box titles, checkbox options, and dialog box options are

shown in bold, initial capital letters. Example: Save As dialog box.

filenames, filename extensions, and software utility names are shown in bold

type. Examples: f

Document titles are shown in italic type with initial capital letters. Example: AN 75:

High-Speed Board Designs.

Examples: t

Variable names are enclosed in angle brackets (< >) and shown in italic type.

Example: <file name>, <project name>.pof file.

Delete key, the Options menu.

shown in quotation marks. Example: “Typographic Conventions.”

PIA

, \qdesigns directory, d: drive, chiptrip.gdf file.

MAX

, n + 1.

tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.

Anything that must be typed exactly as it appears is shown in Courier type. For

example:

actual file, such as a Report File, references to parts of files (e.g., the AHDL

keyword

Courier.

Numbered steps are used in a list of items when the sequence of the items is

important, such as the steps listed in a procedure.

c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an

SUBDESIGN), as well as logic function names (e.g., TRI) are shown in

x Altera Corporation

Page 11

Section I. Stratix Device

Family Data Sheet

This section provides the data sheet specifications for Stratix® devices.

They contain feature definitions of the internal architecture,

configuration and JTAG boundary-scan testing information, DC

operating conditions, AC timing parameters, a reference to power

consumption, and ordering information for Stratix devices.

This section contains the following chapters:

■ Chapter 1, Introduction

■ Chapter 2, Stratix Architecture

■ Chapter 3, Configuration & Testing

■ Chapter 4, DC & Switching Characteristics

■ Chapter 5, Reference & Ordering Information

Revision History

The table below shows the revision history for Chapters 1 through 5.

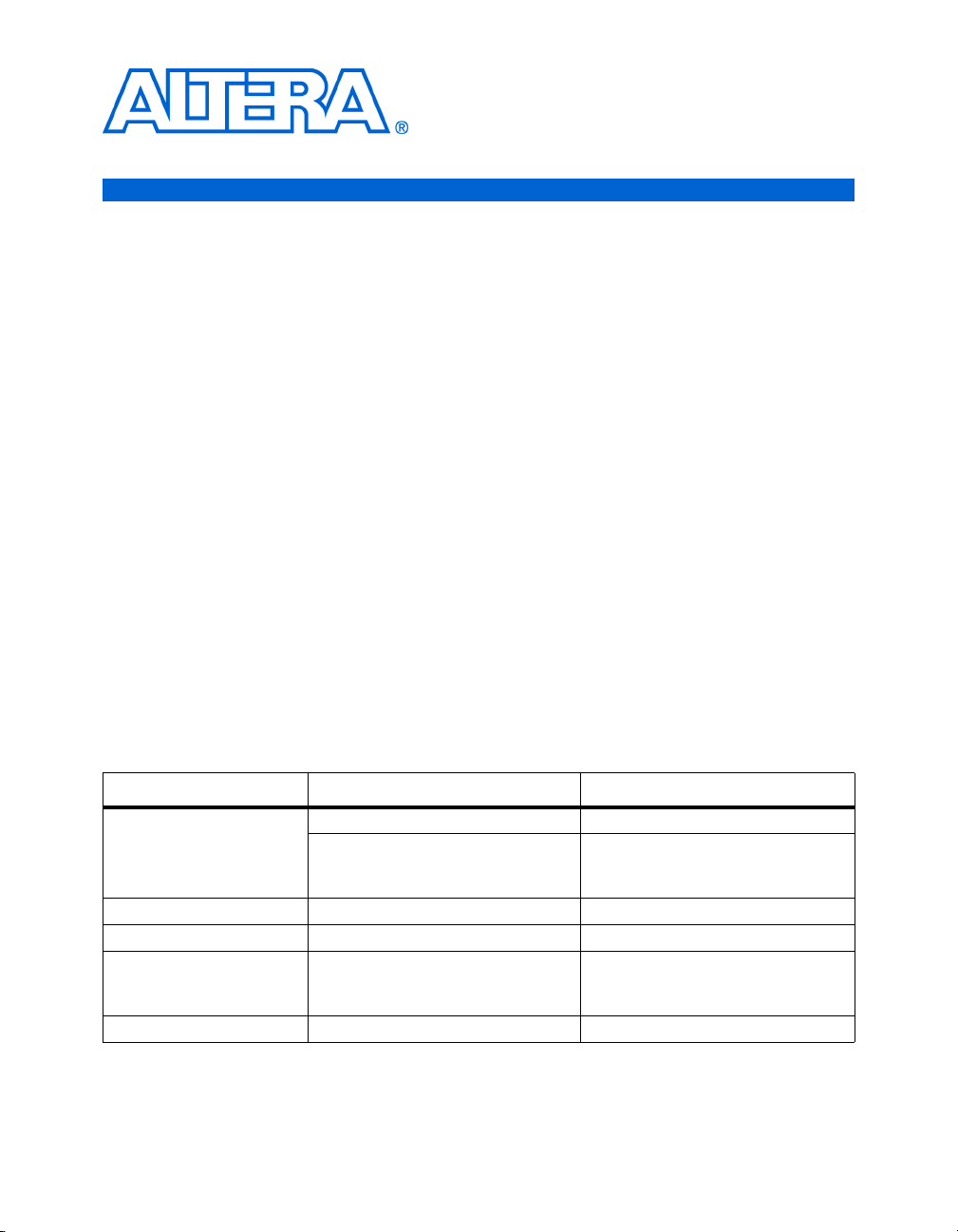

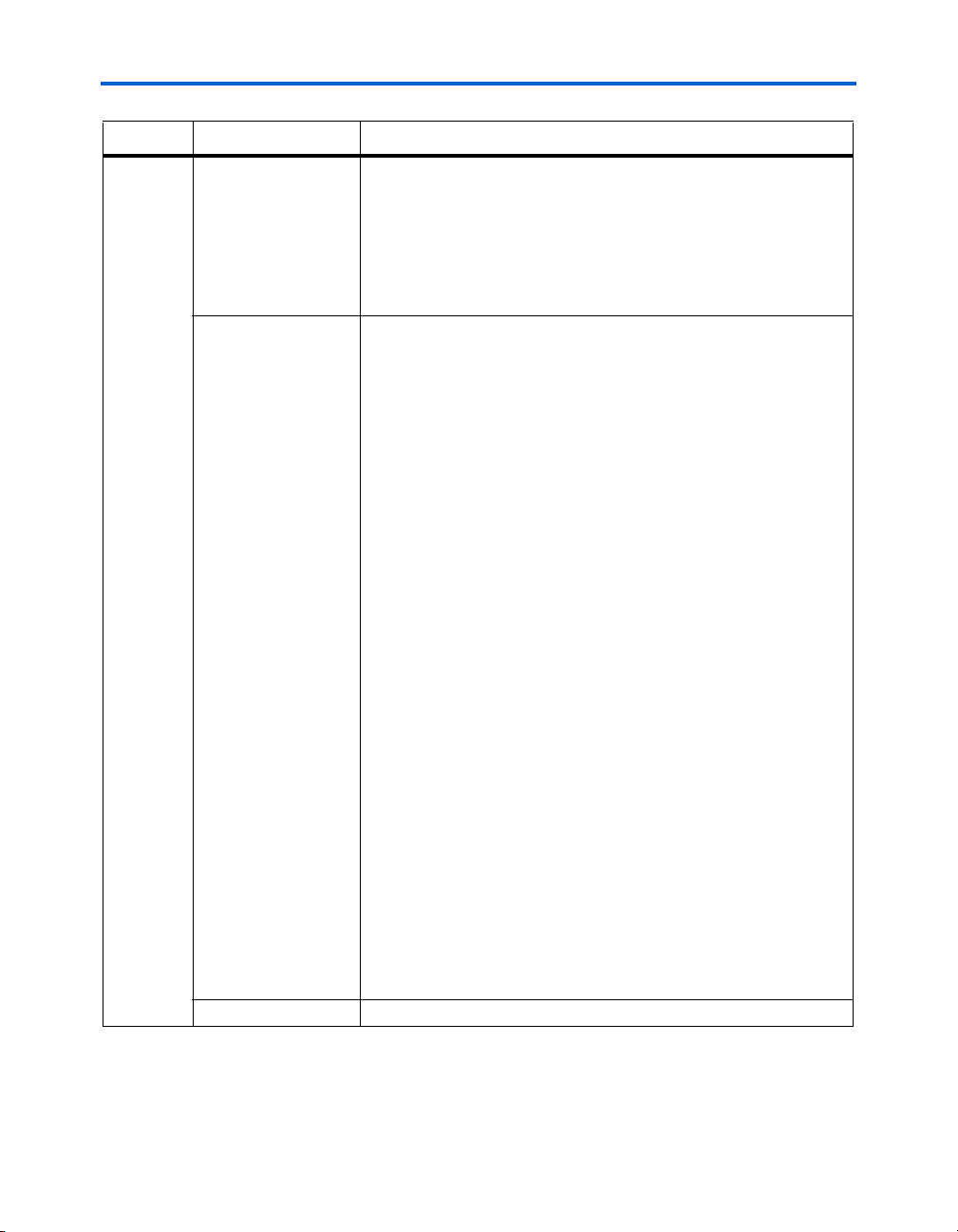

Chapter Date/Version Changes Made

1 July 2005, v3.2 ● Minor content changes.

September 2004, v3.1

April 2004, v3.0

January 2004, v2.2

October 2003, v2.1

July 2003, v2.0

Altera Corporation Section I–1

● Updated Table 1–6 on page 1–5.

● Main section page numbers changed on first page.

● Changed PCI-X to PCI-X 1.0 in “Features” on page 1–2.

● Global change from SignalTap to SignalTap II.

● The DSP blocks in “Features” on page 1–2 provide dedicated

implementation of multipliers that are now “faster than 300 MHz.”

● Updated -5 speed grade device information in Table 1-6.

● Add -8 speed grade device information.

● Format changes throughout chapter.

Page 12

Stratix Device Family Data Sheet Stratix Device Handbook, Volume 1

Chapter Date/Version Changes Made

2 July 2005 v3.2 ● Added “Clear Signals” section.

● Updated “Power Sequencing & Hot Socketing” section.

● Format changes.

September 2004, v3.1

April 2004, v3.0

November 2003, v2.2

October 2003, v2.1

● Updated fast regional clock networks description on page 2–73.

● Deleted the word preliminary from the “specification for the maximum

time to relock is 100 µs” on page 2–90.

● Added information about differential SSTL and HSTL outputs in

“External Clock Outputs” on page 2–92.

● Updated notes in Figure 2–55 on page 2–93.

● Added information about m counter to “Clock Multiplication &

Division” on page 2–101.

● Updated Note 1 in Table 2–58 on page 2–101.

● Updated description of “Clock Multiplication & Division” on

page 2–88.

● Updated Table 2–22 on page 2–102.

● Added references to AN 349 and AN 329 to “External RAM

Interfacing” on page 2–115.

● Table 2–25 on page 2–116: updated the table, updated Notes 3 and

4. Notes 4, 5, and 6, are now Notes 5, 6, and 7, respectively.

● Updated Table 2–26 on page 2–117.

● Added information about PCI Compliance to page 2–120.

● Table 2–32 on page 2–126: updated the table and deleted Note 1.

● Updated reference to device pin-outs now being available on the web

on page 2–130.

● Added Notes 4 and 5 to Table 2–36 on page 2–130.

● Updated Note 3 in Table 2–37 on page 2–131.

● Updated Note 5 in Table 2–41 on page 2–135.

● Added note 3 to rows 11 and 12 in Table 2–18.

● Deleted “Stratix and Stratix GX Device PLL Availability” table.

● Added I/O standards row in Table 2–28 that support max and min

strength.

● Row clk [1,3,8,10] was removed from Ta bl e 2 – 30 .

● Added checkmarks in Enhanced column for LVPECL, 3.3-V PCML,

LVDS, and HyperTransport technology rows in Table 2–32.

● Removed the Left and Right I/O Banks row in Table 2–34.

● Changed RCLK values in Figures 2–50 and 2–51.

● External RAM Interfacing section replaced.

● Added 672-pin BGA package information in Table 2–37.

● Removed support for series and parallel on-chip termination.

● Termination Technology renamed differential on-chip termination.

● Updated the number of channels per PLL in Tables 2-38 through 2-

42.

● Updated Figures 2–65 and 2–67.

● Updated DDR I information.

● Updated Table 2–22.

● Added Tables 2–25, 2–29, 2–30, and 2–72.

● Updated Figures 2–59, 2–65, and 2–67.

● Updated the Lock Detect section.

Section I–2 Altera Corporation

Page 13

Stratix Device Family Data Sheet

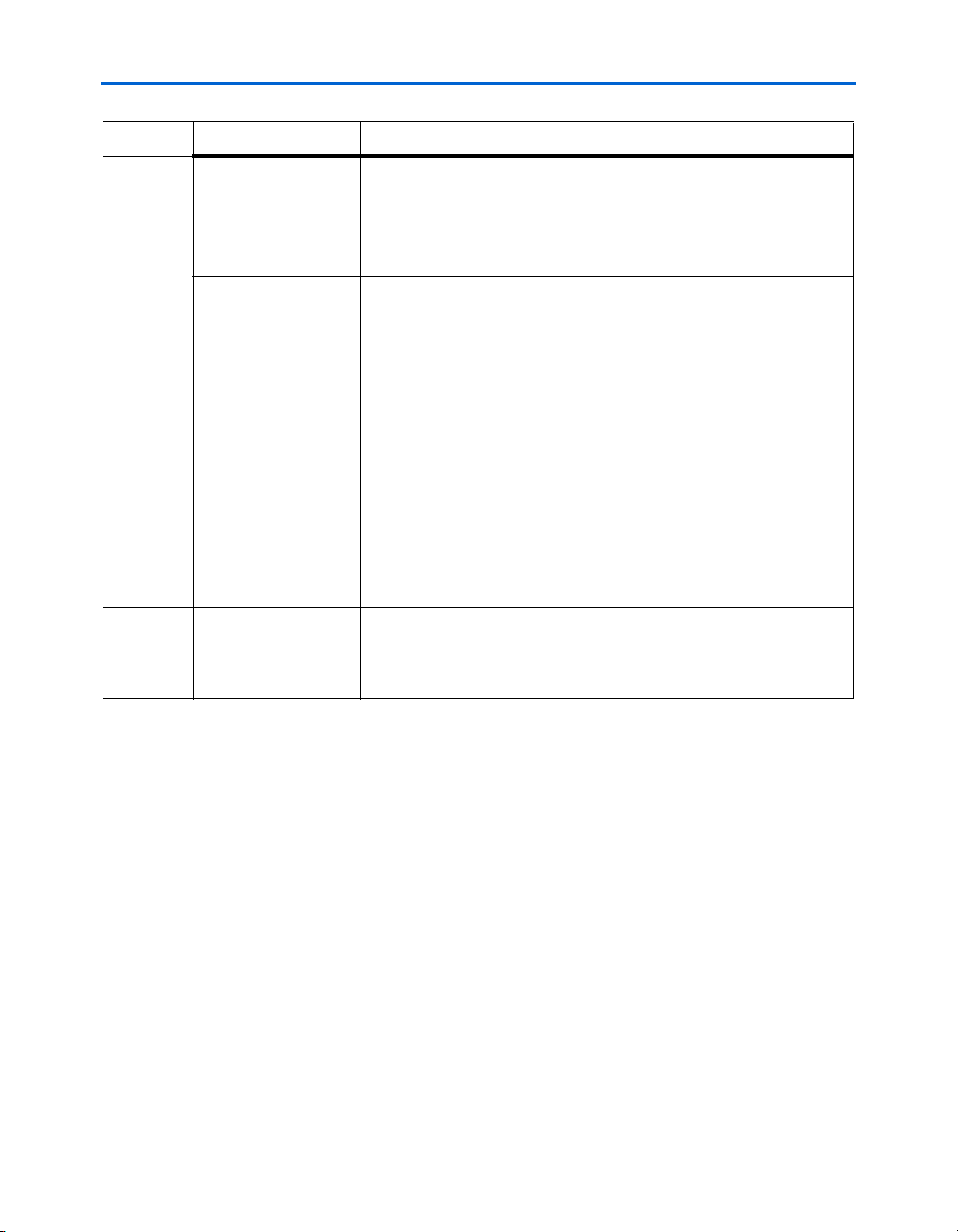

Chapter Date/Version Changes Made

2 July 2003, v2.0

3 July 2005, v1.3

January 2005, v1.2

September 2004, v1.1

April 2003, v1.0

4 January 2006, v3.4

July 2005, v3.3

● Added reference on page 2-73 to Figures 2-50 and 2-51 for RCLK

connections.

● Updated ranges for EPLL post-scale and pre-scale dividers on page

2-85.

● Updated PLL Reconfiguration frequency from 25 to 22 MHz on page

2-87.

● New requirement to assert are set signal each PLL when it has to re-

acquire lock on either a new clock after loss of lock (page 2-96).

● Updated max input frequency for CLK[1,3,8,10] from 462 to 500,

Table 2-24.

● Renamed impedance matching to series termination throughout.

● Updated naming convention for DQS pins on page 2-112 to match pin

tables.

● Added DDR SDRAM Performance Specification on page 2-117.

● Added external reference resistor values for terminator technology

(page 2-136).

● Added Terminator Technology Specification on pages 2-137 and 2-

138.

● Updated Tables 2-45 to 2-49 to reflect PLL cross-bank support for

high speed differential channels at full speed.

● Wire bond package performance specification for “high” speed

channels was increased to 624 Mbps from 462 Mbps throughout

chapter.

● Updated “Operating Modes” section.

● Updated “Temperature Sensing Diode” section.

● Updated “IEEE Std. 1149.1 (JTAG) Boundary-Scan Support” section.

● Updated “Configuration” section.

● Updated limits for JTAG chain of devices.

● Added new section, “Stratix Automated Single Event Upset (SEU)

Detection” on page 3–12.

● Updated description of “Custom-Built Circuitry” on page 3–13.

● No new changes in Stratix Device Handbook v2.0.

● Added Table 4–135.

● Updated Tables 4–6 and 4–30.

● Updated Tables 4–103 through 4–108.

● Updated Tables 4–114 through 4–124.

● Updated Table 4–129.

● Added Table 4–130.

Altera Corporation Section I–3

Page 14

Stratix Device Family Data Sheet Stratix Device Handbook, Volume 1

Chapter Date/Version Changes Made

4 January 2005, 3.2 ● Updated rise and fall input values.

September 2004, v3.1

● Updated Note 3 in Table 4–8 on page 4–4.

● Updated Table 4–10 on page 4–6.

● Updated Table 4–20 on page 4–12 through Table 4–23 on

page 4–13. Added rows V

● Updated Table 4–26 on page 4–14 through Table 4–29 on

IL(AC)

and V

to each table.

IH(AC)

page 4–15.

● Updated Table 4–31 on page 4–16.

● Updated description of “External Timing Parameters” on page 4–33.

● Updated Table 4–36 on page 4–20.

● Added signals t

● Added rows t

, TXZ, and TZX to Figure 4–4 on page 4–33.

OUTCO

M512CLKENSU

and t

M512CLKENH

to Table 4–40 on

page 4–24.

● Added rows t

● Updated Note 2 in Table 4–54 on page 4–35.

● Added rows t

M4CLKENSU

MRAMCLKENSU

and t

and t

M4CLKENH

MRAMCLKENH

to Table 4–41 on page 4–24.

to Table 4–42 on

page 4–25.

● Updated Table 4–46 on page 4–29.

● Updated Table 4–47 on page 4–29.

Section I–4 Altera Corporation

Page 15

Stratix Device Family Data Sheet

Chapter Date/Version Changes Made

4 ● Table 4–48 on page 4–30: added rows t

and updated symbol names.

● Updated power-up current (ICCINT) required to power a Stratix

device on page 4–17.

● Updated Table 4–37 on page 4–22 through Table 4–43 on

page 4–27.

● Table 4–49 on page 4–31: added rows t

, and t

t

M4KBESU

updated symbol names.

● Table 4–50 on page 4–31: added rows t

t

MRAMBESU

t

MRAMRADDRH

● Table 4–52 on page 4–34: updated table, deleted “Conditions”

, and t

, and updated symbol names.

column, and added rows t

● Table 4–52 on page 4–34: updated table, deleted “Conditions”

column, and added rows t

● Table 4–53 on page 4–34: updated table and added rows t

t

.

ZXPLL

● Updated Note 2 in Table 4–53 on page 4–34.

● Table 4–54 on page 4–35: updated table, deleted “Conditions”

column, and added rows t

● Updated Note 2 in Table 4–54 on page 4–35.

● Deleted Note 2 from Table 4–55 on page 4–36 through Table 4–66 on

page 4–41.

● Updated Table 4–55 on page 4–36 through Table 4–96 on

page 4–56. Added rows T

● Added Note 4 to Table 4–101 on page 4–62.

● Deleted Note 1 from Table 4–67 on page 4–42 through Table 4–84 on

page 4–50.

● Added new section “I/O Timing Measurement Methodology” on

page 4–60.

● Deleted Note 1 from Table 4–67 on page 4–42 through Table 4–84 on

page 4–50.

● Deleted Note 2 from Table 4–85 on page 4–51 through Table 4–96 on

page 4–56.

● Added Note 4 to Table 4–101 on page 4–62.

● Table 4–102 on page 4–64: updated table and added Note 4.

● Updated description of “External I/O Delay Parameters” on

page 4–66.

● Added Note 1 to Table 4–109 on page 4–73 and Table 4–110 on

page 4–74.

● Updated Table 4–103 on page 4–66 through Table 4–110 on

page 4–74.

● Deleted Note 2 from Table 4–103 on page 4–66 through Table 4–106

on page 4–69.

● Added new paragraph about output adder delays on page 4–68.

● Updated Table 4–110 on page 4–74.

● Added Note 1 to Table 4–111 through Table 4–113 on page 4–75.

M4KBEH,

MRAMBEH

deleted rows t

, deleted rows t

and tZX.

XZ

and tZX.

XZ

and t

XZPLL

, TZX, T

XZ

M4KRADDRASU

ZXPLL

XZPLL

M512CLKSENSU

M4KCLKENSU

and t

MRAMCLKENSU

MRAMADDRASU

.

, and T

ZXPLL.

and t

, t

M4KCLKENH

M4KRADDRH

, t

MRAMCLKENH

and

M512CLKENH

,

, and

,

and

XZPLL

,

Altera Corporation Section I–5

Page 16

Stratix Device Family Data Sheet Stratix Device Handbook, Volume 1

Chapter Date/Version Changes Made

4 ● Updated Table 4–123 on page 4–85 through Table 4–126 on

page 4–92.

● Updated Note 3 in Table 4–123 on page 4–85.

● Table 4–125 on page 4–88: moved to correct order in chapter, and

updated table.

● Updated Table 4–126 on page 4–92.

● Updated Table 4–127 on page 4–94.

● Updated Table 4–128 on page 4–95.

April 2004, v3.0

November 2003, v2.2

● Table 4–129 on page 4–96: updated table and added Note 10.

● Updated Table 4–131 and Table 4–132 on page 4–100.

● Updated Table 4–110 on page 4–74.

● Updated Table 4–123 on page 4–85.

● Updated Table 4–124 on page 4–87. through Table 4–126 on

page 4–92.

● Added Note 10 to Table 4–129 on page 4–96.

● Moved Table 4–127 on page 4–94 to correct order in the chapter.

● Updated Table 4–131 on page 4–100 through Table 4–132 on

page 4–100.

● Deleted t

● Waveform was added to Figure 4–6.

● The minimum and maximum duty cycle values in Note 3 of Table 4–8

and tZX from Figure 4–4.

XZ

were moved to a new Tab l e 4 – 9 .

● Changes were made to values in SSTL-3 Class I and II rows in

Table 4–17.

● Note 1 was added to Table 4–34.

● Added t

● Changed Table 4–55 title from “EP1S10 Column Pin Fast Regional

SU_R

and t

rows in Table 4–38.

SU_C

Clock External I/O Timing Parameters” to “EP1S10 External I/O

Timing on Column Pins Using Fast Regional Clock Networks.”

● Changed values in Tables 4–46, 4–48 to 4–51, 4–128, and 4–131.

● Added t

● Deleted -5 Speed Grade column in Tables 4–117 to 4–119 and 4–122

row in Tables 4–127 to 4–132.

ARESET

to 4–123.

● Fixed differential waveform in Figure 4–1.

● Added “Definition of I/O Skew” section.

● Added t

t

CLKHL

● Values changed in the t

● Values changed in the t

● Values changed in the t

● Added Ta b l e 4 – 5 1 to “Internal Timing Parameters” section.

● The timing information is preliminary in Tables 4–55 through 4–96.

● Table 4–111 was separated into 3 tables: Tables 4–111 to 4–113.

● Updated Tables 4–127 through 4–129.

SU

and t

rows and made changes to values in t

CO_C

rows in Table 4–46.

SU

M4KCLKHL

MRAMCLKHL

and tH rows in Table 4–47.

row in Table 4–49.

row in Table 4–50.

PRE

and

Section I–6 Altera Corporation

Page 17

Stratix Device Family Data Sheet

Chapter Date/Version Changes Made

4 October 2003, v2.1 ● Added -8 speed grade information.

● Updated performance information in Table 4–36.

● Updated timing information in Tables 4–55 through 4–96.

● Updated delay information in Tables 4–103 through 4–108.

● Updated programmable delay information in Tables 4–100 and

4–103.

July 2003, v2.0

5 September 2004, v2.1

April 2003, v1.0

● Updated clock rates in Tables 4–114 through 4–123.

● Updated speed grade information in the introduction on page 4-1.

● Corrected figures 4-1 & 4-2 and Table 4-9 to reflect how VID and VOD

are specified.

● Added note 6 to Table 4-32.

● Updated Stratix Performance Table 4-35.

● Updated EP1S60 and EP1S80 timing parameters in Tables 4-82 to 4-

93. The Stratix timing models are final for all devices.

● Updated Stratix IOE programmable delay chains in Tables 4-100 to 4-

101.

● Added single-ended I/O standard output pin delay adders for loading

in Table 4-102.

● Added spec for FPLL[10..7]CLK pins in Tables 4-104 and 4-107.

● Updated high-speed I/O specification for J=2 in Tables 4-114 and 4-

115.

● Updated EPLL specification and fast PLL specification in Tables 4-

116 to 4-120.

● Updated reference to device pin-outs on page 5–1 to indicate that

device pin-outs are no longer included in this manual and are now

available on the Altera web site.

● No new changes in Stratix Device Handbook v2.0.

Altera Corporation Section I–7

Page 18

Stratix Device Family Data Sheet Stratix Device Handbook, Volume 1

Section I–8 Altera Corporation

Page 19

S51001-3.2

1. Introduction

Introduction

The Stratix® fa mi ly of FPGAs is based o n a 1.5-V, 0.13-µm, all-layer copper

SRAM process, with densities of up to 79,040 logic elements (LEs) and up

to 7.5 Mbits of RAM. Stratix devices offer up to 22 digital signal

processing (DSP) blocks with up to 176 (9-bit × 9-bit) embedded

multipliers, optimized for DSP applications that enable efficient

implementation of high-performance filters and multipliers. Stratix

devices support various I/O standards and also offer a complete clock

management solution with its hierarchical clock structure with up to

420-MHz performance and up to 12 phase-locked loops (PLLs).

The following shows the main sections in the Stratix Device Family Data

Sheet:

Section Page

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1–2

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–1

Logic Array Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–3

Logic Elements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–6

MultiTrack Interconnect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–14

TriMatrix Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–21

Digital Signal Processing Block . . . . . . . . . . . . . . . . . . . . . . . . 2–52

PLLs & Clock Networks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–73

I/O Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2–104

High-Speed Differential I/O Support. . . . . . . . . . . . . . . . . . 2–130

Power Sequencing & Hot Socketing . . . . . . . . . . . . . . . . . . . 2–140

IEEE Std. 1149.1 (JTAG) Boundary-Scan Support. . . . . . . . . . 3–1

SignalTap II Embedded Logic Analyzer . . . . . . . . . . . . . . . . . 3–5

Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3–5

Temperature Sensing Diode. . . . . . . . . . . . . . . . . . . . . . . . . . . 3–13

Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–1

Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–17

Timing Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–19

Software. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

Device Pin-Outs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5–1

Altera Corporation 1–1

July 2005

Page 20

Features

Features

The Stratix family offers the following features:

■ 10,570 to 79,040 LEs; see Table 1–1

■ Up to 7,427,520 RAM bits (928,440 bytes) available without reducing

logic resources

■ TriMatrix

TM

memory consisting of three RAM block sizes to

implement true dual-port memory and first-in first-out (FIFO)

buffers

■ High-speed DSP blocks provide dedicated implementation of

multipliers (faster than 300 MHz), multiply-accumulate functions,

and finite impulse response (FIR) filters

■ Up to 16 global clocks with 22 clocking resources per device region

■ Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device

provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication

and phase shifting

■ Support for numerous single-ended and differential I/O standards

■ High-speed differential I/O support on up to 116 channels with up

to 80 channels optimized for 840 megabits per second (Mbps)

■ Support for high-speed networking and communications bus

standards including RapidIO, UTOPIA IV, CSIX, HyperTransportTM

technology, 10G Ethernet XSBI, SPI-4 Phase 2 (POS-PHY Level 4),

and SFI-4

■ Differential on-chip termination support for LVDS

■ Support for high-speed external memory, including zero bus

turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM,

double data rate (DDR) SDRAM, DDR fast cycle RAM (FCRAM),

and single data rate (SDR) SDRAM

■ Support for 66-MHz PCI (64 and 32 bit) in -6 and faster speed-grade

devices, support for 33-MHz PCI (64 and 32 bit) in -8 and faster

speed-grade devices

■ Support for 133-MHz PCI-X 1.0 in -5 speed-grade devices

■ Support for 100-MHz PCI-X 1.0 in -6 and faster speed-grade devices

■ Support for 66-MHz PCI-X 1.0 in -7 speed-grade devices

■ Support for multiple intellectual property megafunctions from

Altera MegaCore® functions and Altera Megafunction Partners

SM

Program (AMPP

■ Support for remote configuration updates

) megafunctions

1–2 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 21

Introduction

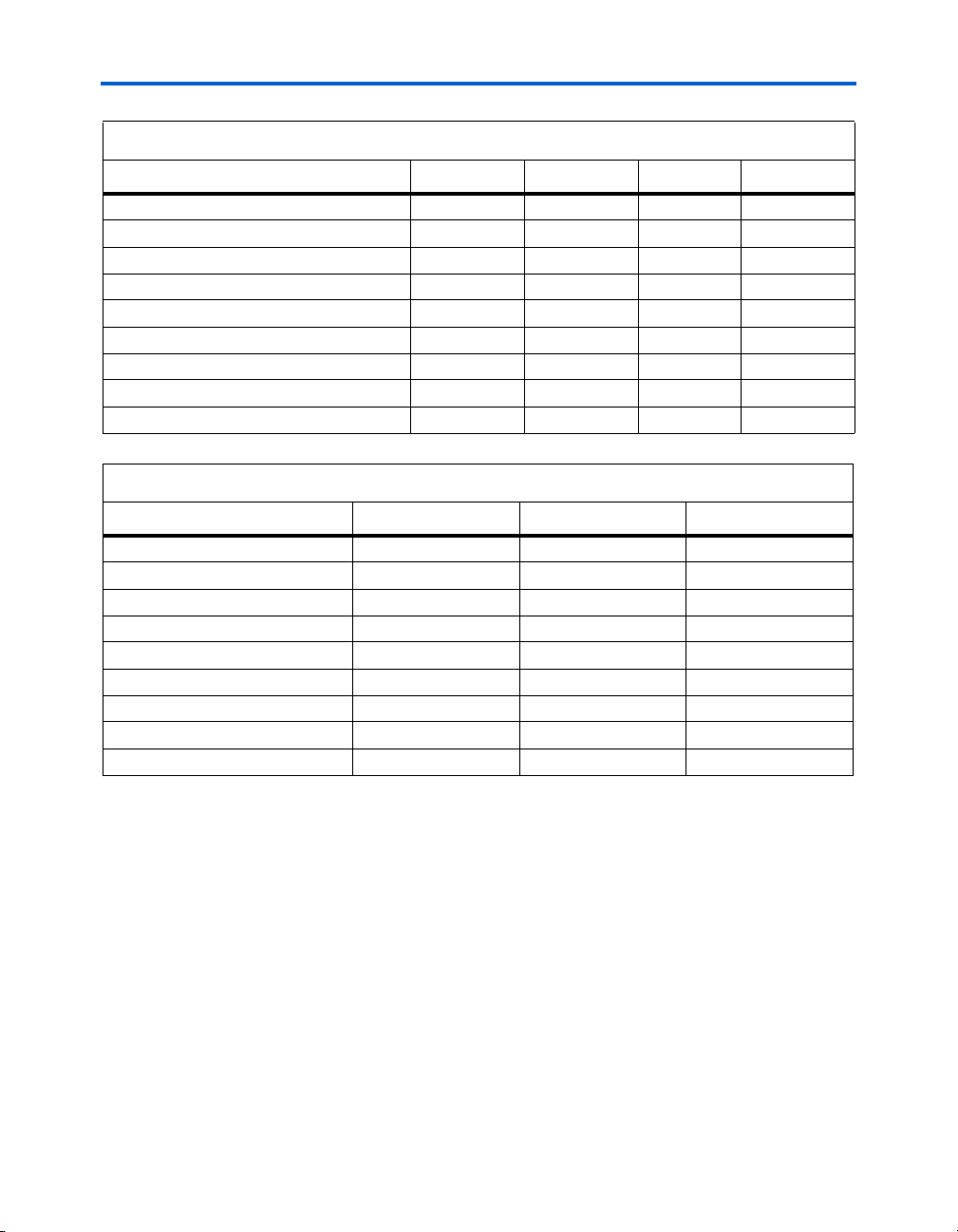

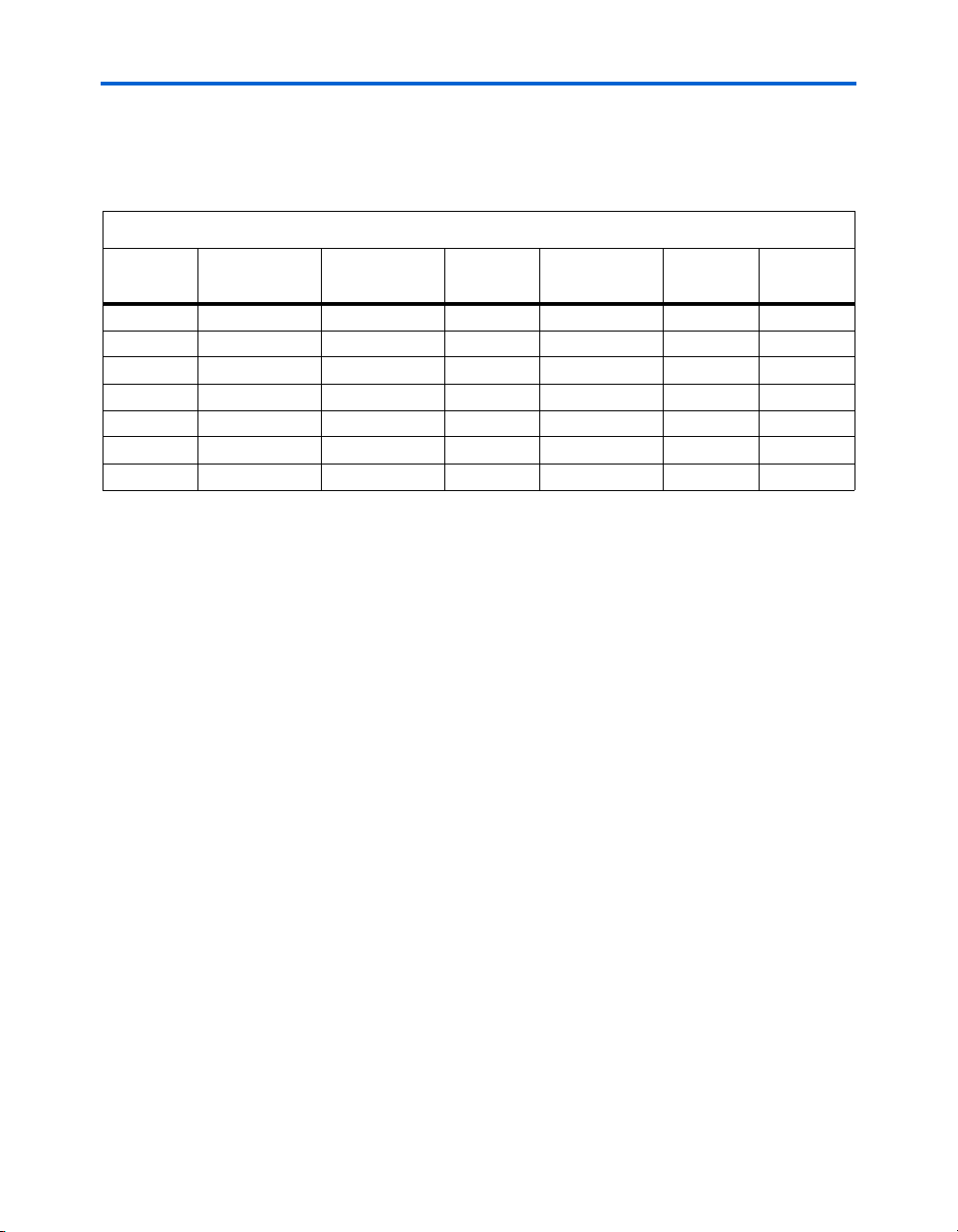

Table 1–1. Stratix Device Features — EP1S10, EP1S20, EP1S25, EP1S30

Feature EP1S10 EP1S20 EP1S25 EP1S30

LEs 10,570 18,460 25,660 32,470

M512 RAM blocks (32 × 18 bits) 94 194 224 295

M4K RAM blocks (128 × 36 bits) 60 82 138 171

M-RAM blocks (4K × 144 bits) 1 2 2 4

Total RAM bits 920,448 1,669,248 1,944,576 3,317,184

DSP blocks 6 101012

Embedded multipliers (1) 48 80 80 96

PLLs 6 6 6 10

Maximum user I/O pins 426 586 706 726

Table 1–2. Stratix Device Features — EP1S40, EP1S60, EP1S80

Feature EP1S40 EP1S60 EP1S80

LEs 41,250 57,120 79,040

M512 RAM blocks (32 × 18 bits) 384 574 767

M4K RAM blocks (128 × 36 bits) 183 292 364

M-RAM blocks (4K × 144 bits) 4 6 9

Total RAM bits 3,423,744 5,215,104 7,427,520

DSP blocks 14 18 22

Embedded multipliers (1) 112 144 176

PLLs 12 12 12

Maximum user I/O pins 822 1,022 1,238

Note to Ta b le s 1 – 1 and 1–2:

(1) This parameter lists the total number of 9 × 9-bit multipliers for each device. For the total number of 18 × 18-bit

multipliers per device, divide the total number of 9 × 9-bit multipliers by 2. For the total number of 36 × 36-bit

multipliers per device, divide the total number of 9 × 9-bit multipliers by 8.

Altera Corporation 1–3

July 2005 Stratix Device Handbook, Volume 1

Page 22

Features

Stratix devices are available in space-saving FineLine BGA® and ball-grid

array (BGA) packages (see Tables 1–3 through 1–5). All Stratix devices

support vertical migration within the same package (for example, you

can migrate between the EP1S10, EP1S20, and EP1S25 devices in the 672pin BGA package). Vertical migration means that you can migrate to

devices whose dedicated pins, configuration pins, and power pins are the

same for a given package across device densities. For I/O pin migration

across densities, you must cross-reference the available I/O pins using

the device pin-outs for all planned densities of a given package type to

identify which I/O pins are migrational. The Quartus

automatically cross reference and place all pins except differential pins

for migration when given a device migration list. You must use the pinouts for each device to verify the differential placement migration. A

future version of the Quartus II software will support differential pin

migration.

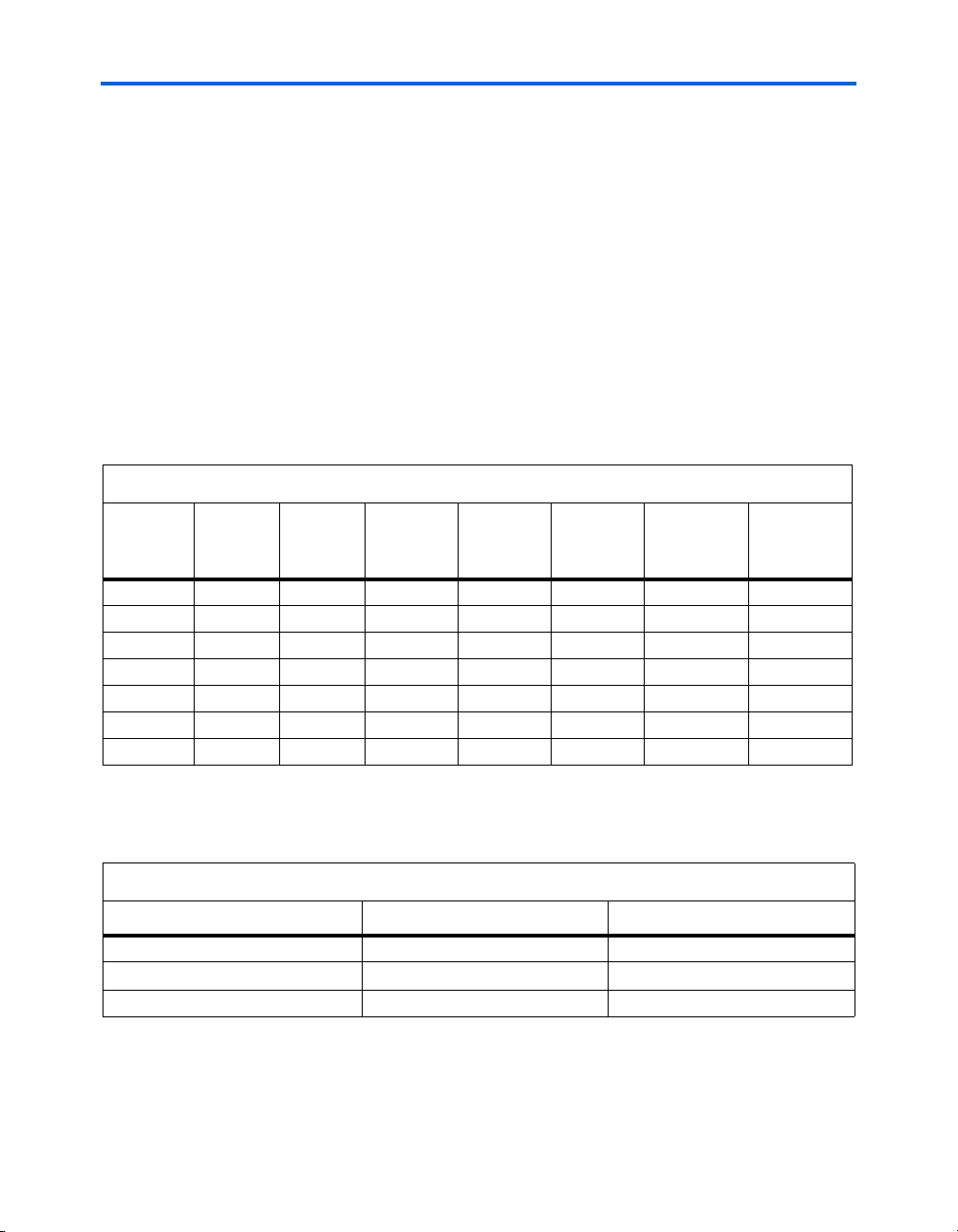

Table 1–3. Stratix Package Options & I/O Pin Counts

®

II software can

Device

EP1S10 345 335 345 426

EP1S20 426 361 426 586

EP1S25 473 473 597 706

EP1S30 683 597 726

EP1S40 683 615 773 822

EP1S60 683 773 1,022

EP1S80 683 773 1,203

Note to Ta b le 1 –3 :

(1) All I/O pin counts include 20 dedicated clock input pins (clk[15..0]p, clk0n, clk2n, clk9n, and clk11n)

that can be used for data inputs.

672-Pin

BGA

956-Pin

BGA

484-Pin

FineLine

BGA

672-Pin

FineLine

BGA

780-Pin

FineLine

BGA

1,020-Pin

FineLine

BGA

1,508-Pin

FineLine

BGA

Table 1–4. Stratix BGA Package Sizes

Dimension 672 Pin 956 Pin

Pitch (mm) 1.27 1.27

Area (mm

Length × width (mm × mm) 35 × 35 40 × 40

2

)

1,225 1,600

1–4 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 23

Introduction

Table 1–5. Stratix FineLine BGA Package Sizes

Dimension 484 Pin 672 Pin 780 Pin 1,020 Pin 1,508 Pin

Pitch (mm) 1.00 1.00 1.00 1.00 1.00

Area (mm

Length × width

(mm × mm)

2

)

529 729 841 1,089 1,600

23 × 23 27 × 27 29 × 29 33 × 33 40 × 40

Stratix devices are available in up to four speed grades, -5, -6, -7, and -8,

with -5 being the fastest. Table 1–6 shows Stratix device speed-grade

offerings.

Table 1–6. Stratix Device Speed Grades

Device

EP1S10 -6, -7 -5, -6, -7 -6, -7 -5, -6, -7

EP1S20 -6, -7 -5, -6, -7 -6, -7 -5, -6, -7

EP1S25 -6, -7 -6, -7, -8 -5, -6, -7 -5, -6, -7

EP1S30 -5, -6, -7 -5, -6, -7, -8 -5, -6, -7

EP1S40 -5, -6, -7 -5, -6, -7, -8 -5, -6, -7 -5, -6, -7

EP1S60 -6, -7 -5, -6, -7 -6, -7

EP1S80 -6, -7 -5, -6, -7 -5, -6, -7

672-Pin

BGA

956-Pin

BGA

484-Pin

FineLine

BGA

672-Pin

FineLine

BGA

780-Pin

FineLine

BGA

1,020-Pin

FineLine

BGA

1,508-Pin

FineLine

BGA

Altera Corporation 1–5

July 2005 Stratix Device Handbook, Volume 1

Page 24

Features

1–6 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 25

S51002-3.2

2. Stratix Architecture

Functional Description

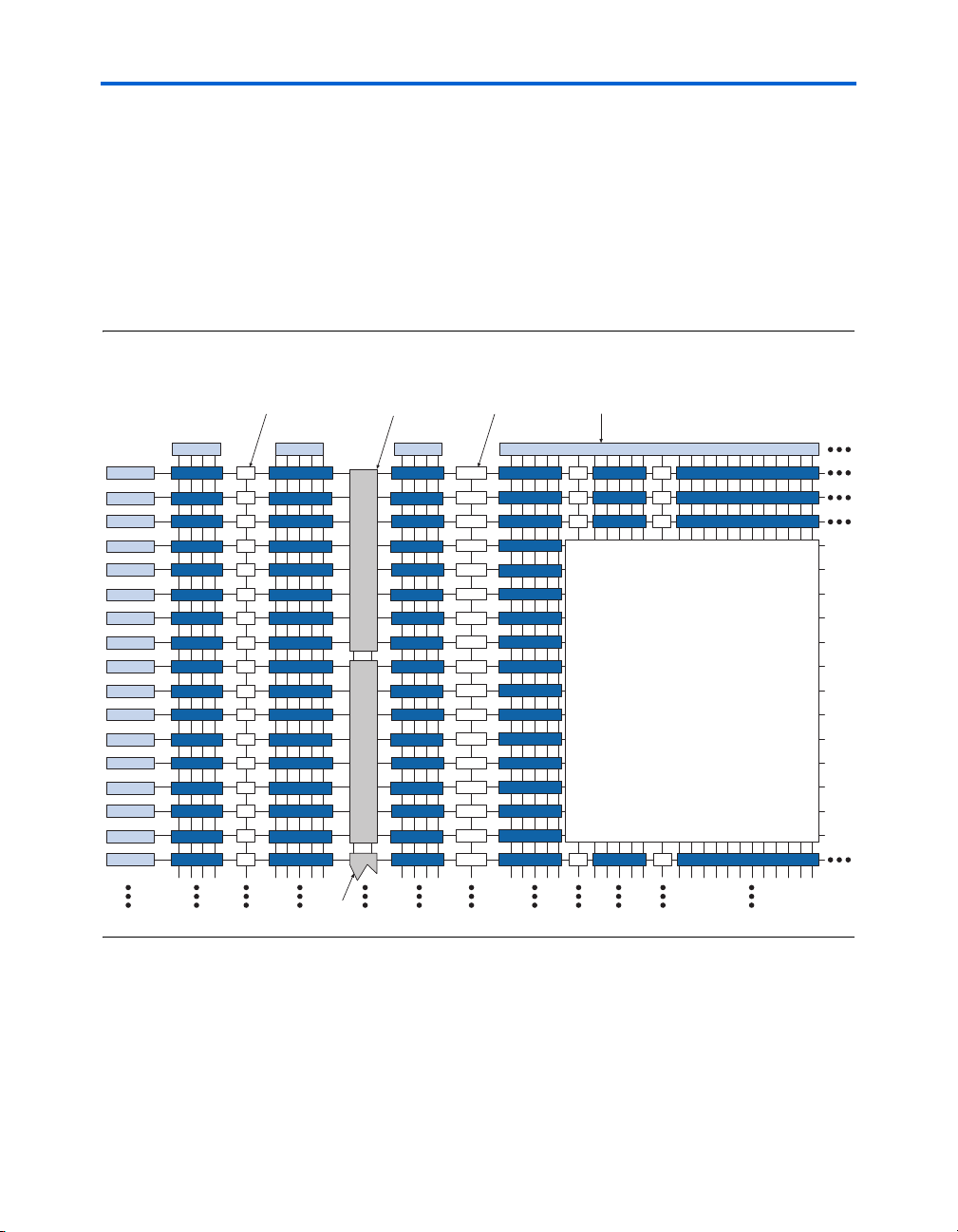

Stratix® devices contain a two-dimensional row- and column-based

architecture to implement custom logic. A series of column and row

interconnects of varying length and speed provide signal interconnects

between logic array blocks (LABs), memory block structures, and DSP

blocks.

The logic array consists of LABs, with 10 logic elements (LEs) in each

LAB. An LE is a small unit of logic providing efficient implementation of

user logic functions. LABs are grouped into rows and columns across the

device.

M512 RAM blocks are simple dual-port memory blocks with 512 bits plus

parity (576 bits). These blocks provide dedicated simple dual-port or

single-port memory up to 18-bits wide at up to 318 MHz. M512 blocks are

grouped into columns across the device in between certain LABs.

M4K RAM blocks are true dual-port memory blocks with 4K bits plus

parity (4,608 bits). These blocks provide dedicated true dual-port, simple

dual-port, or single-port memory up to 36-bits wide at up to 291 MHz.

These blocks are grouped into columns across the device in between

certain LABs.

M-RAM blocks are true dual-port memory blocks with 512K bits plus

parity (589,824 bits). These blocks provide dedicated true dual-port,

simple dual-port, or single-port memory up to 144-bits wide at up to

269 MHz. Several M-RAM blocks are located individually or in pairs

within the device’s logic array.

Digital signal processing (DSP) blocks can implement up to either eight

full-precision 9 × 9-bit multipliers, four full-precision 18 × 18-bit

multipliers, or one full-precision 36 × 36-bit multiplier with add or

subtract features. These blocks also contain 18-bit input shift registers for

digital signal processing applications, including FIR and infinite impulse

response (IIR) filters. DSP blocks are grouped into two columns in each

device.

Each Stratix device I/O pin is fed by an I/O element (IOE) located at the

end of LAB rows and columns around the periphery of the device. I/O

pins support numerous single-ended and differential I/O standards.

Each IOE contains a bidirectional I/O buffer and six registers for

registering input, output, and output-enable signals. When used with

Altera Corporation 2–1

July 2005

Page 26

Functional Description

dedicated clocks, these registers provide exceptional performance and

interface support with external memory devices such as DDR SDRAM,

FCRAM, ZBT, and QDR SRAM devices.

High-speed serial interface channels support transfers at up to 840 Mbps

using LVDS, LVPECL, 3.3-V PCML, or HyperTransport technology I/O

standards.

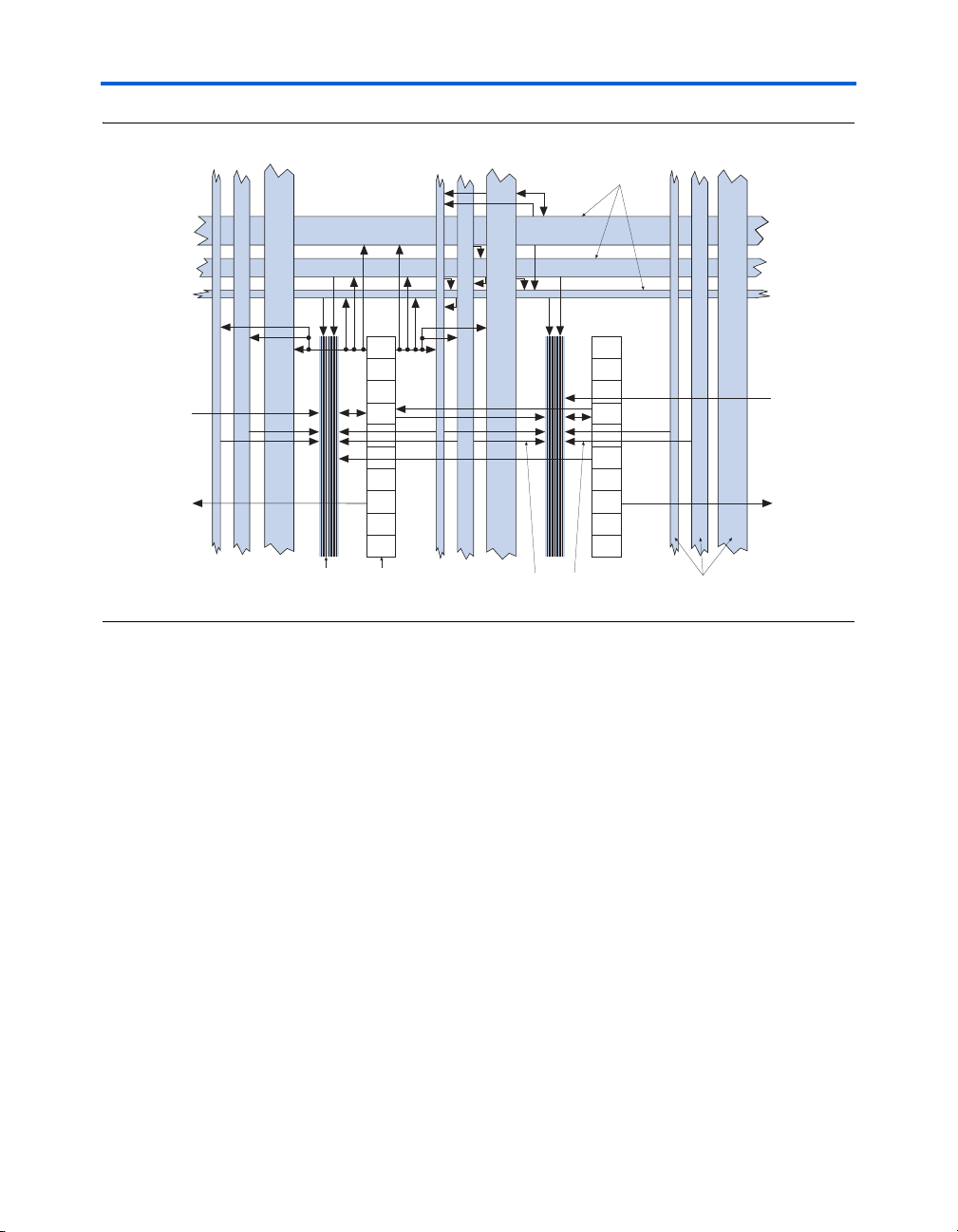

Figure 2–1 shows an overview of the Stratix device.

Figure 2–1. Stratix Block Diagram

M512 RAM Blocks for

Dual-Port Memory, Shift

Registers, & FIFO Buffers

DSP Blocks for

Multiplication and Full

Implementation of FIR Filters

M4K RAM Blocks

for True Dual-Port

Memory & Other Embedded

Memory Functions

IOEs Support DDR, PCI, GTL+, SSTL-3,

SSTL-2, HSTL, LVDS, LVPECL, PCML,

HyperTransport & other I/O Standards

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

IOEs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

IOEs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

DSP

Block

IOEs IOEs

LABs LABs

LABs

LABs LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

LABs

M-RAM Block

2–2 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 27

The number of M512 RAM, M4K RAM, and DSP blocks varies by device

along with row and column numbers and M-RAM blocks. Table 2–1 lists

the resources available in Stratix devices.

Table 2–1. Stratix Device Resources

Stratix Architecture

Device

EP1S10 4 / 94 2 / 60 1 2 / 6 40 30

EP1S20 6 / 194 2 / 82 2 2 / 10 52 41

EP1S25 6 / 224 3 / 138 2 2 / 10 62 46

EP1S30 7 / 295 3 / 171 4 2 / 12 67 57

EP1S40 8 / 384 3 / 183 4 2 / 14 77 61

EP1S60 10 / 574 4 / 292 6 2 / 18 90 73

EP1S80 11 / 767 4 / 364 9 2 / 22 101 91

M512 RAM

Columns/Blocks

Logic Array Blocks

M4K RAM

Columns/Blocks

M-RAM

Blocks

DSP Block

Columns/Blocks

LAB

Columns

LAB Rows

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, local

interconnect, LUT chain, and register chain connection lines. The local

interconnect transfers signals between LEs in the same LAB. LUT chain

connections transfer the output of one LE’s LUT to the adjacent LE for fast

sequential LUT connections within the same LAB. Register chain

connections transfer the output of one LE’s register to the adjacent LE’s

®

register within an LAB. The Quartus

II Compiler places associated logic

within an LAB or adjacent LABs, allowing the use of local, LUT chain,

and register chain connections for performance and area efficiency.

Figure 2–2 shows the Stratix LAB.

Altera Corporation 2–3

July 2005 Stratix Device Handbook, Volume 1

Page 28

Logic Array Blocks

Figure 2–2. Stratix LAB Structure

Direct link

interconnect from

adjacent block

Row Interconnects of

Variable Speed & Length

Direct link

interconnect from

adjacent block

Direct link

interconnect to

adjacent block

Direct link

interconnect to

adjacent block

Local Interconnect

LAB

Three-Sided Architecture—Local

Interconnect is Driven from Either Side by

Columns & LABs, & from Above by Rows

Column Interconnects of

Variable Speed & Length

LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB

local interconnect is driven by column and row interconnects and LE

outputs within the same LAB. Neighboring LABs, M512 RAM blocks,

M4K RAM blocks, or DSP blocks from the left and right can also drive an

LAB’s local interconnect through the direct link connection. The direct

link connection feature minimizes the use of row and column

interconnects, providing higher performance and flexibility. Each LE can

drive 30 other LEs through fast local and direct link interconnects.

Figure 2–3 shows the direct link connection.

2–4 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 29

Figure 2–3. Direct Link Connection

Stratix Architecture

Direct link interconnect from

left LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link

interconnect

to left

Interconnect

Direct link interconnect from

right LAB, TriMatrix memory

block, DSP block, or IOE output

Direct link

interconnect

to right

Local

LAB

LAB Control Signals

Each LAB contains dedicated logic for driving control signals to its LEs.

The control signals include two clocks, two clock enables, two

asynchronous clears, synchronous clear, asynchronous preset/load,

synchronous load, and add/subtract control signals. This gives a

maximum of 10 control signals at a time. Although synchronous load and

clear signals are generally used when implementing counters, they can

also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB’s

clock and clock enable signals are linked. For example, any LE in a

particular LAB using the labclk1 signal will also use labclkena1. If

the LAB uses both the rising and falling edges of a clock, it also uses both

LAB-wide clock signals. De-asserting the clock enable signal will turn off

the LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous

load/preset signal. The asynchronous load acts as a preset when the

asynchronous load data input is tied high.

Altera Corporation 2–5

July 2005 Stratix Device Handbook, Volume 1

Page 30

Logic Elements

With the LAB-wide addnsub control signal, a single LE can implement a

one-bit adder and subtractor. This saves LE resources and improves

performance for logic functions such as DSP correlators and signed

multipliers that alternate between addition and subtraction depending

on data.

The LAB row clocks [7..0] and LAB local interconnect generate the LABwide control signals. The MultiTrack

allows clock and control signal distribution in addition to data. Figure 2–4

shows the LAB control signal generation circuit.

Figure 2–4. LAB-Wide Control Signals

Dedicated

Row LAB

Clocks

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

Logic Elements

8

The smallest unit of logic in the Stratix architecture, the LE, is compact

and provides advanced features with efficient logic utilization. Each LE

contains a four-input LUT, which is a function generator that can

implement any function of four variables. In addition, each LE contains a

programmable register and carry chain with carry select capability. A

single LE also supports dynamic single bit addition or subtraction mode

selectable by an LAB-wide control signal. Each LE drives all types of

interconnects: local, row, column, LUT chain, register chain, and direct

link interconnects. See Figure 2–5.

labclkena1

TM

interconnect’s inherent low skew

labclkena2

labclk2labclk1

asyncload

or labpre

syncload

labclr1

labclr2

addnsub

synclr

2–6 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 31

Figure 2–5. Stratix LE

LAB Carry-In

addnsub

data1

data2

data3

data4

labclr1

labclr2

labpre/aload

Chip-Wide

Reset

labclk1

labclk2

Asynchronous

Clear/Preset/

Load Logic

Clock &

Clock Enable

Select

Carry-In1

Carry-In0

Look-Up

Tabl e

(LUT)

Carry

Chain

Register chain

routing from

previous LE

Synchronous

LAB-wide

Load

Synchronous

Synchronous

Load and

Clear Logic

LAB-wide

Clear

Register Bypass

Packed

Register Select

PRN/ALD

D

ADATA

ENA

CLRN

Register

Feedback

Stratix Architecture

Programmable

Register

LUT chain

routing to next LE

Row, column,

Q

and direct link

routing

Row, column,

and direct link

routing

Local Routing

Register chain

output

labclkena1

labclkena2

Carry-Out0

Carry-Out1

LAB Carry-Out

Each LE’s programmable register can be configured for D, T, JK, or SR

operation. Each register has data, true asynchronous load data, clock,

clock enable, clear, and asynchronous load/preset inputs. Global signals,

general-purpose I/O pins, or any internal logic can drive the register’s

clock and clear control signals. Either general-purpose I/O pins or

internal logic can drive the clock enable, preset, asynchronous load, and

asynchronous data. The asynchronous load data input comes from the

data3 input of the LE. For combinatorial functions, the register is

bypassed and the output of the LUT drives directly to the outputs of the

LE.

Each LE has three outputs that drive the local, row, and column routing

resources. The LUT or register output can drive these three outputs

independently. Two LE outputs drive column or row and direct link

routing connections and one drives local interconnect resources. This

allows the LUT to drive one output while the register drives another

output. This feature, called register packing, improves device utilization

because the device can use the register and the LUT for unrelated

Altera Corporation 2–7

July 2005 Stratix Device Handbook, Volume 1

Page 32

Logic Elements

functions. Another special packing mode allows the register output to

feed back into the LUT of the same LE so that the register is packed with

its own fan-out LUT. This provides another mechanism for improved

fitting. The LE can also drive out registered and unregistered versions of

the LUT output.

LUT Chain & Register Chain

In addition to the three general routing outputs, the LEs within an LAB

have LUT chain and register chain outputs. LUT chain connections allow

LUTs within the same LAB to cascade together for wide input functions.

Register chain outputs allow registers within the same LAB to cascade

together. The register chain output allows an LAB to use LUTs for a single

combinatorial function and the registers to be used for an unrelated shift

register implementation. These resources speed up connections between

LABs while saving local interconnect resources. See “MultiTrack

Interconnect” on page 2–14 for more information on LUT chain and

register chain connections.

addnsub Signal

The LE’s dynamic adder/subtractor feature saves logic resources by

using one set of LEs to implement both an adder and a subtractor. This

feature is controlled by the LAB-wide control signal addnsub. The

addnsub signal sets the LAB to perform either A + B or A – B. The LUT

computes addition, and subtraction is computed by adding the two’s

complement of the intended subtractor. The LAB-wide signal converts to

two’s complement by inverting the B bits within the LAB and setting

carry-in = 1 to add one to the least significant bit (LSB). The LSB of an

adder/subtractor must be placed in the first LE of the LAB, where the

LAB-wide addnsub signal automatically sets the carry-in to 1. The

Quartus II Compiler automatically places and uses the adder/subtractor

feature when using adder/subtractor parameterized functions.

LE Operating Modes

The Stratix LE can operate in one of the following modes:

■ Normal mode

■ Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available

inputs to the LE—the four data inputs from the LAB local interconnect;

carry-in0 and carry-in1 from the previous LE; the LAB carry-in

from the previous carry-chain LAB; and the register chain connection—

are directed to different destinations to implement the desired logic

function. LAB-wide signals provide clock, asynchronous clear,

2–8 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 33

Stratix Architecture

asynchronous preset load, synchronous clear, synchronous load, and

clock enable control for the register. These LAB-wide signals are available

in all LE modes. The addnsub control signal is allowed in arithmetic

mode.

The Quartus II software, in conjunction with parameterized functions

such as library of parameterized modules (LPM) functions, automatically

chooses the appropriate mode for common functions such as counters,

adders, subtractors, and arithmetic functions. If required, you can also

create special-purpose functions that specify which LE operating mode to

use for optimal performance.

Normal Mode

The normal mode is suitable for general logic applications and

combinatorial functions. In normal mode, four data inputs from the LAB

local interconnect are inputs to a four-input LUT (see Figure 2–6). The

Quartus II Compiler automatically selects the carry-in or the data3

signal as one of the inputs to the LUT. Each LE can use LUT chain

connections to drive its combinatorial output directly to the next LE in the

LAB. Asynchronous load data for the register comes from the data3

input of the LE. LEs in normal mode support packed registers.

Figure 2–6. LE in Normal Mode

sclear

(LAB Wide)

addnsub (LAB Wide)

(1)

data1

data2

data3

cin (from cout

of previous LE)

data4

4-Input

LUT

Register Feedback

Register chain

connection

sload

(LAB Wide)

clock (LAB Wide)

ena (LAB Wide)

aclr (LAB Wide)

Note to Figure 2–6:

(1) This signal is only allowed in normal mode if the LE is at the end of an adder/subtractor chain.

Altera Corporation 2–9

July 2005 Stratix Device Handbook, Volume 1

aload

(LAB Wide)

ALD/PRE

ADATA

D

ENA

CLRN

Q

Row, column, and

direct link routing

Row, column, and

direct link routing

Local routing

LUT chain

connection

Register

chain output

Page 34

Logic Elements

Dynamic Arithmetic Mode

The dynamic arithmetic mode is ideal for implementing adders, counters,

accumulators, wide parity functions, and comparators. An LE in dynamic

arithmetic mode uses four 2-input LUTs configurable as a dynamic

adder/subtractor. The first two 2-input LUTs compute two summations

based on a possible carry-in of 1 or 0; the other two LUTs generate carry

outputs for the two chains of the carry select circuitry. As shown in

Figure 2–7, the LAB carry-in signal selects either the carry-in0 or

carry-in1 chain. The selected chain’s logic level in turn determines

which parallel sum is generated as a combinatorial or registered output.

For example, when implementing an adder, the sum output is the

selection of two possible calculated sums: data1 + data2 + carry-in0

or data1 + data2 + carry-in1. The other two LUTs use the data1 and

data2 signals to generate two possible carry-out signals—one for a carry

of 1 and the other for a carry of 0. The carry-in0 signal acts as the carry

select for the carry-out0 output and carry-in1 acts as the carry select

for the carry-out1 output. LEs in arithmetic mode can drive out

registered and unregistered versions of the LUT output.

The dynamic arithmetic mode also offers clock enable, counter enable,

synchronous up/down control, synchronous clear, synchronous load,

and dynamic adder/subtractor options. The LAB local interconnect data

inputs generate the counter enable and synchronous up/down control

signals. The synchronous clear and synchronous load options are LABwide signals that affect all registers in the LAB. The Quartus II software

automatically places any registers that are not used by the counter into

other LABs. The addnsub LAB-wide signal controls whether the LE acts

as an adder or subtractor.

2–10 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 35

Figure 2–7. LE in Dynamic Arithmetic Mode

LAB Carry-In

Carry-In0

Carry-In1

addnsub

(LAB Wide)

(1)

Register chain

connection

sload

(LAB Wide)

sclear

(LAB Wide)

aload

(LAB Wide)

Stratix Architecture

data1

data2

data3

LUT

LUT

LUT

LUT

clock (LAB Wide)

ena (LAB Wide)

aclr (LAB Wide)

Register Feedback

Carry-Out1Carry-Out0

ALD/PRE

ADATA

D

ENA

CLRN

Note to Figure 2–7:

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

Carry-Select Chain

The carry-select chain provides a very fast carry-select function between

LEs in arithmetic mode. The carry-select chain uses the redundant carry

calculation to increase the speed of carry functions. The LE is configured

to calculate outputs for a possible carry-in of 1 and carry-in of 0 in

parallel. The carry-in0 and carry-in1 signals from a lower-order bit

feed forward into the higher-order bit via the parallel carry chain and feed

into both the LUT and the next portion of the carry chain. Carry-select

chains can begin in any LE within an LAB.

Q

Row, column, and

direct link routing

Row, column, and

direct link routing

Local routing

LUT chain

connection

Register

chain output

The speed advantage of the carry-select chain is in the parallel precomputation of carry chains. Since the LAB carry-in selects the

precomputed carry chain, not every LE is in the critical path. Only the

propagation delay between LAB carry-in generation (LE 5 and LE 10) are

now part of the critical path. This feature allows the Stratix architecture to

implement high-speed counters, adders, multipliers, parity functions,

and comparators of arbitrary width.

Altera Corporation 2–11

July 2005 Stratix Device Handbook, Volume 1

Page 36

Logic Elements

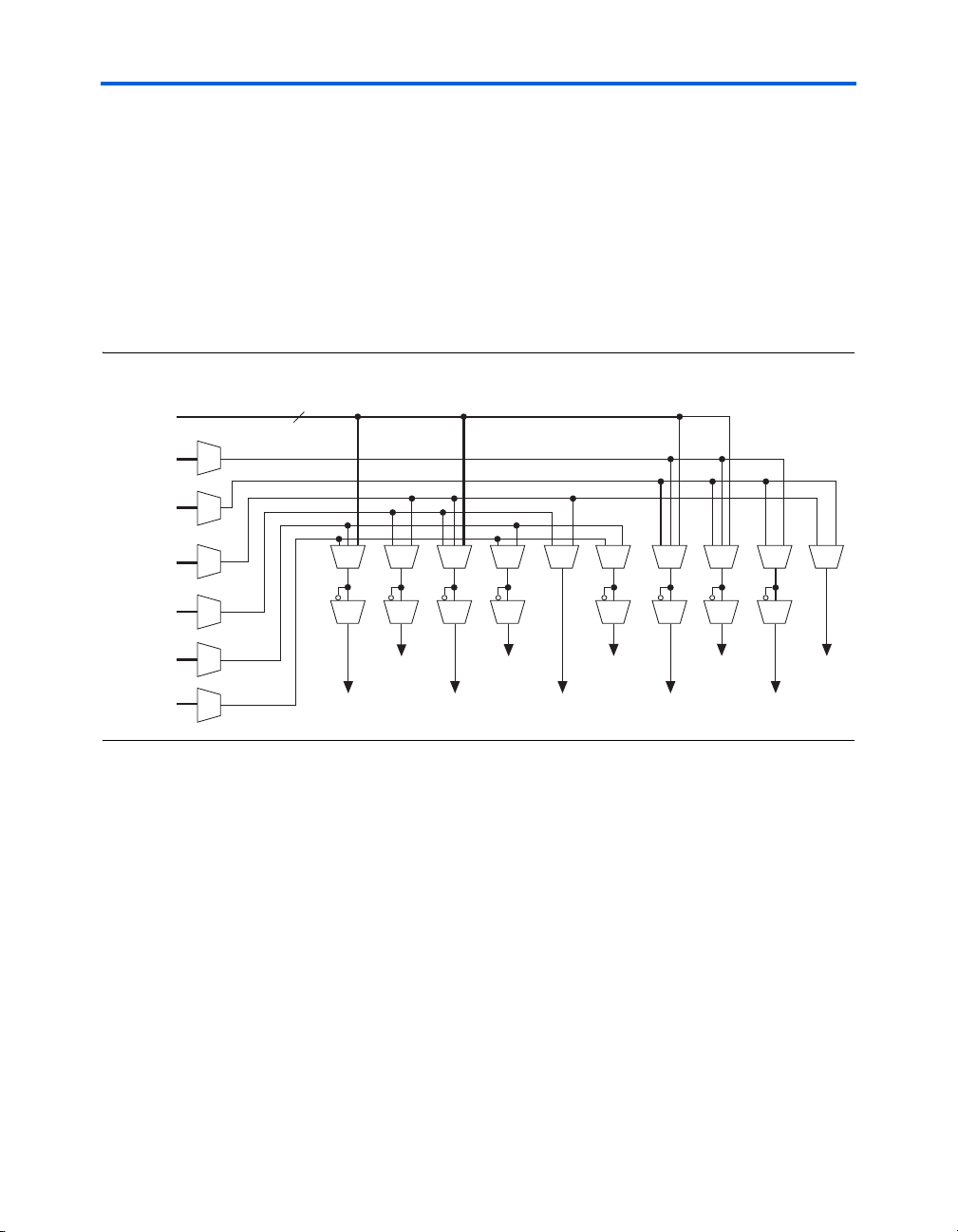

Figure 2–8 shows the carry-select circuitry in an LAB for a 10-bit full

adder. One portion of the LUT generates the sum of two bits using the

input signals and the appropriate carry-in bit; the sum is routed to the

output of the LE. The register can be bypassed for simple adders or used

for accumulator functions. Another portion of the LUT generates carryout bits. An LAB-wide carry in bit selects which chain is used for the

addition of given inputs. The carry-in signal for each chain, carry-in0

or carry-in1, selects the carry-out to carry forward to the carry-in

signal of the next-higher-order bit. The final carry-out signal is routed to

an LE, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during

design processing, or you can create it manually during design entry.

Parameterized functions such as LPM functions automatically take

advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by

linking LABs together automatically. For enhanced fitting, a long carry

chain runs vertically allowing fast horizontal connections to TriMatrix

™

memory and DSP blocks. A carry chain can continue as far as a full

column.

2–12 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 37

Figure 2–8. Carry Select Chain

Stratix Architecture

LAB Carry-In

A1

B1

A2

B2

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

A8

B8

A9

B9

01

LE1

LE2

LE3

LE4

LE5

01

LE6

LE7

LE8

LE9

Sum1

Sum2

Sum3

Sum4

Sum5

Sum6

Sum7

Sum8

Sum9

LAB Carry-In

Carry-In0

Carry-In1

data1

data2

LUT

Sum

LUT

LUT

LUT

Carry-Out0 Carry-Out1

A10

B10

LAB Carry-Out

LE10

Sum10

Clear & Preset Logic Control

LAB-wide signals control the logic for the register’s clear and preset

signals. The LE directly supports an asynchronous clear and preset

function. The register preset is achieved through the asynchronous load

of a logic high. The direct asynchronous preset does not require a NOTgate push-back technique. Stratix devices support simultaneous preset/

Altera Corporation 2–13

July 2005 Stratix Device Handbook, Volume 1

Page 38

MultiTrack Interconnect

asynchronous load, and clear signals. An asynchronous clear signal takes

precedence if both signals are asserted simultaneously. Each LAB

supports up to two clears and one preset signal.

In addition to the clear and preset ports, Stratix devices provide a chipwide reset pin (DEV_CLRn) that resets all registers in the device. An

option set before compilation in the Quartus II software controls this pin.

This chip-wide reset overrides all other control signals.

MultiTrack

Interconnect

In the Stratix architecture, connections between LEs, TriMatrix memory,

DSP blocks, and device I/O pins are provided by the MultiTrack

interconnect structure with DirectDriveTM technology. The MultiTrack

interconnect consists of continuous, performance-optimized routing lines

of different lengths and speeds used for inter- and intra-design block

connectivity. The Quartus II Compiler automatically places critical design

paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures

identical routing resource usage for any function regardless of placement

within the device. The MultiTrack interconnect and DirectDrive

technology simplify the integration stage of block-based designing by

eliminating the re-optimization cycles that typically follow design

changes and additions.

The MultiTrack interconnect consists of row and column interconnects

that span fixed distances. A routing structure with fixed length resources

for all devices allows predictable and repeatable performance when

migrating through different device densities. Dedicated row

interconnects route signals to and from LABs, DSP blocks, and TriMatrix

memory within the same row. These row resources include:

■ Direct link interconnects between LABs and adjacent blocks.

■ R4 interconnects traversing four blocks to the right or left.

■ R8 interconnects traversing eight blocks to the right or left.

■ R24 row interconnects for high-speed access across the length of the

device.

The direct link interconnect allows an LAB, DSP block, or TriMatrix

memory block to drive into the local interconnect of its left and right

neighbors and then back into itself. Only one side of a M-RAM block

interfaces with direct link and row interconnects. This provides fast

communication between adjacent LABs and/or blocks without using row

interconnect resources.

The R4 interconnects span four LABs, three LABs and one M512 RAM

block, two LABs and one M4K RAM block, or two LABs and one DSP

block to the right or left of a source LAB. These resources are used for fast

2–14 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 39

row connections in a four-LAB region. Every LAB has its own set of R4

interconnects to drive either left or right. Figure 2–9 shows R4

interconnect connections from an LAB. R4 interconnects can drive and be

driven by DSP blocks and RAM blocks and horizontal IOEs. For LAB

interfacing, a primary LAB or LAB neighbor can drive a given R4

interconnect. For R4 interconnects that drive to the right, the primary

LAB and right neighbor can drive on to the interconnect. For R4

interconnects that drive to the left, the primary LAB and its left neighbor

can drive on to the interconnect. R4 interconnects can drive other R4

interconnects to extend the range of LABs they can drive. R4

interconnects can also drive C4 and C16 interconnects for connections

from one row to another. Additionally, R4 interconnects can drive R24

interconnects.

Figure 2–9. R4 Interconnect Connections

Adjacent LAB can

Drive onto Another

LAB's R4 Interconnect

R4 Interconnect

Driving Left

C4, C8, and C16

Column Interconnects (1)

R4 Interconnect

Driving Right

Stratix Architecture

LAB

Neighbor

Primary

LAB (2)

LAB

Neighbor

Notes to Figure 2–9:

(1) C4 interconnects can drive R4 interconnects.

(2) This pattern is repeated for every LAB in the LAB row.

The R8 interconnects span eight LABs, M512 or M4K RAM blocks, or DSP

blocks to the right or left from a source LAB. These resources are used for

fast row connections in an eight-LAB region. Every LAB has its own set

of R8 interconnects to drive either left or right. R8 interconnect

connections between LABs in a row are similar to the R4 connections

shown in Figure 2–9, with the exception that they connect to eight LABs

to the right or left, not four. Like R4 interconnects, R8 interconnects can

drive and be driven by all types of architecture blocks. R8 interconnects

Altera Corporation 2–15

July 2005 Stratix Device Handbook, Volume 1

Page 40

MultiTrack Interconnect

can drive other R8 interconnects to extend their range as well as C8

interconnects for row-to-row connections. One R8 interconnect is faster

than two R4 interconnects connected together.

R24 row interconnects span 24 LABs and provide the fastest resource for

long row connections between LABs, TriMatrix memory, DSP blocks, and

IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row

interconnects drive to other row or column interconnects at every fourth

LAB and do not drive directly to LAB local interconnects. R24 row

interconnects drive LAB local interconnects via R4 and C4 interconnects.

R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and

vertically routes signals to and from LABs, TriMatrix memory, DSP

blocks, and IOEs. Each column of LABs is served by a dedicated column

interconnect, which vertically routes signals to and from LABs, TriMatrix

memory and DSP blocks, and horizontal IOEs. These column resources

include:

■ LUT chain interconnects within an LAB

■ Register chain interconnects within an LAB

■ C4 interconnects traversing a distance of four blocks in up and down

direction

■ C8 interconnects traversing a distance of eight blocks in up and

down direction

■ C16 column interconnects for high-speed vertical routing through

the device

Stratix devices include an enhanced interconnect structure within LABs

for routing LE output to LE input connections faster using LUT chain

connections and register chain connections. The LUT chain connection

allows the combinatorial output of an LE to directly drive the fast input

of the LE right below it, bypassing the local interconnect. These resources

can be used as a high-speed connection for wide fan-in functions from

LE 1 to LE 10 in the same LAB. The register chain connection allows the

register output of one LE to connect directly to the register input of the

next LE in the LAB for fast shift registers. The Quartus II Compiler

automatically takes advantage of these resources to improve utilization

and performance. Figure 2–10 shows the LUT chain and register chain

interconnects.

2–16 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 41

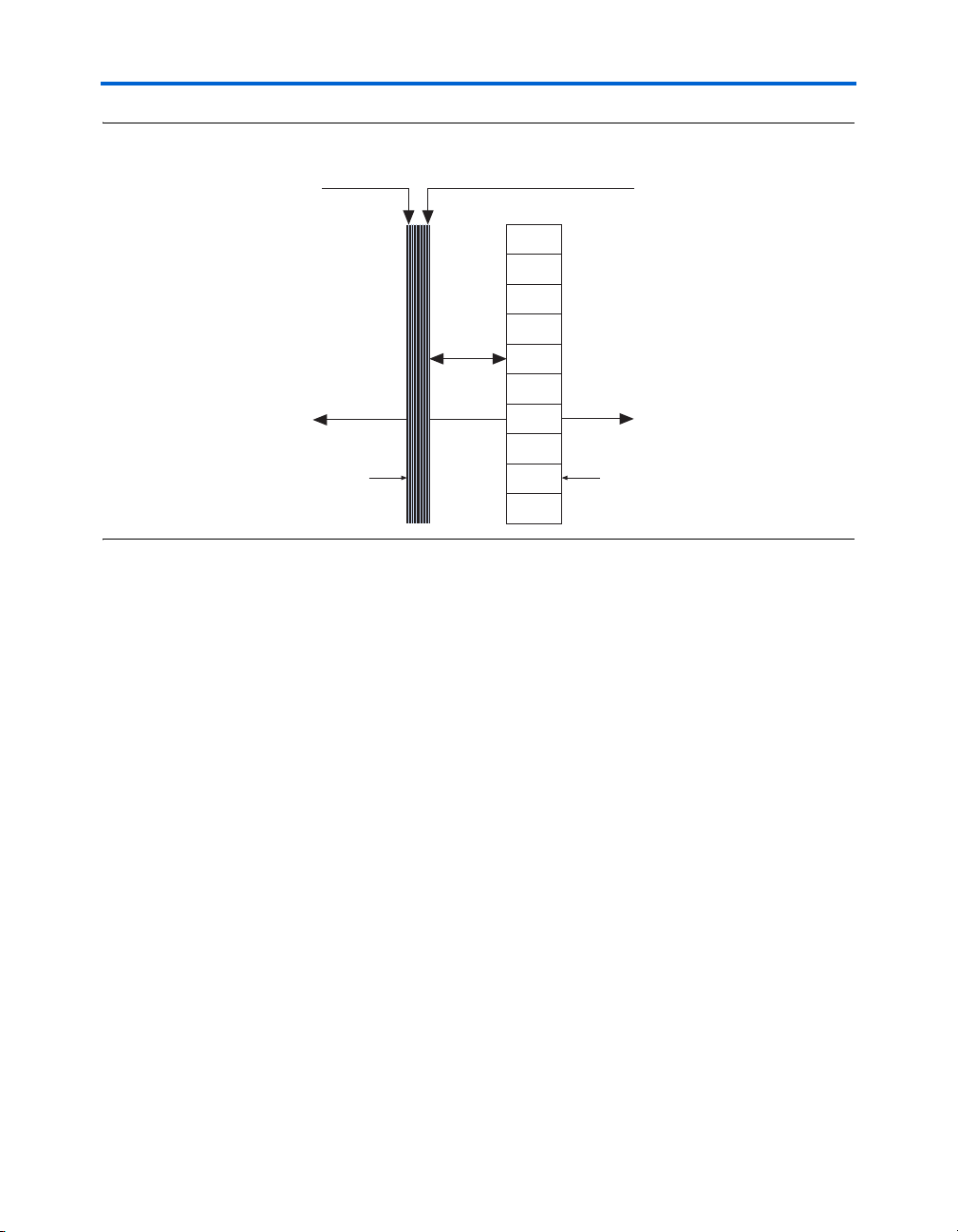

Figure 2–10. LUT Chain & Register Chain Interconnects

t

Local Interconnect

Routing Among LEs

in the LAB

Stratix Architecture

LUT Chain

Routing to

Adjacent LE

Local

Interconnect

LE 1

LE 2

LE 3

LE 4

LE 5

LE 6

LE 7

LE 8

LE 9

LE 10

Register Chain

Routing to Adjacen

LE's Register Input

The C4 interconnects span four LABs, M512, or M4K blocks up or down

from a source LAB. Every LAB has its own set of C4 interconnects to drive

either up or down. Figure 2–11 shows the C4 interconnect connections

from an LAB in a column. The C4 interconnects can drive and be driven

by all types of architecture blocks, including DSP blocks, TriMatrix

memory blocks, and vertical IOEs. For LAB interconnection, a primary

LAB or its LAB neighbor can drive a given C4 interconnect.

C4 interconnects can drive each other to extend their range as well as

drive row interconnects for column-to-column connections.

Altera Corporation 2–17

July 2005 Stratix Device Handbook, Volume 1

Page 42

MultiTrack Interconnect

4

Figure 2–11. C4 Interconnect Connections Note (1)

C4 Interconnect

Drives Local and R

Interconnects

up to Four Rows

C4 Interconnect

Driving Up

LAB

Row

Interconnect

Adjacent LAB can

drive onto neighboring

LAB's C4 interconnect

Local

Interconnect

C4 Interconnect

Driving Down

Note to Figure 2–11:

(1) Each C4 interconnect can drive either up or down four rows.

2–18 Altera Corporation

Stratix Device Handbook, Volume 1 July 2005

Page 43

Stratix Architecture

C8 interconnects span eight LABs, M512, or M4K blocks up or down from

a source LAB. Every LAB has its own set of C8 interconnects to drive

either up or down. C8 interconnect connections between the LABs in a

column are similar to the C4 connections shown in Figure 2–11 with the

exception that they connect to eight LABs above and below. The C8

interconnects can drive and be driven by all types of architecture blocks