Alliance Semiconductor P2811, P2812, P2814 Service Manual

October 2003 P2811/12/14

rev

Low-Power EMI Reduction IC

Features

FCC approved method of EMI attenuation

Provides up to 15 dB EMI reduction

Generates 1X, 2X, and 4X low EMI spread spectrum

clock of the input frequency

1X: P2811, 2X: P2812, 4X: P2814

Optimized for input frequency range from 10 to 40

MHz P2811: 10 to 40 MHz P2812: 10 to 40 MHz

P2814: 10 to 40 MHz

Internal loop filter minimizes external components

and board space

Selectable spread options: Down Spread and Center

Spread

Low inherent cycle-to-cycle jitter

Eight spread % selections: ±0.625% to –3.5%

3.3 V operating voltage

CMOS/TTL compatible inputs and outputs

Pinout compatible with Cypress CY25811,

CY25812, and CY25814

Products available for industrial temperature range

Available in 8-pin SOIC and TSSOP

Product Description

The P28xx is a versatile spread spectrum frequency

modulator designed specifically for input clock frequencies

from 10 to 40 MHz (see Input/Output Frequency Range

Selections). The P28xx can generate an EMI reduced clock

from crystal, ceramic resonator, or system clock. The

P28xx-A and P28xx-B offer various combinations of spread

options and percentage deviations (see Output Frequency

Block Diagram

Deviation and Spread Option Selections section). These

combinations include Down Spread, Center Spread and

percentage deviation range from ±0.625% to -3.50%.

The P28xx reduces electromagnetic interference (EMI) at

the clock source, allowing a system wide EMI reduction for

all the down stream clocks and data dependent signals.

The P28xx allows significant system cost savings by

reducing the number of circuit board layers, ferrite beads,

shielding, and other passive components that are

traditionally required to pass EMI regulations.

The P28xx modulates the output of a single PLL in order to

“spread” the bandwidth of a synthesized clock, thereby

decreasing the peak amplitudes of its harmonics. This

results in significantly lower system EMI compared to the

typical narrow band signal produced by oscillators and

most clock generators. Lowering EMI by increasing a

signal’s bandwidth is called “spread spectrum clock

generation”.

The P28xx uses the most efficient and optimized

modulation profile approved by the FCC and is

implemented by using a proprietary all-digital method.

Applications

The P28xx is targeted towards EMI management for

memory interfaces in mobile graphic chipsets and high-

speed digital applications such as PC peripheral devices,

consumer electronics, and embedded controller systems.

Alliance Semiconductor

2575, Augustine Drive • Santa Clara, CA • Tel: 408.855.4900 • Fax: 408.855.4999 • www.alsc.com

Notice: The information in this document is subject to change without notice.

October 2003 P2811/12/14

rev

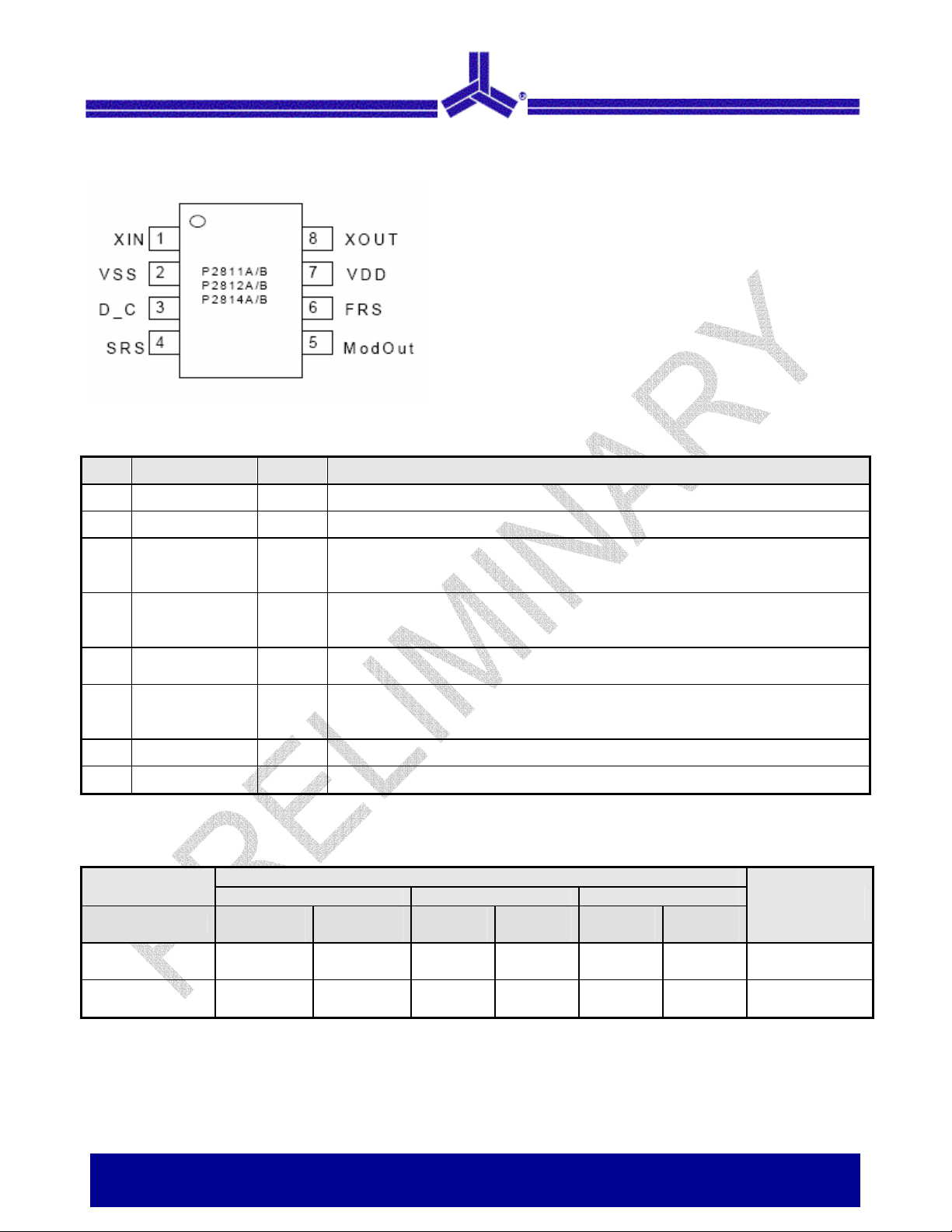

Pin Configuration

Pin Description

Pin# Pin Name Type Description

1

2

3

4

5

6

7

8

Input/Output Frequency Range Selections

Pin 6

FRS

XIN I Connect to externally generated clock signal or crystal.

VSS P Ground Connection. Connect to system ground.

D_C I Digital logic input used to select Down (LOW) or Center (HIGH) Spread

Options (see Output Frequency Deviation and Spread Option Selections).

This pin has an internal pull-up resistor.

SRS I Spread Range Selection. Digital logic input used to select frequency

deviation (see Output Frequency Deviation and Spread Option Selections).

This pin has an internal pull-up resistor.

ModOut O Spread Spectrum clock output (see Input/Output Frequency Range

Selections and Output Frequency Deviation and Spread Option Selections).

FRS I Frequency Range Selection. Digital logic input used to select input fre-

quency range (see Input/Output Frequency Range Selections). This pin has

an internal pull-up resistor.

VDD P Connect to +3.3 V

XOUT I Connect to crystal. No connect if externally generated clock signal is used.

P2811 (1X) P2812 (2X) P2814 (4X)

Input

(MHz)

0 10-20 10-20 10-20 20-40 10-20 40-80

1 20-40 20-40 20-40 40-80 20-40 80-160

Output

(MHz)

Part number

Input

(MHz)

Output

(MHz)

Input

(MHz)

Output

(MHz)

Modulation

rate

Input frequency

/ 448

Input frequency

/ 896

Notice: The information in this document is subject to change without notice.

Low Power EMI Reduction IC 2 of 8

October 2003 P2811/12/14

rev

Output Frequency Deviation and Spread Option Selections

Part number Pin 3 D_C Pin 4 SRS

0 0 -2.50% (Down)

P2811/12/14A

0 1 -3.50% (Down)

1 0 +/-1.25% (Center)

1 1 +/-1.75% (Center)

0 0 -1.25% (Down)

P2811/12/14B

0 1 -1.75% (Down)

1 0 +/-0.625% (Center)

1 1 +/-0.875% (Center)

Absolute Maximum Ratings

Symbol Parameter Rating Unit

VDD, VIN Voltage on any pin with respect to GND

T

Storage temperature

STG

TA Operating temperature

DC Electrical Characteristics

3.3 V, 25° C

Symbol Parameter Min Typ Max Unit

VIL Input Low Voltage GND – 0.3 – 0.8 V

VIH Input High Voltage – – VDD + 0.3 V

IIL

Input low Current (inputs

D_C, SRS, and FRS)

-60.00 – -20.00 µA

IIH Input High Current – – 1.00 µA

I

XOL

I

XOH

VOL

VOH

IDD

XOUT Output Low Current

(@ 0.4V, VDD = 3.3V)

XOUT Output High Current

(@ 2.5V, VDD = 3.3V)

Output Low Voltage

(VDD=3.3V, IOL = 20 mA)

Output High Voltage

(VDD=3.3V, IOH = 20 mA)

Static Supply Current

Standby Mode

2.00 – 12.00 mA

– – 12.00 mA

– – 0.4 V

– – 2.8 V

– 4.5 – mA

Dynamic Supply Current

ICC

Normal Mode (3.3V and 25

7.1 fIN-min – 13.9 f

pF probe loading)

VDD Operating Voltage – 3.3 – V

tON

Z

Clock Output Impedance – 50 – Ω

OUT

Power Up Time (First locked

clock cycle after power up)

– 0.18 – mS

Output frequency deviation and

spread option

-0.5 to + 7.0 V

-65 to +125 °C

0 to 70 °C

mA

IN-max

Notice: The information in this document is subject to change without notice.

Low Power EMI Reduction IC 3 of 8

Loading...

Loading...