Alliance Semiconductor ASM3P623S00A, ASM3P623S00B, ASM3P623S00C, ASM3P623S00D, ASM3P623S00E Service Manual

...

r

r

r

r

r

查询ASM3I623S00AF-08-SR供应商

July 2005 ASM3P623S00A/B/C/D/E/F

rev 1.0

Zero Cycle Slip Peak EMI reduction IC

General Features

Input frequency range: 20MHz - 50MHz.

Zero input - output propagation delay.

Low-skew outputs.

Output-output skew less than 250pS.

Device-device skew less than 700pS.

Less than 200pS cycle-to-cycle jitter is compatible

with Pentium

®

based systems.

Available in 16pin, 150mil SOIC, 4.4mm TSSOP

(ASM3P623S00D/E/F), and in 8pin, 150 mil SOIC,

4.4mm TSSOP Packages (ASM3P623S00A/B/C).

3.3V operation

Advanced 0.35µ CMOS technology.

The First True Drop-in Solution.

Functional Description

ASM3P623S00D/E/F is a versatile, 3.3V zero-delay buffer

designed to distribute high-speed clocks. It accepts one

reference input and drives out eight low-skew clocks. It is

available in a 16pin package. The ASM3P623S00A/B/C is

the eight-pin version of the ASM3P623S00. It accepts one

reference input and drives out one low-skew clock.

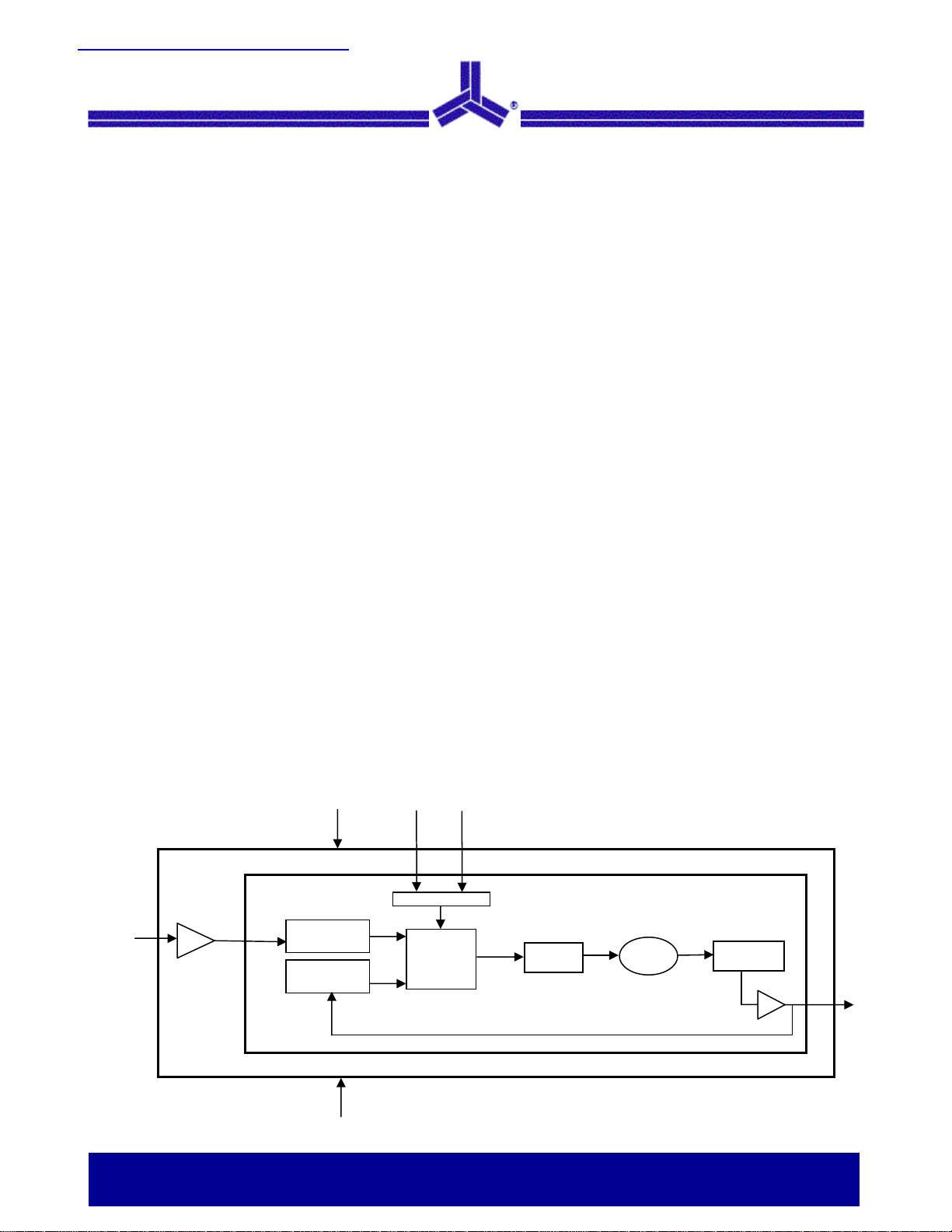

Block Diagram

VDD

SSON

All parts have on-chip PLLs that lock to an input clock on

the CLKIN pin. The PLL feedback is on-chip and is

obtained from the CLKOUT pad, internal to the device.

Multiple ASM3P623S00D/E/F devices can accept the same

input clock and distribute it. In this case, the skew between

the outputs of the two devices is guaranteed to be less than

700pS.

All outputs have less than 200pS of cycle-to-cycle jitter.

The input and output propagation delay is guaranteed to be

less than 250pS, and the output-to-output skew is

guaranteed to be less than 250pS.

Please refer

“Differential Cycle Slips and Spread Spectrum

Control Table” for deviations and differential Cycle Slips

for ASM3P623S00A/B/C and the ASM3P623S00D/E/F

devices

The ASM3P623S00A/B/C and the ASM3P623S00D/E/F

are available in two different configurations, as shown in

the ordering information table.

SS%

CLKIN

Reference

Divide

Feedback

Divide

Modulation

Phase

Detecto

Loop

Filte

VCO

PLL

Feedforward

Divide

CLKOUT

VSS

Alliance Semiconductor

2575 Augustine Drive • Santa Clara, CA • Tel: 408.855.4900 • Fax: 408.855.4999 • www.alsc.com

Notice: The information in this document is subject to change without notice.

July 2005

ASM3P623S00A/B/C/D/E/F

rev 1.0

Spread Spectrum Frequency Generation

The clocks in digital systems are typically square waves

with a 50% duty cycle and as frequencies increase the

edge rates also get faster. Analysis shows that a square

wave is composed of fundamental frequency and

harmonics. The fundamental frequency and harmonics

generate the energy peaks that become the source of

EMI. Regulatory agencies test electronic equipment by

measuring the amount of peak energy radiated from the

equipment. In fact, the peak level allowed decreases as

the frequency increases. The standard methods of

reducing EMI are to use shielding, filtering, multi-layer

Cycle Slip

Cycle slip occurs when the output clock edge

‘wanders’ away from the corresponding input clock

edge. There are two types of cycle slips – a Differential

cycle slip and an Integral cycle slip. The differential

cycle slip is caused due the clock edge variation over

one modulation cycle. It is defined by the maximum

amount of ‘wander’ the clock edge will have within one

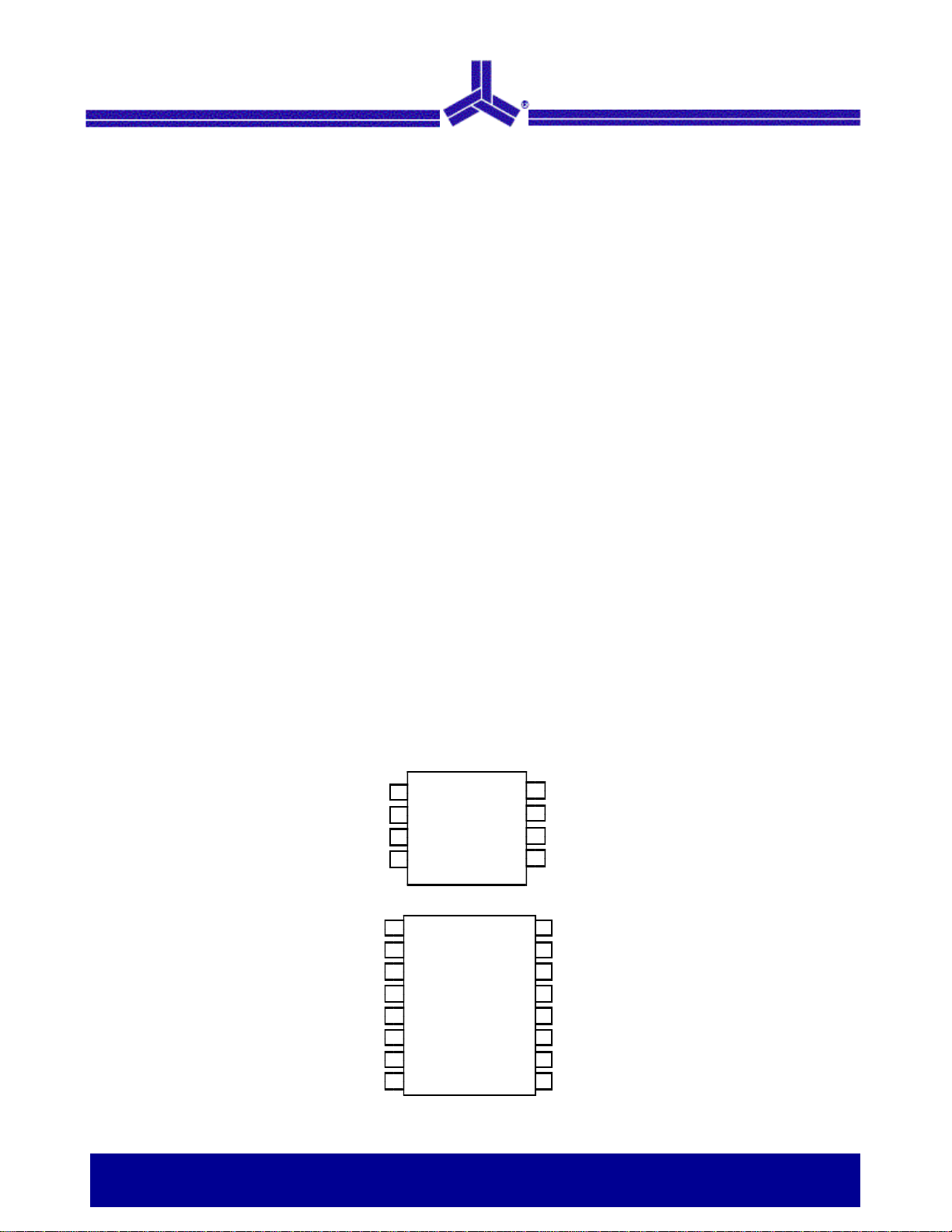

Pin Configuration

PCBs etc. These methods are expensive. Spread

spectrum clocking reduces the peak energy by reducing

the Q factor of the clock. This is done by slowly

modulating the clock frequency. The ASM3P623S00X

uses the center modulation spread spectrum technique in

which the modulated output frequency varies above and

below the reference frequency with a specified

modulation rate. With center modulation, the average

frequency is the same as the unmodulated frequency and

there is no performance degradation

modulation cycle. Integral cycle slip occurs due to the

accumulation of the cycle slip over successive modulation

cycles. In ASM3P623S00A/B/C/D/E/F the differential cycle

slip is within the value mentioned in the

“Differential Cycle

Slip and Spread Spectrum Control Table” and the Integral

Cycle Slip is ‘Zero’.

NC

CLKIN

NC

SS%

GND

1

2

ASM3P623S00A/B/C

3

4

8

7

6

5

V

DD

CLKOUT

SSON

1

CLKIN

VDD

SS%

GND

2

3

4

ASM3P623S00 D/E/F

5

6

7

8

CLKOUT1

CLKOUT2

CLKOUT3

DLY CNTRL

16

15

14

13

12

11

10

9

CLKOUT8

CLKOUT7

CLKOUT6

VDD

GND

CLKOUT5

CLKOUT4

SSON

Zero Cycle Slip Peak EMI Reduction IC 2 of 16

Notice: The information in this document is subject to change without notice.

July 2005

ASM3P623S00A/B/C/D/E/F

rev 1.0

Pin Description for ASM3P623S00A/B/C

Pin # Pin Name Description

1 CLKIN2 Input reference frequency, 5V-tolerant input

2 NC No Connect

3 SS%4 Spread Spectrum Selection

4 GND Ground

5 SSON4 Spread Spectrum enable and disable option When SSON is HIGH, the spread

spectrum is enabled and when LOW, it turns off the spread spectrum.

6 CLKOUT

7 VDD 3.3V supply

8 NC No Connect

Pin Description for ASM3P623S00D/E/F

Pin # Pin Name Description

1 CLKIN2 Input reference frequency, 5V tolerant input

2 CLKOUT13 Buffered clock output

3 VDD 3.3V supply

4 SS%4 Spread Spectrum Selection

5 GND Ground

6 CLKOUT23 Buffered clock output

7 CLKOUT33 Buffered clock output

8 DLY CNTRL

9 SSON4

10 CLKOUT43 Buffered clock output

11 CLKOUT53 Buffered clock output

12 GND Ground

13 VDD 3.3V supply

14 CLKOUT63 Buffered clock output

15 CLKOUT73 Buffered clock output

16 CLKOUT83 Buffered clock output

Notes:

1. This output is driven and has an internal feedback for the PLL.

2. Weak pull-down. 3. Weak pull-down on all outputs. 4. Weak pull-up on these inputs.

1,3

Buffered clock output

The pin is used to skew the outputs such that they align with the input. The skew can

is in the range of 100-200pS

Spread Spectrum enable and disable option. When SSON is HIGH, the spread

spectrum is enabled and when LOW, it turns off the spread spectrum.

Zero Cycle Slip Peak EMI Reduction IC 3 of 16

Notice: The information in this document is subject to change without notice.

July 2005

ASM3P623S00A/B/C/D/E/F

rev 1.0

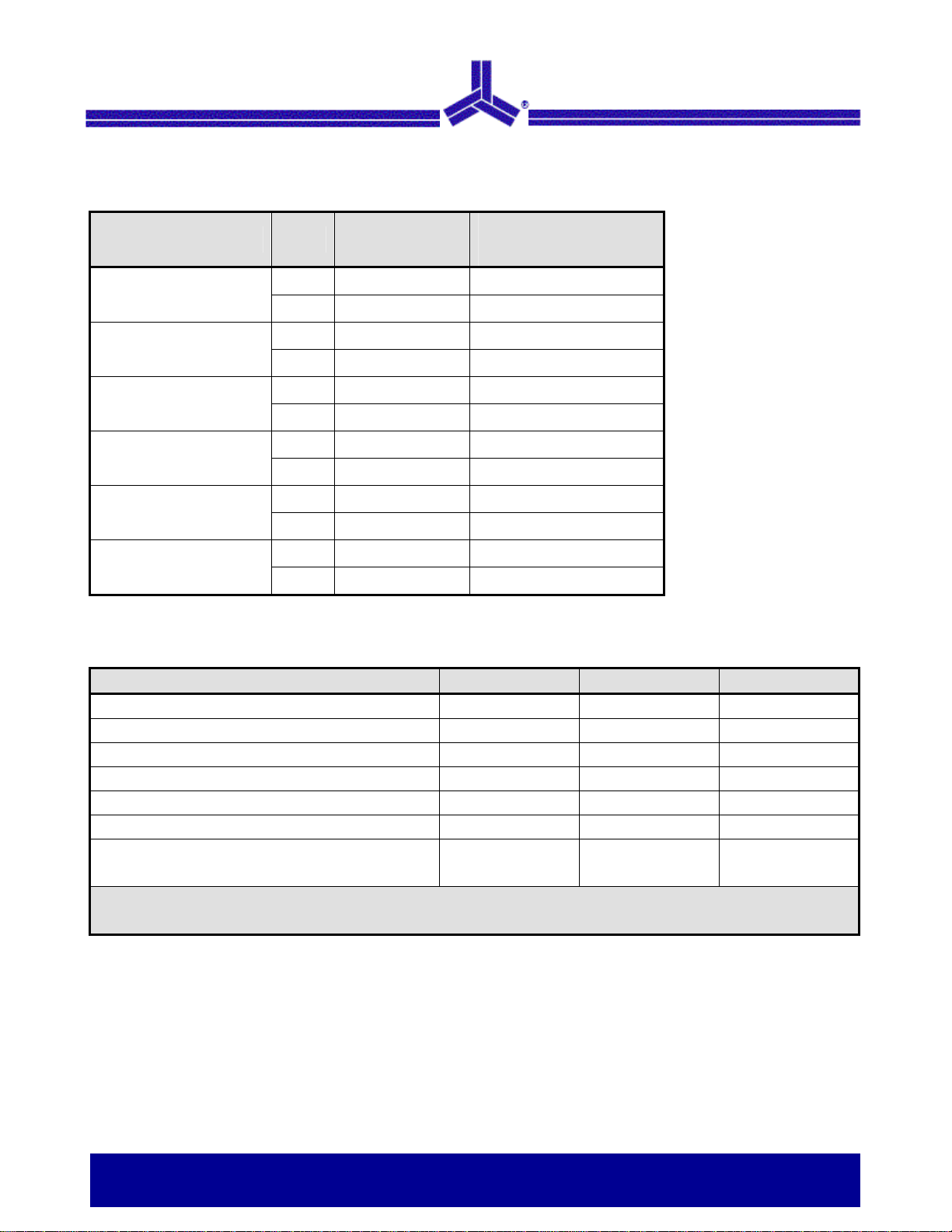

Differential Cycle Slips and Spread Spectrum Control Table

(Note: The values given in the table are for an input frequency of 32 MHz)

Device SS% Deviation

ASM3P623S00A

ASM3P623S00B

ASM3P623S00C

ASM3P623S00D

ASM3P623S00E

0 ±0.5 % 0.125

1 ±1 % 0.25

0 ±0.25 % 0.125

1 ±0.5 % 0.25

0 ±0.125 % 0.125

1 ±0.25 % 0.25

0 ±0.5 % 0.125

1 ±1 % 0.25

0 ±0.25 % 0.125

1 ±0.5 % 0.25

Differential Cycle Slips

(Nd)

ASM3P623S00F

0 ±0.125 % 0.125

1 ±0.25 % 0.25

Absolute Maximum Ratings

Parameter Min Max Unit

Supply Voltage to Ground Potential -0.5 +7.0 V

DC Input Voltage (Except CLKIN) -0.5 VDD + 0.5 V

DC Input Voltage (CLKIN) -0.5 7 V

Storage Temperature -65 +150 °C

Max. Soldering Temperature (10 sec) 260 °C

Junction Temperature 150 °C

Static Discharge Voltage

(As per JEDEC STD22- A114-B)

Note: These are stress ratings only and functional usage is not implied. Exposure to absolute maximum ratings for prolonged periods can affect device

reliability.

2000 V

Zero Cycle Slip Peak EMI Reduction IC 4 of 16

Notice: The information in this document is subject to change without notice.

July 2005

ASM3P623S00A/B/C/D/E/F

rev 1.0

Operating Conditions for ASM3P623S00A/B/C and ASM3P623S00D/E/F Devices

Parameter Description Min Max Unit

VDD Supply Voltage 3.0 3.6 V

TA Operating Temperature (Ambient Temperature) 0 70 °C

CL Load Capacitance 30 pF

CIN Input Capacitance 7 pF

Electrical Characteristics for ASM3P623S00A/B/C and ASM3P623S00D/E/F

Parameter Description Test Conditions Min Typ Max Unit

VIL Input LOW Voltage5 0.8 V

VIH Input HIGH Voltage5 2.0 V

IIL Input LOW Current VIN = 0V 50 µA

IIH Input HIGH Current VIN = VDD 100 µA

VOL Output LOW Voltage6 I

VOH Output HIGH Voltage6 I

IDD Supply Current Unloaded outputs 15 mA

Zo Output Impedance 23 Ω

Switching Characteristics for ASM3P623S00A/B/C and ASM3P623S00D/E/F

= 8mA 0.4 V

OL

= -8mA 2.4 V

OH

7

Parameter Description Test Conditions Min Typ Max Unit

1/t1 Output Frequency 30pF load 20 50 MHz

Duty Cycle

t3 Output Rise Time 6 Measured between 0.8V and 2.0V 2.5 nS

t4 Output Fall Time 6 Measured between 2.0V and 0.8V 2.5 nS

t5 Output-to-output skew

t6 Delay, CLKIN Rising Edge to

CLKOUT Rising Edge

t7 Device-to-Device Skew

tJ Cycle-to-cycle jitter

t

PLL Lock Time 6 Stable power supply, valid clock presented

LOCK

Notes:

5. CLKIN input has a threshold voltage of VDD/2

6. Parameter is guaranteed by design and characterization. Not 100% tested in production

7. All parameters specified with loaded outputs.

6

= (t2 / t1) * 100 Measured at VDD/2 40 50 60 %

6

All outputs equally loaded 250 pS

Measured at VDD /2

6

6

Measured at VDD/2 on the CLKOUT pins

of the device

6

Loaded outputs 200 pS

on CLKIN pin

±350 pS

700 pS

1.0 mS

Zero Cycle Slip Peak EMI Reduction IC 5 of 16

Notice: The information in this document is subject to change without notice.

Loading...

Loading...