Alliance Semiconductor AS7C1024B Service Manual

March 2004

Features

• Industrial and commercial temperatures

• Organization: 131,072 words x 8 bits

• High speed

- 10/12/15/20 ns address access time

- 5/6/7/8 ns output enable access time

• Low power consumption: ACTIVE

- 605 mW / max @ 10 ns

• Low power consumption: STANDBY

- 55 mW / max CMOS

• 6T 0.18u CMOS technology

• Easy memory expansion with CE1

• TTL/LVTTL-compatible, three-state I/O

• 32-pin JEDEC standard packages

, CE2, OE inputs

®

5V 128K X 8 CMOS SRAM

- 300 mil SOJ

- 400 mil SOJ

- 8 × 20mm TSOP 1

- 8 x 13.4mm sTSOP 1

• ESD protection ≥ 2000 volts

• Latch-up current ≥ 200 mA

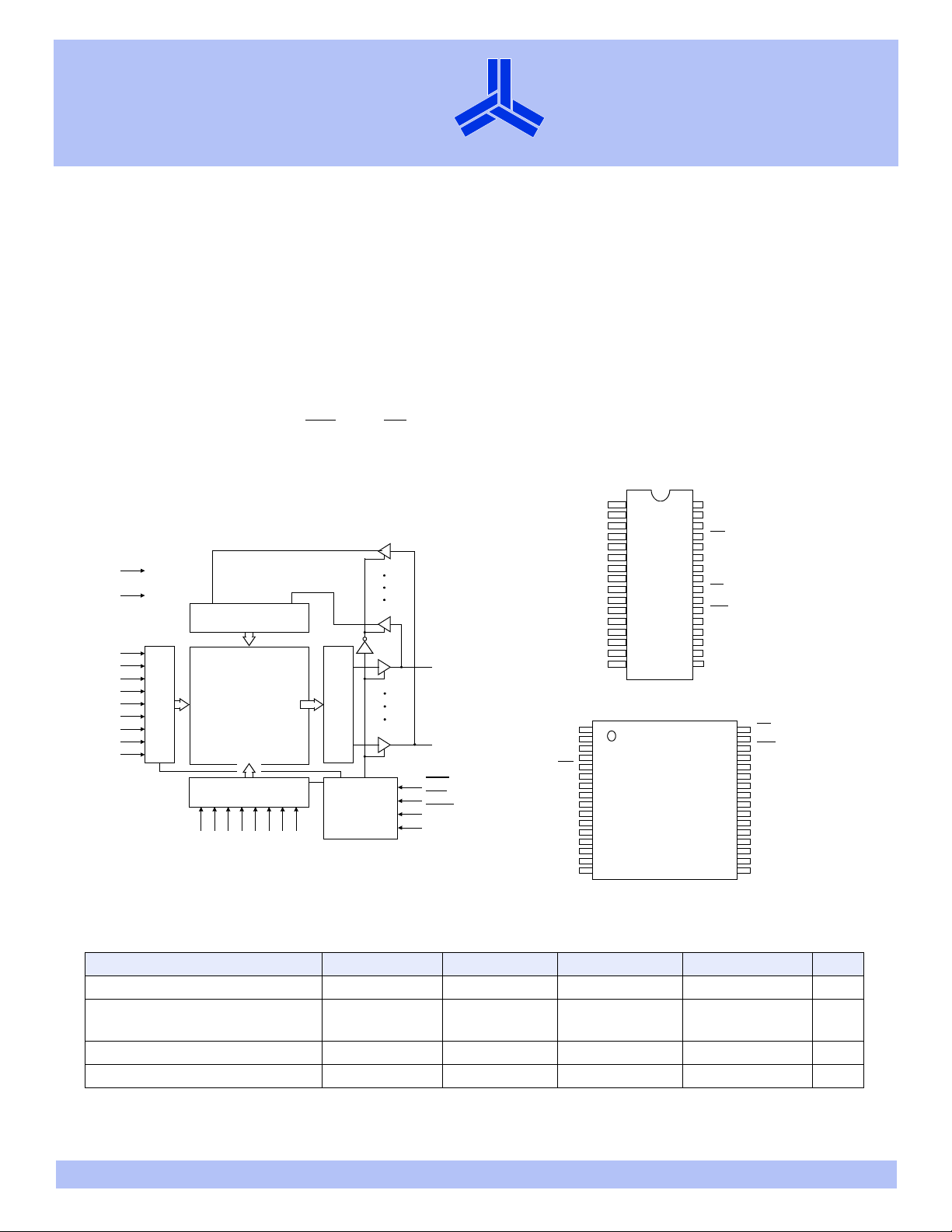

Pin arrangement

32-pin SOJ (300 mil)

32-pin SOJ (400 mil)

AS7C1024B

Logic block diagram

V

CC

GND

Input buffer

A0

A1

A2

A3

A4

A5

A6

A7

A8

512 x 256 x 8

(1,048,576)

Row decoder

Column decoder

A9

A10

Array

A11

A12

A13

A14

A15

A16

Sense amp

Control

circuit

I/O7

I/O0

WE

OE

CE1

CE2

1

NC

A16

A14

A12

I/O0

I/O1

I/O2

GND

A11 OE

A9

A8

A13

WE

CE2

A15

V

CC

NC

A16

A14

A12

A7

A6

A5

A4 A3

2

3

4

5

A7

6

A6

7

A5

8

A4

9

A3

10

A2

11

A1

A0

32-pin (8 x 20mm) TSOP I

32-pin (8 x 13.4mm) sTSOP1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

12

13

14

15

16

AS7C1024B

AS7C1024B

V

32

CC

A15

31

CE2

30

29

WE

28

A13

27

A8

A9

26

A11

25

24

OE

A10

23

22

CE1

21

I/O7

I/O6

20

I/O5

19

18

I/O4

17

I/O3

32

A10

31

CE1

30

I/O7

29

28

I/O6

27

I/O5

26

I/O4

25

I/O3

24

GND

23

I/O2

22

I/O1

21

I/O0

20

A0

19

A1

18

A2

17

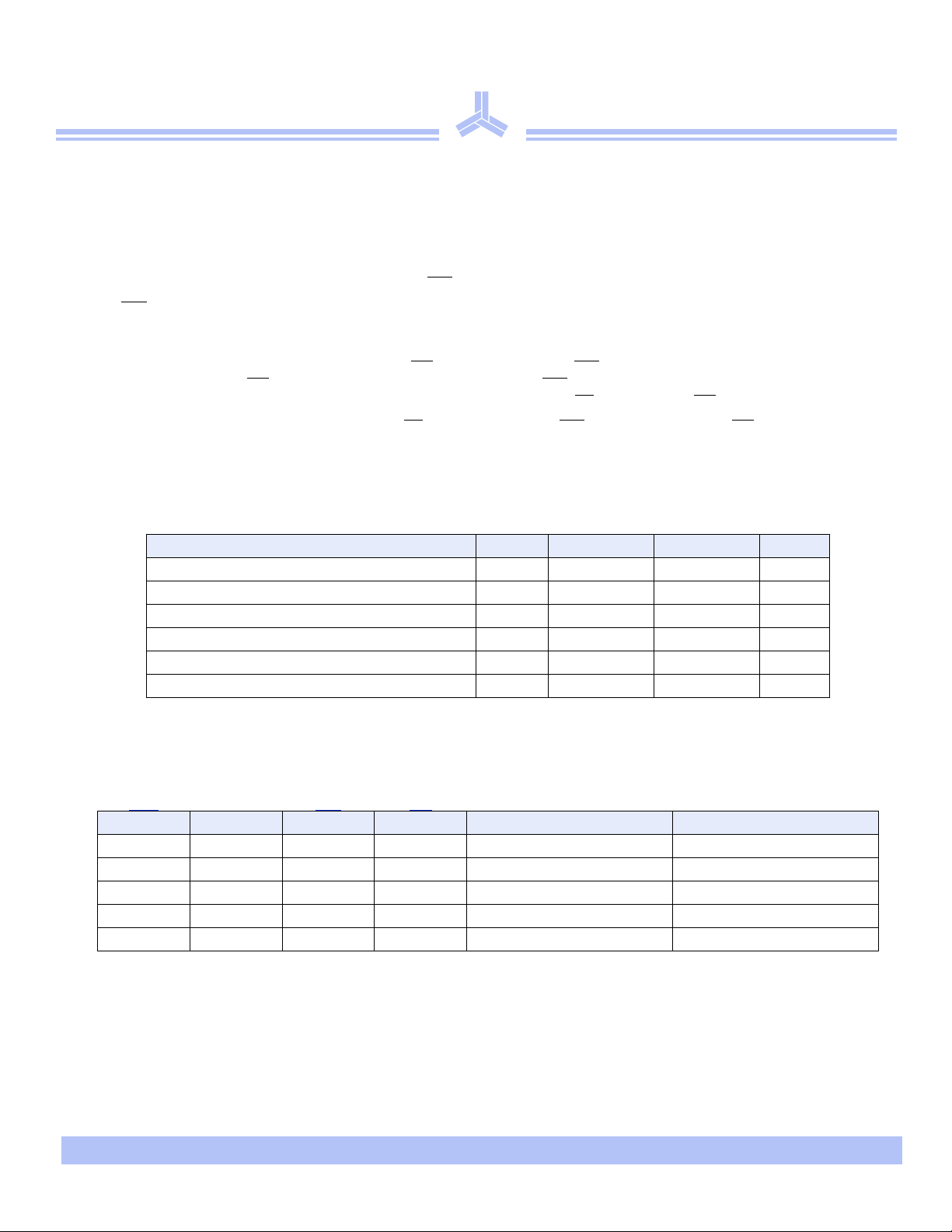

Selection guide

-10

-12

Maximum address access time 10 12 15 20 ns

Maximum output enable access

time

567 8ns

Maximum Operating Current 110 100 90 80 mA

Maximum CMOS standby Current 10 10 10 10 mA

-15 -20 Unit

3/26/04, v 1.2 Alliance Semiconductor P. 1 of 9

Copyright © Alliance Semiconductor. All rights reserved.

AS7C1024B

®

Functional description

The AS7C1024B is a high performance CMOS 1,048,576-bit Static Random Access Memory (SRAM) device organized as 131,072 words x 8

bits. It is designed for memory applications where fast data access, low power, and simple interfacing are desired.

Equal address access and cycle times (tAA, tRC, tWC) of 10/12/15/20 ns with output enable access times (tOE) of 5/6/7/8 ns are ideal for high

performance applications. Active high and low chip enables (CE1

When CE1

static, then full standby power is reached (I

conditions.

A write cycle is accomplished by asserting write enable (WE) and both chip enables (CE1, CE2). Data on the input pins I/O0 through I/O7 is

written on the rising edge of WE (write cycle 1) or the active-to-inactive edge of CE1 or CE2 (write cycle 2). To avoid bus contention, external

devices should drive I/O pins only after outputs have been disabled with output enable (OE) or write enable (WE).

A read cycle is accomplished by asserting o utput enab le (OE ) and both chi p enabl es ( CE 1, CE2), with write enable (WE) high. The ch ips drive I/

O pins with the data word referenced by the input address. When either chip enable is inactive, output enable is inactive, or write enable is active,

output drivers stay in high-impedance mode.

is high or CE2 is low, the devices enter standby mode. If inputs are still toggling, the device will consume ISB power. If the bus is

). For example, the AS7C1024B is guaranteed not to exceed 55 mW under nominal full standby

SB1

, CE2) permit easy memory expansion with multiple-bank systems.

Absolute maximum ratings

Parameter Symbol Min Max Unit

Voltage on V

Voltage on any pin relative to GND V

Power dissipation P

Storage temperature (plastic) T

Ambient temperature with V

DC current into outputs (low) I

Note: Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damag e to the device. This is a stress rating only and functional

operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect reliability.

relative to GND V

CC

applied T

CC

t1

t2

D

stg

bias

OUT

–0.50 +7.0 V

–0.50 VCC +0.50 V

–1.0W

–65 +150 °C

–55 +125 °C

–20mA

Truth table

CE1

H X X X High Z Standby (I

X L X X High Z Standby (I

L H H H High Z Output disable (I

LHHL D

LHLX D

Key: X = don’t care, L = low, H = high

CE2

WE OE

Data Mode

SB

SB

OUT

IN

Read (ICC)

Write (

ICC

, I

, I

SB1

SB1

)

CC

)

)

)

3/26/04, v 1.2 Alliance Semiconductor P. 2 of 9

ecommended operating conditions

Parameter Symbol Min Nominal Max Unit

Supply Voltage V

Input Voltage

Ambient operating

temperature

min = -1.0V for pulse width less than 5ns

IL

max = VCC+2.0V for pulse width less than 5ns.

IH

commercial T

industrial T

AS7C1024B

®

CC

V

IH

V

IL

A

A

4.5 5.0 5.5 V

2.2 - VCC + 0.5 V

–0.5 – 0.8 V

0–70°C

–40 – 85 °C

C operating characteristics (over the operating range)

-10 -12 -15 -20

Parameter Sym Test conditions

Input leakage

current

Output leakage

current

Operating power

supply current

Standby power

supply current

Output voltage

|VCC = Max, VIN = GND to V

|I

LI

V

= Max, CE1 = VIH or

|I

|

LO

CC

CE2 = V

, V

IL

OUT

VCC = Max, CE1 ≤ VIL,

I

CC

I

SB

CE2 ≥ V

I

OUT

IH

= 0 mA

VCC = Max, CE1 ≥ VIH and/or

CE2 ≤ V

IL

VCC = Max, CE1 ≥ VCC–0.2V

I

V

V

SB1

OL

OH

and/or CE2 ≤ 0.2V

V

≤ 0.2V or

IN

≥ VCC – 0.2V, f = 0

V

IN

IOL = 8 mA, VCC = Min - 0.4 – 0.4 – 0.4 – 0.4

IOH = –4 mA, VCC = Min 2.4 - 2.4 – 2.4 – 2.4 –

= GND to V

, f = f

, f = f

Max

Max

,

Min Max Min Max Min Max Min Max

CC

-1–1–1–1µA

-1–1–1–1µA

CC

- 110 – 100 – 90 – 80 mA

-50–45–45–40

-10–10–10–10

Capacitance (f = 1 MHz, Ta = 25 °C, VCC = NOMINAL)

1

Unit

mA

V

2

Parameter Symbol Signals Test conditions Max Unit

Input capacitance C

I/O capacitance C

3/26/04, v 1.2 Alliance Semiconductor P. 3 of 9

IN

I/O

A, CE1, CE2, WE, OE VIN = 0V 5 pF

I/O VIN = V

= 0V 7 pF

OUT

Loading...

Loading...