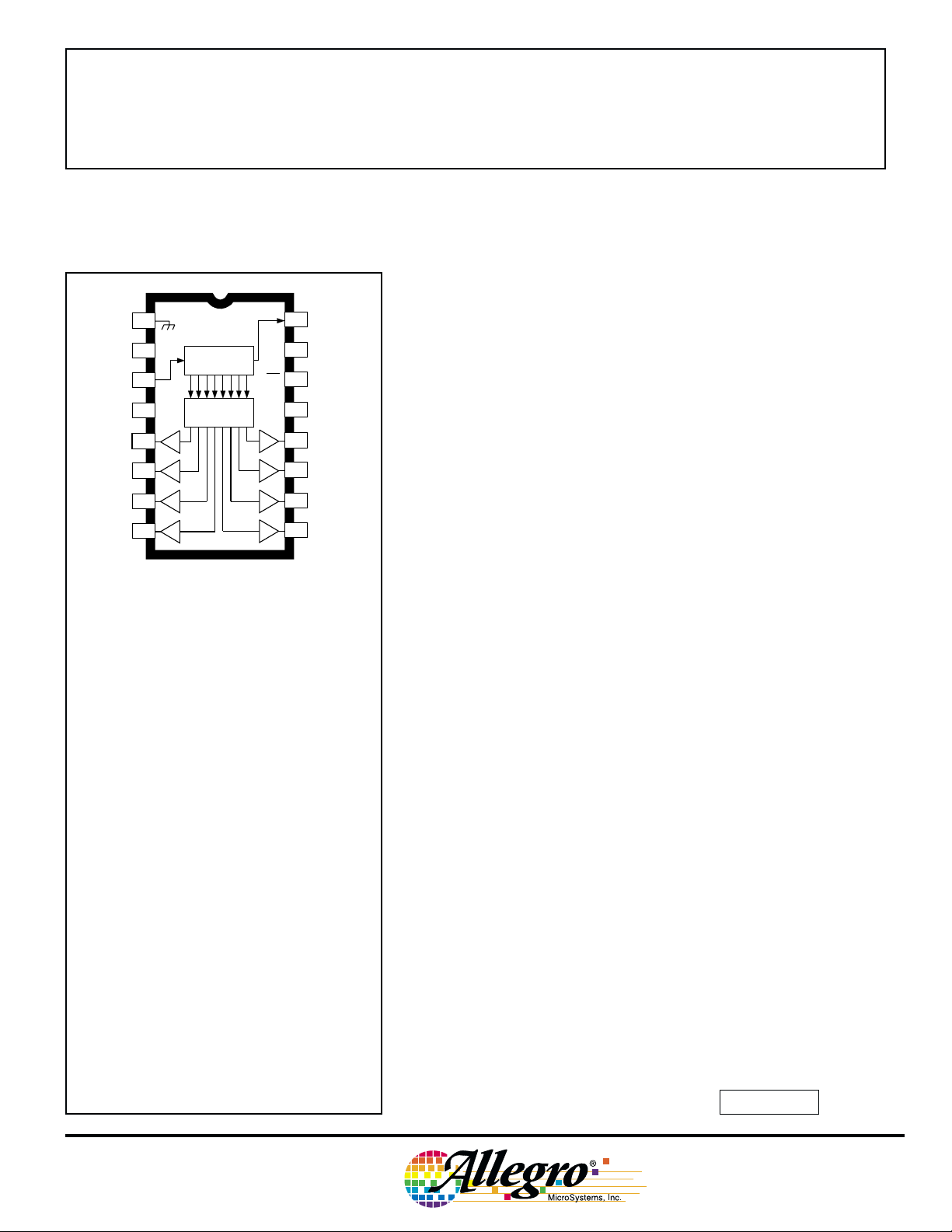

1GROUND

CLOCK CLK

SERIAL

DATA IN

STROBE

OUT

OUT

OUT

OUT

2

3

4

5

1

6

2

7

3

8

4

ST

SHIFT

REGISTER

LATCHES

Data Sheet

5890

AND

26182.12C

5891

BIMOS II 8-BIT SERIAL-INPUT,

LATCHED SOURCE DRIVERS

Frequently applied in non-impact printer systems, the UCN5890A,

SERIAL

16

DATA OUT

V

OE

V

LOGIC

15

DD

SUPPLY

OUTPUT

14

ENABLE

LOAD

13

BB

SUPPLY

12

OUT

8

11

OUT

7

OUT

10

6

OUT

9

5

UCN5890LW, UCN5891A, and UCN5891LW are BiMOS II serial-input,

latched source (high-side) drivers. The octal, high-current smart-power ICs

merge an 8-bit CMOS shift register, associated CMOS latches, and CMOS

control logic (strobe and output enable) with sourcing power Darlington

outputs. Typical applications include multiplexed LED and incandescent

displays, relays, solenoids, and similar peripheral loads to a maximum of

-500 mA per output.

Except for output voltage ratings, these smart high-side driver ICs are

equivalent. The UCN5890A/LW are rated for operation with load supply

voltages of 20 V to 80 V and a minimum output sustaining voltage of 50 V.

The UCN5891A/LW are optimized for operation with supply voltages of 5 V

to 50 V (35 V sustaining).

Dwg. PP-026-2A

Note the suffix ‘A’ devices (DIP) and the suffix

‘LW’ devices (SOIC) are electrically identical and

share a common terminal number assignment.

ABSOLUTE MAXIMUM RATINGS

at TA = +25°C

Output Voltage, V

(UCN5890A & UCN5890LW) .........80 V

(UCN5891A & UCN5891LW) .........50 V

Logic Supply Voltage Range,

VDD....................................4.5 V to 15 V

Driver Supply Voltage Range, V

(UCN5890A/LW)................ 20 V to 80 V

(UCN5891A/LW)............... 5.0 V to 50 V

Input Voltage Range,

V

........................ -0.3 V to VDD + 0.3 V

IN

Continuous Output Current,

I

........................................... -500 mA

OUT

Allowable Package Power Dissipation,

P

......................................... See Graph

D

Operating Temperature Range,

T

.................................. -20°C to +85°C

A

Storage Temperature Range,

T

................................ -55°C to +150°C

S

Caution: CMOS devices have input static

protection, but are susceptible to damage when

exposed to extremely high static electrical

charges.

OUT

BB

BiMOS II devices have higher data-input rates than the original BiMOS

circuits. With a 5 V supply, they will operate to at least 3.3 MHz. At 12 V,

higher speeds are possible. The CMOS inputs are compatible with standard

CMOS and NMOS logic levels. TTL circuits may require the use of appropriate pull-up resistors to ensure a proper input-logic high. A CMOS serial data

output, allows cascading these devices in multiple drive-line applications

required by many dot matrix, alphanumeric, and bar graph displays.

Suffix ‘A’ devices are supplied in a standard dual in-line plastic package

with copper lead frame for enhanced package power dissipation characteristics. Suffix ‘LW’ devices are supplied in a standard wide-body SOIC package

for surface-mount applications. Similar driver, featuring reduced output

saturation voltage, are the UCN5895A and A5895SLW. Complementary,

8-bit serial-input, latched sink drivers are the Series UCN5820A.

FEATURES

■ 50 V or 80 V Source Outputs

■ Output Current to -500 mA

■ Output Transient-Suppression Diodes

■ To 3.3 MHz Data-lnput Rate

■ Low-Power CMOS Logic and Latches

Always order by complete part number, e.g., UCN5891LW .

5890

AND

5891

8-BIT SERIAL-INPUT,

LATCHED SOURCE DRIVERS

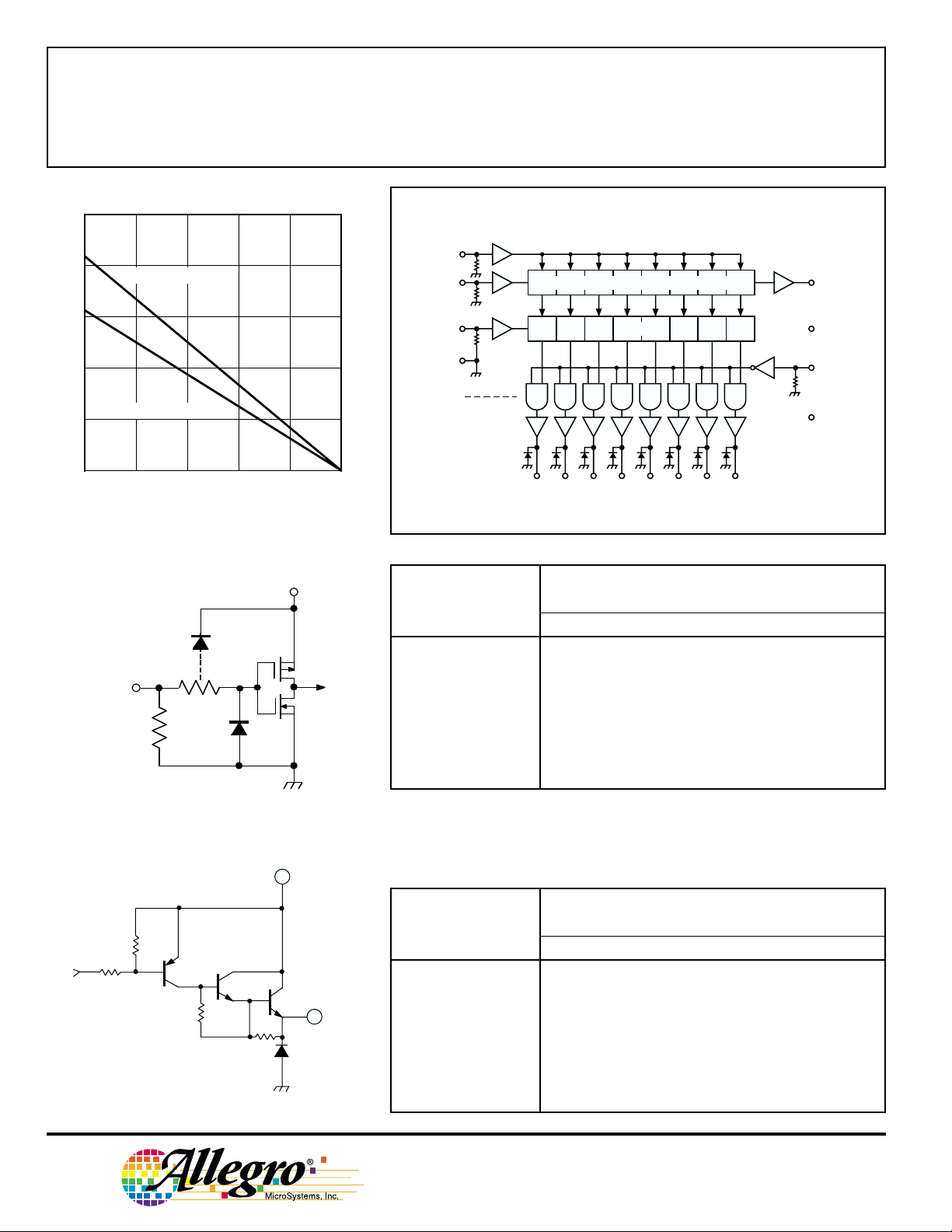

2.5

2.0

1.5

1.0

0.5

ALLOWABLE PACKAGE POWER DISSIPATION IN WATTS

SUFFIX 'A', R = 60°C/W

SUFFIX 'LW', R = 80°C/W

0

25

50 75 100 125 150

AMBIENT TEMPERATURE IN °C

θJA

θJA

Dwg. GP-018B

TYPICAL INPUT CIRCUIT

V

DD

IN

FUNCTIONAL BLOCK DIAGRAM

CLOCK

SERIAL

DATA IN

STROBE

GROUND

MOS

BIPOLAR

Number of UCN5890/91A Max. Allowable Duty Cycle

Outputs On at at T

= -200 mA 50°C60°C70°C

I

OUT

8 53% 47% 41%

7 60% 54% 48%

6 70% 64% 56%

5 83% 75% 67%

4 100% 94% 84%

3 100% 100% 100%

2 100% 100% 100%

1 100% 100% 100%

8-BIT SERIAL-PARALLEL SHIFT REGISTER

LATCHES

OUT1OUT2OUT3OUT4OUT5OUT6OUT7OUT

of

A

8

Dwg. No. A-12,654

SERIAL

DATA OUT

V

DD

OUTPUT

ENABLE

V

BB

Dwg. EP-010-4A

TYPICAL OUTPUT DRIVER

V

BB

OUT

Dwg. No. A-12,648

Number of UCN5890/91LW Max. Allowable Duty Cycle

Outputs On at at T

= -200 mA 50°C60°C70°C

I

OUT

of

A

8 40% 35% 31%

7 45% 41% 36%

6 53% 48% 42%

5 62% 56% 50%

4 80% 71% 62%

3 100% 96% 84%

2 100% 100% 100%

1 100% 100% 100%

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Copyright © 1985, 2000 Allegro MicroSystems, Inc.

5890

AND

8-BIT SERIAL-INPUT,

LATCHED SOURCE DRIVERS

ELECTRICAL CHARACTERISTICS at TA = +25°C, VBB = 80 V (UCN5890A/LW) or 50 V

(UCN5891A/LW), VDD = 5 V and 12 V (unless otherwise noted).

Limits

Characteristic Symbol V

Output Leakage Current I

Output Saturation Voltage V

Output Sustaining Voltage V

Input Voltage V

Input Current I

Input lmpedance Z

Max. Clock Frequency f

Serial Data Output R

Resistance

Turn-On Delay t

Turn-Off Delay t

Supply Current I

Diode Leakage Current I

Diode Forward Voltage V

CE(SAT)

CE(sus)

V

CEX

IN(1)

IN(0)

IN(1)

IN

c

OUT

PLH

PHL

BB

l

DD

R

F

Max. TA = +25°C — -50 µA

50 V I

Max. I

50 V VDD = 5.0 V 3.5 5.3 V

50 V VDD = 5 V to 12 V -0.3 +0.8 V

50 V VDD = VIN = 5.0 V — 50 µA

50 V VDD = 5.0 V 100 — kΩ

50 V 3.3* — MHz

50 V VDD = 5.0 V — 20 kΩ

50 V Output Enable to Output, I

50 V Output Enable to Output, I

50 V All outputs on, All outputs open — 10 mA

50 V VDD = 5 V, All outputs off, Inputs = 0 V — 100 µA

Max. TA = +25°C — 50 µA

Open IF = 350 mA — 2.0 V

BB

Test Conditions Min. Max. Units

TA = +70°C — -100 µA

= -100 mA — 1.8 V

OUT

I

= -225 mA — 1.9 V

OUT

I

= -350 mA — 2.0 V

OUT

= -350 mA, L = 2 mH, UCN5891A/LW 35 — V

OUT

I

= -350 mA, L = 2 mH, UCN5890A/LW 50 — V

OUT

VDD = 12 V 10.5 12.3 V

VDD = VIN = 12 V — 240 µA

VDD = 12 V 50 — kΩ

= 12 V — 6.0 kΩ

V

DD

= -350 mA — 2.0 µs

OUT

= -350 mA — 10 µs

OUT

All outputs off — 200 µA

VDD = 12 V, All outputs off, Inputs = 0 V — 200 µA

VDD = 5 V, One output on, All Inputs = 0 V — 1.0 mA

VDD = 12 V, One output on, All Inputs = 0 V — 3.0 mA

TA = +70°C — 100 µA

5891

NOTES: Turn-off delay is influenced by load conditions. Systems applications well below the specified output loading may require

timing considerations for some designs, i.e., multiplexed displays or when used in combination with sink drivers in a totem

pole configuration.

Positive (negative) current is defined as going into (coming out of) the specified device pin.

* Operation at a clock frequency greater than the specified minimum value is possible but not warranteed.

www.allegromicro.com

Loading...

Loading...