Page 1

STR-S5707

1234567

8

9

STR-S5703

QUASI-RESONANT FLYBACK

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

OFF-LINE SWITCHING REGULATOR

STR-S5703

OFF-LINE SWITCHING REGULATOR

– WITH BIPOLAR SWITCHING TRANSISTOR

The STR-S5703 is specifically designed to meet the requirement

for increased integration and reliability in off-line quasi-resonant flyback

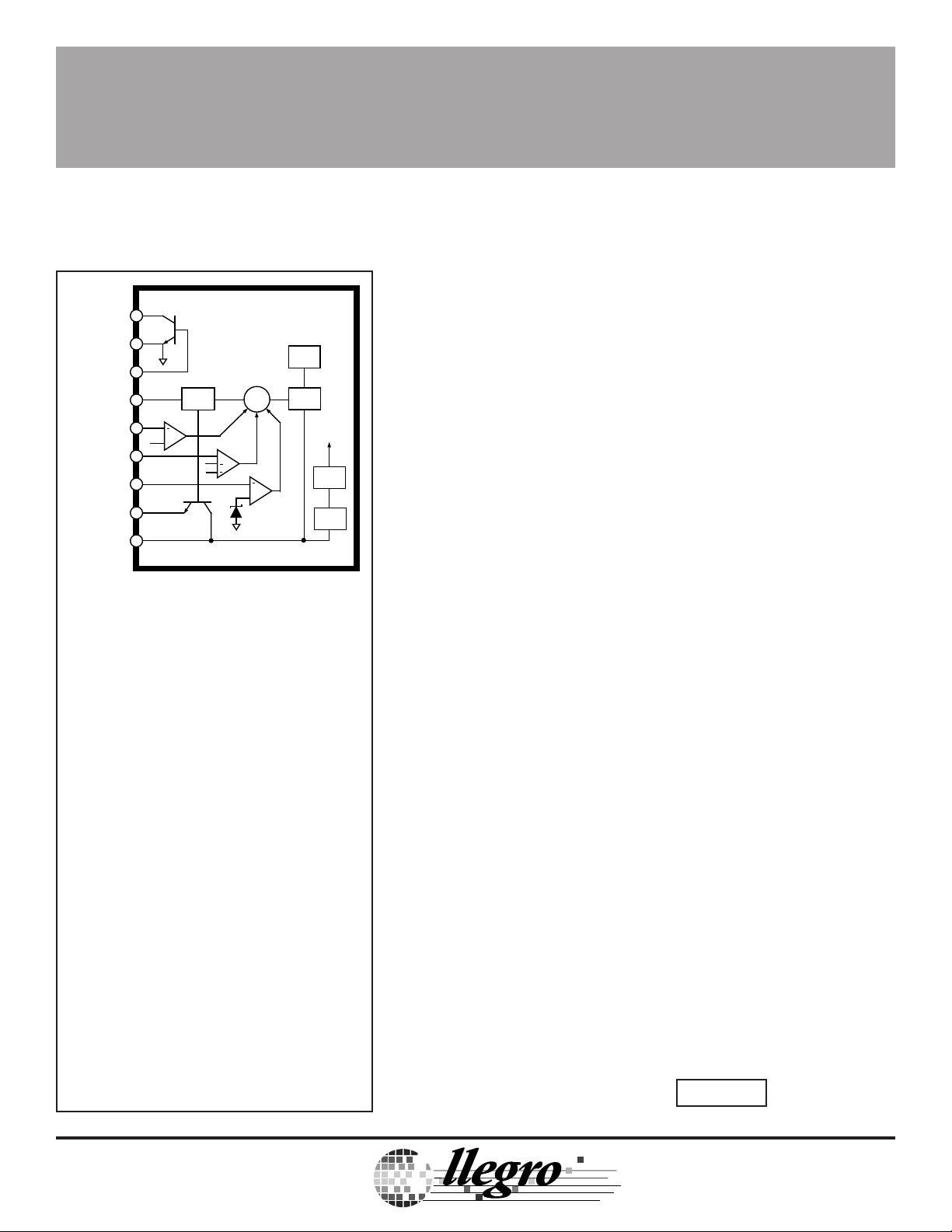

COLLECTOR

COMMON

BASE

SINK

OVER-CURRENT

PROTECTION

INHIBIT

32 V SENSE

DRIVE

DRIVE

+

+

V

IN

OSC.

FAULT

S

FAULT

LATCH

R

+

REF.

UVLO

Dwg. PK-004

ABSOLUTE MAXIMUM RATINGS

Supply Voltage, VIN........................... 15 V

Output Voltage, V

V

................................................ 7 V

EBO

Continuous Output Current,

IC.................................................. 6.0 A

1 ms Single-Pulse Output Current,

ICM................................................. 12 A

Sink Current, IS................................. 1.5 A

Drive Current, ID.......................... -700 mA

Inhibit Voltage, V

Over-Current Protection Voltage Range,

V

............................................ ±3.5 V

OCP

Insulation Voltage, V

Package Power Diss., PD........ See Graph

Output Junction Temperature, TJ.. +150°C

Internal Frame Temperature, TF... +125°C

Operating Temperature Range,

TA............................... -20°C to +125°C

Storage Temperature Range,

T

............................. -40°C to +125°C

stg

....................... 500 V

CEX

........................... 15 V

INH

WM(RMS)

.......... 2000 V

converters with indirect feedback. The device incorporates the primary

control and proportional drive circuit with a third-generation high-voltage

bipolar switching transistor.

Crucial system parameters such as maximum ON time and OFF

time are fixed during manufacture. Local control circuit decoupling and

layout are optimized within each device.

Cycle-by-cycle current limiting, under-voltage lock-out with hysteresis, over-voltage protection, and thermal shutdown protect these

devices during all normal and overload conditions. Over-voltage

protection and thermal shutdown are latched after a short delay. A

primary-side error amplifier with reference is included to facilitate

regulation from an auxiliary or bias winding of the power transformer. A

versatile triple-level inhibit circuit includes the OFF time synchronization

required to establish quasi-resonant operation. The inhibit function has

also been expanded to initiate operation in stand-by mode in which the

power supply delivers a small fraction of the steady-state output power.

The dual requirements of dielectric isolation and low transient thermal

impedance and steady-state thermal resistance are satisfied in an overmolded single-in-line power package.

Proven in substantial volumes, this device and its fixed-frequency

counterparts represents a significant advance in off-line SMPS reliability

growth and integration. Similar devices with increased ratings are the

STR-S5707 and STR-S5708.

FEATURES

■ Quasi-Resonant Operation for Low EMI and High Efficiency

■ Output Power to 140 W

■ Low-Power Output Standby Mode

■ Indirect Feedback from Auxiliary Winding

Reduces External Component Count

■ Pulse-by-Pulse Over-Current Protection

■ Latched Over-Voltage and Thermal Protection

■ Third-Generation Switching Transistor with Proportional Drive

■ Maximum ON Time and Off Time Set During Manufacture

■ Internal Under-Voltage Lockout with Hysteresis

■ Over-Molded SIP with Integral Isolated Heat Spreader

Always order by complete part number: STR-S5703 .

Data Sheet

28114.1

TM

TM

A

MicroSystems, Inc.

Page 2

STR-S5703

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

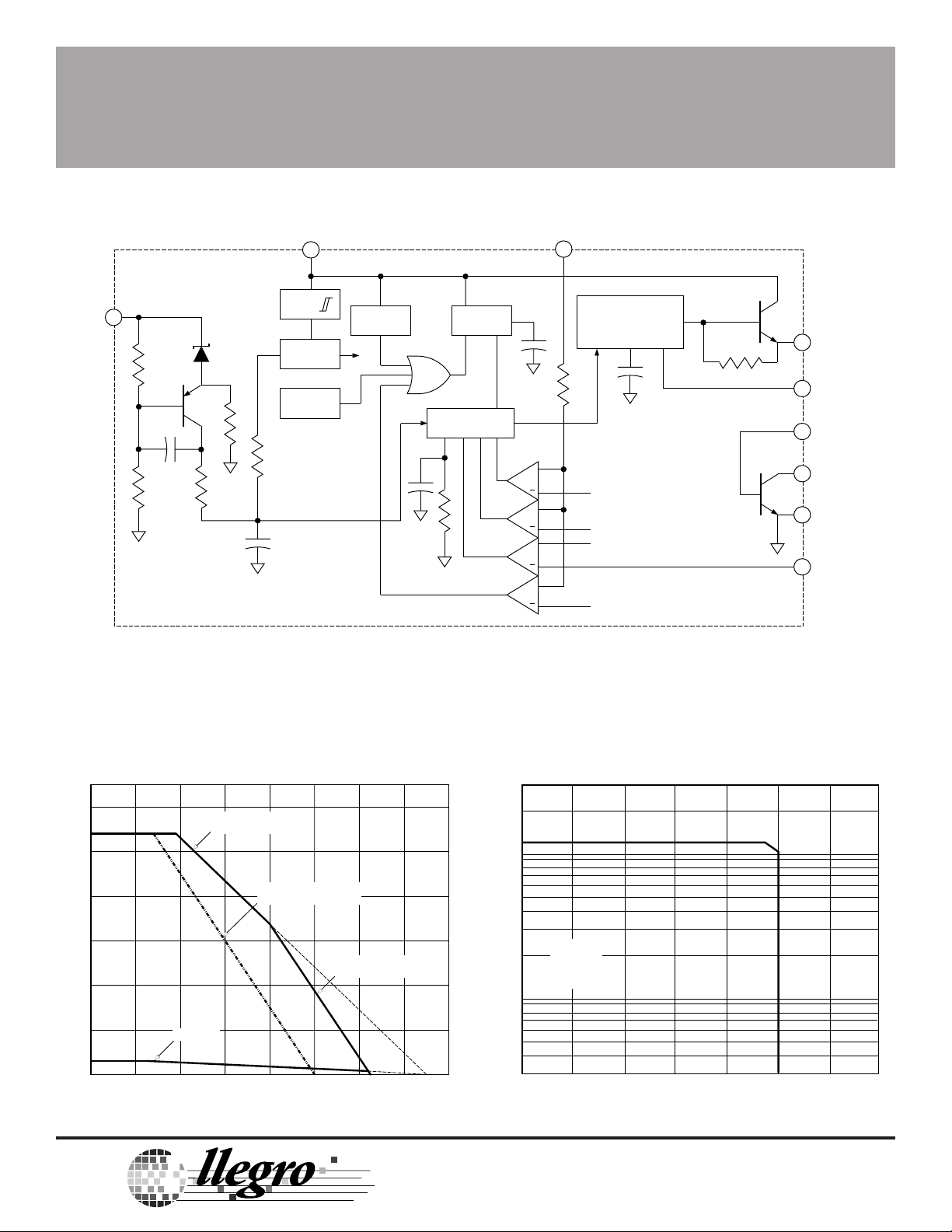

FUNCTIONAL BLOCK DIAGRAM

SENSE

V

IN

9

R

FAULT

LATCH

S

OSC.

R

toff

R

ton

3300 pF

UVLO

REF.

TSD

7

1500 pF

OVER-VOLT.

PROTECT

INHIBIT

6

PROPORTIONAL

Q

+

+

+

+

DRIVE

1 kΩ

0.75 V

1.4 V

-1 V

5.1 V

DRIVE

8

SINK

4

BASE

3

COLLECTOR

1

COMMON

2

OVER-CURRENT

5

PROTECTION

Dwg. FK-001-1

ALLOWABLE PACKAGE POWER DISSIPATION MAXIMUM SAFE OPERATING AREA

30

60

54 W

40

20

3.2 W

ALLOWABLE PACKAGE POWER DISSIPATION in WATTS

0

20 60 100

A

MOUNTING SURFACE

TEMPERATURE

FREE AIR

RECOMMENDED MAX.

FRAME TEMP. = +100°C

TEMPERATURE in °C

MicroSystems, Inc.

LIMITED BY FRAME

TEMP. = +125°C MAX.

TM

TM

10

5.0

3.0

L = 6 mH

I

B1

= 2.5 A

I

B2

= 0.8 A

t

on

= 100 µs

dc < 1%

1.0

COLLECTOR CURRENT in AMPERES

0.5

0.3

140

Dwg. GK-003-2

115 Northeast Cutoff, Box 15036

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Worcester, Massachusetts 01615-0036 (508) 853-5000

Copyright © 1994 Allegro MicroSystems, Inc.

0 200 400 600

100 300 500 700

COLLECTOR-EMITTER VOLTAGE in VOLTS

Dwg. GK-002-2A

Page 3

STR-S5707

STR-S5703

QUASI-RESONANT FLYBACK

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

OFF-LINE SWITCHING REGULATOR

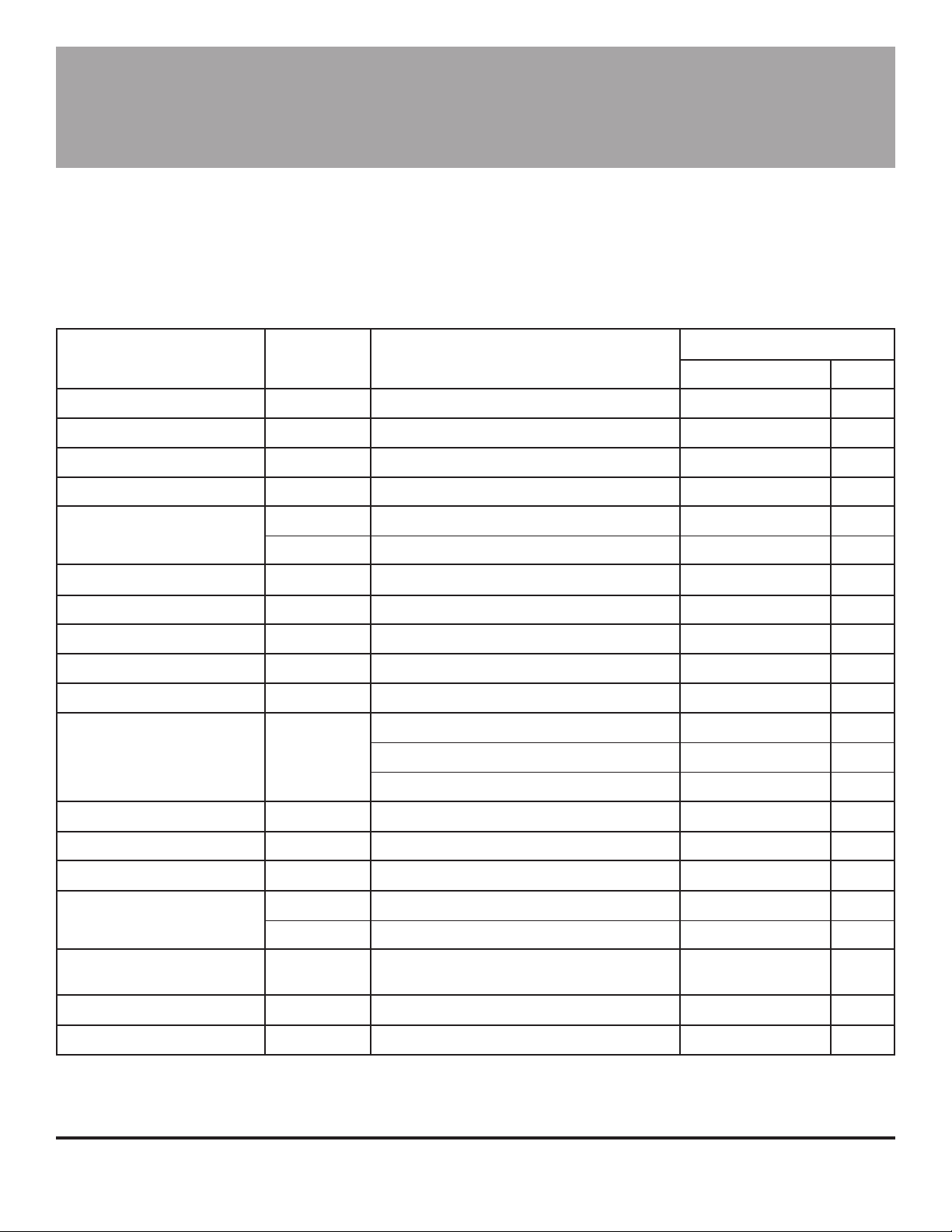

ELECTRICAL CHARACTERISTICS at TA = +25°C, VIN = 8.5 V, voltage measurements are

referenced to Common (pin 2) (unless otherwise noted).

Limits

Characteristic Symbol Test Conditions Min. Typ. Max. Units

On-State Voltage V

Under-Voltage Lockout V

Over-Voltage Threshold V

OVP(th)

Output Leakage Current I

Output Saturation Voltage V

CE(sat)

V

BE(sat)

DC Current Gain h

Maximum ON Time t

Minimum OFF Time t

Over-Current Threshold V

Sense Voltage V

Inhibit Threshold Voltage V

OCP(th)

SENSE

INH(th)

Latch Holding Current I

Latch Reset Voltage V

Ref. Voltage Temp. Coeff. α

Supply Current I

Insulation RMS Voltage V

IN(ON)

I

IN(OFF)

WM(RMS)

INT

INQ

CEX

FE

on

off

INH

VZ

Turn-on, increasing V

Turn-off, decreasing V

IN

IN

7.6 8.0 8.4 V

4.6 4.9 5.2 V

9.2 – 10.7 V

VCE = 500 V, VBE = -1.5 V – – 100 µA

IC = 2 A, IB = 400 mA – – 400 mV

IC = 2 A, IB = 400 mA – – 1.5 V

VCE = 4 V, IC = 1 A 23 – 46 –

33 – 41 µs

45 – 55 µs

-0.88 -1.0 -1.12 V

I

= 3.2 mA 31.7 32.0 32.3 V

SENSE

Oscillation stops 0.65 0.75 0.85 V

Oscillation synchronized – 1.4 2.0 V

Oscillation stops (fault latch set) 3.2 5.1 5.8 V

VIN reduced from 10.7 V to 4 V – – 500 µA

Q

IIN ≤ 100 µA, VIN reduced from 10.7 V 2.5 3.1 – V

-20°C ≤ TF ≤ +100°C, IIN = 3.2 mA – 2.5 – mV/°C

Operating 15 – 28 mA

– – 200 µA

All terminals simultaneous reference 2000 – – V

metal plate against backside

Thermal Shutdown T

Thermal Resistance R

J

θJM

Output junction to mounting surface – 2.0 – °C/W

125 150 – °C

NOTES: Negative current is defined as coming out of (sourcing) the specified device terminal.

Typical Data is for design information only.

Page 4

STR-S5703

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

TYPICAL CHARACTERISTICS

100

50

30

V = 4 V

CE

10

DC CURRENT GAIN

5.0

3.0

1.0

0.01 0 .1 1.0 10 100

0.03 0.3 3.0 30

COLLECTOR CURRENT in AMPERES

Dwg. GK-001-1

A

TM

TM

MicroSystems, Inc.

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Page 5

STR-S5707

STR-S5703

QUASI-RESONANT FLYBACK

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

OFF-LINE SWITCHING REGULATOR

TYPICAL QUASI-RESONANT FLYBACK CONVERTER

WARNING: lethal potentials are present. See below.

+ OUTPUT

AC INPUT

RECTIFIER

FULL-BRIDGE

7

+

WARNING —

Circuit designs that embody these components must conform with applicable safety requirements.

Precautions must be taken to prevent accidental contact with power-line potentials.

Do not connect grounded test equipment.

9

R

SQ

+

+

+

+

6

8

4

3

1

2

5

+

+

+

★

APPLICATIONS INFORMATION

These devices are designed to be operated at lethal voltages and energy levels.

+

– OUTPUT

Dwg. EK-005A

The use of an isolation transformer is recommended during circuit development and breadboarding.

Recommended mounting hardware torque:

4.34 – 5.79 lbf•ft (6 – 8 kg•cm or 0.588 – 0.784 Nm).

Recommended metal-oxide-filled, alkyl-degenerated oil base, silicone grease:

Dow Corning 340, or equivalent

Page 6

STR-S5703

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

Dimensions in Inches

(Based on 1 mm = 0.03937")

UGN3055U AND UGS3055U

MULTIPLEXED TWO-WIRE HALL EFFECT SENSOR IC

0.953 ±0.008

T REF.

0.610

±0.008

0.118

1.49 ±0.012

M

0.130

±0.008

0.709 ±0.008

ø

0.216

±0.008

0.130

±0.004

0.033

+0.008

–0.004

1

0.016

PACKAGE

CENTER

9

LEAD

CENTER

0.100

±0.004

0.177

±0.028

0.276

±0.016

0.216

0.026

+0.008

–0.004

Dwg. MK-003-9 in

A

TM

TM

MicroSystems, Inc.

NOTE: Exact body and lead configuration at vendor’s option within limits shown.

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Page 7

STR-S5707

STR-S5703

QUASI-RESONANT FLYBACK

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

OFF-LINE SWITCHING REGULATOR

Dimensions in Millimeters

24.2

±0.2

T REF

15.5 ±0.2

3.0

3.3

±0.2

M

ø

5.5

±0.2

23.0 ±0.3

0.85

+0.2

–0.1

1

0.4

PACKAGE

CENTER

9

LEAD

CENTER

2.54

±0.1

18.0 ±0.2

0.65

+0.2

–0.1

3.3

±0.1

7.0

±0.4

5.5

4.5

±0.7

Dwg. MK-003-9 mm

NOTE: Exact body and lead configuration at vendor’s option within limits shown.

Page 8

STR-S5703

QUASI-RESONANT FLYBACK

OFF-LINE SWITCHING REGULATOR

POWER CONVERSION/POWER MANAGEMENT

SELECTION GUIDES

SWITCHING REGULATOR PMCMs

Part

Number* Application AC In Max P

5703 Quasi-Resonant Flyback Converter 110/120 V 140 W 500 V 6 A Bipolar

5707 Quasi-Resonant Flyback Convertter 85-265 V 90 W 850 V 6 A Bipolar

220/240V 140 W

5708 Quasi-Resonant Flyback Converter 85-265 V 120 W 850 V 7.5 A Bipolar

220/240 V 180 W

6511 Quasi-Resonant Flyback Converter 110/120 V 180 W 450 V 11 A MOSFET

6525 Quasi-Resonant Flyback Converter 85-265 V 120 W 600 V 6 A MOSFET

O

Power Switch

6529 Quasi-Resonant Flyback Converter 220/240 V 180 W 800 V 5.4 A MOSFET

6703 Quasi-Resonant Flyback Converter 110/120V 140 W 500 V 6 A Bipolar

6704 Quasi-Resonant Flyback Converter 110/120 V 100 W 500 V 5 A Bipolar

6707 Quasi-Resonant Flyback converter 85-265 V 90 W 850 V 6 A Bipolar

220/240 V 140 W

6708 Quasi-Resonant Flyback Converter 85-265 V 120 W 850 V 7.5 A Bipolar

220/240 V 180 W

6709 Quasi-Resonant Flyback Converter 85-265 V 160 W 850 W 10 A Bipolar

220/240 V 220 W

* Complete part number includes additional characters to indicate operating temperature range and package style.

LINEAR REGULATOR ICs

Part

Number* V

8184 3.0 V 10 V 300 mV @ 125 mA 250 mA SOT-89

8187 3.3 V 10 V 300 mV @ 125 mA 250 mA SOT-89

* Complete part number includes additional characters to indicate operating temperature range and package style.

Also — 83145 and 84145 Latched, Universal Input-Voltage Switches.

O

Max DC In Max Dropout Max I

O

Package

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such

departures from the detail specifications as may be required to permit improvements in

the design of its products. Components made under military approvals will be in

accordance with the approval requirements.

The information included herein is believed to be accurate and reliable. However,

Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements

of patents or other rights of third parties which may result from its use.

TM

TM

A

MicroSystems, Inc.

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Loading...

Loading...