Allegro A6810SLWP, A6810SEP, A6810SA, A6810ELW, A6810EEP Datasheet

...

DABiC-IV, 10-BIT SERIAL-INPUT,

LATCHED SOURCE DRIVERS

A6810xA

Data Sheet

26182.124B

ABSOLUTE MAXIMUM RATINGS

at TA = 25°C

Logic Supply Voltage, VDD................... 7.0 V

Driver Supply Voltage, V

BB

................... 60 V

Continuous Output Current Range,

I

OUT

......................... -40 mA to +15 mA

Input Voltage Range,

V

IN

....................... -0.3 V to VDD + 0.3 V

Package Power Dissipation,

P

D

........................................ See Graph

Operating Temperature Range, T

A

(Suffix ‘E–’) .................. -40°C to +85°C

(Suffix ‘S–’) .................. -20

°C to +85°C

Storage Temperature Range,

T

S

............................... -55°C to +125°C

Caution: These CMOS devices have input

static protection (Class 2) but are still

susceptible to damage if exposed to

extremely high static electrical charges.

The A6809– and A6810– devices combine 10-bit CMOS shift

registers, accompanying data latches and control circuitry with bipolar

sourcing outputs and pnp active pull downs. Designed primarily to

drive vacuum-fluorescent displays, the 60 V and -40 mA output ratings

also allow these devices to be used in many other peripheral power

driver applications. The A6809– and A6810– feature an increased data

input rate (compared with the older UCN/UCQ5810-F) and a controlled output slew rate. The A6809xLW and A6810xLW are identical

except for pinout.

The CMOS shift register and latches allow direct interfacing with

microprocessor-based systems. With a 3.3 V or 5 V logic supply,

typical serial-data input rates are up to 33 MHz.

A CMOS serial data output permits cascade connections in applications requiring additional drive lines. Similar devices are avail-able as

the A6811– (12 bits), A6812– (20 bits), and A6818– (32 bits).

The A6809– and A6810– output source drivers are npn Darlingtons, capable of sourcing up to 40 mA. The controlled output slew rate

reduces electromagnetic noise, which is an important consideration in

systems that include telecommunications and/or microprocessors and

to meet government emissions regulations. For inter-digit blanking, all

output drivers can be disabled and all sink drivers turned on with a

BLANKING input high. The pnp active pull-downs will sink at least

2.5 mA.

All devices are available in two temperature ranges for optimum

performance in commercial (suffix S-) or industrial (suffix E-) applications. The A6810– is provided in three package styles for through-hole

DIP (suffix -A), surface-mount SOIC (suffix -LW), or minimum-area

surface-mount PLCC (suffix -EP). The A6809– is provided in the

SOIC (suffix -LW) only. Copper lead frames, low logic-power dissipation, and low output-saturation voltages allow all devices to source

25 mA from all outputs continuously over the maximum operating

temperature range.

FEATURES

■ Controlled Output Slew Rate

■ High-Speed Data Storage

■ 60 V Minimum

Output Breakdown

■ High Data Input Rate

■ PNP Active Pull-Downs

Complete part number includes a suffix to identify operating

temperature range (E- or S-) and package type (-A, -EP, or -LW).

Always order by complete part number, e.g., A6810SLW .

6809

AND

6810

■ Low Output-Saturation Voltages

■ Low-Power CMOS Logic

and Latches

■ Improved Replacements

for TL4810–, UCN5810–,

and UCQ5810–

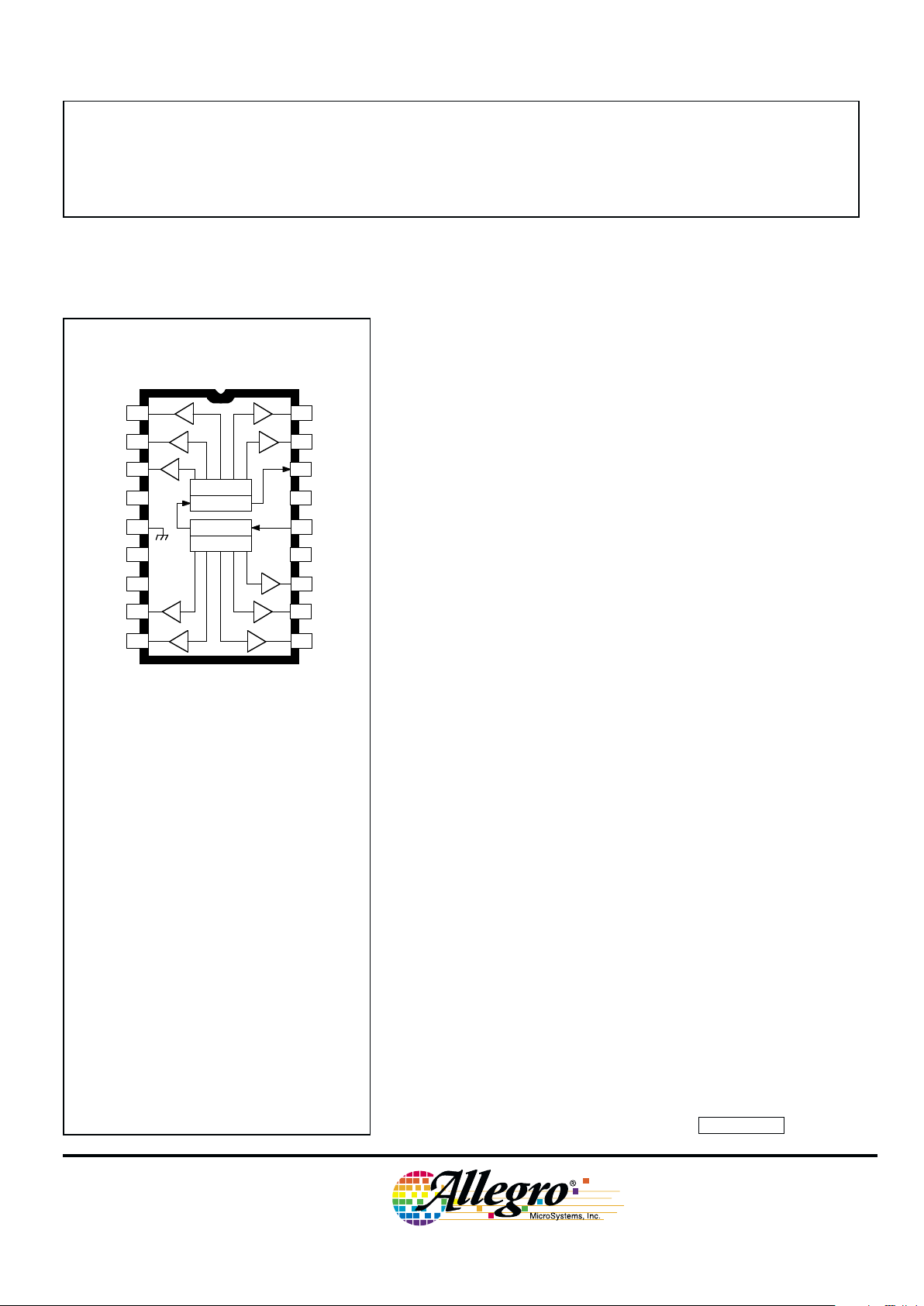

2

3

4

5

6

7

8

910

11

12

13

14

15

16

17

18

SERIAL

DATA OUT

LOAD

SUPPLY

SERIAL

DATA IN

BLANKING

LOGIC

SUPPLY

STROBE

GROUND

CLOCK

CLK

V

ST

BLNK

DD

BB

V

OUT

9

OUT

10

OUT

1

OUT

2

OUT

3

Dwg. PP-029

OUT

8

OUT

7

OUT

6

OUT

5

OUT

4

1

LATCHES

REGISTER

REGISTER

LATCHES

6809

AND

6810

10-BIT SERIAL-INPUT,

LATCHED SOURCE DRIVERS

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Copyright © 1998, 2000 Allegro MicroSystems, Inc.

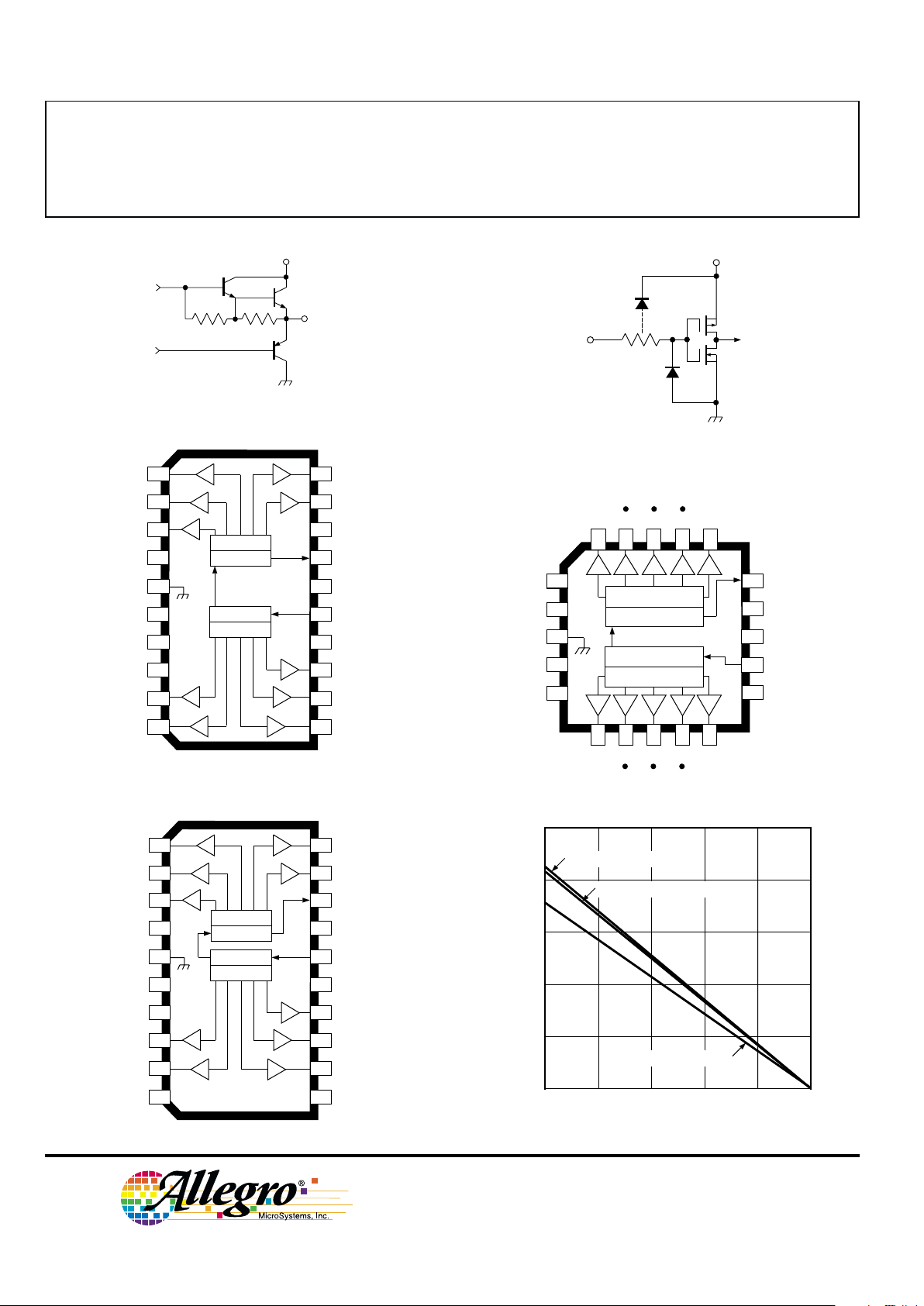

A6810xEP

TYPICAL OUTPUT DRIVER TYPICAL INPUT CIRCUIT

A6809xLW

SERIAL

DATA OUT

LOAD SUPPLY

SERIAL

DATA IN

BLANKING

BLNK

V

OUT

1

OUT

2

OUT

3

REGISTER

LATCHES

LOGIC SUPPLY

STROBE

V

ST

DD

OUT

5

OUT

4

1

2

3

8

9

13

14

15

16

17

19

4

5

6

7

12

18

20

GROUND

CLOCK

CLK

BB

OUT

9

OUT

10

Dwg. PP-029-9

OUT

8

OUT

7

OUT

6

LATCHES

REGISTER

10 11

NO

CONNECTION

NC

NO

CONNECTION

NC

A6810xLW

13

14

15

16

17

19

12

18

20

SERIAL

DATA OUT

LOAD SUPPLY

SERIAL

DATA IN

BLANKING

OUT

9

OUT

10

OUT

1

OUT

2

OUT

3

11

NO

CONNECTION

1

2

3

8

9

4

5

6

7

LOGIC SUPPLY

STROBE

GROUND

CLOCK

OUT

8

OUT

7

OUT

6

OUT

5

OUT

4

10

NO

CONNECTION

CLK

V

ST

BLNK

DD

BB

V

Dwg. PP-029-2

LATCHES

REGISTER

REGISTER

LATCHES

NC

NC

14

15

16

17

18

1

2

3

4

5

6

7

8

9

10

11

12

13

19

20

STROBE

V

DD

Dwg. PP-059

OUT

1

OUT

10

OUT

5

OUT

6

LATCHES

REGISTER

REGISTER

LATCHES

V

BB

CLOCK

NC

GROUND

LOGIC

SUPPLY

SERIAL

DATA OUT

LOAD

SUPPLY

NC

SERIAL

DATA IN

BLANKING

ST

CLK

BLNK

50 75 100 125 150

2.5

0.5

0

ALLOWABLE PACKAGE POWER DISSIPATION IN WATTS

AMBIENT TEMPERATURE IN °C

2.0

1.5

1.0

25

SUFFIX 'A', R = 60°C/W

θJA

SUFFIX 'EP', R = 59°C/W

θJA

Dwg. GP-024-1

SUFFIX 'LW', R = 70°C/W

θJA

Dwg. EP-010-5

IN

V

DD

V

BB

Dwg. EP-021-19

OUT

N

6809

AND

6810

10-BIT SERIAL-INPUT,

LATCHED SOURCE DRIVERS

www.allegromicro.com

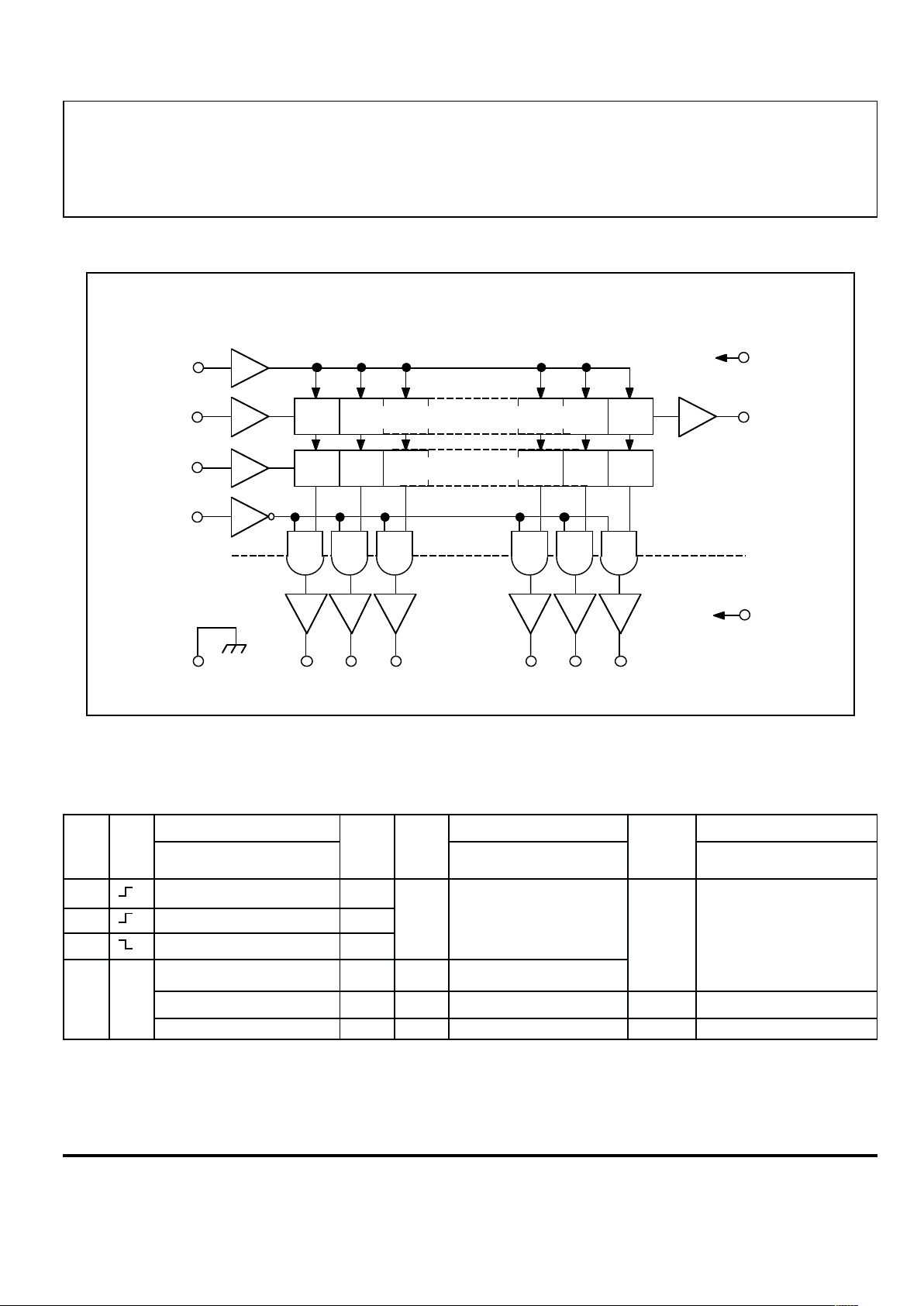

FUNCTIONAL BLOCK DIAGRAM

TRUTH TABLE

Serial Shift Register Contents Serial Latch Contents Output Contents

Data Clock Data Strobe

Input Input I

1I2I3

... I

N-1IN

Output Input I1I2I3... I

N-1IN

Blanklng I1I2I3... I

N-1

I

N

HHR

1R2

... R

N-2RN-1

R

N-1

LLR

1R2

... R

N-2RN-1

R

N-1

XR

1R2R3

... R

N-1RN

R

N

XXX...X X X L R1R2R3... R

N-1 RN

P1P2P3... P

N-1PN

P

N

HP1P2P3... P

N-1 PN

LP1P2P3... P

N-1 PN

X X X ... X X H L L L ... L L

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous State

MOS

BIPOLAR

OUT1OUT

2

GROUND

Dwg. FP-013-1

OUT

3

OUT

N

CLOCK

SERIAL

DATA IN

STROBE

BLANKING

SERIAL

DATA OUT

SERIAL-PARALLEL SHIFT REGISTER

LATCHES

V

DD

V

BB

LOGIC

SUPPLY

LOAD

SUPPLY

Loading...

Loading...